# Project Olympus Power Supply Software Interface Specification

Author:

Bryan Kelly, Principal Software Engineering Manager, Microsoft John Siegler, Senior Hardware Engineer, Microsoft

# **REVISION HISTORY**

| Revision/<br>Date | Notes                            |

|-------------------|----------------------------------|

| V1.0              | Ready for Project Olympus github |

© 2017 Microsoft Corporation.

As of November 1, 2017, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at <u>http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0</u>

Microsoft Corporation.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at <u>Project Olympus</u> <u>License Agreements</u>, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

CONTRIBUTORS AND LICENSORS OF THIS SPECIFICATION MAY HAVE MENTIONED CERTAIN TECHNOLOGIES THAT ARE MERELY REFERENCED WITHIN THIS SPECIFICATION AND NOT LICENSED UNDER THE OWF CLA OR OWFa. THE FOLLOWING IS A LIST OF MERELY REFERENCED TECHNOLOGY: INTELLIGENT PLATFORM MANAGEMENT INTERFACE (IPMI); I<sup>2</sup>C IS A TRADEMARK AND TECHNOLOGY OF NXP SEMICONDUCTORS ; EPYC IS A TRADEMARK AND TECHNOLOGY OF ADVANCED MICRO DEVICES INC.; ASPEED AST 2400/2500 FAMILY PROCESSORS IS A TECHNOLOGY OF ASPEED TECHNOLOGY INC.; MOLEX NANOPITCH, NANO PICOBLADE, AND MINI-FIT JR AND ASSOCIATED CONNECTORS ARE TRADEMARKS AND TECHNOLOGIES OF MOLEX LLC; WINBOND IS A TRADEMARK OF WINBOND ELECTRONICS CORPORATION; NVLINK IS A TECHNOLOGY OF NVIDIA; INTEL XEON SCALABLE PROCESSORS, INTEL QUICKASSIST TECHNOLOGY, INTEL HYPER-THREADING TECHNOLOGY, ENHANCED INTEL SPEEDSTEP TECHNOLOGY, INTEL VIRTUALIZATION TECHNOLOGY ARE TRADEMARKS AND TECHNOLOGIES OF INTEL CORPORATION; SITARA ARM CORTEX-A9 PROCESSOR IS A TRADEMARK AND TECHNOLOGY OF TEXAS INSTRUMENTS; GUIDE PINS FROM PENCOM; BATTERIES FROM PANASONIC. IMPLEMENTATION OF THESE TECHNOLOGIES MAY BE SUBJECT TO THEIR OWN LEGAL TERMS.

# CONTENTS

| 1 | Proj  | ect Olympus Power Supply Series - Overview6                               |

|---|-------|---------------------------------------------------------------------------|

| 2 | Proj  | ect Olympus Power Supply Series - PMBUS Commands7                         |

|   | 2.1   | Standard PMBUS Commands7                                                  |

|   | 2.2   | Custom PMBUS Commands8                                                    |

|   | 2.3   | Firmware Update Commands9                                                 |

| 3 | Com   | imand Description10                                                       |

|   | 3.1   | MAX_POUT (0xDA)10                                                         |

|   | 3.2   | PHASE (0x04)10                                                            |

|   | 3.3   | CAPABILITY (0x19)11                                                       |

|   | 3.4   | SMBALERT_MASK (0x1B)12                                                    |

|   | 3.5   | STATUS_MFR_SPECIFIC Or Batt_ATTN_Indicator (0x80)14                       |

|   | 3.6   | Battery Status (0xD6)15                                                   |

|   | 3.7   | BATT HEALTH TEST (0xD8)17                                                 |

|   | 3.8   | BATTERY POWER OUTPUT (BATT_POUT, 0xD5)17                                  |

|   | 3.9   | BATTERY STATE OF CHARGE (BATT_STAT_OF_CHARGE, 0xD7)17                     |

|   | 3.10  | BATTERY OPERATION TIME AT 100% LOAD (BATT_OP_TIME_100_LOAD, 0xD2)17       |

|   | 3.11  | BATTERY CHARGING OVER CURRENT LIMIT (BATT_OC_CHARGE_LIMIT, 0xDC)          |

|   | 3.12  | BATTERY STATE OF CHARGE CRITICAL LOWER LIMIT (BATT_SOC_LOWER_LIMIT, 0xDB) |

|   | 3.13  | PEAK SHAVING CONFIGURATION (PEAK_SHAVE_CONFIG, 0xD3)18                    |

|   | 3.14  | PEAK SHAVING LIMIT (PEAK_SHAVE_LIMIT, 0xD4)19                             |

|   | 3.15  | BATT_ARM (0xD0)19                                                         |

|   | 3.16  | PSU_FEED (0xD1)                                                           |

|   | 3.17  | FAN_COMMAND_1/2 (0x3B, 0x3C)21                                            |

|   | 3.18  | FAULT_HISTORY (0xA0)21                                                    |

| 4 | Firm  | ware Update Description23                                                 |

|   | 4.1   | Firmware Update Commands and Usage23                                      |

|   | 4.2   | Firmware Image Description24                                              |

|   | 4.3   | Firmware Upgrade Procedure:24                                             |

|   | 4.3.  | 1 Firmware Upgrade Flowchart26                                            |

|   | 4.4   | Firmware Update Command Description27                                     |

|   | 4.4.2 | 2 Additional Firmware Update Details/Requirements                         |

# 1 Project Olympus Power Supply Unit (POPSU) - Overview

This specification provides the PMBUS interface requirements for the POPSUs. The following table provides the power supplies governed by this specification:

| Power Supply         | Command Support Requi | red    |         |

|----------------------|-----------------------|--------|---------|

| Series Name          | Standard              | Custom | Battery |

| Server POPSU without | Х                     | Х      |         |

| Battery              |                       |        |         |

| Server POPSU with    | x                     | Х      | х       |

| Battery              |                       |        |         |

| JBOD POPSU without   | X                     | Х      |         |

| Battery              |                       |        |         |

Note: JBOD POPSU does not support a battery option.

# 2 Project Olympus Power Supply Series - PMBUS Commands

# 2.1 Standard PMBUS Commands

Refer to the PMBUS SPEC Rev 1.2 (<u>http://pmbus.org</u>) for definition of the commands listed in the table below. Some commands have overload their behavior (indicated using the '(Overloaded)' tag in the table), where behavior is described in subsequent sections in this document.

|         | Command [           | Description      |        |       | Applica | bility |

|---------|---------------------|------------------|--------|-------|---------|--------|

|         |                     | PMBUS            |        |       | PSU     | PSU    |

| Command |                     | Transaction Type | Data   | #Data |         | w/Batt |

| Code    | Command Name        | (Write/Read)     | Format | Bytes |         |        |

|         |                     | Write Byte/Read  |        |       | Y       | Y      |

| 0x01    | OPERATION           | Byte             | N/A    | 1     |         |        |

| 0x03    | CLEAR_FAULTS        | Send Byte/NA     | N/A    | 0     | Y       | Y      |

|         | FAN_COMMAND_1       | Write Word/Read  |        |       | Y       | Y      |

| 0x3B    |                     | Word             | Linear | 2     |         |        |

|         | FAN_COMMAND_2       | Write Word/Read  |        |       | Y       | Y      |

| 0x3C    |                     | Word             | Linear | 2     |         |        |

|         | IOUT_OC_FAULT_LIMIT | Write Word/Read  |        |       | Y       | Y      |

| 0x46    |                     | Word             | Linear | 2     |         |        |

|         | IOUT_OC_WARN_LIMIT  | Write Word/Read  |        |       | Y       | Y      |

| 0x4A    |                     | Word             | Linear | 2     |         |        |

| 0x5B    | IIN_OC_FAULT_LIMIT  | Read Word        | Linear | 2     | Y       | Y      |

|         | IIN_OC_WARN_LIMIT   | Write Word/Read  |        |       | Y       | Y      |

| 0x5D    |                     | Word             | Linear | 2     |         |        |

|         | PIN_OP_WARN_LIMIT   | Write Word/Read  |        |       | Y       | Y      |

| 0x6B    |                     | Word             | Linear | 2     |         |        |

|         |                     | Write Word/Read  |        |       | Y       | Y      |

| 0x79    | STATUS_WORD         | Word             | N/A    | 2     |         |        |

|         |                     | Write Byte/Read  |        |       | Y       | Y      |

| 0x7A    | STATUS_VOUT         | Byte             | N/A    | 1     |         |        |

|         |                     | Write Byte/Read  |        |       | Y       | Y      |

| 0x7B    | STATUS_IOUT         | Byte             | N/A    | 1     |         |        |

|         |                     | Write Byte/Read  |        |       | Y       | Y      |

| 0x7C    | STATUS_INPUT        | Byte             | N/A    | 1     |         |        |

|         |                     | Write Byte/Read  |        |       | Y       | Y      |

| 0x7D    | STATUS_TEMPERATURE  | Byte             | N/A    | 1     |         |        |

|         |                     | Write Byte/Read  |        |       | Y       | Y      |

| 0x7E    | STATUS_CML          | Byte             | N/A    | 1     |         |        |

| 0x8C    | READ_IOUT           | NA/Read Word     | Linear | 2     | Y       | Y      |

#### Table 1 - Standard Pmbus commands

| Open Compute Project     Project Olympus Power Supply Software Interface Spe | ecification |

|------------------------------------------------------------------------------|-------------|

| open compare i roject orjinpas i onei ouppij continui e interiate opt        |             |

| 0x96  | READ_POUT          | NA/Read Word      | Linear | 2  | Y | Y |

|-------|--------------------|-------------------|--------|----|---|---|

| 0x88  | READ_VIN           | NA/Read Word      | Linear | 2  | Y | Y |

| 0x89  | READ_IIN           | NA/Read Word      | Linear | 2  | Y | Y |

| 0x8D  | READ_TEMPERATURE_1 | NA/Read Word      | Linear | 2  | Y | Y |

| 0x97  | READ_PIN           | NA/Read Word      | Linear | 2  | Y | Y |

|       |                    | Block Write/Block |        |    | Y | Y |

| 0x9A  | MFR_MODEL          | Read              | ASCII  | 15 |   |   |

|       |                    | Block Write/Block |        |    | Y | Y |

| 0x9E  | MFR_SERIAL         | Read              | ASCII  | 15 |   |   |

|       |                    | Write Byte/Read   |        |    | Y | Y |

| 0x04  | PHASE (Overloaded) | Byte              | Linear | 1  |   |   |

|       | CAPABILITY         |                   |        |    | Y | Y |

| 0x19  | (Overloaded)       | NA/Read Byte      | N/A    | 1  |   |   |

|       |                    | Write             |        |    | Y | Y |

|       |                    | Word/Block        |        |    |   |   |

|       | SMBALERT_MASK      | write-Block read  |        |    |   |   |

| 0x1B  | (Overloaded)       | process call      | N/A    | 2  |   |   |

| 0xADh | IC_DEVICE_ID       | Block Read        | ASCII  | 20 | Y | Y |

| 0x99h | MFR_ID             | Block Read        | ASCII  | 15 | Y | Y |

Note: MFR\_MODEL, MFR\_SERIAL, IC\_DEVICE\_ID and MFR\_ID will have the length of the ASCII string as the first byte in the data payload.

# 2.2 Custom PMBUS Commands

The following table describes the custom PMBUS commands in detail in this section.

Note: JBOD POPSU does not support battery, therefore these commands and functions do not need to be implemented in systems supporting JBOD POPSU specification power supply.

Table 2 - Custom Pmbus commands

|          | Command Description   |              |        |       |        | Applicability |      |  |

|----------|-----------------------|--------------|--------|-------|--------|---------------|------|--|

|          |                       | PMBUS        |        |       | SERVE  | SERVE         | JBOD |  |

|          |                       | Transaction  |        |       | R      | R             | POPS |  |

|          |                       | Туре         | Data   | #Data | POPSU  | POPS          | U    |  |

| Cmd Code | Command Name          | (Write/Read) | Format | Bytes | w/Batt | U             |      |  |

|          | STATUS_MFR_SPECIFIC   | Write Word/  |        |       | Y      | Ν             | Ν    |  |

| 0x80     | (BATT_ATTN_INDICATOR) | Read Word    | N/A    | 1     |        |               |      |  |

| 0xA0     | FAULT_HISTORY         | Block Read   | N/A    | 24    | Y      | Y             | Y    |  |

|          |                       | NA/Read      |        |       | Y      | Ν             | Ν    |  |

| 0xD2     | BATT_OP_TIME_100_LOAD | Word         | Linear | 2     |        |               |      |  |

|          |                       | Write word/  |        |       | Y      | N             | Ν    |  |

| 0xD3     | PEAK_SHAVE_CONFIG     | Read Word    | N/A    | 2     |        |               |      |  |

| Open Co | ompute Project • Pr | oject Olympus Pow | er Supply Softwa | ire Interfac | e Specific | ation |   |

|---------|---------------------|-------------------|------------------|--------------|------------|-------|---|

|         |                     |                   | 1                |              |            |       | 1 |

|      |                      | Write word/ |        |   | Y | N | N |

|------|----------------------|-------------|--------|---|---|---|---|

| 0xD4 | PEAK_SHAVE_LIMIT     | Read Word   | N/A    | 2 |   |   |   |

|      |                      | NA/Read     |        |   | Y | N | N |

| 0xD5 | BATT_POUT            | Word        | Linear | 2 |   |   |   |

|      |                      | NA/Read     |        |   | Y | N | N |

| 0xD6 | BATT _STATUS         | Word        | N/A    | 2 |   |   |   |

|      |                      | NA/Read     |        |   | Y | N | N |

| 0xD7 | BATT_STAT_OF_CHARGE  | Word        | Linear | 2 |   |   |   |

|      |                      | Write Word/ |        |   | Y | N | N |

| 0xD8 | BATT_HEALTH_TEST     | Read Word   | N/A    | 2 |   |   |   |

|      |                      | Write Byte/ |        |   | Y | N | N |

| 0xD0 | BATT_ARM             | Read Byte   | N/A    | 1 |   |   |   |

|      |                      | NA/Read     |        |   | Y | N | N |

| 0xD1 | PSU_FEED             | Byte        | N/A    | 1 |   |   |   |

|      |                      | Write word/ |        |   | Y | N | N |

| 0xDA | MAX_POUT             | Read Word   | Linear | 2 |   |   |   |

|      | BATT_SOC_LOWER_LIMIT | Write Byte/ |        |   | Y | N | N |

| 0xDB |                      | Read Byte   | Linear | 1 |   |   |   |

|      | BATT_OC_CHARGE_LIMIT | Write Word/ |        |   | Y | N | N |

| 0xDC |                      | Read Word   | Linear | 2 |   |   |   |

# 2.3 FIRMWARE UPDATE COMMANDS

The following table describes the PMBUS commands required for PSU firmware update.

Table 3 - Custom Pmbus commands

|      | Command De        | escription   |        |          | Appli | cability |

|------|-------------------|--------------|--------|----------|-------|----------|

|      |                   | PMBUS        |        |          | PSU   | PSU      |

|      |                   | Transaction  |        |          |       | w/Batt   |

| Cmd  |                   | Туре         | Data   | #Data    |       |          |

| Code | Command Name      | (Write/Read) | Format | Bytes    |       |          |

|      |                   | NA/Block     |        |          | Y     | Y        |

|      |                   | write-Block  |        | 9(read)  |       |          |

|      |                   | read process |        | with     |       |          |

| OxEF | READ_FW_INFO      | call         | ASCII  | 1(write) |       |          |

|      | ENTER PROGRAMMING | Write Word   |        |          | Y     | Y        |

| 0xF0 | MODE              |              | N/A    | 1        |       |          |

| OxFB | WR_PROGRAM_MEM    | Block Write  | N/A    | 8        | Y     | Y        |

|      | FW_UPDATE_STATUS  | Write        |        |          | Y     | Y        |

|      |                   | Byte/Read    |        |          |       |          |

| 0xFC |                   | Byte         | N/A    | 1        |       |          |

|      | RD_PROGRAM_MEM    | NA/Block     |        | 8(read)  | Y     | Y        |

|      |                   | write-Block  |        | with     |       |          |

| 0xFD |                   |              | N/A    | 2(write) |       |          |

|      |                       | read process<br>call |     |          |   |   |

|------|-----------------------|----------------------|-----|----------|---|---|

| 0xF1 | EXIT_PROGRAMMING_MODE | Write Word           | N/A | 1        | Y | Y |

|      |                       | NA/Block             |     |          | Y | Y |

|      |                       | write-Block          |     | 3(read)  |   |   |

|      |                       | read process         |     | with     |   |   |

| 0xF2 | FW_DELAYS             | call                 | N/A | 1(write) |   |   |

|      |                       | Write Byte/          |     |          | Y | Y |

| 0xF8 | Send ROM Page         | Read Byte            | N/A | 1        |   |   |

# **3** COMMAND DESCRIPTION

This section describes each of the PMBUS commands. We provide detailed description of all the custom commands and provide necessary clarifications to standard PMBUS SPEC commands.

# 3.1 MAX\_POUT (0xDA)

The PSU will record the maximum observed output power (monitoring granularity: 1 second) and report this value via this command in a 2byte linear format. Refer to the standard PMBUS command IIN\_OC\_FAULT\_LIMIT which has a similar format. The monitoring window can be reset by the host by writing the value=0 using this command (write of any other value should return error).

Note that upon reset of the monitoring window, the PSU should overwrite the maximum power with the instantaneous power reading. Also, the maximum power reading should be persistent across PSU MCU resets (following a firmware update).

# 3.2 PHASE (0x04)

The PHASE command provides the ability to configure, control, and monitor the 3 phases supported by the PSU unit. The power-on default value of this command should be FFh indicating phase agnostic aggregate behavior (explained below). Monitoring of individual phase can be achieved by using the PHASE command with values from 00h to 02h.

After setting appropriate value in the PHASE command, all subsequently executed PMBUS commands should return phase specific values if applicable (refer to details below).

| Value     | Feed/Phase              |

|-----------|-------------------------|

| OxFF      |                         |

| (Power on | Applies to all 3 phases |

| Default)  | (aggregate)             |

| 0x00      | Applies to Phase 1      |

| 0x01      | Applies to Phase 2      |

0x02 Applies to Phase 3

The table above (Table 4 – Phase select command.), provides all supported values for the PHASE command. Note that, write of any other value for this PHASE command, other than the ones listed in this table, should return invalid or unsupported data PMBUS response.

The table below (Table 5 – Phase commands.) provides the expected behavior of the PMBUS commands for both aggregate phase (0xFF) and individual phase (values 0x00, 0x01, and 0x02) selection.

| Command Name       | Aggregate Behavior                            | Individual Behavior    |

|--------------------|-----------------------------------------------|------------------------|

|                    |                                               | Clear faults on chosen |

| CLEAR_FAULTS       | Clear faults on <i>all</i> phases and battery | phase                  |

| IIN_OC_FAULT_LIMIT |                                               | Value for the chosen   |

|                    | Aggregate value across all phases             | phase                  |

| IIN_OC_WARN_LIMIT  |                                               | Value for the chosen   |

|                    | Aggregate value across all phases             | phase                  |

| PIN_OP_WARN_LIMIT  |                                               | Value for the chosen   |

|                    | Aggregate value across all phases             | phase                  |

|                    | Indicate fault if any of the phase has        | Indicate fault if the  |

| STATUS_WORD        | fault                                         | chosen phase has fault |

|                    | Indicate fault if <i>any</i> of the phase has | Indicate fault if the  |

| STATUS_INPUT       | fault                                         | chosen phase has fault |

|                    |                                               | RMS Value for the      |

| READ_VIN           | RMS Average value across all phases           | <i>chosen</i> phase    |

|                    |                                               | RMS Value for the      |

| READ_IIN           | RMS Aggregate value across all phases         | <i>chosen</i> phase    |

|                    |                                               | Value for the chosen   |

| READ_PIN           | Aggregate value across all phases             | phase                  |

|                    |                                               | Behavior for the       |

| SMBALERT_MASK      | Aggregate behavior across all phases          | <i>chosen</i> phase    |

|                    | Aggregate behavior across all phases.         | Behavior for the       |

| OPERATION          | Read will be OR value of all phases.          | <i>chosen</i> phase    |

Table 5 – Phase commands.

Note: Commands that are not specified in the above table are Not Applicable (N/A) – it will have the same behavior irrespective of the phase selection.

# 3.3 CAPABILITY (0x19)

This is a standard PMBUS command (refer to the PMBUS SPEC II) and the expected value for this command is follows,

- Bit 7 : 1 (Packet Error Checking is supported)

- Bit 6:5 : 01 (Maximum supported bus speed is 400 Khz)

- Bit 4 : 1 (ALERT# signal with expected response supported)

- Bit 3 : 1 if Battery present (supported), 0 if Battery NOT present (not supported)

- Bit 2:0 : 000 (Reserved)

Note: On JBOD POPSU and SERVER POPSU without battery, bit 5 will read 0.

# 3.4 SMBALERT\_MASK (0x1B)

This command provides the ability to configure events that may trigger SMBALERT signal.

#### ALERT Trigger Requirements:

Each of the following events should be capable of asserting the SMBALERT. Table provides, events, trigger conditions and the expected response delay,

Table 6 – Alert commands.

| Command                | Bit Location          | Fault Trigger<br>Condition (default values)                       | Expected<br>trigger delay |

|------------------------|-----------------------|-------------------------------------------------------------------|---------------------------|

| STATUS_VOUT<br>(0x7A)  | Bit7: Vout_OV_fault   | Vo >13.8V                                                         | <2ms                      |

|                        | Bit4: Vout_UV_fault   | Vo < 9.8V                                                         | <2ms                      |

| STATUS_IOUT<br>(0X7B)  | Bit7: lout_OC_fault   | lout > max rated current (see<br>details below)                   | <5-10ms                   |

|                        | Bit5: lout_OC_warning | lout > programmable current value<br>(see details below)          | <5-10ms                   |

| STATUS_INPUT<br>(0x7C) | Bit1: IIN_OC_warning  | 'Input Power + battery charge<br>power' exceeds warning threshold | <5ms                      |

|                                                                       | Bit2: IIN_OC_fault                                                                                                                                                                                                                                                          | 'Input Power + battery charge<br>power' exceeds fault threshold  | <5ms                                   |  |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------|--|--|

|                                                                       | Bit3: Unit off for low<br>output voltage<br>Bit4: Vin_UV_fault                                                                                                                                                                                                              | AC_Fail<br>Vac < 180 Vpk (Blackout)<br>Vac< 180 Vrms (Brownout)  | <10ms (from either<br>of these events) |  |  |

| STATUS_TEMPE<br>RATURE<br>(0x7D)                                      | Bit7: OT_fault                                                                                                                                                                                                                                                              | Default threshold value: 20 degrees below max rated temperature. | < 1s                                   |  |  |

|                                                                       | Bit6: OT_warning                                                                                                                                                                                                                                                            | Default threshold value: 20 degrees below max rated temperature. | < 1s                                   |  |  |

| STATUS_CML<br>(0x7E)                                                  | Bit0: Other_Logic_Fault<br>Bit1: Other<br>communication Fault<br>Bit2: Reserved<br>Bit3: Processor Fault<br>Detected<br>Bit4: Memory Fault<br>Detected<br>Bit5: Packet Error<br>Check Failed<br>Bit6:<br>Invalid/Unsupported<br>Data<br>Bit7:<br>Invalid/Unsupported<br>Cmd | 1.) UART Communication Error<br>2.) Battery Communication Error  | 1.) <125ms<br>2.) <1sec                |  |  |

| STATUS_MFR_S<br>PECIFIC –<br>Battery<br>Attention<br>Indicator (0x80) | N/A                                                                                                                                                                                                                                                                         | N/A                                                              | N/A                                    |  |  |

Note that each of events indicated via corresponding STATUS commands, when triggered, apart from sending ALERT signal, should also register a fault status. This status can be probed via the corresponding STATUS commands. Further, both the fault status bits signal MUST be sticky – it should be cleared only upon receiving an explicit CLEAR\_FAULTS command (and not upon removal of the trigger event or power reset of the PSU).

The SMB\_ALERT is expected to be non-sticky with a minimum assertion time of 20ms.

Finally, the value of the ALERT thresholds (current, voltage etc.,) configured via separate PMBUS commands (Iout\_OC\_fault, Iout\_OC\_warning etc.,) must be respected within +/- 1% accuracy (Note that this deviation accuracy refers to the difference between the measured alert event reading and set alert event threshold (and NOT the deviation from actual event reading). We specify the timing requirement (delay between the ALERT event trigger and assertion of the ALERT signal) in the table. In other words, we expect the ALERT signal to be sent as soon as the ALERT threshold is violated, both in time and in the threshold magnitude.

SMBALERT\_MASK command will be used to determine what events raise SMBALERT and what events are masked. By default, only over current should be enabled and all other events should be masked. For all other STATUS\_\* commands except for over current, the default power-on value of SMBALERT\_MASK command should be 0xFF (1111 1111). For STATUS\_IOUT, the value should be 0x5F (0101 1111).

The factory-default value for the IOUT\_OC\_FAULT\_LIMIT (0x46) register is specified in the hardware SPEC. This register should be made READ ONLY and any attempt to write should fail.

The factory-default value for the IOUT\_OC\_WARN\_LIMIT (0x4A) is the same as that of IOUT\_OC\_FAULT\_LIMIT. But this register is Read/Write and can later be modified.

There should be no other conditions that cause SMB\_ALERT to assert other than overcurrent.

Note: SMB\_ALERT is externally tied to a notification mechanism that results in performance degradation and throttling of the server. It is imperative SMB\_ALERT does not occur for any event other than OC.

# 3.5 STATUS\_MFR\_SPECIFIC OR BATT\_ATTN\_INDICATOR (0x80)

The table below (Table 7 – Manufacture specific error status.) provides details of the status bits for STATUS\_MFR\_SPECIFIC PMBUS command.

| Function              | Bit<br>position | Value:<br>1/0 | Conditions                                                                                                                                                                                                                                                            |

|-----------------------|-----------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Over temperature (OT) | Bit 7           | 1             | Battery over-temperature is detected<br>*In charging<br>Cell temperature > 53 degree C<br>or Cell temperature < 3 degree C<br>*Not charging<br>Cell temperature > 50 degree C<br>or Cell temperature < 5 degree C<br>Or discharge and charge converter OT is detected |

Table 7 – Manufacture specific error status.

|                                                    |       | 0 | Battery over-temperature is not detected                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------|-------|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    |       | 0 | State of Charge threshold breach Flag. Active                                                                                                                                                                                                                                                                                                            |

| State of charge critical                           |       | 1 | when set. Indicates battery state of charge is                                                                                                                                                                                                                                                                                                           |

| lower threshold                                    | Bit 6 | - | below SOC_LT threshold (say <25%)                                                                                                                                                                                                                                                                                                                        |

| (SOC_LT)                                           |       | 0 | State of charge is higher than critical (SOC_LT)<br>threshold                                                                                                                                                                                                                                                                                            |

| Under voltage<br>protection (UVP)                  | Bit 5 | 1 | Status bit that indicates one or more cells is below<br>the cell minimum operating voltage threshold<br>Or the discharge and charge converter output is <<br>out of limit UVP                                                                                                                                                                            |

|                                                    |       | 0 | Under voltage is not detected                                                                                                                                                                                                                                                                                                                            |

| Over voltage charge<br>protection<br>(OV_CHG)      | Bit 4 | 1 | Status bit that indicates one or more cells is above<br>the cell voltage threshold that indicates an<br>overcharge condition. Charging is prohibited.<br>Active when set.                                                                                                                                                                                |

|                                                    |       | 0 | No over voltage charge is detected                                                                                                                                                                                                                                                                                                                       |

| Over current<br>charge protection                  | Bit 3 | 1 | Indicates Overcurrent in charge condition<br>detected. Active when set. Charge is prohibited<br>until flag is cleared.                                                                                                                                                                                                                                   |

| (OC_CHG)                                           |       | 0 | Battery charge current is normal                                                                                                                                                                                                                                                                                                                         |

| Over current<br>discharge protection<br>(OC_DSCHG) | Bit 2 | 1 | Indicates Overcurrent in discharge condition<br>detected. Active when set. Discharge is<br>prohibited until flag is cleared.<br>Or the discharge and charge converter output is ><br>out of limit OCP                                                                                                                                                    |

|                                                    |       | 0 | Battery discharge current is normal                                                                                                                                                                                                                                                                                                                      |

| Cell Imbalance/Failure                             | Bit 1 | 1 | Status bit that indicates Cell imbalance or Weak<br>Cell detected. Active when set.                                                                                                                                                                                                                                                                      |

| (CF)                                               |       | 0 | No cell imbalance or weak cell detected.                                                                                                                                                                                                                                                                                                                 |

| Permanent Failure (PF)                             | Bit O | 1 | Indicates Permanent hardware failure detected,<br>such as unrecoverable communication errors<br>internal to the battery, open thermistor, etc., Cell<br>permanent fail condition detected, Momentary<br>cell temperature or cell voltage reached<br>permanent fail limits. Active when set. Charge<br>and discharge is prohibited until flag is cleared. |

|                                                    |       | 0 | No permanent failures                                                                                                                                                                                                                                                                                                                                    |

|                                                    |       |   | •                                                                                                                                                                                                                                                                                                                                                        |

# 3.6 BATTERY STATUS (0xD6)

On PSU where battery is supported the following table (Table 8 – Battery Status) provides status bits.

Table 8 – Battery Status

| Function | Bit<br>position | Value:<br>1/0 | Conditions |

|----------|-----------------|---------------|------------|

|----------|-----------------|---------------|------------|

| Reserve     | Bit 15                   | 1 |                                                                 |

|-------------|--------------------------|---|-----------------------------------------------------------------|

| Neserve     | DICID                    | 0 |                                                                 |

| Reserve     | Bit 14                   | 1 |                                                                 |

|             |                          | 0 |                                                                 |

| Reserve     | Bit 13                   | 1 |                                                                 |

|             |                          | 0 |                                                                 |

| Reserve     | Bit 12                   | 1 |                                                                 |

|             | 511 12                   | 0 |                                                                 |

| Reserve     | Bit 11                   | 1 |                                                                 |

|             |                          | 0 |                                                                 |

| Reserve     | Bit 10                   | 1 |                                                                 |

|             | Dit 10                   | 0 |                                                                 |

| Reserve     | Bit 9                    | 1 |                                                                 |

|             |                          | 0 |                                                                 |

| Reserve     | Bit 8                    | 1 |                                                                 |

|             |                          | 0 |                                                                 |

|             |                          | 1 | Status bit indicating that cells are being balanced.            |

| BAL_ACTIVE  | Bit 7                    |   | Active when set.                                                |

|             |                          | 0 |                                                                 |

|             |                          |   | Status bit that indicates battery management                    |

|             | <b>D</b> <sup>11</sup> C | 1 | system is running on external power (+12Vsb).                   |

| EP_PRESENT  | Bit 6                    |   | This represents normal operating condition.<br>Active when set. |

|             |                          | 0 | Active when set.                                                |

|             |                          | 0 | Status bit that indicates that battery cell voltage             |

|             |                          | 1 | conditions are below normal charging limits, but                |

| PCHG_EN     | Bit 5                    | - | above Permanent Fail limits. Active when set.                   |

|             |                          | 0 |                                                                 |

|             |                          |   | Status bit that indicates battery conditions are                |

|             |                          |   | normal, and things like SOC, cell voltage, balance,             |

|             | Bit 4                    |   | etc. are suitable for discharge. Active when set.               |

| DSCHG_EN    |                          |   |                                                                 |

|             |                          |   | Status bit that indicates battery conditions are                |

|             | Bit 3                    | 1 | normal, and battery is capable of accepting                     |

|             | DIL 5                    |   | charge. Active when set.                                        |

| CHG_EN      |                          | 0 |                                                                 |

|             |                          | 1 | Status bit indicating that charge current is                    |

|             | Bit 2                    |   | detected. Active when set.                                      |

| Charging    |                          | 0 | Not Charging                                                    |

|             |                          | 1 | Status bit indicating that discharge current is                 |

|             | Bit 1                    |   | detected. Active when set.                                      |

| Discharging |                          | 0 | Not discharging                                                 |

|             | Bit O                    | 1 | Assembled in battery manufacturer                               |

| Initialized |                          | 0 | EEPROM Error is detected                                        |

# 3.7 BATT HEALTH TEST (0xD8)

This command is a Write Word command which can force battery to enter backup mode for 2 seconds.

After test, user can read BATT\_HEALTH\_STATUS (0xD6) and BATT\_FAULT\_INDICATOR (0x80) to check if Battery can function properly.

Table 9 – Battery Health Test (0xD8)

| #Bytes  | 1 | 7                | 1 | 1 | 8                                    | 1 | 8                              | 1 | 8                               | 1 | 8                 | 1 | 1 |

|---------|---|------------------|---|---|--------------------------------------|---|--------------------------------|---|---------------------------------|---|-------------------|---|---|

| Content | S | Slave<br>Address | W | A | BATT_HEALTH_TEST<br>(cmd code: 0xD8) | А | Password<br>Low<br>Byte (0xCD) | А | Password<br>High Byte<br>(0xAB) | A | PEC<br>(Optional) | A | Ρ |

Below is the suggested test sequence:

- 1. User send 0xD8 (Battery Health Test) PMBus command with password (0xABCD) to start Battery Health Test.

- 2. During or after the test, user can monitor the result by reading the 0xD6 (Battery Health Status) and 0x80 (Battery Fault Indicator) through the PMBus Command.

If this command require the battery to be discharged, it should be restricted to less than 2 seconds of discharge.

NOTE: Before battery health test finished, another battery health test command will be ignored. Further, both battery peak shaving (see below) and battery health test can coincide if possible, otherwise, clear failure response must be provided back to the user.

# 3.8 BATTERY POWER OUTPUT (BATT\_POUT, 0xD5)

This command returns the battery power output in Watts. This command follows the same request/response format as the standard PMBUS command, READ\_POUT (0x96) specified in the PMBUS SPEC.

# 3.9 BATTERY STATE OF CHARGE (BATT\_STAT\_OF\_CHARGE, 0xD7)

This command returns the battery charge level and is presented as a percentage between 0 to 100%. This command follows the same request/response format as the standard PMBUS command, READ\_POUT (0x96) specified in the PMBUS SPEC.

# 3.10 BATTERY OPERATION TIME AT 100% LOAD (BATT\_OP\_TIME\_100\_LOAD, 0xD2)

This command returns the number of seconds the battery can deliver power at 100% (full load) of its power output capacity, starting from 100% or full capacity.

This command follows the same request/response format as the standard PMBUS command, READ\_POUT (0x96) specified in the PMBUS SPEC.

# 3.11 BATTERY CHARGING OVER CURRENT LIMIT (BATT\_OC\_CHARGE\_LIMIT, 0xDC)

This commands sets the over current limit in Amperes associated with battery charge current. This command follows the same request/response format as the standard PMBUS command, IOUT\_OC\_FAULT\_LIMIT Read/Write Word specified in the PMBUS SPEC. The set limit value will be used for triggering the ALERT# signal on the power device.

# 3.12 BATTERY STATE OF CHARGE CRITICAL LOWER LIMIT (BATT\_SOC\_LOWER\_LIMIT, 0xDB)

This commands sets the lower limit for the battery state of charge in percentage (between 0 and 100%) The set limit value will be used for triggering the ALERT# signal on the power device.

# 3.13 PEAK SHAVING CONFIGURATION (PEAK\_SHAVE\_CONFIG, 0xD3)

This command is a Read/Write Word command which get/set configuration settings associated with peak shaving using battery energy. This command will be used in conjunction with the command to set the power limit (see 0xD4 below).

Configuration parameters for peak shaving:

- Battery lower threshold in percentage (0 to 100) which specifies the threshold beyond which battery will stop performing peak shaving. Default value for this is 50.

- Battery higher threshold in percentage (0 to 100) which specifies the threshold beyond which battery will start performing peak shaving. When this value is 100, it signifies that peak shaving is disabled. Default value is 100 (disabled).

| 1 | 7                | 1 | 1 | 8                | 1 | 8                             | 1 | 8                              | 1 | 8                 | 1 | 1 |

|---|------------------|---|---|------------------|---|-------------------------------|---|--------------------------------|---|-------------------|---|---|

| S | Slave<br>Address | W | А | Cmd code<br>0xD3 | А | Battery<br>Lower<br>Threshold | А | Battery<br>Higher<br>Threshold | A | PEC<br>(Optional) | А | Ρ |

Table 10 – Write Peak Shaving Configuration (0xD3)

Table 11 – Read Peak Shaving Configuration (0xD3)

| 1 | 7                    | 1 | 1 | 8                    | 1 | 1      | 7                | 1 | 1 | 8                             | 1 | 8                              | 1 | 8                 | 1 | 1 |

|---|----------------------|---|---|----------------------|---|--------|------------------|---|---|-------------------------------|---|--------------------------------|---|-------------------|---|---|

| S | Slave<br>Addres<br>s | w | А | Cmd<br>code:<br>0xD3 | А | S<br>r | Slave<br>Address | R | А | Battery<br>Lower<br>Threshold | А | Battery<br>Higher<br>Threshold | A | PEC<br>(Optional) | Ν | Р |

# 3.14 PEAK SHAVING LIMIT (PEAK\_SHAVE\_LIMIT, 0xD4)

This command is a Read/Write Word command with "Linear" data format which gets/sets the power limit in watts. The PSU/battery module will try to adhere to this power limit in an opportunistic fashion (refer to the battery peak shaving configuration command 0xD3 above) by using battery energy. This command follows the same request/response format as the standard PMBUS command, IOUT\_OC\_FAULT\_LIMIT (0x46) specified in the PMBUS SPEC.

When the set power limit is about to be breached, the battery will "supplement" power to ensure that the power limit is always enforced. It is important to note that the PSU will still provide power up to the set power limit and the battery will supplement the rest. For instance, if the set power limit is 120W and the actual power draw is 135W, the PSU will provide 120W and the battery will provide the remaining 15W. This peak shaving operation is further determined by the lower/higher configuration battery charge thresholds as specified in the Peak\_shave\_config (0xD3) command above.

|   | Write Peak Shaving Limit (0xD4) |   |   |                  |   |                       |   |                       |   |                   |   |   |

|---|---------------------------------|---|---|------------------|---|-----------------------|---|-----------------------|---|-------------------|---|---|

| 1 | 7                               | 1 | 1 | 8                | 1 | 8                     | 1 | 8                     | 1 | 8                 | 1 | 1 |

| S | Slave<br>Address                | W | А | Cmd code<br>0xD4 | А | Power Limit<br>Byte 1 | А | Power Limit<br>Byte 2 | A | PEC<br>(Optional) | A | Ρ |

#### Table 12 – Write Peak Shaving Limit (0xD4)

#### Table 13 – Read Peak Shaving Limit (0xD4)

|   | Read Peak Shaving Limit (0xD4) |   |   |                      |   |        |                  |   |   |                       |   |                       |   |                   |   |   |

|---|--------------------------------|---|---|----------------------|---|--------|------------------|---|---|-----------------------|---|-----------------------|---|-------------------|---|---|

| 1 | 7                              | 1 | 1 | 8                    | 1 | 1      | 7                | 1 | 1 | 8                     | 1 | 8                     | 1 | 8                 | 1 | 1 |

| s | Slave<br>Addres<br>s           | W | A | Cmd<br>code:<br>0xD4 | А | S<br>r | Slave<br>Address | R | А | Power Limit<br>Byte 1 | A | Power Limit<br>Byte 2 | A | PEC<br>(Optional) | Ν | Ρ |

# 3.15 BATT\_ARM (0xD0)

This command is a Read/Write Byte command which can enables/disables PSU to enter battery backup mode when AC is loss. Default setting is battery backup mode enabled. This command's data content will be reset to default value after PSU shutdown.

Table 14 – Write BATT\_ARM (0xD0)

| 1 | 7                | 1 | 1 | 8                | 1 | 8                                                                    | 1 | 8                 | 1 | 1 |

|---|------------------|---|---|------------------|---|----------------------------------------------------------------------|---|-------------------|---|---|

| S | Slave<br>Address | w | А | Cmd code<br>0xD0 | А | BATTERY ARM State<br>No Op (0xAA)<br>Enable (0xBB)<br>Disable (0xCC) | А | PEC<br>(Optional) | А | Ρ |

#### **Battery ARM state:**

<u>No Op (0xAA)</u>: Factory-default and power-on-default value and indicates default PSU/Battery operation. In this mode, the PSU will start to source from battery when any of the following events happen,

- If AC is lost,

- When the PSU is removed from the chassis (PS\_KILL goes from low to high),

<u>Enable (0xBB)</u>: When AC/utility is available and active, this command will forcefully initiate battery sourcing. This command is ignored when battery is already sourcing.

- When battery capacity becomes empty and utility power is available, utility sourcing should resume and the value should revert to 0xAA.

- When battery capacity becomes empty and utility power is not available, the PSU will shut off output. In this event, upon subsequent power on (when utility resumes), the value should go back to 0xAA.

#### Disable (0xCC):

When Battery sourcing is active, this command will

- (i) When AC/utility is available, initiate AC/utility sourcing (and revert value to 0xAA)

- (ii) When AC/utility is unavailable, shutdown PSU output and all microcontrollers (and revert value to 0xAA upon subsequent PSU power on).

When utility/AC sourcing is active, this command will not cause any immediate effect but the value is stored and later used when AC is lost.

NOTE: IT IS IMPERATIVE THAT THE BATT\_ARM MODE GOES BACK TO 0xAA WHENEVER THE PSU/MICROCONTROLLER IS RESET.

NOTE: PSU must meet ITIC requirement whenever switching between AC and battery.

Table 15 - Read BATT\_ARM (0xD0)

| 1 | 7                | 1 | 1 | 8                 | 1 | 1  | 7                | 1 | 1 | 8                    | 1 | 8                 | 1 | 1 |

|---|------------------|---|---|-------------------|---|----|------------------|---|---|----------------------|---|-------------------|---|---|

| s | Slave<br>Address | W | A | Cmd code:<br>0xD0 | А | Sr | Slave<br>Address | R | A | BATTERY<br>ARM State | A | PEC<br>(Optional) | N | Ρ |

# 3.16 PSU\_FEED (0xD1)

This command is a Read Byte command which returns the active feed of the PSU.

Table 16 – Read PSU\_FEED (0xD1)

| ç | Slave   | W  | Δ | Cmd code: | ^ | Sr | Slave   | D | Δ | PSU ACTIVE | Α | PEC        |   |   |

|---|---------|----|---|-----------|---|----|---------|---|---|------------|---|------------|---|---|

| 3 | Address | vv | ~ | 0xD1      | ~ |    | Address | n | ~ | FEED       |   | (Optional) | Ν | Р |

|  |  |  |  |  | 0xAA: Primary        |  |  |

|--|--|--|--|--|----------------------|--|--|

|  |  |  |  |  | Feed                 |  |  |

|  |  |  |  |  | OxBB: Backup         |  |  |

|  |  |  |  |  | Feed                 |  |  |

|  |  |  |  |  | 0xCC: No Feed        |  |  |

|  |  |  |  |  | (in battery<br>mode) |  |  |

|  |  |  |  |  | mode)                |  |  |

# 3.17 FAN\_COMMAND\_1/2 (0x3B, 0x3C)

These are standard PMBUS commands used to control the fans in the power supply unit. To set the fans to 100% duty cycle, set the data bytes to 0x64 0x00 (Data Byte Low, Data Byte High). To set the fans to 30% duty cycle, set the data bytes to 0x1E 0x00 (Data Byte Low, Data Byte High).

# 3.18 FAULT\_HISTORY (0xA0)

This read-only command is used to retrieve the failure history log. The failure history event will be stored into non-volatile memory (external flash) if any sub module encounters a fault that causes its output to shut off. The fault history is recorded immediately prior to the 12V output going low. If there is already a log entry present, another fault should not overwrite the existing log entry.

The following conditions should trigger the log history to be recorded:

- Input UVP

- Input OVP

- Output UVP

- Output OVP

- Input OCP

- Output OCP

- Any OTP

- Fan fault

- Watchdog reset

- Both IVS Feed A/B Error

The CLEAR\_FAULTS command is used clear the log history. If there are no faults, the hour and minute bytes (bytes 1-3) should return zero. That will indicate to the client that the log is clear.

The following table shows the data returned.

|                | Fault History |                     |             |  |  |  |  |  |  |

|----------------|---------------|---------------------|-------------|--|--|--|--|--|--|

| Byte<br>number | Byte order    | Description         | Data Format |  |  |  |  |  |  |

| 0              |               | Phase (single byte) | N/A         |  |  |  |  |  |  |

|    |           | Bit 0: Phase 1<br>Bit 1: Phase 2<br>Bit 2: Phase 3<br>Bit 3: BBU (Battery Backup Unit)<br>The corresponding bit where the fault occurred<br>should be set. If all phases had the fault, the<br>value in this byte should be 0x7. |                                                    |

|----|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1  |           | Minute used when fault occurred (single byte)                                                                                                                                                                                    | N/A                                                |

| 2  | Low byte  | Hour used when fault occurred                                                                                                                                                                                                    |                                                    |

| 3  | High byte | Hour used when fault occurred                                                                                                                                                                                                    | N/A                                                |

| 4  | Low byte  | Fault status word (same as 0x70h)                                                                                                                                                                                                |                                                    |

| 5  | High byte | Fault status word (same as 0x79h)                                                                                                                                                                                                | N/A                                                |

| 6  | Low byte  |                                                                                                                                                                                                                                  | Linear. Note:                                      |

| 7  |           | Output voltage when fault occurred                                                                                                                                                                                               | VOUT_MODE<br>is fixed to<br>0x1A for<br>converting |

|    | High byte |                                                                                                                                                                                                                                  | this field.                                        |

| 8  | Low byte  | Output Current when fault occurred                                                                                                                                                                                               | Linear                                             |

| 9  | High byte |                                                                                                                                                                                                                                  |                                                    |

| 10 | Low byte  | Output Power when fault occurred                                                                                                                                                                                                 | Linear                                             |

| 11 | High byte |                                                                                                                                                                                                                                  | Lincul                                             |

| 12 | Low byte  | Input Voltage when fault occurred                                                                                                                                                                                                | Linear                                             |

| 13 | High byte |                                                                                                                                                                                                                                  | Linedi                                             |

| 14 | Low byte  | Input Current when fault occurred                                                                                                                                                                                                | Linear                                             |

| 15 | High byte |                                                                                                                                                                                                                                  | Lincui                                             |

| 16 | Low byte  | Input Power when fault occurred                                                                                                                                                                                                  | Linear                                             |

| 17 | High byte |                                                                                                                                                                                                                                  | Lincui                                             |

| 18 | Low byte  | Ambient Temperature                                                                                                                                                                                                              | Linear                                             |

| 19 | High byte |                                                                                                                                                                                                                                  |                                                    |

| 20 | Low byte  | Fan 1 speed                             | Linear |

|----|-----------|-----------------------------------------|--------|

| 21 | High byte |                                         |        |

| 22 | Low byte  | Fan 2 speed                             | Linear |

| 23 | High byte |                                         |        |

| 24 |           | Bit map for reset flag and IVS Feed A/B | Linear |

| 25 |           | BATT_ATTN_INDICATOR (0x80)              | N/A    |

| 26 | Low byte  |                                         | N/A    |

| 27 | High byte | Battery Status (0xD6)                   | ,      |

| Bit map for reset flag and<br>IVS FeedA/B | Description                       |

|-------------------------------------------|-----------------------------------|

| 0                                         | BOR: DSP brown out reset flag     |

| 1                                         | WDTO: watchdog time out flag      |

| 2                                         | SWR: software reset flag          |

| 3                                         | EXTR: external reset flag         |

| 4                                         | IOPUWR: illegal opcode reset flag |

| 5                                         | RESERVE                           |

| 6                                         | Feed A lost                       |

| 7                                         | Feed B lost                       |

# 4 FIRMWARE UPDATE DESCRIPTION

This section describes each of the Firmware Update commands.

# 4.1 Firmware Update Commands and Usage

In this section, we provide the instructions and requirement associated with updating the firmware in the power supply unit.

# 4.2 FIRMWARE IMAGE DESCRIPTION

The firmware image is logically divided into two regions, bootloader image region and the application image region. The application region is in turn divided in to two regions – region A and region B – which will be used for storing two version of the application image. Note that only one version of the application, either A or B will be active at any time. These three regions, Bootloader, Application Image A and Application Image B of the firmware image along with their recommended size are specified in the table below. Note that the specified size is only a recommendation and we expect provisioning enough storage space (FLASH size) to accommodate future PMBUS command and functional additions.

Each of the three regions will have a corresponding *Intel HEX* formatted image file.

| Area                | Size     |

|---------------------|----------|

| Bootloader Image    | 16Kbytes |

| Application Image A | 32Kbytes |

| Application Image B | 32Kbytes |

Table 18 – Firmware Regions

Table: Firmware regions with recommended size

# 4.3 FIRMWARE UPGRADE PROCEDURE:

- 1. Firmware update will be performed to one of the 3 regions (Boot loader, Application image A and Application Image B) of the firmware image at any time, using the corresponding region's hex file.

- 2. Host enters firmware update mode to the chosen region by specific PMBUS Command (enter\_programming\_mode 0xF0) with specific region. Power device will erase the specified region as part of the enter\_programming\_mode command.

- 3. Host reads the *Intel Hex* formatted image file in sequence and perform action based on the record type,

- a. Record type 0x00: Write the firmware image in the specified address location in the HEX file

- b. Record type 0x04: Set the appropriate Page number specified in the HEX file

- c. Record type 0x01: Exit programming.

- 4. Status code is provided to indicate status/error during firmware update process.

- 5. When there is any interruption during programming (e.g. power reset), host can restart procedure by exiting then entering the programming mode again.

- 6. Host verifies integrity of the written image by reading back image data and compare it with HEX file data.

- 7. After verification, program can exit firmware update mode by specific PMBUS command (0xF1).

- 8. When firmware update mode is exited, the user can specify the following actions:

- a. Jump to bootloader:

- Power device should jump to new bootloader and run the active application image

- b. Jump to application image:

- Power device should switch to the specified application image

- Once the specified firmware image is loaded correctly, update active application image (refer to READ\_FW\_INFO command). Any error during application load should revert to the original application image region.

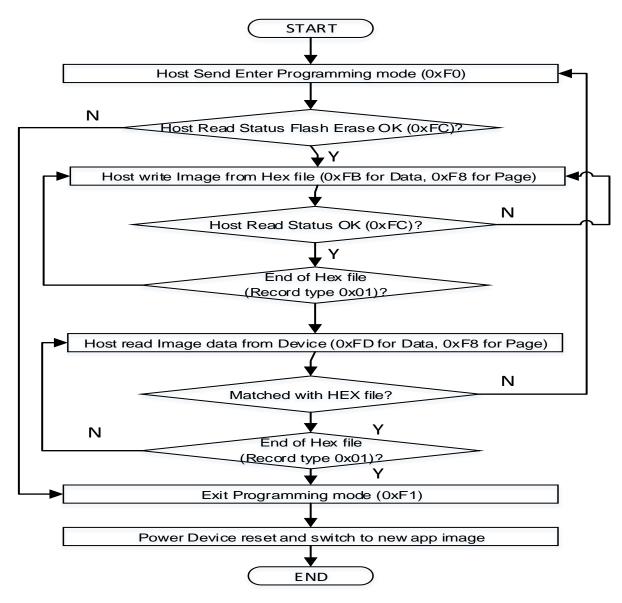

#### 4.3.1 Firmware Upgrade Flowchart

The firmware update follow the workflow outlined in Figure 1 - Firmware Update

Figure 1 - Firmware Update workflow

# 4.4 FIRMWARE UPDATE COMMAND DESCRIPTION

# 4.4.1.1 Enter Programming Mode (0xF0)

This command is used to enter into the firmware upgrade mode from application mode. The programming mode indicates which region should be erased. The power device shall return failure when the host attempts to program (ENTER\_PROGRAMMING) the *active* application region.

| 1 | 7                | 1 | 1 | 8                                                      |   | 8    | 1 | 8                 | 1 | 1 |

|---|------------------|---|---|--------------------------------------------------------|---|------|---|-------------------|---|---|

| s | Slave<br>Address | w | A | Enter<br>Programming<br>Mode<br>Command Code<br>(0xF0) | А | Mode | А | PEC<br>(Optional) | A | Ρ |

Table 19 – Enter Programming Mode (0xF0)

| Name | Length | Description  | Remark                                    |

|------|--------|--------------|-------------------------------------------|

|      |        |              | 0 – Bootloader<br>1 – Application Image A |

| Mode | 1 byte | Programming  | 2 – Application Image A                   |

|      |        | Mode         | 5 – No erase. Used by host to read        |

|      |        |              | program memory                            |

| PEC  | 1 byte | Packet Error | CRC8 code is calculated per SMBus         |

| FEC  | T Dyte | Check        | Specification.                            |

# 4.4.1.2 Send ROM Page (0xF8)

This command is used to change Flash memory page setting when host is reading/writing program memory. When used in READ mode, the command should return the current page in the flash memory.

Example:

Host need to extract 1 byte highlighted in green from HEX file and send as below format,

#### :0200000400<mark>01</mark>F9

Table 20 – Send ROM Page (0xF8)

| 1 | 7                | 1 | 1 | 8                       | 1 | 1  | 7                                    | 1 | 8        | 1 | 1 |

|---|------------------|---|---|-------------------------|---|----|--------------------------------------|---|----------|---|---|

| s | Slave<br>Address | w | А | Send ROM<br>Page (0xF8) | А | Sr | Rom<br>Page<br>(Ox <mark>01</mark> ) | А | Checksum | А | Ρ |

| Name     | Length | Description               | Remark                                                                                                                 |

|----------|--------|---------------------------|------------------------------------------------------------------------------------------------------------------------|

| Rom Page | 1 byte | Flash memory page setting | Set target flash memory page<br>in program memory.                                                                     |

| Checksum | 1 byte | Checksum                  | Arithmetic sum of all bytes sent,<br>including slave address and its<br>R/W bit. Note that this field is<br>mandatory. |

# 4.4.1.3 Write Program Memory (Write ROM data) (0xFB)

This command is used to transfer data from HEX file to the power device, and write into the program memory. Please refer to Table 21 – HEX File Data Format for more detailed information.

| Name              | Length   | Description                              | Remark                                                                                                                          |

|-------------------|----------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Data Length       | 1 byte   | Number of bytes in<br>the<br>data field. | 16 (0x10) bytes of data are the<br>usual values. Directly get from<br>HEX file                                                  |

| Address<br>offset | 2 bytes  | 16-bit program<br>memory address         | Directly get from HEX file                                                                                                      |

| Record Type       | 1 byte   | Defining the type of<br>the data field   | Only below record types are<br>supported:<br>00: Data Record<br>01: End of File Record<br>04: Extended Linear Address<br>Record |

| Data Row          | 16 bytes | Each data row consists 16 bytes.         |                                                                                                                                 |

| Hex<br>Checksum   | 1 byte   | Checksum of HEX file                     | This checksum is calculated using all above bytes.                                                                              |

Table 21 – HEX File Data Format

Host shall skip the data length byte, HEX Checksum and record type byte, and then follow below format to write flash

Table 22 – Host Sends Byte 1~8 to power device

| 1 | 7 | 1 | 1 | 8 | 1 | 8 | 1 | 8 | 1 | 8 | 1 | 8 | 1 | 8 | 1 | 1 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S | Slave<br>Address | W | А | Write<br>program<br>memory<br>Command<br>Code | А | Address<br>mid<br>byte<br>(from<br>HEX<br>file) | А | Address<br>low<br>byte<br>(from<br>HEX<br>file) | А | Data<br>Byte<br>1<br>(from<br>HEX<br>file) | А | <br>Data<br>byte<br>8<br>(from<br>HEX<br>file) | A | Check<br>Sum<br>(Optional) | А | Ρ |  |

|---|------------------|---|---|-----------------------------------------------|---|-------------------------------------------------|---|-------------------------------------------------|---|--------------------------------------------|---|------------------------------------------------|---|----------------------------|---|---|--|

|   |                  |   |   | (OxFB)                                        |   | file)                                           |   | file)                                           |   | file)                                      |   | file)                                          |   |                            |   |   |  |

Table 23 – Host Sends Byte 9~16 to power device

| 1 | 7                | 1 | 1 | 8                                                       | 1 | 8                                               | 1 | 8                                                        | 1 | 8                                          | 1 | 8                                               | 1 | 8                          | 1 | 1 |

|---|------------------|---|---|---------------------------------------------------------|---|-------------------------------------------------|---|----------------------------------------------------------|---|--------------------------------------------|---|-------------------------------------------------|---|----------------------------|---|---|

| S | Slave<br>Address | w | А | Write<br>program<br>memory<br>Command<br>Code<br>(0xFB) | А | Address<br>mid<br>byte<br>(from<br>HEX<br>file) | А | Address<br>low<br>byte <br>0x08<br>(from<br>HEX<br>file) | А | Data<br>Byte<br>9<br>(from<br>HEX<br>file) | A | <br>Data<br>byte<br>16<br>(from<br>HEX<br>file) | A | Check<br>Sum<br>(Optional) | А | Ρ |

Below table (Table 24 – Program Memory (write ROM data) Command) provides the Program Memory (write ROM data) Command,

| Table 24 – Program | Memory | (write ROI | M data) | Command |

|--------------------|--------|------------|---------|---------|

|--------------------|--------|------------|---------|---------|

| Name              | Length  | Description                   | Remark                                                                                                                              |

|-------------------|---------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Address<br>Offset | 2 bytes | 16-bit program memory address | Directly get from HEX file, should<br>add 0x08 to address low byte if<br>send byte 9~16                                             |

| Data              | 8 bytes | 8 bytes of the data           |                                                                                                                                     |

| Checksum          | 1 byte  | Calculated by host            | Arithmetic sum of all bytes<br>received and sent, including<br>slave address and its R/W bit.<br>Note that this field is mandatory. |