# The Open Domain-Specific Architecture (ODSA)

Bapi Vinnakota

Representing an open community in the OCP Broadcom Inc

### Bio

Bapi Vinnakota is a System Architect with Broadcom. After a Ph.D. at Princeton, he taught at the University of Minnesota, where he received an NSF CAREER and IBM Faculty Development Awards.

He joined Intel through an acquisition and was an architect of a VoIP flow processor, worked in networking technology and incubated a networking SaaS product. At Netronome, he created and ran opennfp.org, a service for research in networking.

He leads the Open Domain-Specific Architecture sub-project, in the Open Compute Project. The ODSA has active volunteers from over 30 companies and aims to define an open chiplet marketplace.

#### Overview

- ODSA focus: accelerators and chiplets

- ODSA motivation, charter, community

- Deep dive into the ODSA interface

- How to participate in the ODSA

### **ODSA:** Accelerators and Chiplets

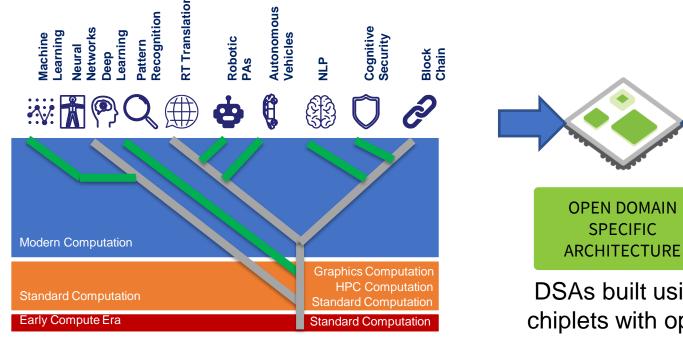

Domain-specific architectures (DSAs) to accelerate targeted computeintensive workloads<sup>1</sup>.

AI/ML/data workload explosion needs DSAs

DSAs built using chiplets with open standard D2D interfaces Chiplet: Die designed to be used with other die in a package, usually with proprietary interfaces<sup>2</sup>.

|                                       | Core Core Core          | MemCntl                          | Core Core Core Core      |  |

|---------------------------------------|-------------------------|----------------------------------|--------------------------|--|

| PCIe                                  | 2<br>10 MB<br>13 Region | S SMP ar                         | 12<br>10 MB<br>13 Region |  |

| Gen4 Signaling (x48)                  | Core Core Core          | SMP and Accelerator Interconnect | Core Core Core           |  |

| aling (x48                            | 12 10 MB<br>13 Region   | or Intercome                     | 10 MB<br>L3 Region       |  |

|                                       | Core Core Core Core     | 2                                | Care Care Care           |  |

| i i i i i i i i i i i i i i i i i i i | 10 MB<br>L3 L3 Region   | MemCntl                          | 12<br>10 MB<br>L3 Region |  |

IBM Power 9: potential modularity

Dharmesh Jani, Facebook – ODSA Workshop Regional Summit, Amsterdam, Sep. 2019

Jeff Stuechli, Josh Friedrich, IBM – ODSA Workshop, IBM, San Jose, Sep. 2019

### Chiplet-Based Products

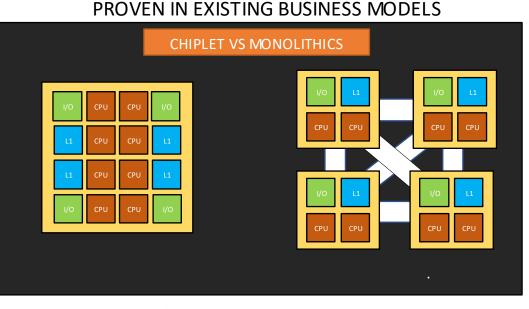

- Heterogeneous integration: modular design across multiple die from multiple process nodes.

- Reduce design, manufacturing cost, choose optimal node for function, near-monolithic performance (ODSA white paper)

- Need an energy-efficient PHY and logical die-to-die interface

- Today: Proprietary D2D interfaces, single-vendor multi-chiplet products

- Tomorrow: An open D2D interface, multi-vendor multi-chiplet products

From Kevin Drucker, Facebook Talk at Broadcom

[L.Su, IEDM'17]

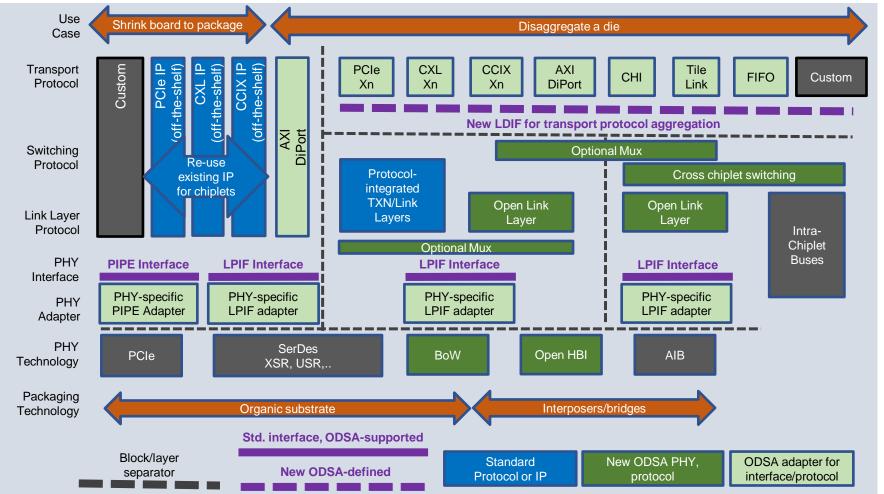

## D2D Interface and Packaging for Chiplets

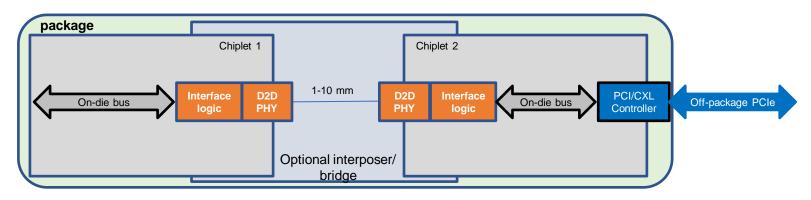

- Die need **PHYsical and logical connectivity** for modular design (ODSA white paper)

- D2D PHYs 10x more energy efficient than off-package protocols, less than on-die buses

- DARPA, Taylor et al (Hot Interconnect, 2019)

- Workflow for multiple chiplets in a package

- Many packaging options<sup>1</sup>: organic laminate, wafer-level fanout, silicon interposer, silicon bridge

- Need to use known good die in a package for acceptable product yield

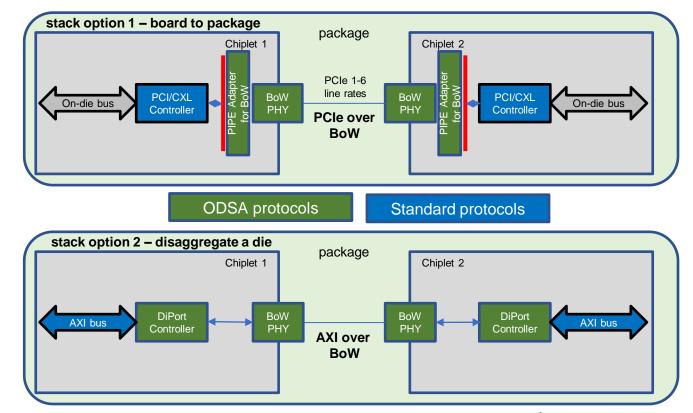

- Use cases drive connectivity and packaging.

- Two use cases (Intel/IBM talks June/Dec ODSA workshops):

- Shrink a board to a package, Disaggregate a die

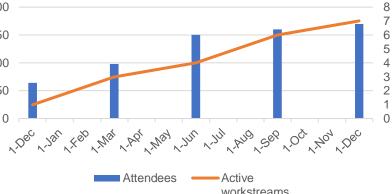

#### Attendees and Participants

Service providers

Attendance and/or participation do not imply corporate endorsement

#### A growing community

DUNDRIES

IME

*K*

Integration

#### **ODSA** workshop attendees

workstreams

### ODSA Work Streams

ODSA meets weekly Fridays, 8 AM Pacific

Each group meets weekly, details at <a href="https://www.opencompute.org/wiki/Server/ODSA">https://www.opencompute.org/wiki/Server/ODSA</a>

| Workstream     | Leader                 | Participants                                  | Objective                  |

|----------------|------------------------|-----------------------------------------------|----------------------------|

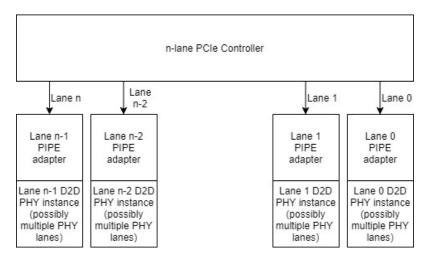

| PHY Layer      | Robert Wang            | EXILINX SYNDPSYS Google                       | PCIe PIPE adapter          |

| Bunch of Wires | Mark Kuemerle          | € XILINX SYNDPSYS ★ KENSIGHT Google<br>SiFive | Scalable low-cost D2D PHY  |

| CDX            | Jawad Nasrullah zGlue  | Thrace Systems cādence SynOPSYS               | Chiplet design exchange    |

| Business       | Sam Fuller             | facebook Aure AyarLabs                        | Chiplet workflowP          |

| PoC hardware   | JP Balachandran        | facebook Achronix                             | PoC board design           |

| PoC software   | Kevin Drucker facebook |                                               | Application/Infra software |

| Link layer     | Open                   |                                               | ODSA Stack                 |

| OpenHBI        | Kenneth Ma             |                                               | High perf D2D PHY          |

Sub-project lead: Bapi Vinnakota

BROADCOM<sup>®</sup>

Attendance and/or participation do not imply corporate endorsement

## ODSA Open D2D Interface Principles

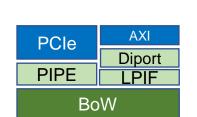

- Layered design: Each layer evolves independently. Aim for <u>at least one</u> <u>fully-open protocol option in each layer</u>.

- Provide multiple options: Low-cost and complex packaging. Enable trade-offs for design cost and software impact. Market chooses best fit.

- Reuse: Leverage existing interfaces for abstraction between layers. <u>Define interface adapters from existing interfaces to open PHYs</u> (AIB, BoW, OpenHBI, XSR)

- Easy adoption: Carry popular protocols over D2D interfaces. PCIe/CXL for board aggregation and AXI/TileLink for SoC disaggregation. <u>Define</u> protocol adapters and enable reuse of off-the-shelf IP

#### ODSA D2D Interface

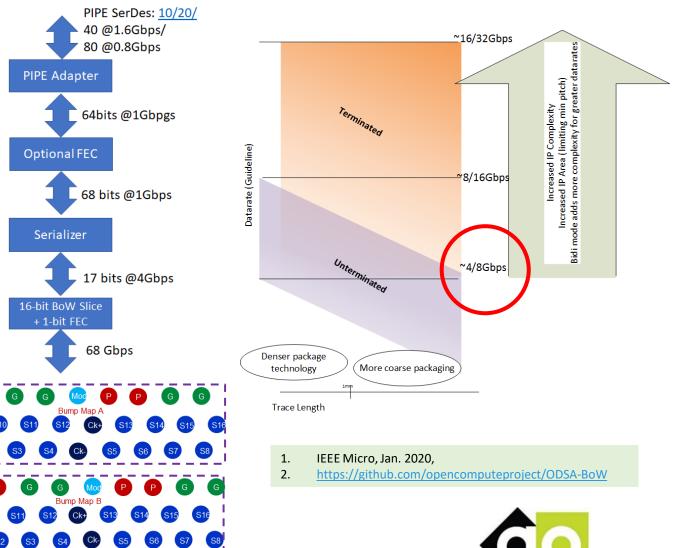

# PHY: Bunch of Wires

Only open D2D PHY to offer graceful tradeoff of performance for complexity

Simple base design – 4-8 Gbps/wire

- Supports process nodes from 3nm to 65nm to enable heterogeneous designs.

- Beachfront bandwidth of 250 Gbps/mm of die edge with regular bumps at 130u spacing and simple laminate packaging

- 0.5 pJ/bit, 10x improvement over off-package PHYs

Increase beachfront density with <sup>1,2</sup>:

- More complex design fast mode doubles bandwidth per lane

- More complex packaging use microbumps at 50u spacing and wafer-level fanout/interposers

- Increase beachfront bandwidth to up to 2 Tbps/mm

To PCIe Link Layer, Controller

Base unit: 16-bit slice

~4xPCle Gen 4 lanes

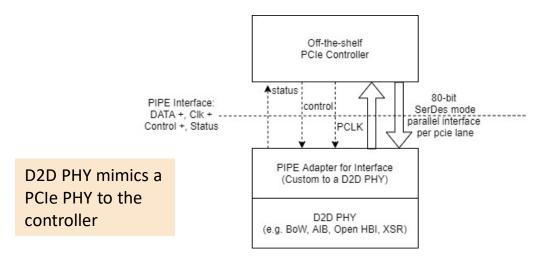

### Logical Transactions: PIPE PCIe, CXL/DiPort AXI

#### PCIe, CXL over D2D interface

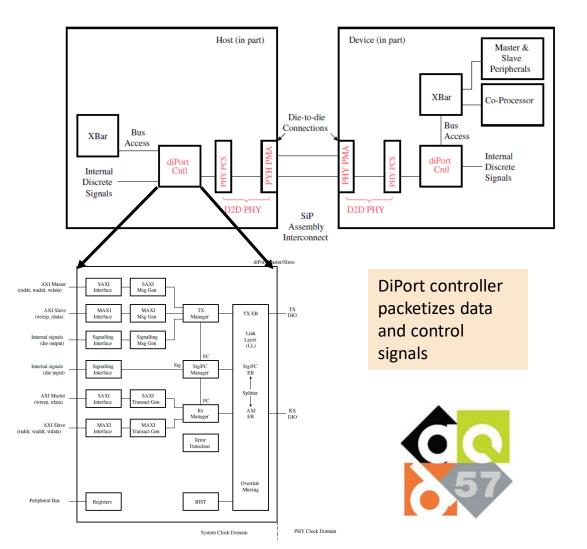

#### DiPort: AXI over D2D interface

# 2020: ODSA PHY/Logic D2D interface

Complete open ODSA logic/PHY interfaces for chiplets for low-cost package.

PCIe/CXL over BoW through standard PIPE interface

• AXI over BoW

<u>Combine the most common system</u> (PCIe/CXL) or SoC protocols (AXI) with new ODSA protocols for chiplets.

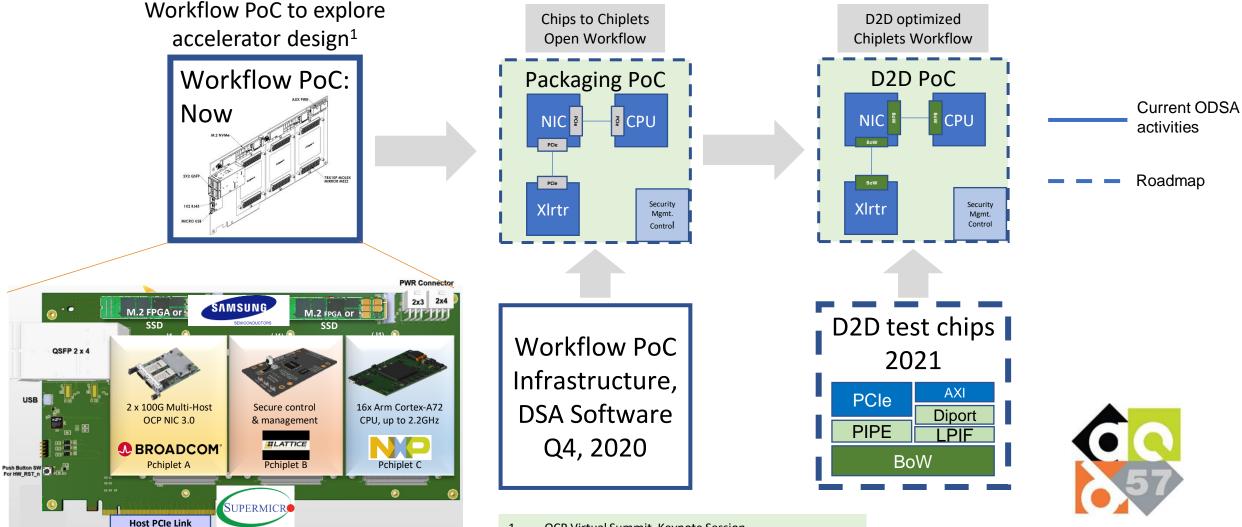

# Proofs of Concept (PoCs) Development Plan

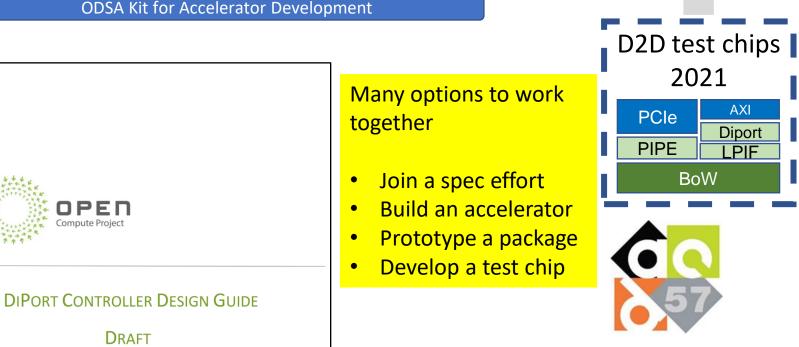

#### **PWR Connector** Please Join Us 2x3 2x4 0 🔿 M.2 FPGA or SSD M.2 FPGA or SSD QSFP 2 x 4 D2D PoC omputeproject/ODSA-BoW \* \* 6 🖸 0 opencomputeproject / ODSA-BoW ⊙ Unwatch = 2 ☆ Star 1 % Fork 6 NIC Sec CPU USB ♦ Code ① Issues 29 ① Pull requests 1 ④ Actions □ Projects 0 □ Wiki ③ Security 0 └ Insights ⑧ Settings 2 x 100G Multi-Host 16x Arm Cortex-A72 Secure control OCP NIC 3.0 & management CPU, up to 2.2GHz Repo for all activity related to the ODSA Bunch of Wires Specification Manage topics *LATTICE* -0- 117 commits P 1 branch 0 package O 1 release 83 5 contributo BROADCOM Create new file Upload files Find file Branch: master - New pull request Pchiplet A Pchiplet B Pchiplet C Push Button SW Xlrtr Security To bapivee Merge pull request #48 from opencomputeproject/revert-44-readme Latest commit 63b6a5b 28 days ago Mgmt. discussions Updated presentation with additional sim 3 months ago Control 0 Revert "Readme" spec 28 days ago README.md Revert "Readme" 28 days ago dsa\_bow\_spec\_0.7.pdf Uploaded BoW spec proposal 0.7 released at AMS 7 months ago Host PCIe Link repo\_bow\_spec\_110619.pdf updating to latest version 7 months ago **ODSA Kit for Accelerator Development** C README.md ODSA-BoW Repo for all activity related to the ODSA Bunch of Wires Specification

#### ODSA D2D PIPE Interface Specification

Chiplet-based designs have recently received a substantial amount of attention. In a chiplet-based product, a design is realized across multiple die integrated into one package. Chiplets require common physical and logical inter-chiplet interfaces to be integrated into one package. Chiplet-based designs use die2die (D2D) PHYs optimized for on-package data transport. D2D PHYs differ from those of both on-die highly parallel buses and off-package SerDes PHYs. Chiplet-based designs also require logical data protocols between the chiplets in a package. Current chiplet-based designs also require logical data protocols between the chiplets are between the chiplets in a package and usually integrate intermally-developed chiplets. With open interfaces, chiplets from multiple vendors can be integrated into one package.

#### The PIPE Interface

D2D technology is still evolving with no one interface being dominant. For example, the Open Domain-Specific Architecture (ODSA) project recently introduced two new open D2D PHYs. An abstraction layer above the PHY will help PHY and logical protocols for the chiplet interface evolve independently. The PIPE interface (latest version 5.2 as of November, 2019) is an abstraction layer between a PCle PHY and the PCle link layer developed by Intel. The interface maps a lane of PCle traffic onto a PCle PHY. The PIPE interface helps verify interoperability between PCle controllers and PCle PHYs (each usually made by different vendors).

This document specifies the PIPE interface for use as an abstraction layer for D2D interfaces in chiplet-based products. The first version of this document specifies how transaction protocols

#### For More Information

- ODSA Wiki: All workshops, weekly calls (open access) with talks from industry experts.

- Specification proposals workstreams meet weekly

- Bunch of Wires GitHub repo (open access)

- <u>PIPE adapter</u>, <u>DiPort</u> (open, but need to request access)

- ODSA PoC Demo (open access), ODSA PoC Implementation Specification (open, but need to request access)

- In-flight

- LPIF, LPIF' proposal

- ODSA PoC SW

- Open HBI specification (needs CLA)

- Technical Papers

- ODSA white paper, ODSA Wiki

- R. Farjadrad, M. Kuemerle, B. Vinnakota, "A Bunch-of-Wires (BoW) Interface for Interchiplet Communication", IEEE Micro, Jan. 2020

- G. Taylor, R. Farjadrad, B. Vinnakota, "High Capacity On-Package Physical Link Considerations", Hot Interconnects, Aug. 2019

- D. Jani, "Musings on Domain Specific Accelerators, Open Compute Project and Cambrian Explosion", LInkedIn

- M. Hutner, R. Sethuram, B. Vinnakota, "Test Challenges in a Chiplet Marketplace", VLSI Test Symposium, Apr. 2020

- B. Vinnakota, "The Open Domain-Specific Architecture: Year in Review", OCP Virtual Summit

- BoW update and ODSA Overview at Hot Interconnect 2020

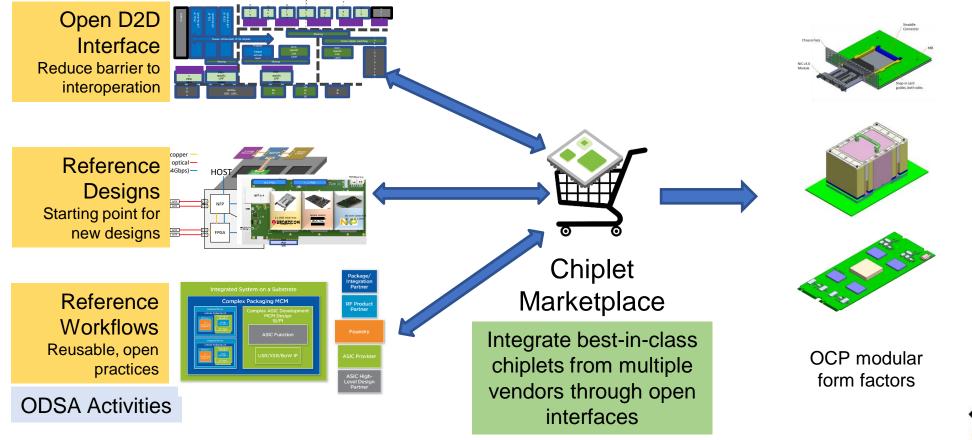

## An Open Chiplet Marketplace

- First open physical and logical interface for chiplets

- Uses abstraction interfaces to allow each layer to evolve independently

- Reusing current open transaction protocols support modular design

- Supports a gradual migration to chiplets, modular design with chiplets

- Two complete PHY/Logical transaction protocol stacks in 2020

- BoW PHY enables the integration of heterogeneous die from multiple vendors