# OCP NIC 3.0 Design Specification

Version <u>0.99</u>0.92

Author: OCP Server Workgroup, OCP NIC subgroup

# **Table of Contents**

| 1 | Overview                                                                                    | 10        |

|---|---------------------------------------------------------------------------------------------|-----------|

|   | 1.1 License                                                                                 | 10        |

|   | 1.2 Acknowledgements                                                                        | 11        |

|   | 1.3 References                                                                              | 12        |

|   | 1.3.1 Trademarks                                                                            | 13        |

|   | 1.4 Acronyms                                                                                | 14        |

|   | 1.5 Background                                                                              | 16        |

|   | 1.6 Overview                                                                                | 18        |

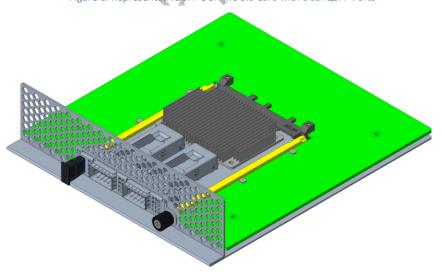

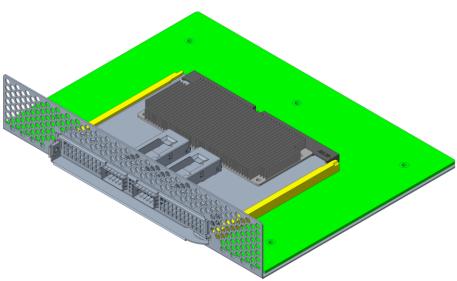

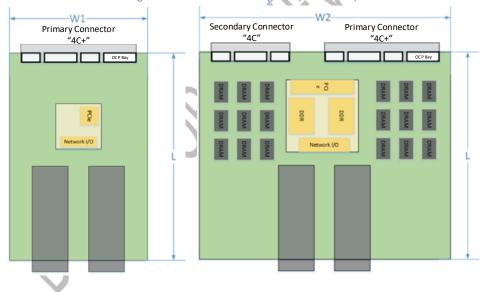

|   | 1.6.1 Mechanical Form Factor Overview                                                       | 18        |

|   | 1.6.2 Electrical Overview                                                                   | 20        |

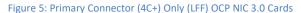

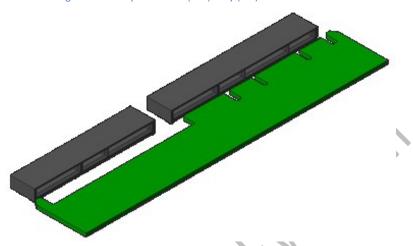

|   | 1.6.2.1 Primary Connector                                                                   | 20        |

|   | 1.6.2.2 Secondary Connector                                                                 | 21        |

|   | 1.7 Non-NIC Use Cases                                                                       | 21        |

| 2 | Mechanical Card Form Factor                                                                 | 22        |

|   | 2.1 Form Factor Options                                                                     | 22        |

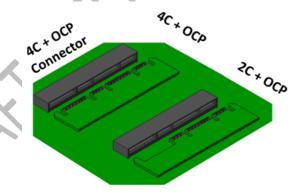

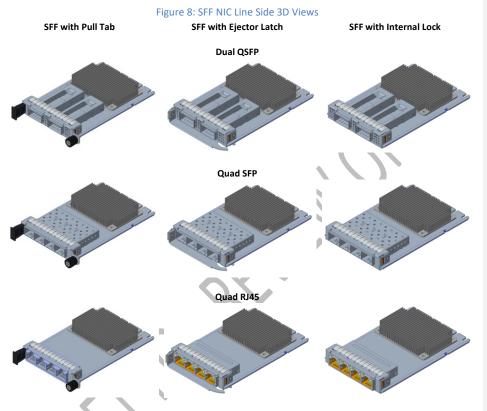

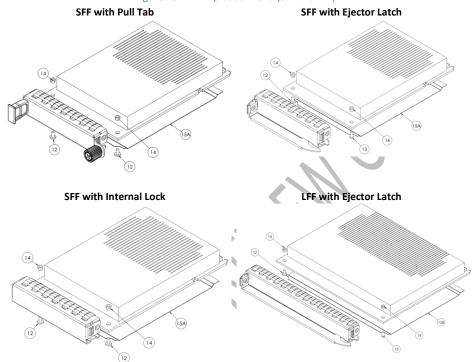

|   | 2.1.1 SFF Faceplate Configurations                                                          |           |

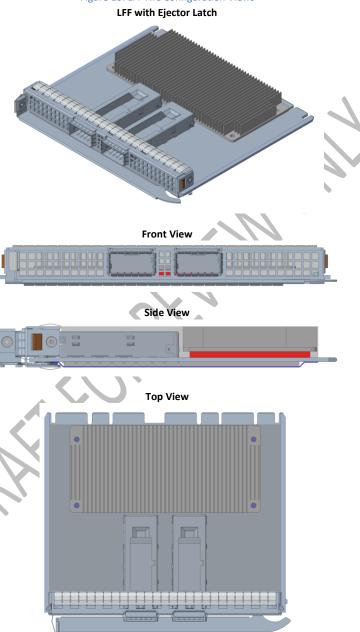

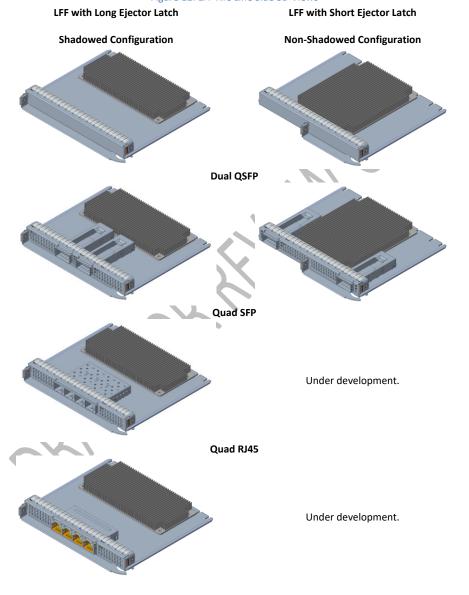

|   | 2.1.2 LFF Faceplate Configurations                                                          | <u>29</u> |

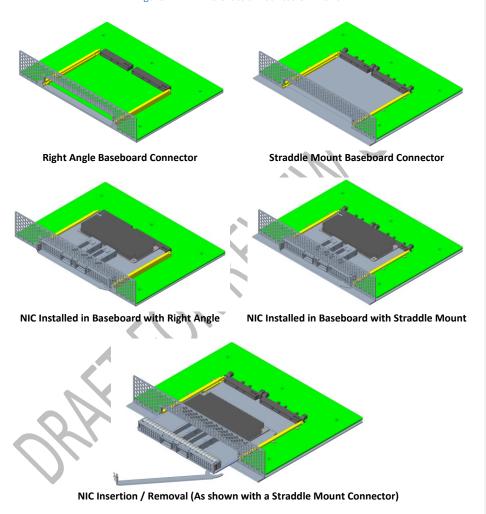

|   | 2.2 Line Side I/O Implementations                                                           | <u>33</u> |

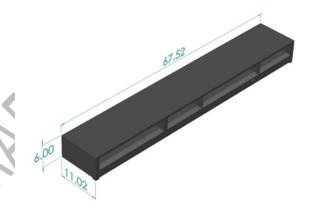

|   | 2.3 Top Level Assembly (SFF and LFF)                                                        | <u>34</u> |

|   | 2.4 Faceplate Subassembly (SFF and LFF)                                                     | <u>35</u> |

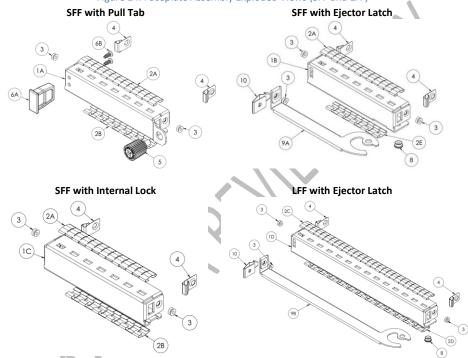

|   | 2.4.1 Faceplate Subassembly – Exploded View                                                 |           |

|   | 2.4.2 Faceplate Subassembly – Bill of Materials (BOM)                                       | <u>35</u> |

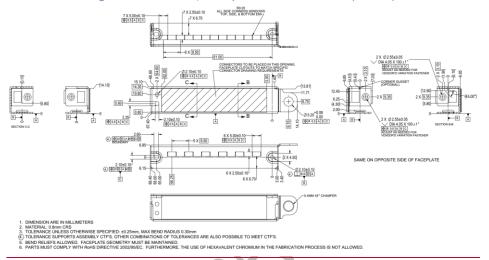

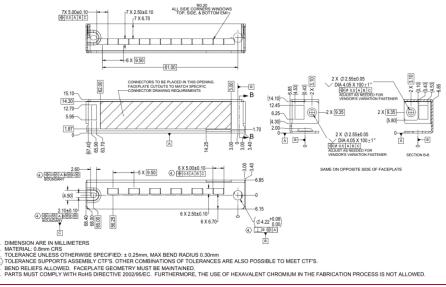

|   | 2.4.3 SFF Generic I/O Faceplate                                                             | <u>38</u> |

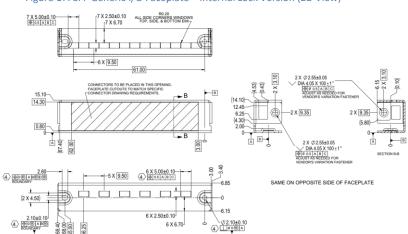

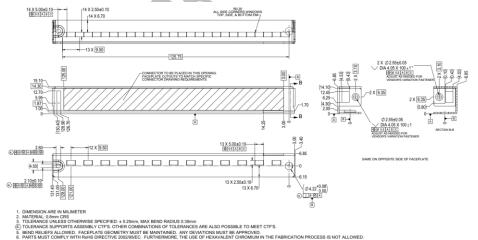

|   | 2.4.4 LFF Generic I/O Faceplate                                                             | <u>40</u> |

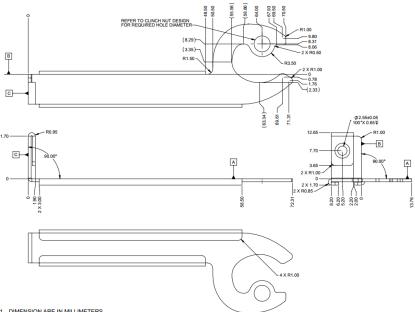

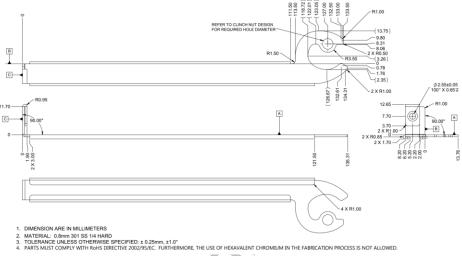

|   | 2.4.5 Ejector Lever (SFF)                                                                   | <u>42</u> |

|   | 2.4.6 Ejector Levers (LFF)                                                                  | <u>43</u> |

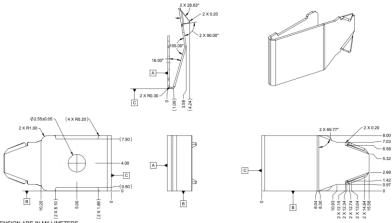

|   | 2.4.7 Ejector Lock (SFF and LFF)                                                            |           |

|   | 2.4.8 Clinch Nut (SFF and LFF)                                                              | <u>45</u> |

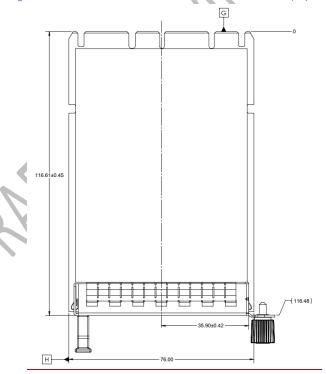

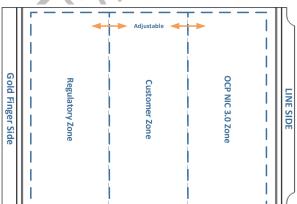

|   | 2.5 Card Keep Out Zones                                                                     |           |

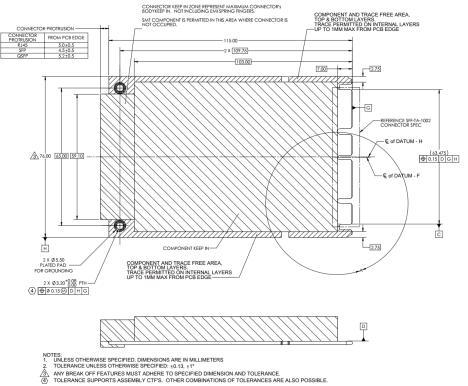

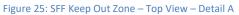

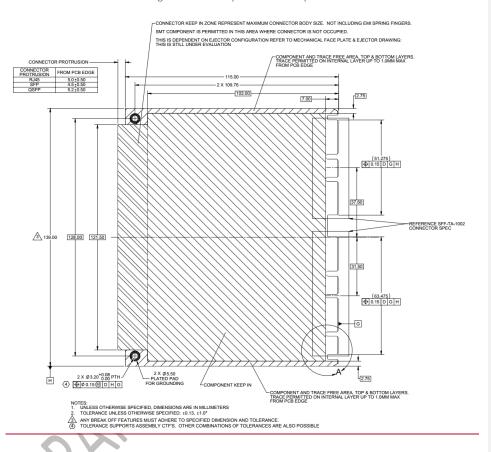

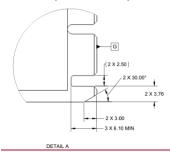

|   | 2.5.1 SFF Keep Out Zones                                                                    |           |

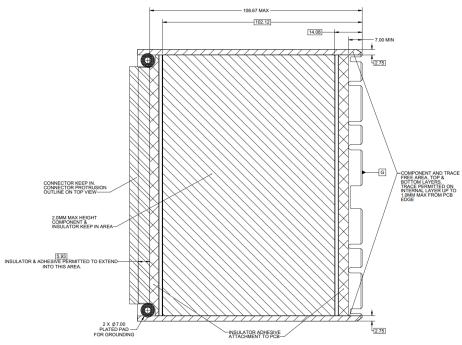

|   | 2.5.2 LFF Keep Out Zones                                                                    |           |

|   | 2.6 Baseboard Keep Out Zones                                                                |           |

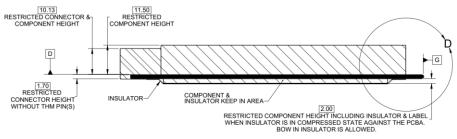

|   | 2.7 Insulation Requirements                                                                 |           |

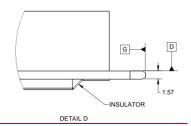

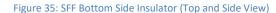

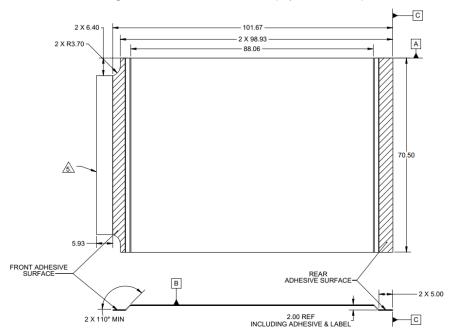

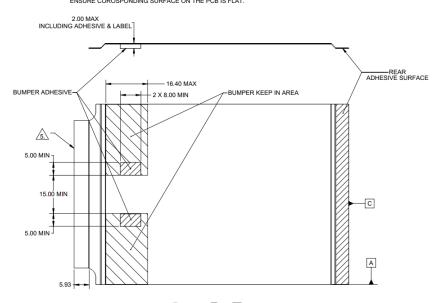

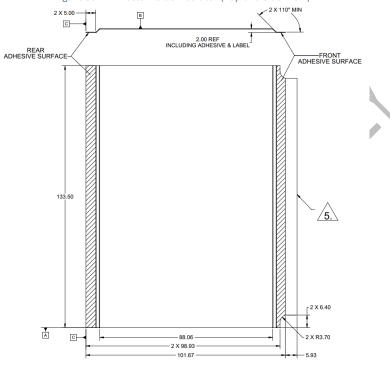

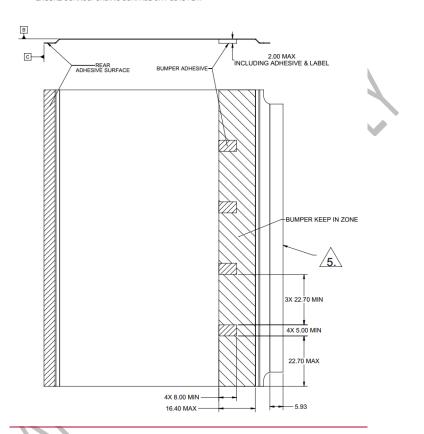

|   | 2.7.1 SFF Insulator                                                                         |           |

|   | 2.7.2 LFF Insulator                                                                         |           |

|   | 2.8 Critical-to-Function (CTF) Dimensions (SFF and LFF)                                     |           |

|   | 2.8.1 CTF Tolerances                                                                        |           |

|   | 2.8.2 SFF Pull Tab CTF Dimensions                                                           | _         |

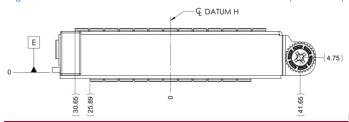

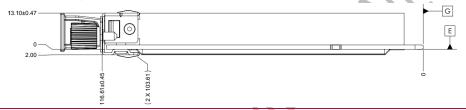

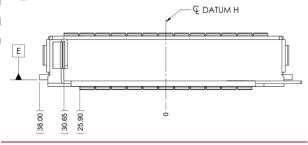

|   | 2.8.3 SFF Ejector Latch CTF Dimensions                                                      | _         |

|   | 2.8.4 SFF Internal Lock CTF Dimensions                                                      | _         |

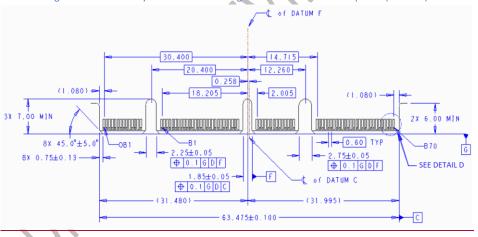

|   | 2.8.5 SFF Baseboard CTF Dimensions                                                          | _         |

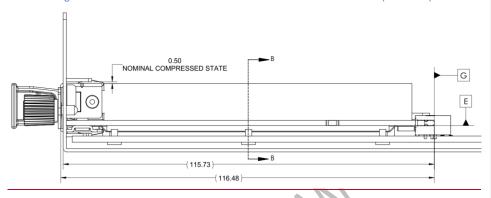

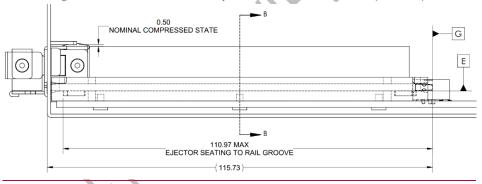

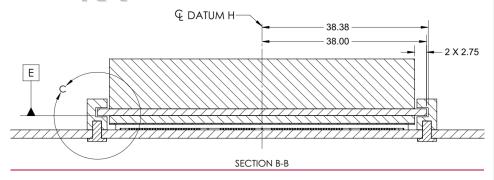

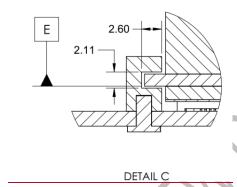

|   | 2.8.6 LFF Ejector Latch CTF Dimensions                                                      | _         |

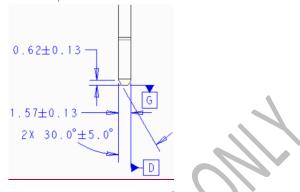

|   | 2.8.7 LFF Baseboard CTF Dimensions                                                          |           |

|   | 2.9 Labeling Requirements                                                                   |           |

|   | 2.9.1 General Guidelines for Label Contents                                                 |           |

|   | 2.9.2 MAC Address Labeling Requirements                                                     |           |

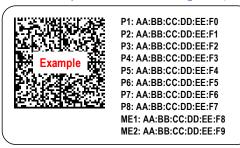

|   | 2.9.2.1 MAC Address Label Example 1 – Quad Port with Single Host, Single Managed Controller |           |

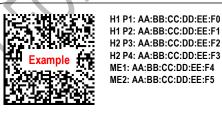

|   |                                                                                             |           |

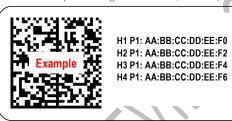

|   | 2.9.2.3 MAC Address Label Example 3 – Quad Port with Dual Hosts, Dual Managed Controllers   |           |

|   | 2.9.2.4 MAC Address Label Example 4 – Singe Port with Quad Host, Single Managed Controller  |           |

| 3 | 2.10 Mechanical CAD Package Examples                                                        |           |

| 3 |                                                                                             |           |

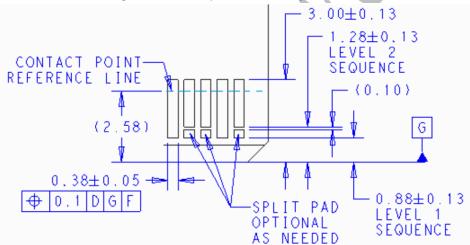

|   | 3.1 Card Edge Gold Finger Requirements                                                      |           |

|   | 3.1.1 Gold Finger Mating Sequence                                                           |           |

|   | 3.2.1 Right Angle Connector                                                                 |           |

|   | 3.2.1 Right Angle Offset                                                                    |           |

|   |                                                                                             |           |

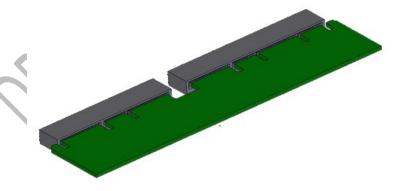

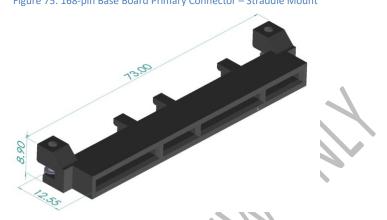

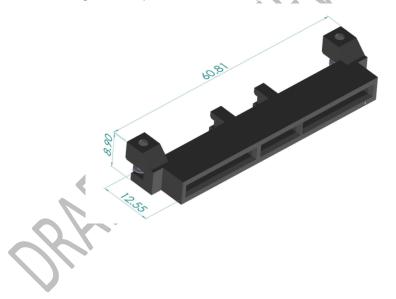

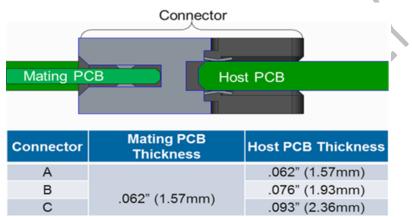

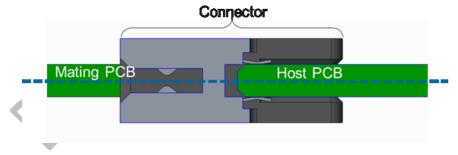

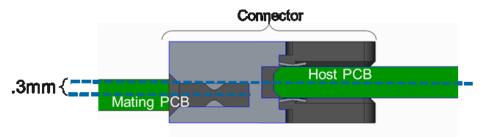

| 3.2  | 2.3   | Straddle Mount Connector                                                             | <u>116</u> |

|------|-------|--------------------------------------------------------------------------------------|------------|

| 3.2  | 2.4   | Straddle Mount Offset and PCB Thickness Options                                      | 118        |

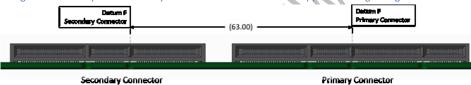

| 3.2  | 2.5   | LFF Connector Locations                                                              | 119        |

| 3.3  | Pin D | Definition                                                                           | 119        |

| 3.3  |       | Primary Connector                                                                    |            |

| 3.3  |       | Secondary Connector                                                                  |            |

| 3.4  |       | al Descriptions                                                                      |            |

| 3.4  | _     | PCIe Interface Pins                                                                  |            |

| 3.4  |       | PCIe Present and Bifurcation Control Pins                                            |            |

|      |       |                                                                                      |            |

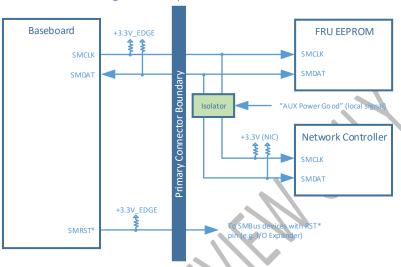

| 3.4  |       | SMBus Interface Pins                                                                 |            |

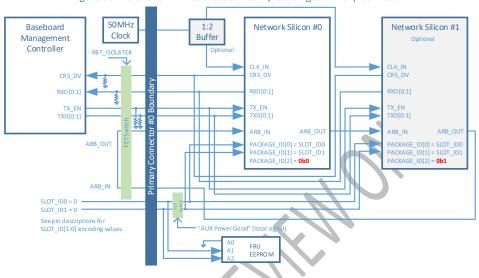

| 3.4  |       | NC-SI over RBT Interface Pins                                                        |            |

| 3.4  |       | Scan Chain Pins                                                                      |            |

| 3.4  |       | Power Supply Pins                                                                    |            |

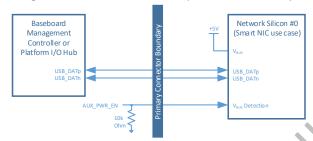

| 3.4  |       | USB 2.0 (A68/A69) – Primary Connector Only                                           |            |

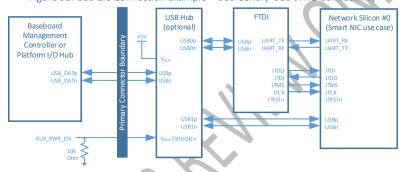

| 3.4  |       | UART (A68/A69) – Secondary Connector Only                                            |            |

| 3.4  |       | RFU[1:4] Pins                                                                        | <u>158</u> |

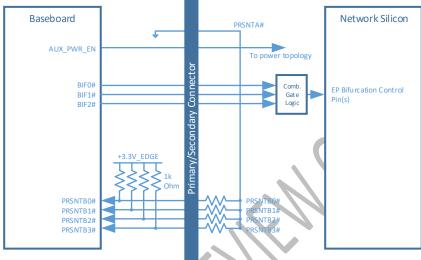

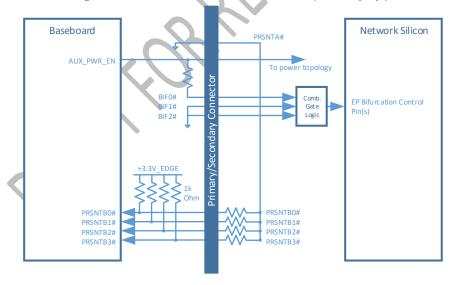

| 3.5  | PCle  | Bifurcation Mechanism                                                                | <u>159</u> |

| 3.5  | 5.1   | PCIe OCP NIC 3.0 Card to Baseboard Bifurcation Configuration (PRSNTA#, PRSNTB[3:0]#) | 159        |

| 3.5  | 5.2   | PCIe Baseboard to OCP NIC 3.0 Card Bifurcation Configuration (BIF[2:0]#)             | 159        |

| 3.5  | 5.3   | PCle Bifurcation Decoder                                                             | 160        |

| 3.5  | 5.4   | Bifurcation Detection Flow                                                           | 162        |

| 3.5  |       | PCle Bifurcation Examples                                                            |            |

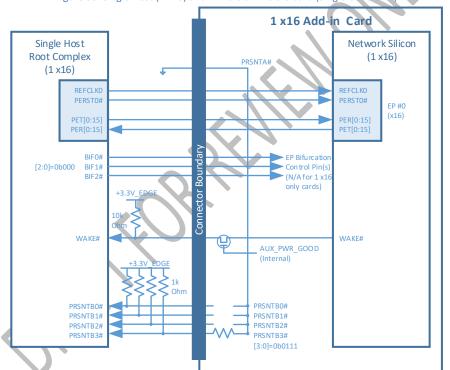

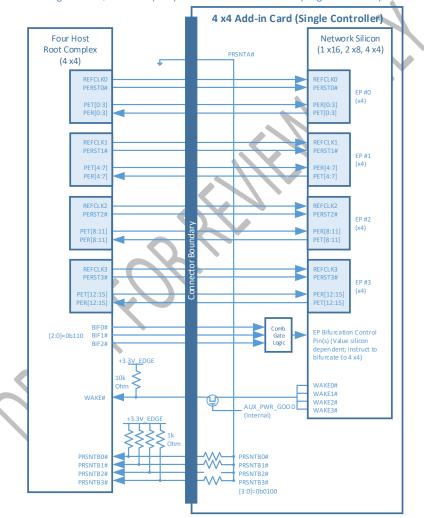

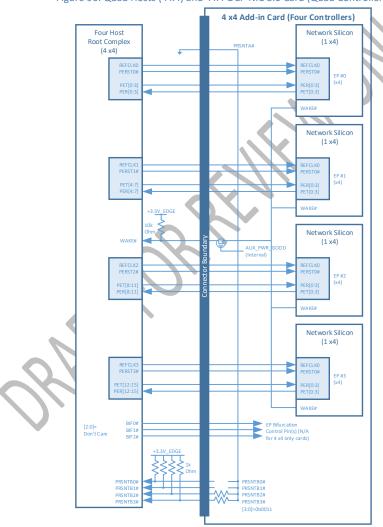

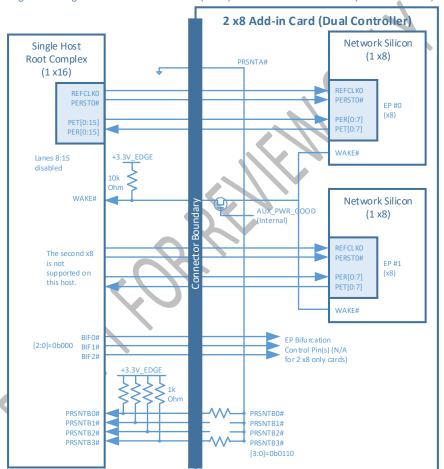

| 0.0  | 3.5.5 |                                                                                      |            |

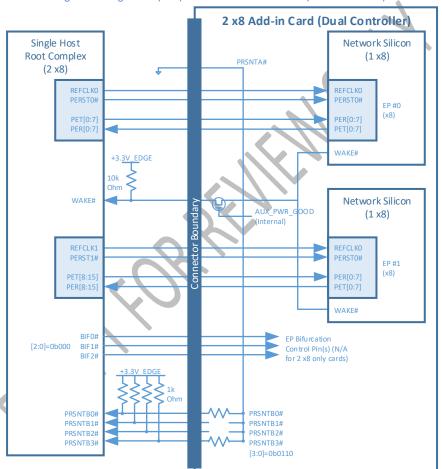

|      | 3.5.5 |                                                                                      |            |

|      | 3.5.5 |                                                                                      |            |

|      | 3.5.5 |                                                                                      |            |

|      | 3.5.5 |                                                                                      |            |

| 2.6  |       |                                                                                      |            |

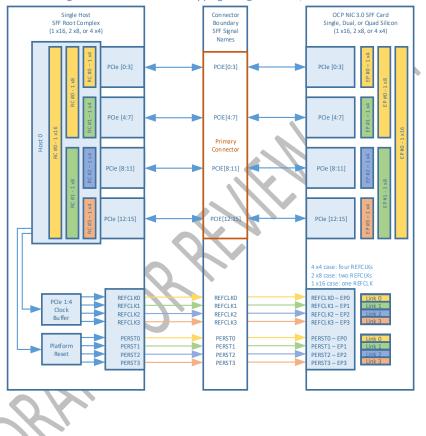

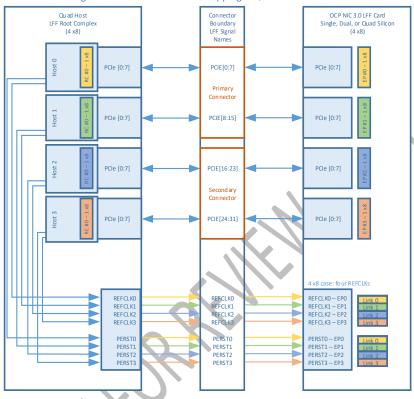

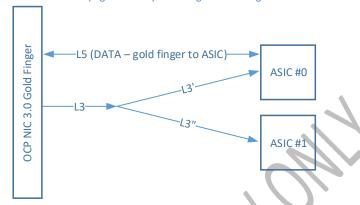

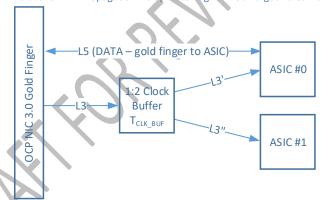

| 3.6  |       | REFCLK and PERST# Mapping                                                            | 168        |

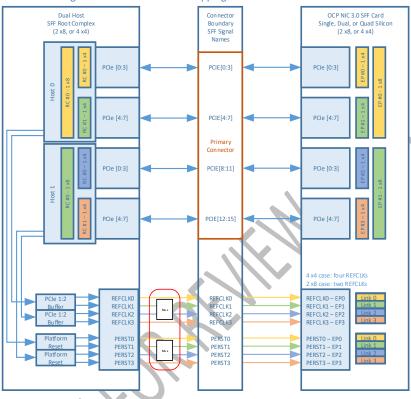

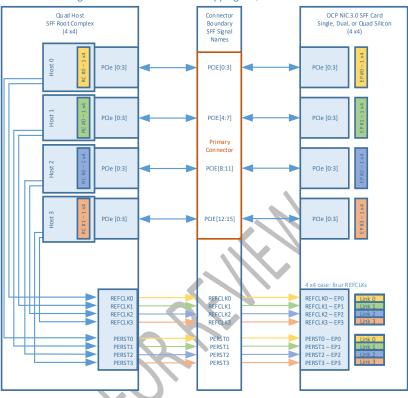

| 3.6  |       | SFF PCIe REFCLK and PERST# Mapping                                                   |            |

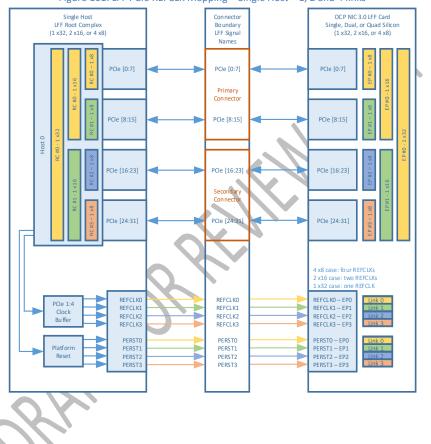

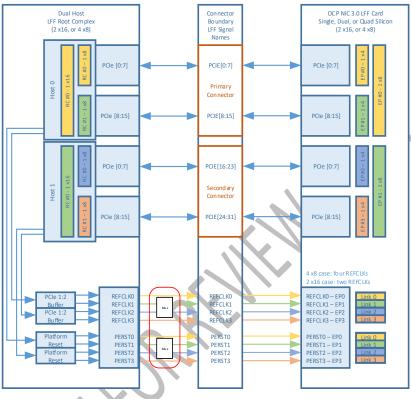

| 3.6  |       | LFF PCIe REFCLK and PERST# Mapping                                                   |            |

| 3.6  |       | REFCLK and PERST# Mapping Expansion                                                  |            |

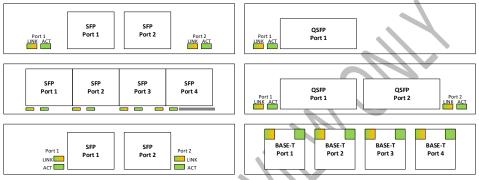

| 3.7  |       | Numbering and LED Implementations                                                    |            |

| 3.7  |       | OCP NIC 3.0 Port Naming and Port Numbering                                           |            |

| 3.7  |       | OCP NIC 3.0 Card LED Configuration                                                   |            |

| 3.7  | 7.3   | OCP NIC 3.0 Card LED Ordering                                                        |            |

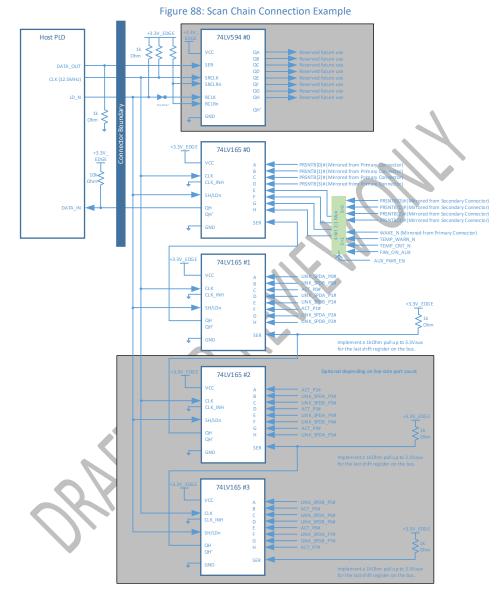

| 3.7  | 7.4   | Baseboard LEDs Configuration over the Scan Chain                                     | <u>178</u> |

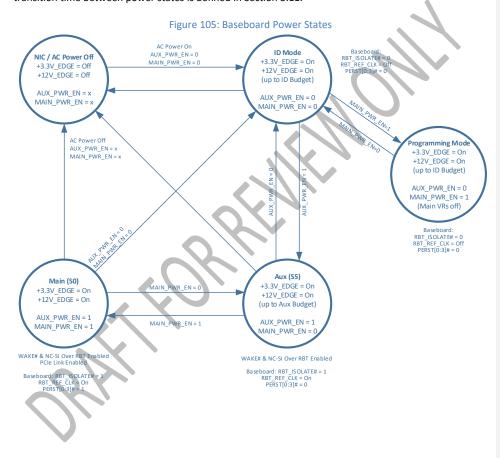

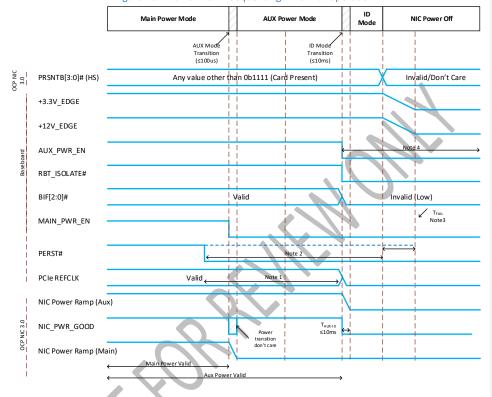

| 3.8  | Powe  | er State Machine                                                                     | <u>179</u> |

| 3.8  | 3.1   | NIC Power Off                                                                        | 180        |

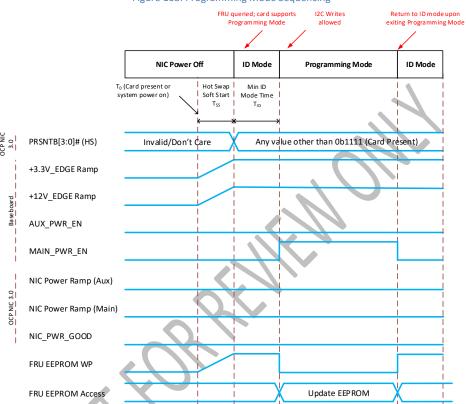

| 3.8  | 3.2   | ID Mode                                                                              | 180        |

| 3.8  | 3.3   | Aux Power Mode (S5)                                                                  | 180        |

| 3.8  | 3.4   | Main Power Mode (S0)                                                                 | 181        |

| 3.8  | 3.5   | Programming Mode                                                                     |            |

| 3.9  |       | er Supply Rail Requirements and Slot Power Envelopes                                 |            |

| 3.10 |       | Swap Considerations for +12V EDGE and +3.3V EDGE Rails                               |            |

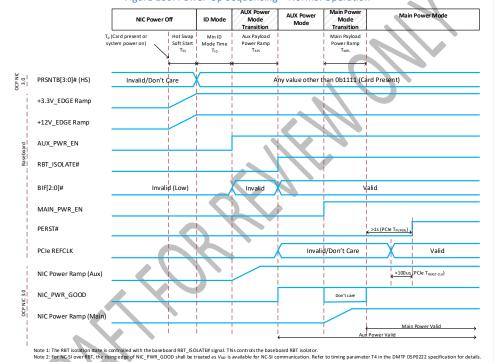

| 3.11 |       | er Sequence Timing Requirements                                                      |            |

| 3.12 |       | al I/O Specifications                                                                |            |

|      |       | t and Pre-OS Requirements                                                            |            |

| 4.1  |       | pand Management Interface and Transport                                              |            |

|      |       |                                                                                      |            |

| 4.2  |       | Traffic                                                                              |            |

| 4.3  |       | agement Controller (MC) MAC Address Provisioning                                     |            |

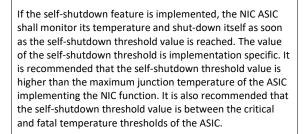

| 4.4  |       | Die Temperature Reporting                                                            |            |

| 4.5  |       | er Consumption Reporting                                                             |            |

| 4.6  |       | gable Transceiver Module Status and Temperature Reporting                            |            |

| 4.7  |       | agement and Pre-OS Firmware Inventory and Update                                     |            |

| 4.7  |       | Secure Firmware                                                                      |            |

| 4.7  | 7.2   | Firmware Inventory                                                                   |            |

| 4.7  | 7.3   | Firmware Inventory and Update in Multi-Host Environments                             | <u>196</u> |

| 4.8  | NC-S  | I Package Addressing and Hardware Arbitration Requirements                           | <u>197</u> |

|      |       |                                                                                      |            |

|   | 4.8.1      | NC-SI over RBT Package Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u>197</u> |

|---|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

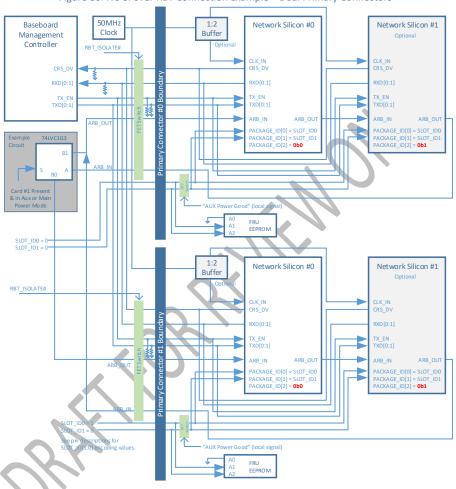

|   | 4.8.2      | Arbitration Ring Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u>197</u> |

|   | 4.9 SMB    | us 2.0 Addressing Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 197        |

|   | 4.9.1      | SMBus Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 198        |

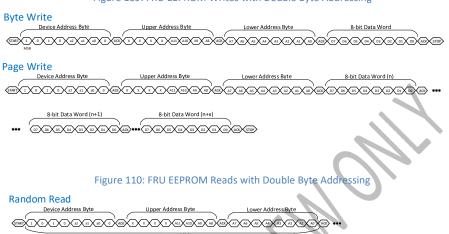

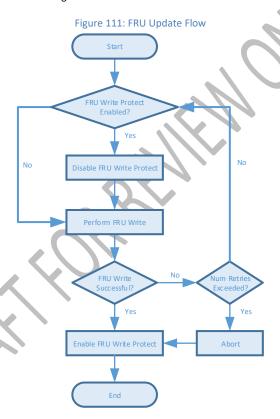

|   | 4.10 FRU I | EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|   | 4.10.1     | FRU EEPROM Addressing and Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 198        |

|   | 4.10.2     | FRU EEPROM Write Protection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _          |

|   | 4.10.3     | FRU EEPROM Content Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _          |

|   | 4.10.4     | FRU Template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _          |

| 5 |            | lelines and Signal Integrity Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _          |

| , |            | l over RBT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |

|   | 5.1.1      | SFF Baseboard Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _          |

|   | 5.1.1      | LFF Baseboard Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _          |

|   | 5.1.2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _          |

|   |            | SFF OCP NIC 3.0 Card Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |            |

|   | 5.1.4      | LFF OCP NIC 3.0 Card Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _          |

|   |            | us 2.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |            |

|   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _          |

|   | 5.3.1      | Channel Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |

|   | 5.3.1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   | 5.3.1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   | 5.3.1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   | 5.3.1      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

|   | 5.3.1      | and the second of the second o |            |

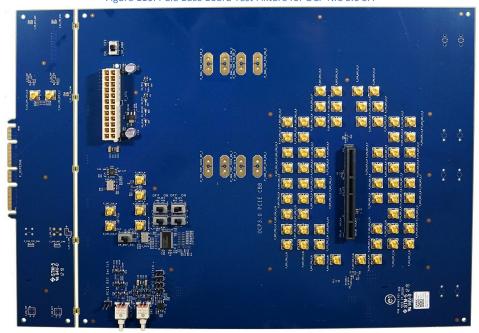

|   | 5.3.2      | Test Fixtures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

|   | 5.3.2      | .1 Compliance Load Board (CLB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <u>213</u> |

|   | 5.3.2      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <u>214</u> |

|   | 5.3.3      | Test Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |

|   | 5.3.3      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |

| 6 |            | Environmental                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |            |

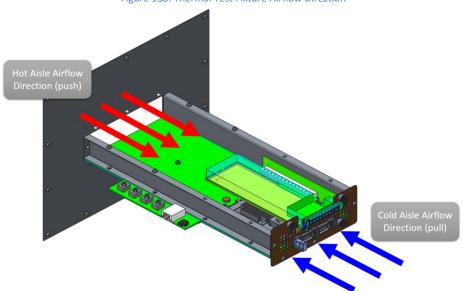

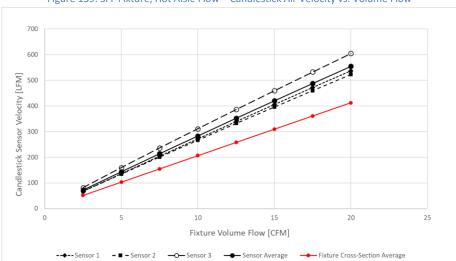

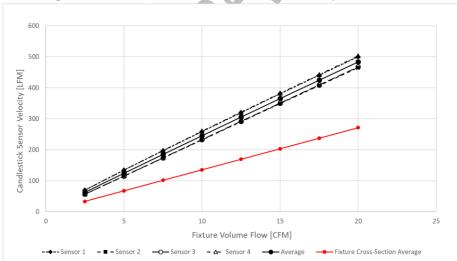

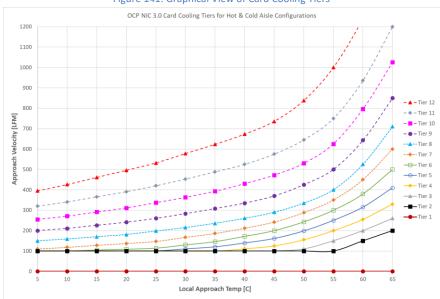

|   |            | ow Direction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <u>215</u> |