# OCP NIC 3.0 Design Specification

Version <u>0.57</u>

1

Author: OCP Server Workgroup, OCP NIC subgroup

# **Table of Contents**

| 1 | Overview         |                                                                     | 8  |

|---|------------------|---------------------------------------------------------------------|----|

|   | 1.1 Lice         | nse                                                                 | 8  |

|   | 1.2 Back         | kground                                                             | 9  |

|   | 1.3 Ack          | nowledgements                                                       | 11 |

|   | 1.4 Ove          | rview                                                               | 12 |

|   | 1.4.1            | Mechanical Form factor overview                                     |    |

|   | 1.4.2            | Electrical overview                                                 | 14 |

|   | 1.5 Refe         | erences                                                             | 16 |

| 2 | <b>Card Form</b> | Factor                                                              | 17 |

|   | 2.1 Form         | n Factor Options                                                    | 17 |

|   | 2.2 1/0          | bracket                                                             | 20 |

|   | 2.2.1            | Small Form Factor Add-in Card I/O Bracket                           | 20 |

|   | 2.2.2            | Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions | 21 |

|   | 2.2.3            | Small Form Factor Baseboard Critical-to-Function (CTF) Dimensions   | 22 |

|   | 2.2.4            | Large Form Factor Add-in Card I/O Bracket                           | 24 |

|   | 2.2.5            | Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions | 25 |

|   | 2.2.6            | Large Form Factor Baseboard Critical-to-Function (CTF) Dimensions   | 26 |

|   | 2.3 Line         | Side I/O Implementations                                            | 27 |

|   | 2.4 LED          | Implementations                                                     | 27 |

|   | 2.4.1            | Add-in Card LED Configuration                                       | 27 |

|   | 2.4.2            | Add-in Card LED Ordering                                            |    |

|   | 2.4.3            | Baseboard LEDs Configuration Over the Scan Chain                    | 29 |

|   | 2.5 Med          | chanical Keepout Zones                                              |    |

|   | 2.5.1            | Baseboard Keep Out Zones – Small Card Form Factor                   | 30 |

|   | 2.5.2            | Baseboard Keep Out Zones – Large Card Form Factor                   |    |

|   | 2.5.3            | Small Card Form Factor Keep Out Zones                               |    |

|   | 2.5.4            | Large Card Form Factor Keep Out Zones                               |    |

|   | 2.6 Insu         | lation Requirements                                                 |    |

|   | 2.6.1            | Small Card Insulator                                                |    |

|   | 2.6.2            | Large Card Insulator                                                |    |

|   |                  | eling Requirements                                                  |    |

|   |                  | Implementation Examples                                             |    |

|   |                  | -NIC Use Cases                                                      |    |

|   | 2.9.1            | PCIe Retimer card                                                   |    |

|   | 2.9.2            | Accelerator card                                                    |    |

|   | 2.9.3            | Storage HBA / RAID card                                             |    |

| 3 |                  | and Baseboard Connector Interface                                   |    |

|   |                  | d Finger Requirements                                               |    |

|   | 3.1.1            | Gold Finger Mating Sequence                                         |    |

|   |                  | eboard Connector Requirements                                       |    |

|   | 3.2.1            | Right Angle Connector                                               |    |

|   | 3.2.2            | Right Angle Offset                                                  |    |

|   | 3.2.3            | Straddle Mount Connector                                            |    |

|   | 3.2.4            | Straddle Mount Offset and PCB Thickness Options                     |    |

|   | 3.2.5            | Large Card Connector Locations                                      | 44 |

|                                                                                | Rev <u>0.57<del>0.56</del></u> |

|--------------------------------------------------------------------------------|--------------------------------|

| 3.3 Pin definition                                                             | 44                             |

| 3.4 Signal Descriptions – Common                                               | 48                             |

| 3.4.1 PCIe Interface Pins                                                      | 48                             |

| 3.4.2 PCIe Present and Bifurcation Control Pins                                | 51                             |

| 3.4.3 SMBus Interface Pins                                                     |                                |

| 3.4.4 Power Supply Pins                                                        | 54                             |

| 3.4.5 Miscellaneous Pins                                                       |                                |

| 3.5 Signal Descriptions – OCP Bay (Primary Connector)                          | 56                             |

| 3.5.1 PCIe Interface Pins – OCP Bay (Primary Connector)                        | 56                             |

| 3.5.2 NC-SI Over RBT Interface Pins – OCP Bay (Primary Connector)              |                                |

| 3.5.3 Scan Chain Pins – OCP Bay (Primary Connector)                            |                                |

| 3.5.4 Primary Connector Miscellaneous Pins – OCP Bay (Primary Connector)       |                                |

| 3.6 PCIe Bifurcation Mechanism                                                 |                                |

| 3.6.1 PCIe Add-in Card to Baseboard Bifurcation Configuration (PRSNTA#, PRSNTE |                                |

| 3.6.2 PCIe Baseboard to Add-in Card Bifurcation Configuration (BIF[2:0]#)      |                                |

| 3.6.3 PCIe Bifurcation Decoder                                                 |                                |

| 3.6.4 Bifurcation Detection Flow                                               |                                |

| 3.6.5 PCIe Bifurcation Examples                                                |                                |

| 3.7 PCIe Clocking Topology                                                     |                                |

| 3.8 PCIe Bifurcation Results and REFCLK Mapping                                |                                |

| 3.9 Power Capacity and Power Delivery                                          |                                |

| 3.9.1 NIC Power Off                                                            |                                |

| 3.9.2 ID Mode                                                                  |                                |

| 3.9.3 Aux Power Mode (S5)                                                      |                                |

| 3.9.4 Main Power Mode (S0)                                                     |                                |

| 3.10 Power Supply Rail Requirements and Slot Power Envelopes                   |                                |

| 3.11 Hot Swap Considerations for 12V and 3.3V Rails                            |                                |

| 3.12 Power Sequence Timing Requirements                                        |                                |

| Management                                                                     |                                |

| 4.1 Sideband Management Interface and Transport                                |                                |

| 4.2 NC-SI Traffic                                                              |                                |

|                                                                                |                                |

| 4.3 Management Controller (MC) MAC Address Provisioning                        |                                |

| 4.4 Temperature Reporting                                                      |                                |

| 4.5 Power Consumption Reporting                                                |                                |

| 4.6 Pluggable Module Status Reporting                                          |                                |

| 4.7 Firmware Inventory and Update                                              |                                |

| 4.7.1 Secure Firmware                                                          |                                |

| 4.7.2 Firmware Inventory                                                       |                                |

| 4.7.3 Firmware Inventory and Update in Multi-Host Environments                 |                                |

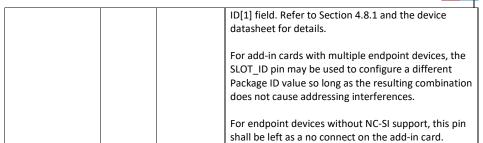

| 4.8 NC-SI Package Addressing and Hardware Arbitration Requirements             |                                |

| 4.8.1 NC-SI over RBT Package Addressing                                        |                                |

| 4.8.2 Arbitration Ring Connections                                             |                                |

| 4.9 SMBus 2.0 Addressing Requirements                                          |                                |

| 4.9.1 SMBus Address Map                                                        |                                |

| 4.10 FRU EEPROM                                                                |                                |

| 4.10.1 FRU EEPROM Address, Size and Availability                               |                                |

| 4.10.2 FRU EEPROM Content Requirements                                         |                                |

| Data Network Requirements                                                      | <u>100</u> 102                 |

5

|   | 5.1              | Network Boot                                      | 100 <del>102</del>        |

|---|------------------|---------------------------------------------------|---------------------------|

| 6 |                  | ng Guidelines and Signal Integrity Considerations |                           |

|   | 6.1              | NC-SI Over RBT                                    | 101 <del>103</del>        |

|   | 6.2              | PCIe                                              | <u>101</u> <del>103</del> |

| 7 | Therr            | nal and Environmental                             | <u>102</u> 104            |

|   | 7.1              | Environmental Requirements                        | <u>102</u> 104            |

|   |                  | 1.1 Thermal Simulation Boundary Example           |                           |

|   |                  | Shock & Vibration                                 |                           |

|   | <mark>7.3</mark> | Regulatory                                        | <u>102</u> 104            |

| 8 | Revis            | ion History                                       | 104106                    |

|   |                  |                                                   |                           |

Rev <u>0.570.5</u>

# List of Figures

| Figure 1: Representative Small OCP NIC 3.0 Card with Quad SFP Ports                                         | 9  |

|-------------------------------------------------------------------------------------------------------------|----|

| Figure 2: Representative Large OCP NIC 3.0 Card with Dual QSFP Ports and on-board DRAM                      | 10 |

| Figure 3: Small and Large Card Form-Factors (not to scale)                                                  | 12 |

| Figure 4: Example Small Card Form Factor                                                                    | 17 |

| Figure 5: Example Large Card Form Factor                                                                    | 18 |

| Figure 6: Primary Connector (4C + OCP Bay) and Secondary Connector (4C) (Large) Add-in Cards                | 18 |

| Figure 7: Primary Connector (4C + OCP Bay) Only (Large) Add-in Cards                                        | 18 |

| Figure 8: Primary Connector (4C + OCP Bay) with 4C and 2C (Small) Add-in Cards                              | 19 |

| Figure 9: Small Card Standard I/O Bracket                                                                   | 20 |

| Figure 10: Small Card Customized bracket for RJ-45 Connector                                                | 20 |

| Figure 11: Small Card 3D Bracket Assembly (Standalone)                                                      | 20 |

| Figure 12: Small Card 3D Bracket Assembly (Installed on Add-in Card)                                        | 20 |

| Figure 13: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Top View)                   | 21 |

| Figure 14: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Front View)                 | 21 |

| Figure 15: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Left) Left)     | 22 |

| Figure 16: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Right)          | 22 |

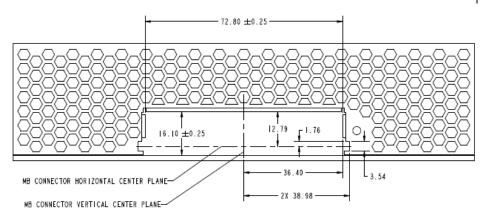

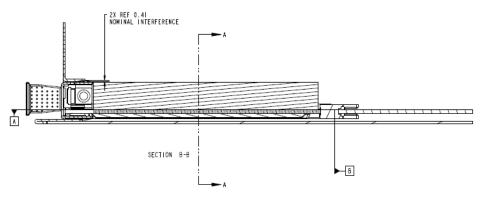

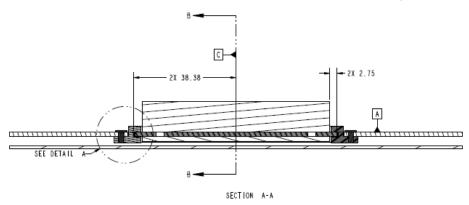

| Figure 17: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear View)            | 22 |

| Figure 18: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Side View)            | 23 |

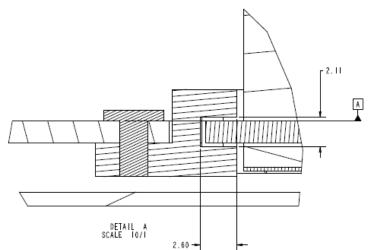

| Figure 19: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear Rail Guide View) | 23 |

| Figure 20: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rail Guide Detail)    |    |

| Figure 21: Baseboard and Rail Assembly Drawing for Small Cards                                              | 24 |

| Figure 22: Large Card Standard I/O Bracket                                                                  | 25 |

| Figure 23: Large Card Customized bracket for RJ-45 Connector                                                |    |

| Figure 24: Large Card 3D Bracket Assembly (Standalone)                                                      | 25 |

| Figure 25: Large Card 3D Bracket Assembly (Installed on Add-in Card)                                        | 25 |

| Figure 26: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Top View)                   | 25 |

| Figure 27: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Front View)                 | 25 |

| Figure 28: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Left) Left)     | 26 |

| Figure 29: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Right) Right    | 26 |

| Figure 30: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear View)            | 26 |

| Figure 31: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Side View)            | 26 |

| Figure 32: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear Rail Guide View) | 26 |

| Figure 33: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rail Guide Detail)    | 26 |

| Figure 34: Baseboard and Rail Assembly Drawing for Large Card                                               |    |

| Figure 35: LED Ordering – Example Small Card Link/Activity and Speed LED Placement                          | 28 |

| Figure 36: Small Form Factor Keep Out Zone – Top View                                                       | 30 |

| Figure 37: Small Form Factor Keep Out Zone – Bottom View                                                    | 31 |

| Figure 38: Small Form Factor Keep Out Zone – Side View                                                      | 31 |

| Figure 39: Large Form Factor Keep Out Zone – Top View                                                       |    |

| Figure 40: Large Form Factor Keep Out Zone – Bottom View                                                    |    |

| Figure 41: Large Form Factor Keep Out Zone – Side View                                                      | 33 |

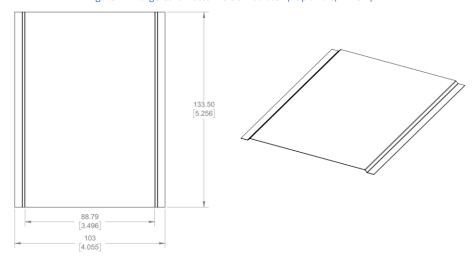

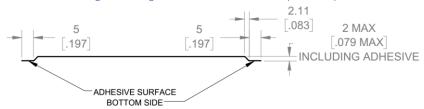

| Figure 42: Small Card Bottom Side Insulator (Top and 3/4 View)                                              | 34 |

| Figure 43: Small Card Bottom Side Insulator (Side View)                                                     | 34 |

| Figure 44: Large Card Bottom Side Insulator (Top and 3/4 View)                                              |    |

| Figure 45: Large Card Bottom Side Insulator (Side View)                                                     |    |

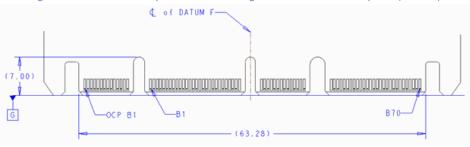

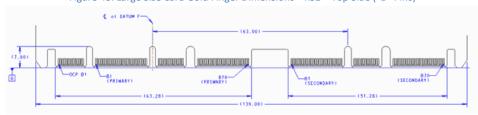

| Figure 46: Small Size Primary Connector Gold Finger Dimensions – x16 – Top Side ("B" Pins)                  |    |

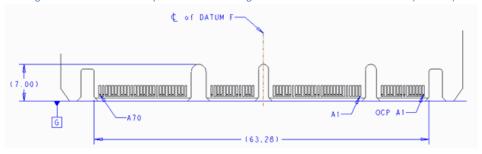

| Figure 47: Small Size Primary Connector Gold Finger Dimensions – x16 – Bottom Side ("A" Pins)               |    |

| Figure 48: Large Size Card Gold Finger Dimensions – x32 – Top Side ("B" Pins)                               |    |

| Figure 49: Large Size Card Gold Finger Dimensions – x32 – Bottom Side ("A" Pins)                            |    |

| Figure 50: 168-pin Base Board Primary Connector – Right Angle                                               |    |

| Figure 51: 140-pin Base Board Secondary Connector – Right Angle                                             |    |

| Figure 52: Add-in Card and Host Offset for Right Angle Connectors                                           |    |

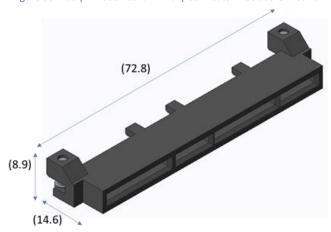

| Figure 53: 168-pin Base Board Primary Connector – Straddle Mount                                            |    |

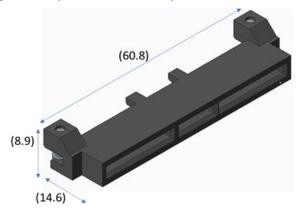

| Figure 54: 140-pin Base Board Secondary Connector – Straddle Mount                                          | 42 |

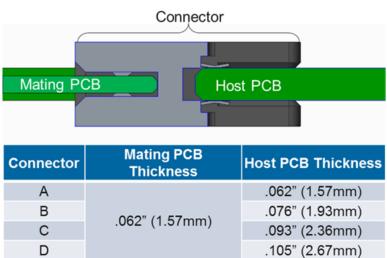

| Figure 55: Add-in Card and Host PCB Thickness Options for Straddle Mount Connectors                         |    |

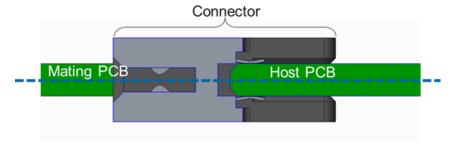

| Figure 56: 0mm Offset (Coplanar) for 0.062" Thick Baseboards                                                |    |

| Figure 57: 0.3mm Offset for 0.076" Thick Baseboards                                                         | 44 |

|                                                                                                             |    |

| Figure 58: Primary and Secondary Connector Locations for Large Card Support with Right Angle Connectors    | 44               |

|------------------------------------------------------------------------------------------------------------|------------------|

| Figure 59: Primary and Secondary Connector Locations for Large Card Support with Straddle Mount Connectors | 44               |

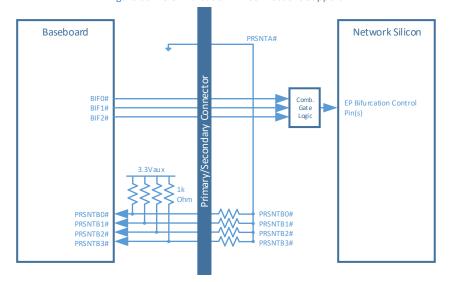

| Figure 60: PCIe Present and Bifurcation Control Pins                                                       | 52               |

| Figure 61: Example SMBus Connections                                                                       | 54               |

| Figure 62: Example Power Supply Topology                                                                   | 55               |

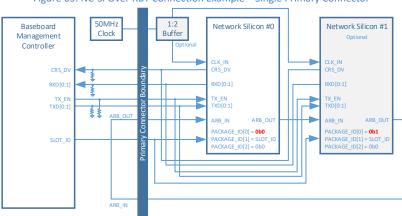

| Figure 63: NC-SI Over RBT Connection Example – Single Primary Connector                                    | 61               |

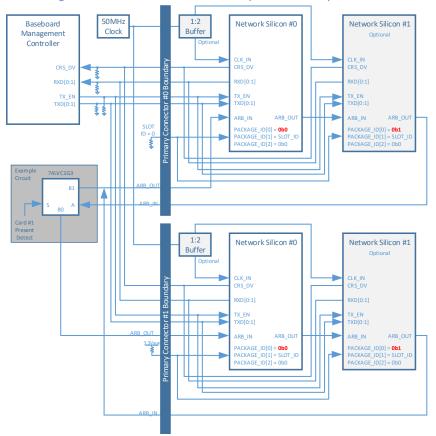

| Figure 64: NC-SI Over RBT Connection Example – Dual Primary Connector                                      | 62               |

| Figure 65: Scan Bus Connection Example                                                                     | 67               |

| Figure 66: PCIe Bifurcation Pin Connections Support                                                        |                  |

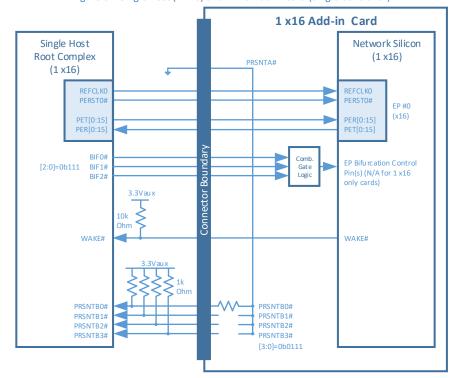

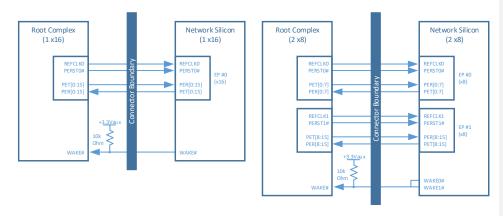

| Figure 67: Single Host (1 x16) and 1 x16 Add-in Card (Single Controller)                                   | <u>73</u> 74     |

| Figure 68: Single Host (2 x8) and 2 x8 Add-in Card (Dual Controllers)                                      | <u>74</u> 75     |

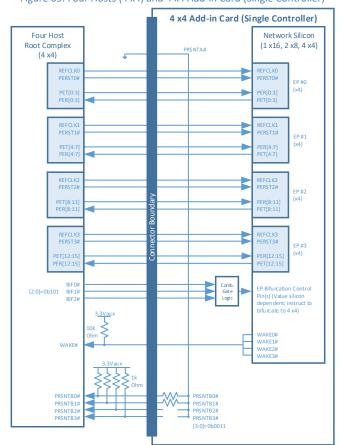

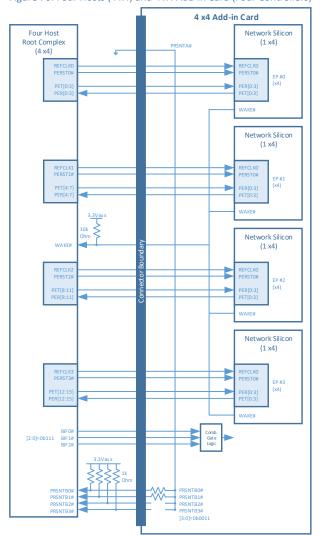

| Figure 69: Four Hosts (4 x4) and 4 x4 Add-in Card (Single Controller)                                      | <u>75</u> 76     |

| Figure 70: Four Hosts (4 x4) and 4 x4 Add-in Card (Four Controllers)                                       | <u>76</u> 77     |

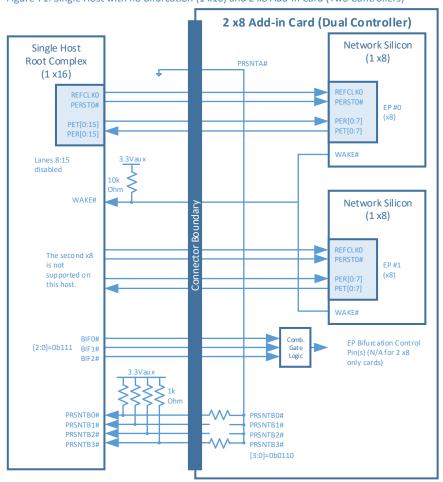

| Figure 71: Single Host with no Bifurcation (1 x16) and 2 x8 Add-in Card (Two Controllers)                  | <u>77</u> 78     |

| Figure 72: PCle Interface Connections for 1 x16 and 2 x8 Add-in Cards                                      | 78 <del>79</del> |

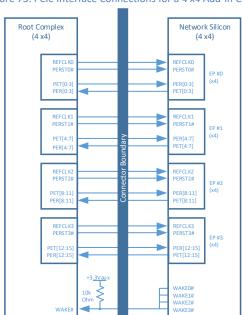

| Figure 73: PCIe Interface Connections for a 4 x4 Add-in Card                                               | 79 <del>80</del> |

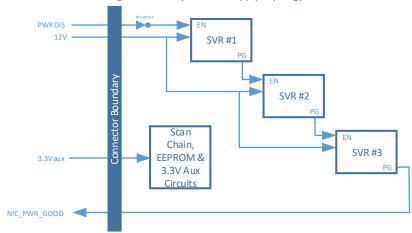

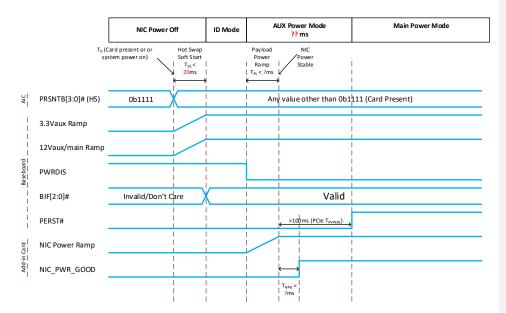

| Figure 74: Baseboard Power States                                                                          | <u>89</u> 91     |

| Figure 75: Power Sequencing                                                                                |                  |

|                                                                                                            |                  |

Rev <u>0.57<del>0.5</del></u>

# List of Tables

| Table 1: Acknowledgements – By Company                                                                             | 11 |

|--------------------------------------------------------------------------------------------------------------------|----|

| Table 2: OCP 3.0 Form Factor Dimensions                                                                            |    |

| Table 3: Baseboard to OCP NIC Form factor Compatibility Chart                                                      |    |

| Table 4: OCP NIC 3.0 Card Definitions                                                                              |    |

| Table 5: Mechanical BOM for the Small Card Bracket                                                                 |    |

| Table 6: Mechanical BOM for the Large Card Bracket                                                                 |    |

| Table 7: OCP 3.0 Line Side I/O Implementations                                                                     |    |

| Table 8: Add-in Card LED Configuration with Two Physical LEDs per Port                                             |    |

| Table 9: Baseboard LED Configurations with Two Physical LEDs per Port                                              |    |

| Table 10: Contact Mating Positions for the Primary and Secondary Connectors                                        |    |

| Table 11: Right Angle Connector Options                                                                            |    |

| Table 12: Straddle Mount Connector Options                                                                         |    |

| Table 13: Primary Connector Pin Definition (x16) (4C + OCP Bay)                                                    |    |

| Table 14: Secondary Connector Pin Definition (x16) (4C)                                                            |    |

| Table 15: Pin Descriptions – PCle 1                                                                                |    |

| Table 16: Pin Descriptions – PCle Present and Bifurcation Control Pins                                             |    |

| Table 17: Pin Descriptions – SMBus                                                                                 |    |

| Table 18: Pin Descriptions – Power                                                                                 |    |

| Table 19: Pin Descriptions – Miscellaneous 1                                                                       |    |

| Table 20: Pin Descriptions – PCle 2                                                                                |    |

| Table 21: Pin Descriptions – NC-SI Over RBT                                                                        |    |

| Table 22: Pin Descriptions – Scan Chain                                                                            |    |

| Table 23: Pin Descriptions – Scan Chain DATA OUT Bit Definition                                                    |    |

| Table 24: Pin Descriptions – Scan Bus DATA IN Bit Definition                                                       |    |

| Table 25: Pin Descriptions – Miscellaneous 2                                                                       |    |

| Table 26: PCle Bifurcation Decoder for x16 and x8 Card Widths                                                      |    |

| Table 27: PCIe Clock Associations                                                                                  |    |

| Table 28: Bifurcation for Single Host, Single Socket and Single Upstream Link (BIF[2:0]#=0b000)                    | _  |

| Table 29: Bifurcation for Single Host, Single Socket and Single/Dual Upstream Links (BIF[2:0]#=0b000)              |    |

| Table 30: Bifurcation for Single Host, Single Socket and Single/Dual/Quad Upstream Links (BIF[2:0]#=0b000)         |    |

| Table 31: Bifurcation for Single Host, Dual Sockets and Dual Upstream Links (BIF[2:0]#=0b001)                      |    |

| Table 32: Bifurcation for Single Host, Four Sockets and Four Upstream Links (BIF[2:0]#=0b010)                      |    |

| Table 33: Bifurcation for Single Host, Four Sockets and Four Upstream Links – First 8 PCIe Lanes (BIF[2:0]#=0b011) |    |

| Table 34: Bifurcation for Dual Host, Dual Sockets and Dual Upstream Links (BIF[2:0]#=0b101)                        |    |

| Table 35: Bifurcation for Quad Host, Quad Sockets and Quad Upstream Links (BIF[2:0]#=0b110)                        |    |

| Table 36: Bifurcation for Quad Host, Quad Sockets and Quad Upstream Links – First 8 lanes (BIF[2:0]#=0b111)        |    |

| Table 37: Power States                                                                                             | _  |

| Table 38: Baseboard Power Supply Rail Requirements – Slot Power Envelopes                                          |    |

| Table 39: Power Sequencing Parameters                                                                              |    |

| Table 40: Sideband Management Interface and Transport Requirements                                                 |    |

| Table 41: NC-SI Traffic Requirements                                                                               |    |

| Table 42: MC MAC Address Provisioning Requirements                                                                 |    |

| Table 43: Temperature Reporting Requirements                                                                       | _  |

| Table 44: Power Consumption Reporting Requirements                                                                 |    |

| Table 45: Pluggable Module Status Reporting Requirements                                                           |    |

| Table 46: Firmware Update Requirements                                                                             |    |

| Table 47: SMBus Address Map                                                                                        |    |

| Table 48: FRU EEPROM Record – OEM Record 0xC0, Offset 0x00                                                         | _  |

| Table 49: FRU EEPROM Record – OEM Record 0xC0, Offset 0x01                                                         | _  |

| Table 50: FRU EEPROM Record – OEM Record 0xC0, Offset 0x02                                                         |    |

| Table 51: FRU EEPROM Record – OEM Record 0xC0, Offset 0x03                                                         | _  |

| Table 52: FRU EEPROM Record – OEM Record 0xC0. Offset 0x04                                                         |    |

#### 1 Overview

#### 1.1 License

As of July 26, 2016, the following persons or entities have made this Specification available under the Open Compute Project Hardware License (Permissive) Version 1.0 (OCPHL-P)

• OCP NIC Subgroup

An electronic copy of the OCPHL-P is available at:

http://www.opencompute.org/assets/download/01-Contribution-Licenses/OCPHL-Permissive-v1.0.pdf

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The Specification implementer and user assume the entire risk as to implementing or otherwise using the Specification. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

### 1.2 Background

The OCP NIC 3.0 specification is a follow-on to the OCP 2.0 form-factor for PCle add-in cards. The OCP NIC 3.0 specification supports two basic card sizes: Small Card, and Large Card. The Small Card allows for up to 16 PCle lanes on the card edge while a Large Card supports up to 32 PCle lanes. Compared to the OCP Mezz Card 2.0 Design Specification, the updated specification provides a broader solution space for NIC and system vendors to support the following use case scenarios:

- NICs with a higher TDP

- Support up to 80W of power delivery to a single connector (Small) card; and 150W to a dual connector (Large) card

- Support up to PCle Gen5 on the system and add-in card

- Support for up to 32 lanes of PCIe per add-in card

- Support for single host, multi-root complex and multi-host environments

- Support a greater board area for more complex add-in card designs

- Support for Smart NIC implementations with on-board DRAM and accelerators

- Simplification of FRU installation and removal while reducing overall down time

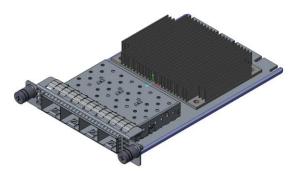

A representative Small Card OCP 3.0 NIC mezzanine card is shown in Figure 1 and a representative Large Card is shown in Figure 2.

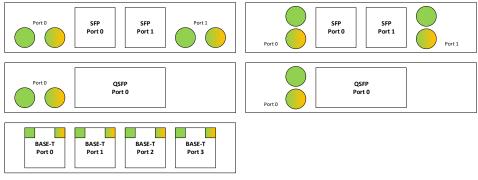

Figure 1: Representative Small OCP NIC 3.0 Card with Quad SFP Ports

Figure 2: Representative Large OCP NIC 3.0 Card with Dual QSFP Ports and on-board DRAM

In order to achieve the features outlined in this specification, OCP 3.0 compliant cards are not backwards compatible to OCP Mezz 2.0 cards.

This specification is created under OCP Server workgroup – OCP NIC subgroup. An electronic copy of this specification can be found on the Open Compute Project website:

http://www.opencompute.org/wiki/Server/Mezz#Specifications and Designs

Rev <u>0.570.56</u>

## 1.3 Acknowledgements

The OCP NIC Subgroup would like to acknowledge the following member companies for their contributions to the OCP NIC 3.0 specification:  $\frac{1}{2} \frac{1}{2} \frac{1$

## Table 1: Acknowledgements – By Company

Amphenol <u>ICC / TCS</u> Intel Corporation

Broadcom Lenovo

Dell Mellanox

Facebook Netronome

Hewlett Packard Enterprise TE

#### 1.4 Overview

#### 1.4.1 Mechanical Form factor overview

The OCP NIC 3.0 specification defines a third generation mechanical form factor that allows for interoperability between compliant baseboards and add-in cards.

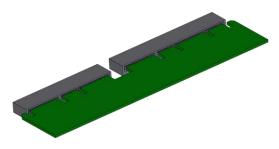

OCP NIC 3.0 cards have two form factors – Small and Large. These cards are shown in Figure 3 below. The components shown in the figures are for illustrative purposes. The Small form factor card has one connector (Primary connector) on baseboard. The Large form factor card has one or two connectors (Primary Connector only and both the Primary and Secondary Connectors) on the baseboard.

Both the Primary and Secondary connectors are defined in and compliant to SFF-TA-1002. On the add-in card side, the card edge is implemented with gold fingers. The small card gold finger area only occupies the Primary Connector area for up to 16 PCIe lanes. The large card gold finger area may occupy both the Primary and Secondary connectors for up to 32 PCIe lanes, or optionally just the Primary connector for up to 16 PCIe lane implementations. The gold finger design follows SFF-TA-1002 as well.

Primary Connector

4C + OCP NIC bay

NIC bay

NIC bay

Network I/O

Net

Figure 3: Small and Large Card Form-Factors (not to scale)

The two form factor dimensions are shown in Table 2.

Table 2: OCP 3.0 Form Factor Dimensions

| Form   | Width    | Depth   | Primary   | Secondary | Typical Use Case               |

|--------|----------|---------|-----------|-----------|--------------------------------|

| Factor |          |         | Connector | Connector |                                |

| Small  | W1 = 76  | L = 115 | 4C + OCP  | N/A       | Low profile and NIC with a     |

|        | mm       | mm      | sideband  |           | similar profile as an OCP NIC  |

|        |          |         | 168 pins  |           | 2.0 add-in card; up to 16 PCle |

|        |          |         |           |           | lanes.                         |

| Large  | W2 = 139 | L = 115 | 4C + OCP  | 4C        | Larger PCB width to support    |

|        | mm       | mm      | sideband  | 140 pins  | additional NICs; up to 32 PCIe |

|        |          |         | 168 pins  |           | lanes.                         |

The OCP NIC 3.0 design allows downward compatibility between the two card sizes. Table 3 shows the compatibility between the baseboard and NIC combinations. A small size baseboard slot may only accept a small sized NIC. A Large size baseboard slot may accept a small or large sized NIC.

Table 3: Baseboard to OCP NIC Form factor Compatibility Chart

| Baseboard | NIC Size / Supported PCIe Width |                     |  |  |

|-----------|---------------------------------|---------------------|--|--|

| Slot Size | Small                           | Large               |  |  |

| Small     | Up to 16 PCIe lanes             | Not Supported       |  |  |

| Large     | Up to 16 PCIe lanes             | Up to 32 PCIe lanes |  |  |

There are two baseboard connector options available for system designers: straddle mount and right angle (RA). The straddle mount connector option allows the OCP NIC and baseboard to exist in a coplaner position. To achieve this, a cutout exists on the baseboard and is defined in this specification. Alternatively, the right angle option allows the OCP NIC to be installed on top of the baseboard. A baseboard cutout is not required for the right angle connector. The right angle option allows the baseboard to use this area for additional routing or backside component placement. The straddle mount and right angle connectors are shown in Section 3.2.

For both the baseboard and OCP card, this specification defines the component and routing keep out areas. Refer to Section 2.5 for details.

Both the straddle mount and right angle implementations shall accept the same OCP add-in card and shall be supported in the baseboard chassis regardless of the baseboard connector selection (right angle or straddle mount) so long as the baseboard slot side and add-in card sizes are a supported combination as shown in Table 3.

This specification defines the form factor at the add-in card level, including the front panel, latching mechanism and card guide features.

More details about the card form-factor is shown in Section 2.

#### 1.4.2 Electrical overview

This specification defines the electrical interface between baseboard and the add-in card. The electrical interface is implemented with a right angle or straddle mount connector on baseboard and gold finger on the add-in card. As previously noted in the mechanical overview, each card may implement a Primary Connector or Primary + Secondary Connector. Cards using only the Primary connector are suitable for both the Small and Large form-factors and may support up to 16 lanes of PCIe. The Secondary connector, when used in conjunction with the Primary connector, allows Large form-factor implementations and may support up to 32 lanes of PCIe.

#### 1.4.2.1 Primary Connector

The Primary connector provides all OCP specific management functions as well as up to 16 lanes of PCIe between the OCP NIC and the system motherboard.

#### Management Function Overview (OCP Bay):

- DSP0222 1.1 compliant Network Controller Sideband Interface (NC-SI) RMII Based Transport (RBT)

Physical Interface

- · Power management and status reporting

- o Power disable

- State change control

- SMBus 2.0

- Control / status serial bus

- NIC-to-Host status

- Port LED Link/Activity

- Environmental Indicators

- Host-to-NIC configuration Information

- Multi-host PCIe support signals (2x PCIe resets, 2x reference clocks)

- The OCP bay provides PERST2#, PERST3#, REFCLK2 and REFCLK3. This enables support for up

to four hosts when used in conjunction with PERST0#, PERST1#, REFCLK0 and REFCLK1 in the

Primary 4C region.

- PCIe Wake signal

See Section 03.5 for a complete list of pin and function descriptions for the OCP Bay portion of the primary connector.

#### PCIe Interface Overview (4C Connector):

- 16x differential transmit/receive pairs

- Up to PCle Gen 5 support

- 2x 100 MHz differential reference clocks

- Control signals

- o 2x PCle Resets

- o Link Bifurcation Control

- o Card power disable/enable

- Power

Rev <u>0.570.56</u>

- o 12V /12V AUX

- o 3.3V AUX

See Section 3.4 for a complete list of pin and function descriptions for the 4C connector.

### 1.4.2.2 Secondary Connector

The secondary connector provides an additional 16 lanes of PCIe and their respective control signals.

#### PCIe Interface Overview (4C Connector):

- 16x differential transmit/receive pairs

- o Up to PCIe Gen 5 support

- 2x 100 MHz differential reference clocks

- Control signals

- o 2x PCIe Resets

- o Link Bifurcation Control

- o Card power disable/enable

- Power

- o 12V /12V AUX

- 3.3V AUX

See Section 3.4 for a complete list of pin and function descriptions for the 4C connector.

#### 1.5 References

- DMTF Standard. DSP0222, Network Controller Sideband Interface (NC-SI) Specification. Distributed Management Task Force, Rev 1.1.0, September 23<sup>rd</sup>, 2015.

- DMTF Standard. *DSP0222, Network Controller Sideband Interface (NC-SI) Specification.* Distributed Management Task Force, Rev 1.2.0, Work-in-progress.

- EDSFF. Enterprise and Datacenter SSD Form Factor Connector Specification. Enterprise and Datacenter SSD Form Factor Working Group, Rev 0.9 (draft), August 2<sup>nd</sup> 2017.

- IPMI Platform Management FRU Information Storage Definition, v1.2, February 28<sup>th</sup>, 2013.

- National Institute of Standards and Technology (NIST). Special Publication 800-147, BIOS Protection Guidelines, April 2011.

- NXP Semiconductors. I<sup>2</sup>C-bus specification and user manual. NXP Semiconductors, Rev 6, April 4<sup>th</sup>, 2014.

- Open Compute Project. OCP NIC Subgroup. Online. http://www.opencompute.org/wiki/Server/Mezz

- PCIe Base Specification. PCI Express Base Specification, Revision 4.0 (draft).

- PCIe CEM Specification. PCI Express Card Electromechanical Specification, Revision 4.0 (draft).

- SMBus Management Interface Forum. System Management Bus (SMBus) Specification. System Management Interface Forum, Inc, Version 2.0, August 3<sup>rd</sup>, 2000.

- SNIA. SFF-TA-1002, Specification for Protocol Agnostic Multi-Lane High Speed Connector. SNIA SFF TWG Technology Affiliate, Rev 1.0, December 12<sup>th</sup>, 2017.

#### 2 Card Form Factor

## 2.1 Form Factor Options

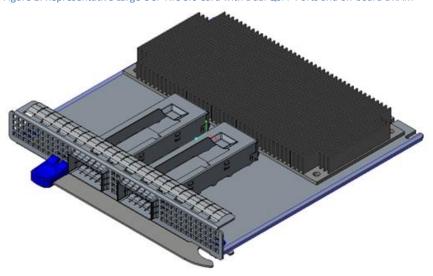

OCP3.0 provides two fundamental form factor options: a small card (76mm x 115mm) and a large card (139mm x 115mm).

These form factors support a Primary Connector and optionally, a Secondary Connector. The Primary Connector is defined to be a SFF-TA-1002 compliant 4C connector plus a 28-pin bay for OCP 3.0 specific pins. The Secondary Connector is the 4C connector as defined in SFF-TA-1002. The 4C specification supports up to 32 differential pairs for a x16 PCle connection per connector. For host platforms, the 28-pin OCP bay is required for the Primary connector. This is also mandatory for add-in cards.

The small card uses the Primary 4C connector to provide up to a x16 PCle interface to the host. The additional 28-pin OCP bay carries sideband management interfaces as well as OCP NIC 3.0 specific control signals for multi-host PCle support. The small size card provides sufficient faceplate area to accommodate up to 2x QSFP modules, 4x SFP modules, or 4x RJ-45 for BASE-T operation. The small card form factor supports up to 80W of delivered power to the card edge.

Figure 4: Example Small Card Form Factor

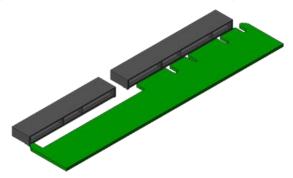

The large card uses the Primary 4C + OCP bay connector to provide the same functionality as the small card along with an additional Secondary 4C connector to provide up to a x32 PCIe interface. The large card may utilize both the Primary and Secondary connectors, or just the Primary connector for lower PCIe lane count applications. Table 4 summarizes the large card permutations. The large size card supports higher power envelopes and provides additional board area for more complex designs. The large card form factor supports up to 150W of delivered power to the card edge across the two connectors.

Figure 5: Example Large Card Form Factor

For large cards, implementations may use both the Primary and Secondary Connector (as shown in Figure 6), or may use the Primary Connector only (as shown in Figure 7) for the card edge gold fingers.

Figure 6: Primary Connector (4C + OCP Bay) and Secondary Connector (4C) (Large) Add-in Cards

Figure 7: Primary Connector (4C + OCP Bay) Only (Large) Add-in Cards

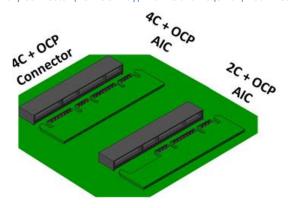

For both form-factors, an add-in card may optionally implement a subset of pins to support up to a x8 PCIe connection. This is implemented using a 2C card edge per SFF-TA-1002. The Primary Connector may

Rev <u>0.570.56</u>

support a 2C sized add-in card along with the 28 pin OCP bay. The following diagram from the SFF-TA-1002 specification illustrates the supported host Primary and Secondary Connectors and add-in card configurations.

Figure 8: Primary Connector (4C + OCP Bay) with 4C and 2C (Small) Add-in Cards

## Table 4

Table 4 summarizes the supported card form factors. Small form factors cards support the Primary Connector and up to 16 PCIe lanes. Large form factor cards support implementations with both the Primary and Secondary Connectors and up to 32 PCIe lanes, or a Primary Connector only implementation with up to 16 PCIe lanes.

Table 4: OCP NIC 3.0 Card Definitions

| Add in Card Size and | Secondary Connector    |    | Prir       | nary Connector |         |

|----------------------|------------------------|----|------------|----------------|---------|

| max PCIe Lane Count  | 4C Connector, x16 PCle |    | 4C Connect | or, x16 PCle   | OCP Bay |

| Small (x8)           |                        |    |            | 2C             | OCP Bay |

| Small (x16)          |                        |    | 4C         |                | OCP Bay |

| Large (x8)           |                        |    | 2C         |                | OCP Bay |

| Large (x16)          |                        |    | 4C         |                | OCP Bay |

| Large (x24)          |                        | 2C | 4C         |                | OCP Bay |

| Large (x32)          | 4C                     |    | 4          | С              | OCP Bay |

### 2.2 I/O bracket

The following section defines the standard I/O bracket and standard chassis opening required for both the Small and Large form-factor cards.

#### 2.2.1 Small Form Factor Add-in Card I/O Bracket

Figure 9 defines the standard Small Card form factor I/O bracket.

Figure 9: Small Card Standard I/O Bracket

Note: The add-in card supplier shall add port identification on bracket that meet their manufacturing and customer requirements.

For RJ-45 implementations, a customized bracket must be created. Figure 10 shows an implementation example.

Figure 10: Small Card Customized bracket for RJ-45 Connector

Drawing to be inserted

Figure 11 shows the standalone bracket assembly and Figure 12 shows the bracket assembly on the add-in card.

Figure 11: Small Card 3D Bracket Assembly (Standalone)

<mark>TBD</mark>

Figure 12: Small Card 3D Bracket Assembly (Installed on Add-in Card)

<mark>TBD</mark>

Rev <u>0.57<del>0.56</del></u>

In addition to the sheet metal, Table 5 lists the additional hardware components used for the Small Card bracket assembly.

Table 5: Mechanical BOM for the Small Card Bracket

| Item description                      | Supplier Part Number |

|---------------------------------------|----------------------|

| Top and bottom EMI fingers            | TF187VE32F11         |

| Screw / Rivet (part of bracket assy)? | TBD TBD              |

| Side EMI Finger                       | TBD TBD              |

| Thumb screw                           | TBD                  |

| Pull Tab                              | TBD TBD              |

| Latch                                 | TBD                  |

| Screw (attaching Bracket & NIC)       | TBD                  |

| SMT Nut (on NIC)                      | TBD                  |

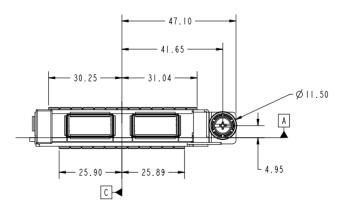

#### 2.2.2 Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions

The following dimensions are considered critical-to-function (CTF) for each small form factor add-in card.

Figure 13: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Top View)

Figure 14: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Front View)

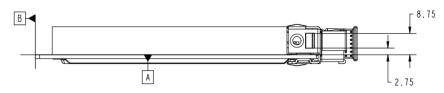

Figure 15: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Left)

Figure 16: Small Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Right)

## 2.2.3 Small Form Factor Baseboard Critical-to-Function (CTF) Dimensions

The following dimensions are considered critical-to-function (CTF) for each small form factor baseboard chassis.

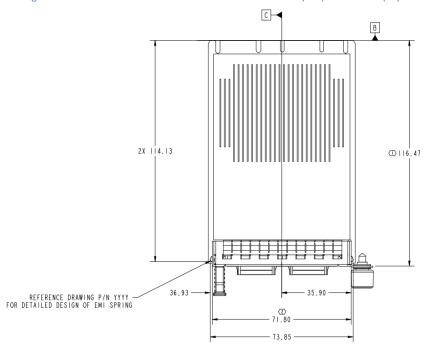

Figure 17: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear View)

Rev <u>0.570.56</u>

Figure 18: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Side View)

Figure 19: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear Rail Guide View)

Figure 20: Small Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rail Guide Detail)

On the baseboard side, the following mechanical dimensions shall be met to support a small form factor add-in card:

Figure 21: Baseboard and Rail Assembly Drawing for Small Cards TBD; need 3D baseboard and rail assembly drawing.

## 2.2.4 Large Form Factor Add-in Card I/O Bracket

TBD. Definition is in progress. All drawings from the Small Form-Factor implementation need to be replicated for the Large form-factor.

Figure 22 defines the standard Large Card form factor I/O bracket.

Figure 22: Large Card Standard I/O Bracket

TBD

Note: The add-in card supplier shall add port identification on bracket that meet their manufacturing and customer requirements.

For RJ-45 implementations, a customized bracket must be created. Figure 23 shows an implementation example.

### Figure 23: Large Card Customized bracket for RJ-45 Connector

Drawing to be inserted

Figure 24 shows the standalone bracket assembly and Figure 25 shows the bracket assembly on the add-in card.

Figure 24: Large Card 3D Bracket Assembly (Standalone)

TBE

Figure 25: Large Card 3D Bracket Assembly (Installed on Add-in Card)

TBC

In addition to the sheet metal, Table 6Table 5 lists the additional hardware components used for the Small Card bracket assembly.

Table 6: Mechanical BOM for the Large Card Bracket

| Item description                      | Supplier Part Number |

|---------------------------------------|----------------------|

| Top and bottom EMI fingers            | TBD TBD              |

| Screw / Rivet (part of bracket assy)? | TBD TBD              |

| Side EMI Finger                       | TBD TBD              |

| Thumb screw                           | TBD TBD              |

| Pull Tab                              | TBD TBD              |

| Latch                                 | TBD TBD              |

| Screw (attaching Bracket & NIC)       | TBD TBD              |

| SMT Nut (on NIC)                      | TBD TBD              |

## 2.2.5 Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions

The following dimensions are considered critical-to-function (CTF) for each large form factor add-in card.

Figure 26: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Top View)

TBE

Figure 27: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Front View)

<mark>TBD</mark>

Figure 28: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Left)

TBD

Figure 29: Large Form Factor Add-in Card Critical-to-Function (CTF) Dimensions (Side View – Right)

### 2.2.6 Large Form Factor Baseboard Critical-to-Function (CTF) Dimensions

The following dimensions are considered critical-to-function (CTF) for each large form factor baseboard chassis.

Figure 30: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear View)

TBD

Figure 31: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Side View)

TBD

Figure 32: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rear Rail Guide View)

**TBD**

Figure 33: Large Form Factor Baseboard Chassis Critical-to-Function (CTF) Dimensions (Rail Guide Detail)

**TBD**

On the baseboard side, the following mechanical dimensions shall be met to support a large form factor add-in card:

Figure 34: Baseboard and Rail Assembly Drawing for Large Card

TBD; need 3D baseboard and rail assembly drawing for large card.

### 2.3 Line Side I/O Implementations

At the time of this writing, the Small and Large form-factor implementations have been optimized to support the following standard line side I/O implementations:

Table 7: OCP 3.0 Line Side I/O Implementations

| Form Factor | Max Topology Connector Count |  |

|-------------|------------------------------|--|

| Small       | 2x QSFP28                    |  |

| Small       | 4x SFP28                     |  |

| Small       | 4x RJ-45                     |  |

| Large       | 2x QSFP28                    |  |

| Large       | 4x SFP28                     |  |

| Large       | 4x RJ-45                     |  |

Additional combinations are permissible as I/O form-factor technologies and thermal capabilities evolve.

### 2.4 LED Implementations

LEDs shall be implemented on the OCP NIC 3.0 I/O bracket when there is sufficient space for local indication. LEDs may <u>also</u> be implemented on the card Scan Chain (as defined in Section 3.5.3) for remote link/activity indication on the baseboard. These two cases are described below. In both cases, the actual link rate may be directly queried through the management interface.

#### 2.4.1 Add-in Card LED Configuration

For low I/O count small form-factor cards without built in light pipes (such as 1x QSFP28, 2x SFP28, or 2x RJ-45), or a large form-factor OCP 3.0 NIC, where additional I/O bracket area is available, the card shall implement on-board link/activity indications in place of the Scan Chain LED stream. The recommended local (on-card) LED implementation uses two physical LEDs (a discrete Link/Activity LED and a bi-colored Speed A/Speed B LED). Table 8 describes the add-in card LED implementations.

Table 8: Add-in Card LED Configuration with Two Physical LEDs per Port

| LED Pin  | LED Color | Description                                                                                                                                                                                                                                                                                            |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link /   | Green     | Active low. Multifunction LED.                                                                                                                                                                                                                                                                         |

| Activity |           | This LED shall be used to indicate link and link activity.  When the link is up and no link activity is present, then this LED shall be lit and solid. This indicates that the link is established, there are no local or remote faults, and the link is ready for data packet transmission/reception. |

|          |           | When the link is up and there is link activity, then this LED should blink at the interval of 50-500ms during link activity.  The Link/Activity LED shall be located on the left hand side or located on the top for each port when the add-in card is viewed in the                                   |

|          |           | horizontal plane.                                                                                                                                                                                                                                                                                      |

| Speed    | Green     | Active low. Bicolor multifunction LED.                                                                                                                                                                                                                                                                 |

|          | Amber     |                                                                                                                                                                                                                                                                                                        |

| Off | The LED is Green when the port is linked at its maximum speed.                                                                                                                               |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | The LED is Amber when the port is linked at it second highest speed. The LED is off when the device is linked at a speed lower than the second highest capable speed, or no link is present. |

|     | The Amber Speed LED indicator may be used for port identification through vendor specific link diagnostic software.                                                                          |

|     | The bicolor speed LED shall be located on the right hand side or located on the bottom for each port when the add-in card is viewed in the horizontal plane.                                 |

### 2.4.2 Add-in Card LED Ordering

For all add-in card use cases, each port shall implement the green Link/Activity LED and a bicolor green/amber speed A/B LED. For all baseboards, each port shall implement the green Link/Activity LED and a green speed A LED.

For horizontal LED positions, the Link/Activity LED shall be located on the left side for each port and the speed LED shall be located on the right side for each port.

For vertical LED positions, the Link/Activity LED shall be located on top and the speed LED shall be located on the bottom.

The placement of the LEDs on the faceplate may be left up to the discretion of the add-in card and baseboard designers. The LED port association shall be clearly labeled on the add-in card and on the baseboard.

Figure 35: LED Ordering – Example Small Card Link/Activity and Speed LED Placement

Rev <u>0.570.56</u>

#### 2.4.3 Baseboard LEDs Configuration Over the Scan Chain

A small form-factor OCP NIC 3.0 with a fully populated I/O bracket (2x QSFP28, 4x SFP28 or 4x RJ-45) does not have has insufficient space for discrete on-board (faceplate) LED indicators. In this case, the line side link and activity LED indicators are implemented on the baseboard system via the Scan Chain. The Scan Chain bit stream is defined in Section 3.5.3.

The baseboard LED implementation uses two discrete LEDs (Link/Activity and Speed indication). Table 9 describes the baseboard LED configuration for baseboard implementations.

The LED implementation is required for all add-in cards. The LED implementation is optional for baseboards.

Table 9: Baseboard LED Configurations with Two Physical LEDs per Port

| LED Pin  | LED Color | Description                                                                                                                                                                                                                                |

|----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link /   | Green     | Active low. Multifunction LED.                                                                                                                                                                                                             |

| Activity |           | This LED shall be used to indicate link and link activity.                                                                                                                                                                                 |

|          |           | When the link is up and no link activity is present, then this LED shall be lit and solid. This indicates that the link is established, there are no local or remote faults, and the link is ready for data packet transmission/reception. |

|          |           | When the link is up and there is link activity, then this LED should blink at the interval of 50-500ms during link activity.                                                                                                               |

|          |           | The baseboard Link/Activity LED location is not mandated in this specification and will be defined by the system vendor.                                                                                                                   |

| Speed    | Green     | Active low. Multifunction LED.                                                                                                                                                                                                             |

|          | Off       | The LED is Green when the port is linked at its maximum speed.  The LED is off when the device is linked at a speed lower than the highest capable speed, or no link is present.                                                           |

|          |           | The baseboard speed LED location is not mandated in this                                                                                                                                                                                   |

|          |           | specification and will be defined by the system vendor.                                                                                                                                                                                    |

|          |           | Note: The baseboard speed LED is only defined to be a single color due to the scan chain bit definition. For dual color indication, the baseboard may obtain this information through the NIC Management Interface.                        |

At the time of this writing, the Scan Chain definition allows for up to one link/activity and one speed LED per port. A total of up to 8 ports are supported in the Scan Chain. The bit stream defines the LEDs to be active low (on). The Scan Chain LED implementation allows the NIC LED indicators to be remotely located on the OCP 3.0 compliant chassis (e.g. front LED indicators with rear I/O cards).

Commented [JN1]: Double check if dual QSFP has room for LED?

2x QSFP shall be smaller than 4x SFP+ and the extra space could

2x QSFP shall be smaller than 4x SFP+ and the extra space could be used for LED implementation

Commented TN2R1]: Dual QSFP designs on the small formfactor do not have sufficient space for on-NIC LEDs. No action. Text okay as-is.

**Commented [JN3]:** 1.For current define, it is not bi-color 2.However, it makes sense to use bi-color to have same amount of feature as on-NIC-LED.

Commented [TN4R3]: As currently defined, the scan chain only provides a single bit to communicate speed, and a single bit to communicate link/activity. Baseboard implementers that wish to use more than one LED need to query the speed via management instead of the scan chain.

## 2.5 Mechanical Keepout Zones

## 2.5.1 Baseboard Keep Out Zones – Small Card Form Factor

TBD – Need keepout drawings and envelopes for small / large size baseboard including primary/secondary/rail keepouts/cutout for straddle mount/keepout for right angle.

## 2.5.2 Baseboard Keep Out Zones – Large Card Form Factor

TBD. – need input from mechanical engineering

## 2.5.3 Small Card Form Factor Keep Out Zones

Figure 36: Small Form Factor Keep Out Zone – Top View

Rev <u>0.57</u>0.56

Figure 37: Small Form Factor Keep Out Zone – Bottom View

Figure 38: Small Form Factor Keep Out Zone – Side View

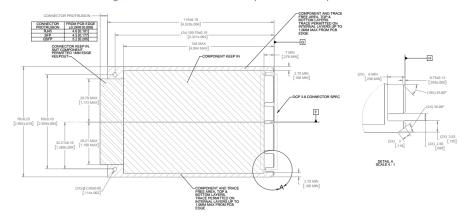

## 2.5.4 Large Card Form Factor Keep Out Zones

CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNECTOR FROMER EDGE

| CONNE

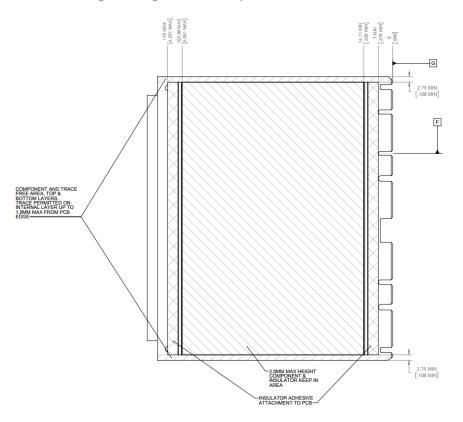

Figure 39: Large Form Factor Keep Out Zone – Top View

Rev <u>0.570.56</u>

Figure 40: Large Form Factor Keep Out Zone – Bottom View

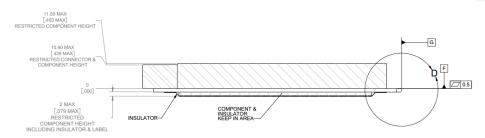

Figure 41: Large Form Factor Keep Out Zone – Side View

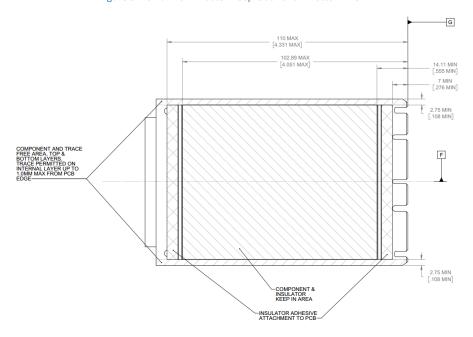

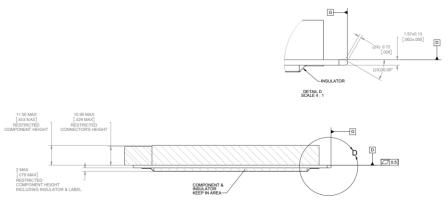

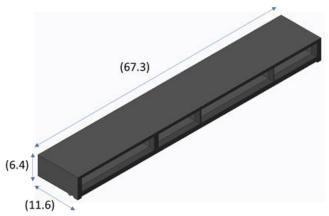

## 2.6 Insulation Requirements

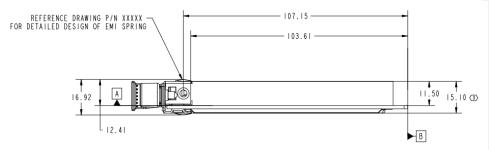

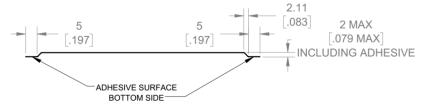

All cards shall implement an insulator to prevent the bottom side card components from shorting out to the baseboard chassis. The recommended insulator thickness is 0.25mm and shall reside within the following mechanical envelope for the Small and Large size cards.

## 2.6.1 Small Card Insulator

Figure 42: Small Card Bottom Side Insulator (Top and 3/4 View)

Figure 43: Small Card Bottom Side Insulator (Side View)

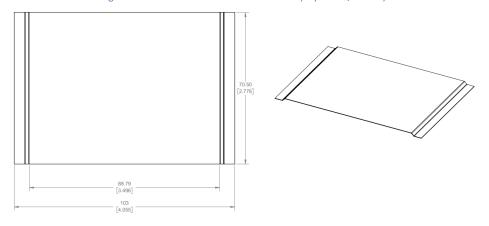

### 2.6.2 Large Card Insulator

Figure 44: Large Card Bottom Side Insulator (Top and 3/4 View)

Figure 45: Large Card Bottom Side Insulator (Side View)

## 2.7 Labeling Requirements

**TBD**

Editor's note [TN 20171214]: Consider the following label attributes:

- Label attributes are human (e.g. ASCII) and machine readable (e.g. barcode)

- Add-in card MAC address shall be visible (used MAC address range, or base value)

- Board serial number

## 2.8 NIC Implementation Examples

<mark>TBD</mark>

## 2.9 Non-NIC Use Cases

"PCIe interface with extra management sideband"

2.9.1 PCIe Retimer card

<mark>TBD</mark>

2.9.2 Accelerator card

**TBD**

2.9.3 Storage HBA / RAID card

<mark>TBD</mark>

# 3 Card Edge and Baseboard Connector Interface

#### 3.1 Gold Finger Requirements

The OCP NIC 3.0 add-in cards are compliant to the SFF-TA-1002 specification with respect to the gold fingers and connectors.

Small Size cards fit in the Primary Connector. Primary Connector compliant cards are 76mm x 115mm and may implement the full 168-pins. The Primary Connector cards may optionally implement a subset of gold finger pins if there is a reduced PCIe width requirement (such as 1 x8 and below). In this case, the card edge gold finger may implement a 2C design. The overall board thickness is 1.57mm. The gold finger dimensions for the Primary Connector compliant cards are shown below.

Large Size Cards support up to a x32 PCIe implementation and may use both the Primary and Secondary connectors. Large Size Cards may implement a reduced PCIe lane count and optionally implement only the Primary Connector 4C, or 2C plus OCP bay.

Note: The "B" pins on the connector are associated with the top side of the add-in card. The "A" pins on the connector are associated with the bottom side of the add-in card.

Figure 46: Small Size Primary Connector Gold Finger Dimensions – x16 – Top Side ("B" Pins)

Figure 47: Small Size Primary Connector Gold Finger Dimensions – x16 – Bottom Side ("A" Pins)

Figure 48: Large Size Card Gold Finger Dimensions – x32 – Top Side ("B" Pins)

Figure 49: Large Size Card Gold Finger Dimensions – x32 – Bottom Side ("A" Pins)

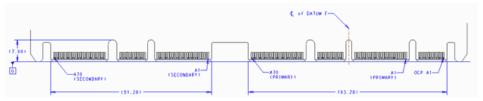

#### 3.1.1 Gold Finger Mating Sequence

Per the SFF-TA-1002 specification, the Primary and Secondary connectors are protocol agnostic and are optimized for high speed differential pairs. For use in the OCP NIC 3.0 application, some pin locations are used for single ended control nets or power and would benefit from a shorter pin length for staggering. As such, the recommended add-in card gold finger staging is shown in Table 10 for a two stage, first-mate, last-break functionality. The host connectors have a single stage mating and do not implement different pin lengths.

The AIC Plug (Free) side refers to the add-in card gold fingers; the receptacle (Fixed) side refers to the physical connector on the host platform. This table is based on the SFF-TA-1002 Table A-1 with modifications for OCP NIC 3.0. Refer to the mechanical drawings for pin the first-mate and second-mate lengths.

Table 10: Contact Mating Positions for the Primary and Secondary Connectors

Rev <u>0.57</u>0.56 B2 B3 B4 B5 B6 B7 B8 B9 B10 B11 B12 B13 B14 B15 B16 B17 B20 B21 B22 B23 B24 B25 B26 B27 B28 B29 B30 B31 B32 B33 B34 B35 B36 B37 B38 B39 B40 B41 B42 B43 B44 B45 B46 B47 B48 B49 B50 B51 B52 B53 B54 B55 B56 B60 B61 B62 B63 B64 B65 B66 B67 B68 B69 B70

# 3.2 Baseboard Connector Requirements

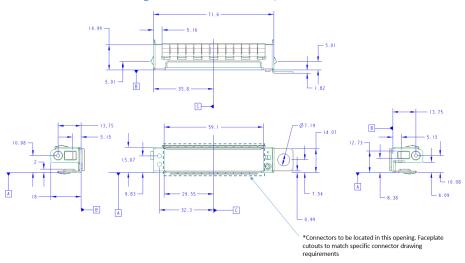

The OCP NIC 3.0 connectors are compliant to the "4C connector" as defined in the SFF-TA-1002 specification for a right angle or straddle mount form-factor. The 4C connector is 140-pins in width and includes support for up to 32 differential pairs to support a x16 PCle connection. The connector also provides 6 pins of 12V for payload power. This implementation is common between both the Primary and Secondary Connectors. In addition, the Primary Connector has a 28-pin OCP Bay to the right of pin 1. These pins are used for management and support for up to a 4 x2 and 4 x4 multi-host configuration on the Primary Connector. The Primary and Secondary Connector drawings are shown below.

All diagram units are in mm unless otherwise noted.

# 3.2.1 Right Angle Connector

The following offset and height options are available for the right angle Primary and Secondary Connectors.

Table 11: Right Angle Connector Options

| Name                         | Pins     | Style and Baseboard Thickness | Offset (mm) |

|------------------------------|----------|-------------------------------|-------------|

| Primary Connector – 4C + OCP | 168 pins | Right Angle                   | 4mm         |

| Secondary Connector – 4C     | 140 pins | Right Angle                   | 4mm         |

Figure 50: 168-pin Base Board Primary Connector – Right Angle

Rev <u>0.570.56</u>

Figure 51: 140-pin Base Board Secondary Connector – Right Angle

# 3.2.2 Right Angle Offset

The OCP NIC 3.0 right angle connectors have a 4.0mm offset from the baseboard (pending SI simulation results). This is shown in Figure 52.

Figure 52: Add-in Card and Host Offset for Right Angle Connectors

### 3.2.3 Straddle Mount Connector

The following offset and height options are available for the straddle mount Primary and Secondary Connectors.

Table 12: Straddle Mount Connector Options

| Name                         | Pins     | Style and Baseboard Thickness | Offset (mm)    |

|------------------------------|----------|-------------------------------|----------------|

| Primary Connector – 4C + OCP | 168 pins | Straddle Mount for 0.062"     | Coplanar (0mm) |

| Primary Connector – 4C + OCP | 168 pins | Straddle Mount for 0.076"     | -0.3mm         |

| Primary Connector – 4C + OCP | 168 pins | Straddle Mount for 0.093"     | Coplanar (0mm) |

| Secondary Connector – 4C     | 140 pins | Straddle Mount for 0.062"     | Coplanar (0mm) |

| Secondary Connector – 4C     | 140 pins | Straddle Mount for 0.076"     | -0.3mm         |

| Secondary Connector – 4C     | 140 pins | Straddle Mount for 0.093"     | Coplanar (0mm) |

Figure 53: 168-pin Base Board Primary Connector – Straddle Mount

Figure 54: 140-pin Base Board Secondary Connector – Straddle Mount

#### 3.2.4 Straddle Mount Offset and PCB Thickness Options

The OCP NIC 3.0 straddle mount connectors have four PCB thicknesses they can accept. The available options are shown in Figure 55. The thicknesses are 0.062'', 0.076'', 0.093'', and 0.105''. These PCBs must be controlled to a thickness of  $\pm 8\%$ . These are available for both the Primary and Secondary connector locations. At the time of this writing, the most commonly used part is expected to be the 0.076'' host board thickness.

Figure 55: Add-in Card and Host PCB Thickness Options for Straddle Mount Connectors

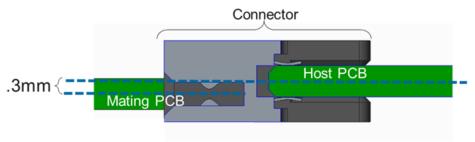

The connectors are capable of being used coplanar as shown in Figure 56. Additionally, the connectors are also capable of having a 0.3mm offset from the centerline of the host board as shown in Figure 57.

Figure 56: 0mm Offset (Coplanar) for 0.062" Thick Baseboards

Figure 57: 0.3mm Offset for 0.076" Thick Baseboards

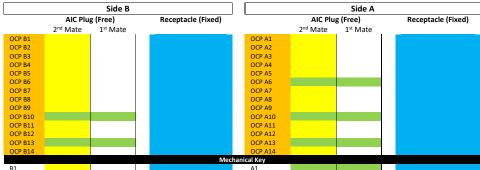

#### 3.2.5 Large Card Connector Locations

In order to the support the large form factor, systems must locate the Primary and Secondary Connectors per the mechanical drawing shown in Figure 58 and Figure 59.

Figure 58: Primary and Secondary Connector Locations for Large Card Support For with Right Angle Connectors

Figure 59: Primary and Secondary Connector Locations for Large Card Support For with Straddle Mount Connectors

#### 3.3 Pin definition

The pin definitions of an OCP NIC 3.0 card with up to a x32 PCIe interface are shown in Table 13 and Table 14. All signal directions are shown from the perspective of the baseboard.

A baseboard system may provide a combination of Primary Connectors only, or Primary and Secondary Connectors to support multiple sizes of add-in cards. Both connectors share common functionality with power, SMBus 2.0, x16 PCIe and bifurcation control. The Primary Connector has an additional OCP Bay (pins OCP\_A[1:14], OCP\_B[1:14]) with additional REFCLKs for supporting up to four PCIe hosts, NC-SI connectivity and a Scan Chain for information exchange between the host and card. The NIC is required

Rev <u>0.570.56</u>

to implement the Scan Chain, while the baseboard may choose to optionally implement it. Depending on the baseboard form-factor, multiple OCP NIC 3.0 compliant cards may be designed into the system.

The pins common to the Primary and Secondary Connectors are shown in Section 3.4. The OCP Bay pins on the Primary Connector only are shown in Section 03.5.

Cards or systems that do not require the use of a PCIe x16 connection may optionally implement a subset electrical connections as applicable to the design. For example, a x8 (or smaller) card using the first 8 PCIe lanes that is compliant with the Primary Connector pinout. Refer to Sections 3.1 and 3.2 for mechanical details. For these cases, the Primary Connector matches the 2C dimensions as defined in SFF-TA-1002.

In all cases, the physical baseboard connectors shall support x16 PCIe widths and must be implemented with the Primary (4C + OCP Bay) and Secondary (4C) connectors.

Table 13: Primary Connector Pin Definition (x16) (4C + OCP Bay)

|         | Side B          | Side A      | oci bayı | 1                                                         |                                                          |

|---------|-----------------|-------------|----------|-----------------------------------------------------------|----------------------------------------------------------|

| OCP B1  | NIC PWR GOOD    | PERST2#     | OCP A1   | _                                                         | _                                                        |

| OCP B2  | PWRBRK#         | PERST3#     | OCP A2   | Ť                                                         | ı ğ                                                      |

| OCP B3  | LD#             | WAKE#       | OCP A3   | ar                                                        | a a                                                      |

| OCP B4  | DATA IN         | RBT ARB IN  | OCP A4   | Primary Connector (x16, 168-pin add-in card with OCP Bay) | Primary Connector (x8, 112-pin add-in card with OCP bay) |

| OCP_B5  | DATA_OUT        | RBT_ARB_OUT | OCP_A5   | ğ                                                         | ğ                                                        |

| OCP_B6  | CLK             | GND         | OCP_A6   | ect                                                       | ect                                                      |

| OCP_B7  | SLOT_ID         | RBT_TX_EN   | OCP_A7   | Ŷ                                                         | o o                                                      |

| OCP_B8  | RBT_RXD1        | RBT_TXD1    | OCP_A8   | <u>X</u>                                                  | (X)                                                      |