# OCP NIC 3.0 Design Specification

Version 0.01

Author: OCP Server Workgroup, OCP NIC subgroup

## Table of Contents

| 1 | Overview                          |                                                  |                        |  |  |  |  |

|---|-----------------------------------|--------------------------------------------------|------------------------|--|--|--|--|

|   | 1.1 Li                            | cense                                            | 9                      |  |  |  |  |

|   | 1.2 B                             | ackground                                        | 10                     |  |  |  |  |

|   | 1.3 A                             | cknowledgements                                  | 11                     |  |  |  |  |

|   | 1.4 Overview                      |                                                  |                        |  |  |  |  |

|   | 1.4.1                             | Mechanical Form factor overview                  | 11                     |  |  |  |  |

|   | 1.4.2                             | Electrical overview                              | 14                     |  |  |  |  |

|   | 1.5 R                             | eferences                                        | 17                     |  |  |  |  |

| 2 | Card Forn                         | n Factor                                         | 18                     |  |  |  |  |

|   | 2.1 O                             | verview                                          | 18                     |  |  |  |  |

|   | 2.2 Fo                            | orm Factor Options                               | 18                     |  |  |  |  |

|   | 2.3 I/                            | O bracket                                        | 20                     |  |  |  |  |

|   | 2.4 Line Side I/O Implementations |                                                  |                        |  |  |  |  |

|   | 2.5 LE                            | ED Implementations                               | 21                     |  |  |  |  |

|   | 2.5.1                             | Baseboard LEDs Configuration Over the Scan Chain | 21                     |  |  |  |  |

|   | 2.5.2                             | Add-in Card LED Configuration                    | 23                     |  |  |  |  |

|   | 2.5.3                             | Add-in Card LED Ordering                         | 24                     |  |  |  |  |

|   | 2.6 N                             | lechanical Keepout Zones                         | <u>26</u> 25           |  |  |  |  |

|   | 2.6.1                             | Baseboard Keep Out Zones                         | <u>26<del>25</del></u> |  |  |  |  |

|   | 2.6.2                             | Add-in Card Keep Out Zones                       | <u>26</u> 25           |  |  |  |  |

|   | 2.7 La                            | abeling Requirements                             | <u>26</u> 25           |  |  |  |  |

|   | 2.8 Insulation Requirements       |                                                  |                        |  |  |  |  |

|   | 2.9 N                             | IC Implementation Examples                       | 26                     |  |  |  |  |

|   | <mark>2.10</mark> N               | <mark>on-NIC Use Cases</mark>                    | <u>27<del>26</del></u> |  |  |  |  |

|   | <mark>2.10.1</mark>               | PCIe Retimer card                                | <u>27<del>26</del></u> |  |  |  |  |

|   | <mark>2.10.2</mark>               | Accelerator card                                 | <u>27<del>26</del></u> |  |  |  |  |

|   | <mark>2.10.3</mark>               | Storage HBA / RAID card                          | <u>27<del>26</del></u> |  |  |  |  |

| 3 | Card Edge                         | e and Baseboard Connector Interface              | <u>27<del>26</del></u> |  |  |  |  |

|   | 31 G                              | old Finger Requirements                          | 2726                   |  |  |  |  |

#### Rev0.01

|                                                     | 3.1.1 Gold Finger Mating Sequence |                                                                     |              |  |

|-----------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|--------------|--|

| 3.2                                                 | Ва                                | Baseboard Connector Requirements                                    |              |  |

| 3.3                                                 | Pin definition                    |                                                                     | 31           |  |

| 3.4                                                 | Si                                | gnal Descriptions – Common                                          | 37           |  |

|                                                     | 3.4.1                             | PCIe Interface Pins                                                 | 37           |  |

|                                                     | 3.4.2                             | PCIe Present and Bifurcation Control Pins                           | 41           |  |

|                                                     | 3.4.3                             | SMBus Interface Pins                                                | 43           |  |

|                                                     | 3.4.4                             | Power Supply Pins                                                   | 44           |  |

|                                                     | 3.4.5                             | Miscellaneous Pins                                                  | 46           |  |

| 3.5                                                 | Si                                | gnal Descriptions – OCP Bay (Primary Connector)                     | 47           |  |

|                                                     | 3.5.1                             | PCIe Interface Pins – OCP Bay (Primary Connector)                   | 47           |  |

|                                                     | 3.5.2                             | NC-SI Over RBT Interface Pins – OCP Bay (Primary Connector)         | 49           |  |

|                                                     | 3.5.3                             | Scan Chain Pins – OCP Bay (Primary Connector)                       | 57           |  |

|                                                     | 3.5.4                             | Primary Connector Miscellaneous Pins – OCP Bay (Primary Connector   | or) 64       |  |

| 3.6                                                 | PC                                | CIe Bifurcation Mechanism                                           | 65           |  |

|                                                     | 3.6.1                             | PCIe Add-in Card to Baseboard Bifurcation Configuration (PRSNTA#    | <u> </u>     |  |

|                                                     | PRSNT                             | TB[3:0]#)                                                           | 66           |  |

|                                                     | 3.6.2                             | PCIe Baseboard to Add-in Card Bifurcation Configuration (BIF[2:0]#) | <u>67</u> 6( |  |

|                                                     | 3.6.3                             | PCIe Bifurcation Decoder                                            | 67           |  |

|                                                     | 3.6.4                             | Bifurcation Detection Flow                                          | 69           |  |

|                                                     | 3.6.5                             | PCIe Bifurcation Examples                                           | 70           |  |

| 3.7                                                 | PC                                | CIe Clocking Topology                                               | 76           |  |

| 3.8                                                 | PC                                | Cle Bifurcation Results and REFCLK Mapping                          | 78           |  |

| 3.9                                                 | Po                                | ower Capacity and Power Delivery                                    | 87           |  |

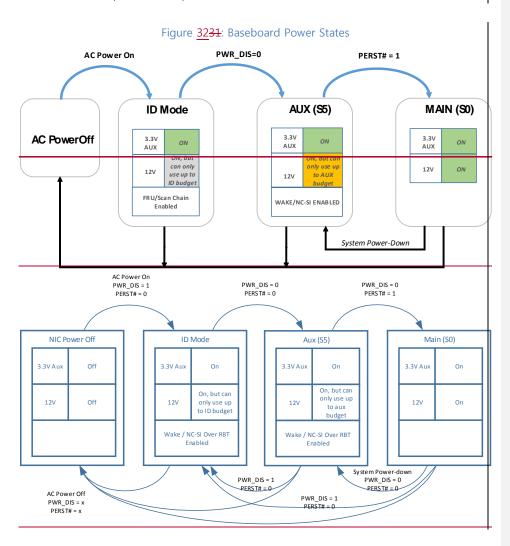

|                                                     | 3.9.1                             | NIC Power Off                                                       | <u>88</u> 8  |  |

|                                                     | 3.9.2                             | ID Mode                                                             | <u>88</u> 8  |  |

|                                                     | 3.9.3                             | Aux Power Mode (S5)                                                 | 88           |  |

|                                                     | 3.9.4                             | Main Power Mode (S0)                                                | 88           |  |

| 3.10 Power Supply R                                 |                                   | ower Supply Rail Requirements and Slot Power Envelopes              | 88           |  |

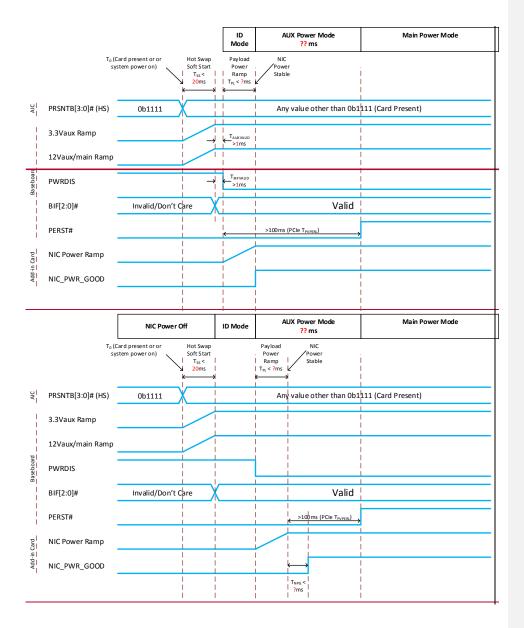

| 3.11 Hot Swap Considerations for 12V and 3.3V Rails |                                   | ot Swap Considerations for 12V and 3.3V Rails                       |              |  |

| 3.12                                                | 2 Po                              | ower Sequence Timing Requirements                                   | <u>90</u> 89 |  |

| Ma                                                  | nagem                             | ent                                                                 | <u>93</u> 91 |  |

| 4.1                                                 | Si                                | deband Management Interface and Transport                           | <u>93</u> 91 |  |

|                                                     |                                   |                                                                     |              |  |

| 4.2 |                              | NC-SI Traffic939                                    |                                             |                           |  |  |  |

|-----|------------------------------|-----------------------------------------------------|---------------------------------------------|---------------------------|--|--|--|

| 4.3 |                              | Management Controller (MC) MAC Address Provisioning |                                             |                           |  |  |  |

| 4.4 |                              | Temperature Reporting                               |                                             |                           |  |  |  |

| 4.5 |                              | Pow                                                 | er Consumption Reporting                    | <u>95<del>93</del></u>    |  |  |  |

| 4.6 |                              | Link                                                | Status/Speed Reporting                      | <u>95<del>93</del></u>    |  |  |  |

| 4.7 |                              | Plug                                                | ggable Module Status Reporting              | <u>96</u> 94              |  |  |  |

| 4.8 |                              | Out                                                 | -Of-Band Firmware Update                    | <u>97<del>95</del></u>    |  |  |  |

| 4.9 |                              | NC-                                                 | SI Over RBT Sideband Interface              | <u>97<del>95</del></u>    |  |  |  |

|     | 4.9.2                        | L                                                   | NC-SI Over RBT Addressing                   | <u>97<del>95</del></u>    |  |  |  |

|     | 4.9.2                        | 2                                                   | Arbitration Ring Connections                | <u>98</u> 96              |  |  |  |

| 4.1 | 0                            | SME                                                 | Bus 2.0 Interface                           | <u>98</u> 96              |  |  |  |

|     | 4.10                         | .1                                                  | SMBus Address Map                           | <u>98</u> 96              |  |  |  |

| 4.1 | 1                            | FRU                                                 | EEPROM                                      | <u>99</u> 97              |  |  |  |

|     | 4.11                         | .1                                                  | FRU EEPROM Address, Size and Availability   | <u>99</u> 97              |  |  |  |

|     | 4.11                         | .2                                                  | FRU EEPROM Content Requirements             | <u>100</u> 98             |  |  |  |

| 4.1 | 2                            | FW                                                  | Requirements                                | <u>102</u> 100            |  |  |  |

|     | 4.12                         | .1                                                  | Firmware Update                             | <u>102</u> 100            |  |  |  |

|     | 4.12                         | .2                                                  | Secure Firmware                             | <u>102<del>100</del></u>  |  |  |  |

|     | 4.12                         | .3                                                  | Firmware Queries                            | <u>102<del>100</del></u>  |  |  |  |

|     | 4.12                         | .4                                                  | Multi-Host Firmware Queries                 | <u>102<del>100</del></u>  |  |  |  |

| 4.1 | 3                            | The                                                 | rmal Reporting Interface                    | <u>103</u> 100            |  |  |  |

|     | 4.13                         | .1                                                  | Emulated Thermal Reporting                  | <u>103</u> <del>101</del> |  |  |  |

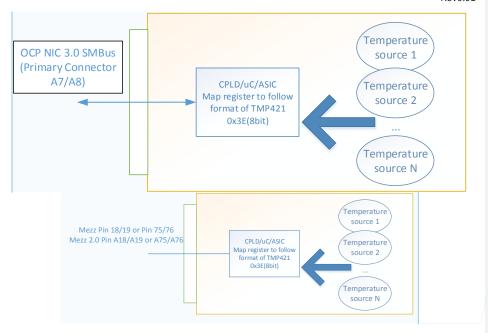

|     | 4.13                         | .2                                                  | Remote on-die sensing                       | <u>107</u> <del>104</del> |  |  |  |

|     | <mark>4.13</mark>            | .3                                                  | PLDM Method                                 | <u>109</u> 106            |  |  |  |

|     | 4.13                         | .4                                                  | Thermal reporting accuracy                  | <u>109</u> 106            |  |  |  |

| Da  | ta Ne                        | two                                                 | rk Requirements                             | <u>110<del>107</del></u>  |  |  |  |

| 5.1 |                              | Net                                                 | work Boot                                   | <u>110<del>107</del></u>  |  |  |  |

| Ro  | uting                        | Gui                                                 | delines and Signal Integrity Considerations | <u>111</u> 108            |  |  |  |

| 6.1 | 6.1 NC-SI Over RBT <u>11</u> |                                                     |                                             |                           |  |  |  |

| 6.2 | PCIe                         |                                                     |                                             |                           |  |  |  |

| The | erma                         | and                                                 | d Environmental                             | <u>112<del>109</del></u>  |  |  |  |

| 7.1 |                              | Envi                                                | ronmental Requirements                      | <u>112<del>109</del></u>  |  |  |  |

|     | 7.1.3                        | L                                                   | Thermal Reporting interface                 | 112 <del>109</del>        |  |  |  |

### Open Compute Project • NIC • 3.0

| _        | _  |   |

|----------|----|---|

| $D \sim$ | 'n | П |

| nΗ       | vu |   |

| • |                  | ······································  | <u></u>                 |

|---|------------------|-----------------------------------------|-------------------------|

| 8 | Revision History |                                         | 113 <del>11</del>       |

|   | 7.3              | Regulatory                              | <u>112<del>10</del></u> |

|   | 1.2              | SHOCK & VIDIATION                       | <u>112<del>10</del></u> |

|   | 7.2              | Shock & Vibration                       | 11210                   |

|   | /.               | 1.2 Memai Simulation Boundary Example   | <u>112</u> 10           |

|   | 7                | 1.2 Thermal Simulation Boundary Example | 11210                   |

## List of Figures

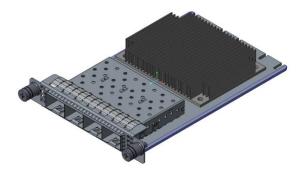

| Figure 1: Representative Small OCP NIC 3.0 Card with Quad SFP Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 10                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

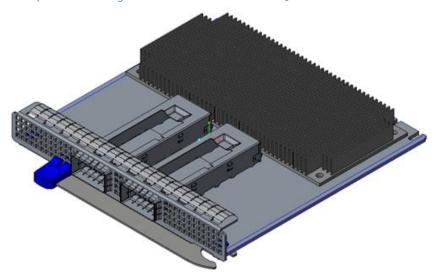

| igure 2: Representative Large OCP NIC 3.0 Card with Dual QSFP Ports and on-board DRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11                        |

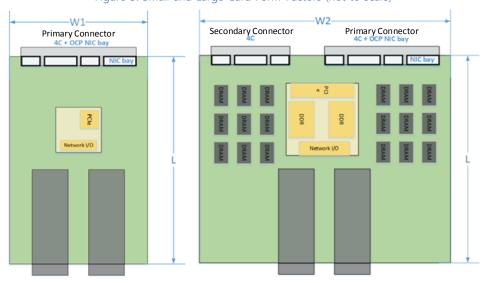

| Figure 3: Small and Large Card Form-Factors (not to scale)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 12                        |

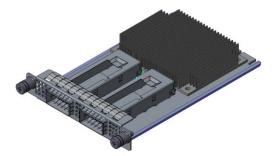

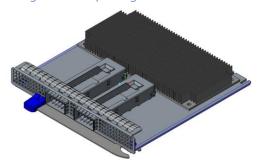

| igure 4: Example Small Card Form Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18                        |

| Figure 5: Example Large Card Form Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 19                        |

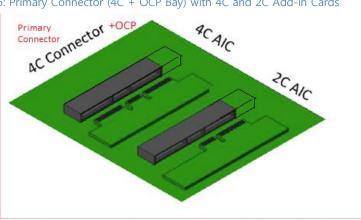

| Figure 6: Primary Connector (4C + OCP Bay) with 4C and 2C Add-in Cards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20                        |

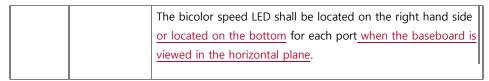

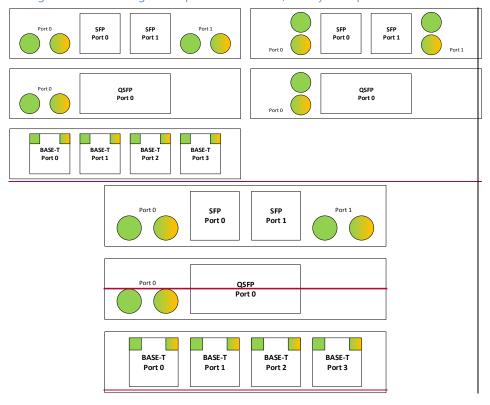

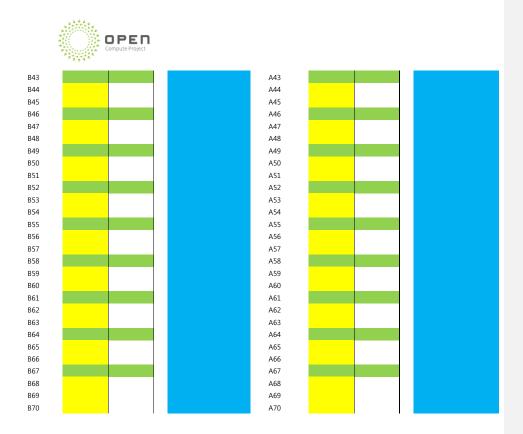

| igure 7: LED Ordering – Example Small Card Link/Activity and Speed LED Placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25                        |

| igure 8: Small Card Bottom Side Insulator and Mechanical Envelope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26                        |

| Figure 9: Large Card Bottom Side Insulator and Mechanical Envelope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 26                        |

| igure 10: Small Size Primary Connector Gold Finger Mating Card Dimensions – x16 – Top Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27                        |

| igure 11: Small Size Primary Connector Gold Finger Mating Card Dimensions – x16 – Bottom Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>28<del>27</del></u>    |

| igure 12: Large Size Card Gold Finger Mating Card Dimensions – x32 – Top Side                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <u>28<del>27</del></u>    |

| Figure 13: Large Size Card Gold Finger Mating Card Dimensions – x32 – Bottom SideSide in the control of t | <u>28</u> <del>27</del>   |

| igure 14: 168-pin Base Board Primary Connector – Right Angle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 30                        |

| Figure 15: 140-pin Base Board Secondary Connector – Right Angle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>31</u> 30              |

| igure 16: 168-pin Base Board Primary Connector – Straddle Mount                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>31</u> 30              |

| Figure 17: 140-pin Base Board Secondary Connector – Straddle Mount                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <u>31</u> 30              |

| Figure 18: Primary and Secondary Connector Locations for Large Card Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u>31</u> 30              |

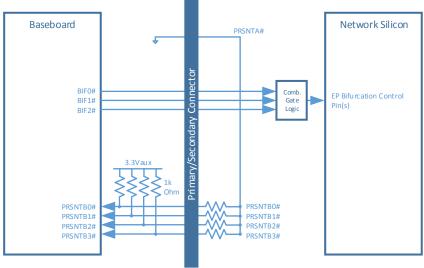

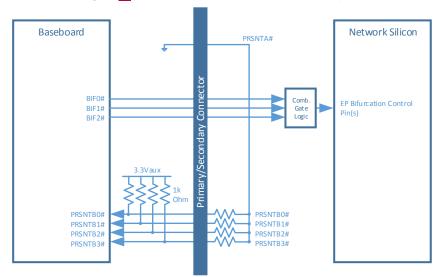

| Figure 19: PCIe Present and Bifurcation Control Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 43                        |

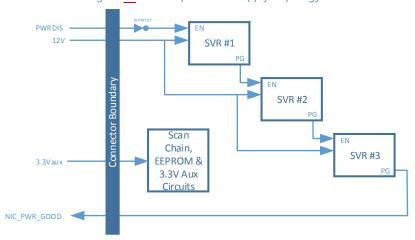

| Figure 20: Example Power Supply Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46                        |

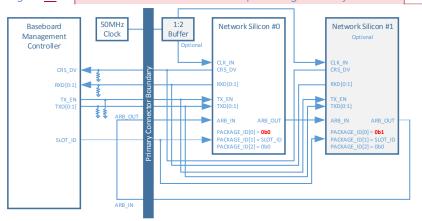

| Figure 21: NC-SI Over RBT Connection Example – Single Primary Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                        |

| Figure 22: NC-SI Over RBT Connection Example – Dual Primary Connector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 55                        |

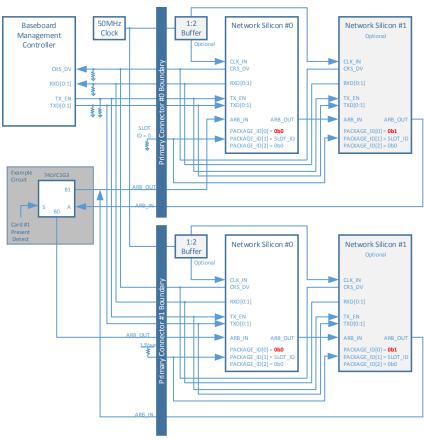

| igure 23: Scan Bus Connection Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 63                        |

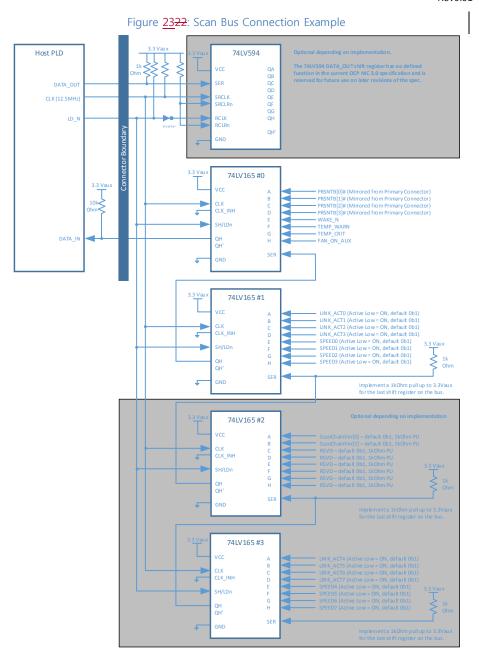

| igure 24: PCIe Bifurcation Pin Connections Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 66                        |

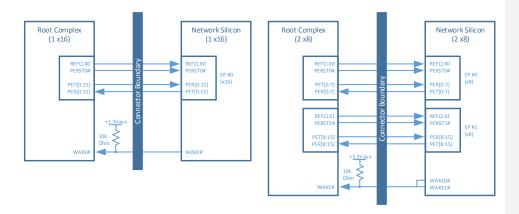

| Figure 25: Single Host (1 x16) and 1 x16 Add-in Card (Single Controller)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 70                        |

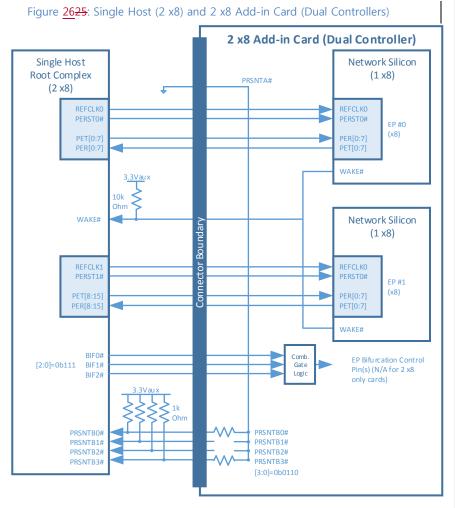

| Figure 26: Single Host (2 x8) and 2 x8 Add-in Card (Dual Controllers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 71                        |

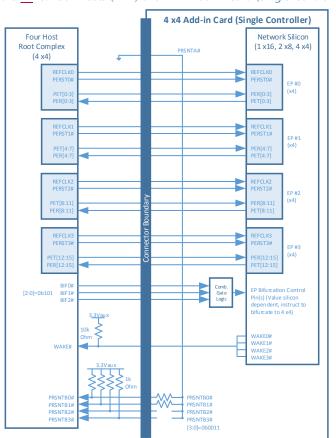

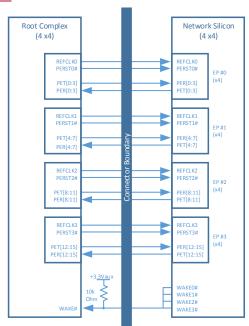

| igure 27: Four Hosts (4 x4) and 4 x4 Add-in Card (Single Controller)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 72                        |

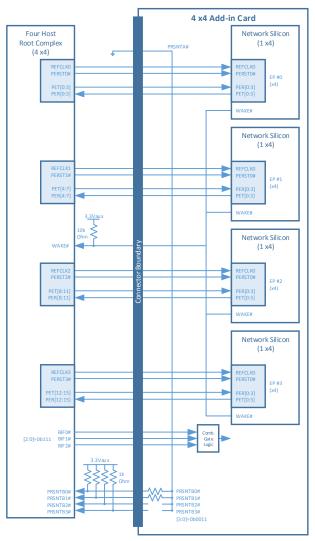

| Figure 28: Four Hosts (4 x4) and 4 x4 Add-in Card (Four Controllers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 73                        |

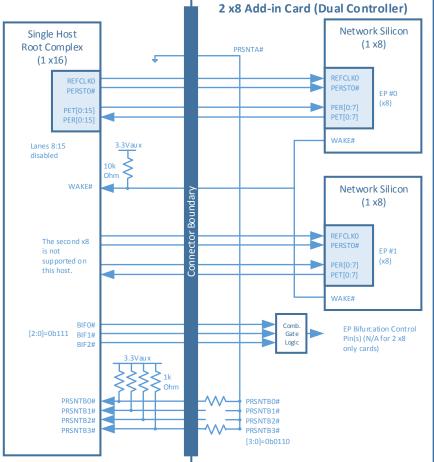

| Figure 29: Single Host with no Bifurcation (1 x16) and 2 x8 Add-in Card (Two Controllers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                        |