# **OCP NIC 3.0 Design Specification**

Version 0.01

Author: OCP Server Workgroup, OCP NIC subgroup

# Table of Contents

| 1 | Overvie           | 2W                                    | 7                      |

|---|-------------------|---------------------------------------|------------------------|

|   | 1.1               | License                               | 7                      |

|   | 1.2               | Background                            | 8                      |

|   | 1.3               | Acknowledgements                      | 9                      |

|   | 1.4               | Overview                              | 9                      |

|   | 1.4.              | .1 Mechanical Form factor overview    | 9                      |

|   | 1.4.              | .2 Electrical overview                | <u>13<del>12</del></u> |

|   | 1.5               | References                            | <u>13<del>12</del></u> |

| 2 | Card Fo           | orm Factor                            | <u>15</u> 14           |

|   | 2.1               | Overview                              | <u>15</u> 14           |

|   | 2.2               | Form Factor Options                   | <u>15</u> 14           |

|   | 2.3               | I/O bracket                           | <u>17<del>16</del></u> |

|   | 2.4               | Line Side I/O Implementations         | <u>17<del>16</del></u> |

|   | 2.5               | LED Implementation                    | <u>18</u> 17           |

|   | 2.6               | Mechanical Keepout Zones              | <u>19<del>18</del></u> |

|   | 2.6.              | .1 Baseboard Keep Out Zones           | <u>19<del>18</del></u> |

|   | 2.6.              | .2 Add-in Card Keep Out Zones         | <u>19<del>18</del></u> |

|   | 2.7               | Labeling Requirements                 | <u>20<del>19</del></u> |

|   | 2.8               | Insulation Requirements               | <u>20<del>19</del></u> |

|   | 2.9               | NIC Implementation Examples           | <u>20<del>19</del></u> |

|   | <mark>2.10</mark> | Non-NIC Use Cases                     | <u>20<del>19</del></u> |

|   | <mark>2.10</mark> | 0.1 PCIe Retimer card                 | <u>20</u> 19           |

|   | <mark>2.10</mark> | 0.2 Accelerator card                  | <u>20<del>19</del></u> |

|   | <mark>2.10</mark> | 0.3 Storage HBA / RAID card           | <u>20</u> 19           |

| 3 | Card Ed           | dge and Baseboard Connector Interface | <u>20<del>19</del></u> |

|   | 3.1               | Gold Finger Requirement               | <u>20<del>19</del></u> |

|   | 3.1.              | .1 Gold Finger Mating Sequence        | <u>22<del>21</del></u> |

|   | 3.2               | Baseboard Connector Requirement       | <u>25<del>23</del></u> |

|   | 3.3               | Pin definition                        | <u>26<del>24</del></u> |

#### Rev0.01

|   | 3.4  |      | Signal Descriptions – Common                                         | . <u>32<del>3</del>(</u> |

|---|------|------|----------------------------------------------------------------------|--------------------------|

|   |      | 3.4. | PCIe Interface Pins                                                  | . <u>32<del>3</del>(</u> |

|   |      | 3.4. | 2 PCIe Present and Bifurcation Control Pins                          | . <u>36<del>3</del>4</u> |

|   |      | 3.4. | 3 SMBus Interface Pins                                               | . <u>38<del>3</del>(</u> |

|   |      | 3.4. | 4 Power Supply Pins                                                  | . <u>40</u> 3            |

|   |      | 3.4. | 5 Miscellaneous Pins                                                 | . <u>41</u> 3            |

|   | 3.5  |      | Signal Descriptions – OCP Bay (Primary Connector)                    | . <u>41<del>3</del>9</u> |

|   |      | 3.5. | PCIe Interface Pins – OCP Bay (Primary Connector)                    | . <u>42<del>3</del>9</u> |

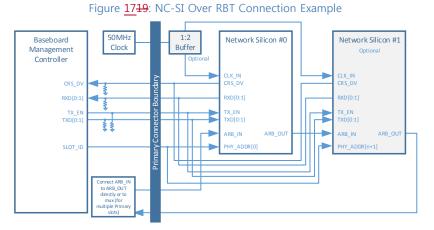

|   |      | 3.5. | 2 NC-SI Over RBT Interface Pins – OCP Bay (Primary Connector)        | . <u>44</u> 4            |

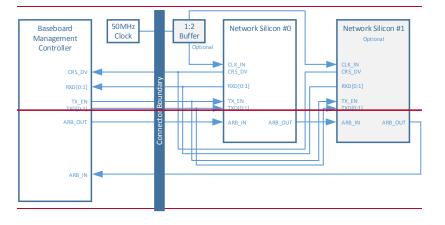

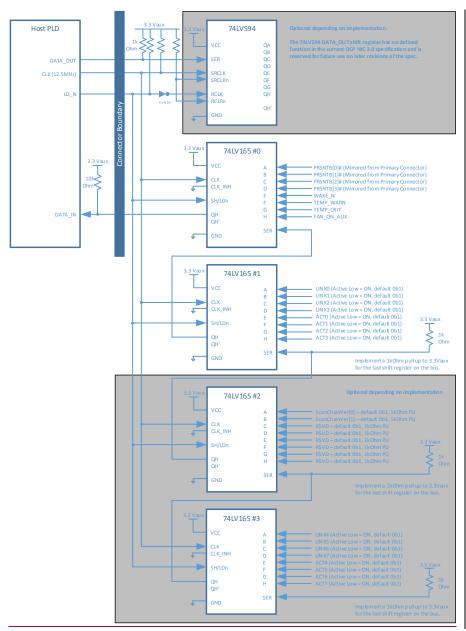

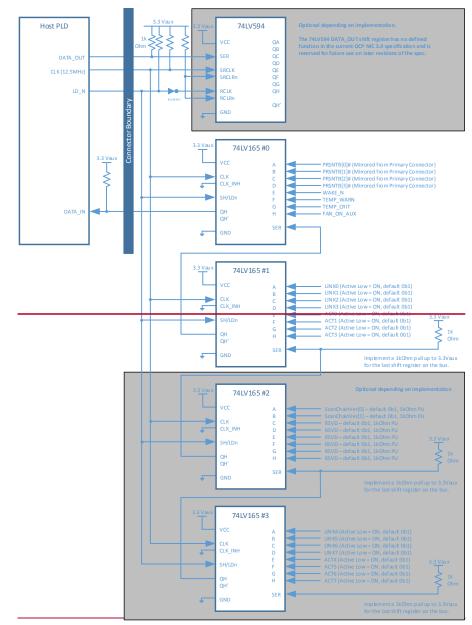

|   |      | 3.5. | 3 Scan Chain Pins – OCP Bay (Primary Connector)                      | . <u>50</u> 4(           |

|   |      | 3.5. | 4 Primary Connector Miscellaneous Pins – OCP Bay (Primary Connector) | . <u>58<del>5</del>4</u> |

|   | 3.6  |      | PCIe Bifurcation Mechanism                                           | . <u>60</u> 5!           |

|   |      | 3.6. | PCIe Add-in Card to Baseboard Bifurcation Configuration (PRSNTA#,    |                          |

|   |      | PRS  | NTB[3:0]#)                                                           | . <u>62<del>5</del>(</u> |

|   |      | 3.6. |                                                                      |                          |

|   |      | 3.6. | 3 PCIe Bifurcation Decoder                                           | . <u>63<del>5</del></u>  |

|   |      | 3.6. | Bifurcation Detection Flow                                           | . <u>66<del>5</del>9</u> |

|   |      | 3.6. | 5 PCIe Bifurcation Examples                                          | . <u>67<del>6</del>(</u> |

|   | 3.7  |      | PCIe Clocking Topology                                               | . <u>79</u> 6(           |

|   | 3.8  |      | PCIe Bifurcation Results and REFCLK Mapping                          | . <u>83<del>6</del></u>  |

|   | 3.9  |      | Power Capacity and Power Delivery                                    | .927                     |

|   |      | 3.9. | AC Power Off                                                         | . <u>937</u>             |

|   |      | 3.9. | 2 Management (FRU Only Mode)                                         | .937                     |

|   |      | 3.9. | 3 Aux Power Mode (S5)                                                | . <u>93</u> 7            |

|   |      | 3.9. | 4 Main Power Mode (S0)                                               | .937                     |

|   | 3.10 | )    | Add-in Card Input Capacitance                                        | . <u>93</u> 7            |

|   | 3.11 | 1    | Hot Swap Considerations for 12V and 3.3V Rails                       | .947                     |

|   | 3.12 | 2    | Power Sequence Timing Requirements                                   | .9479                    |

| 4 | Ma   | nage | ment                                                                 | . <u>96</u> 8(           |

|   | 4.1  |      | SMBus Interface                                                      | . <u>96</u> 8(           |

|   | 4.2  |      | NC-SI Sideband Interface                                             | . <u>96<del>8</del>(</u> |

|   |      | 4.2. | 1 NC-SI addressing and Arb#                                          | . <u>96</u> 8(           |

|   | 4.3  |      | MAC Address Requirement                                              |                          |

|   | 4.4     | FRU EEPROM                                              | <u>96</u> 80       |

|---|---------|---------------------------------------------------------|--------------------|

|   | 4.4     | 1.1 Minimum EEPROM Size                                 |                    |

|   | 4.4     | EEPROM Map Definition                                   | <u>96</u> 80       |

|   | 4.4     | I.3 EEPROM Address                                      | <u>97</u> 81       |

|   | 4.5     | FW Requirement (TBD)                                    | <u>97</u> 81       |

|   | 4.6     | Thermal Reporting Interface                             | <u>97</u> 81       |

| 5 | Data N  | letwork Requirement                                     | <u>98</u> 82       |

|   | 5.1     | Network Booting (collect view from OEMs and hyperscale) | <u>98</u> 82       |

| 6 | Routin  | g Guidelines and Signal Integrity Considerations        | <u>99</u> 83       |

|   | 6.1     | NC-SI Over RBT                                          | <u>99</u> 83       |

| 7 | Therm   | al and Environmental                                    | <u>99</u> 83       |

|   | 7.1     | Environmental Requirements                              | <u>99</u> 83       |

|   | 7.1     | 1.1 Thermal Simulation Boundary Example                 | <u>99</u> 83       |

|   | 7.2     | Shock & Vibration                                       | <u>99</u> 83       |

|   | 7.3     | Regulation                                              | <u>99</u> 83       |

| 8 | Revisio | on History                                              | 100 <del>8</del> 4 |

Rev0.01

# List of Figures

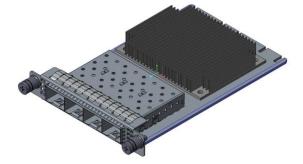

| Figure 1: Representative Small OCP NIC 3.0 Card with Quad SFP Ports                           | 8                        |

|-----------------------------------------------------------------------------------------------|--------------------------|

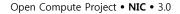

| Figure 2: Representative Large OCP NIC 3.0 Card with Dual QSFP Ports and on-board DRAM        | 9                        |

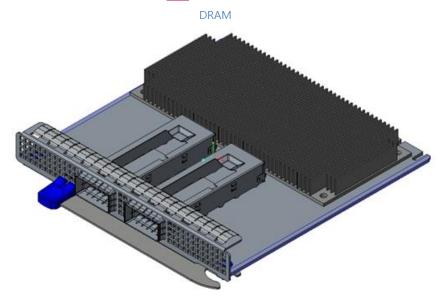

| Figure 3: Small and Large Card Form-Factors (not to scale)                                    | 10                       |

| Figure 4: Example Small Card Form Factor                                                      | <u>15</u> 14             |

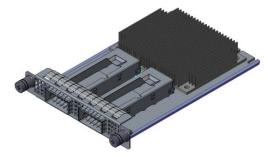

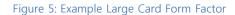

| Figure 5: Example Large Card Form Factor                                                      | <u>16</u> 15             |

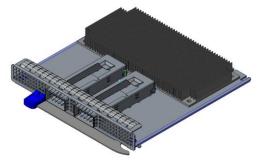

| Figure 6: Primary Connector (4C + OCP Bay) with 4C and 2C Add-in Cards                        | <u>17<del>16</del></u>   |

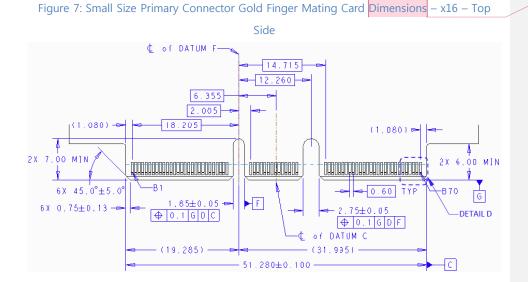

| Figure 7: Small Size Primary Connector Gold Finger Mating Card Dimensions – x16 – Top Side    | <u>21</u> 20             |

| Figure 8: Small Size Primary Connector Gold Finger Mating Card Dimensions – x16 – Bottom Side | <u>22<del>20</del></u>   |

| Figure 9: Large Size Card Gold Finger Mating Card Dimensions – x32 – Top Side                 | <u>22<del>20</del></u>   |

| Figure 10: Large Size Card Gold Finger Mating Card Dimensions – x32 – Bottom Side             | <u>22</u> 21             |

| Figure 11: 168-pin Base Board Primary Connector – Right Angle                                 | <u>25<del>23</del></u>   |

| Figure 12: 140-pin Base Board Secondary Connector – Right Angle                               | <u>25</u> 23             |

| Figure 13: 168-pin Base Board Primary Connector – Straddle Mount                              | <u>25<del>23</del></u>   |

| Figure 14: 140-pin Base Board Secondary Connector – Straddle Mount                            | <u>25</u> 24             |

| Figure 15: Primary and Secondary Connector Locations for Large Card Support                   | <u>26<del>2</del>4</u>   |

| Figure 16: PCIe Present and Bifurcation Control Pins                                          | <u>37</u> 35             |

| Figure 17: NC-SI Over RBT Connection Example                                                  | <u>49</u> 4 <del>6</del> |

| Figure 18: Scan Bus Connection Example                                                        |                          |

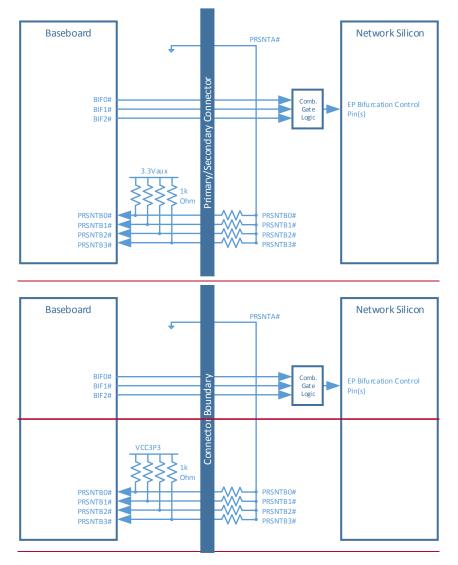

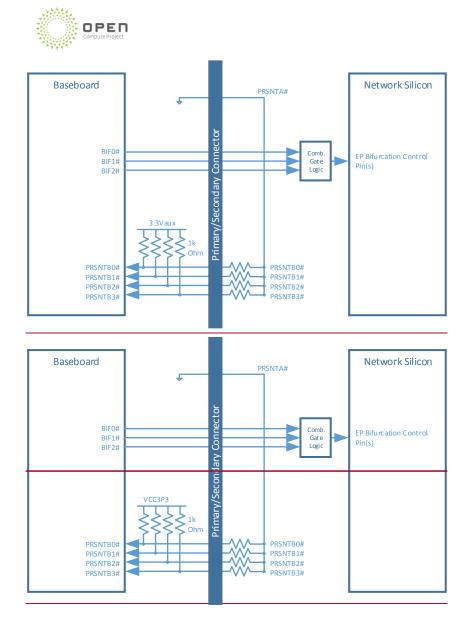

| Figure 19: PCIe Bifurcation Pin Connections Support                                           | <u>61</u> 55             |

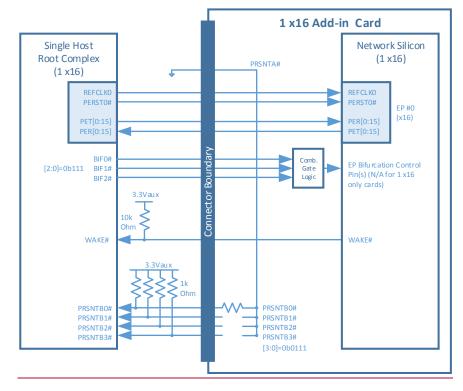

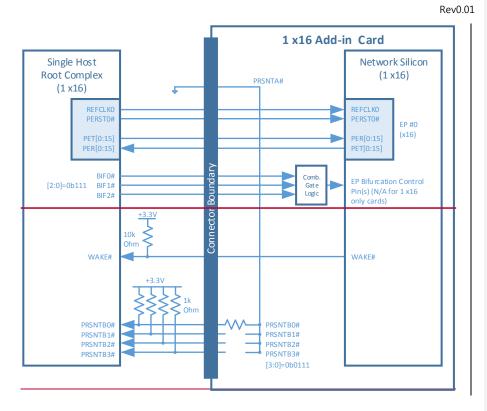

| Figure 20: Single Host (1 x16) and 1 x16 Add-in Card (Single Controller)                      | <u>67<del>60</del></u>   |

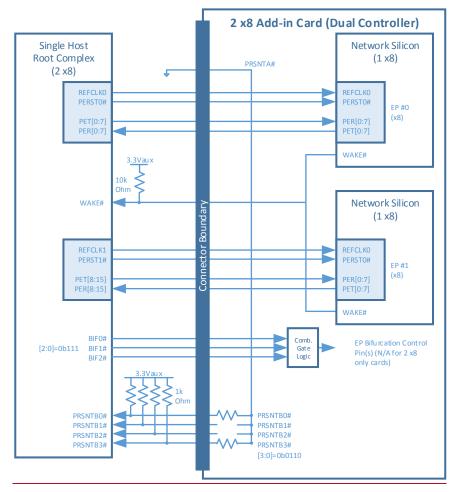

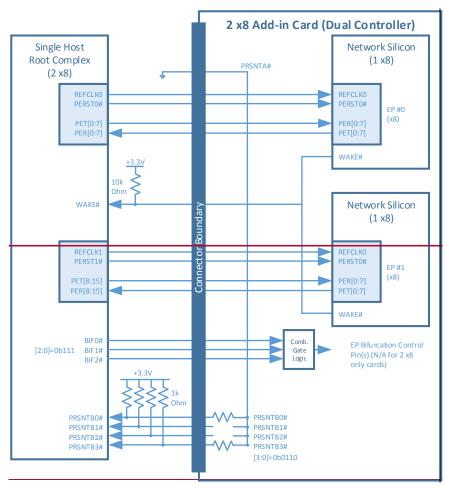

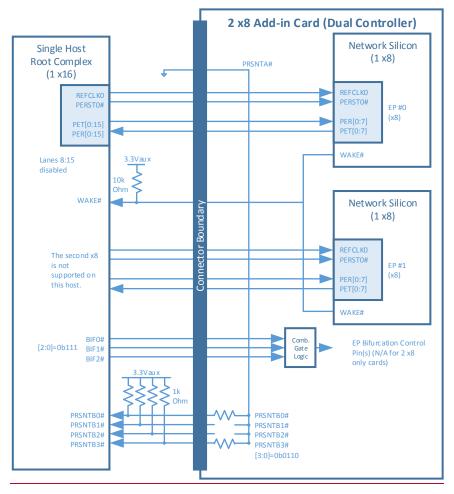

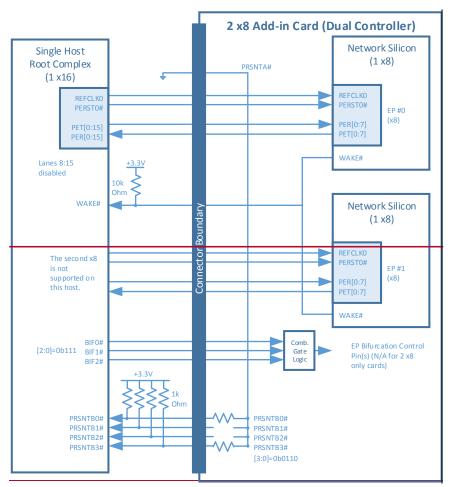

| Figure 21: Single Host (2 x8) and 2 x8 Add-in Card (Dual Controllers)                         | <u>69</u> 61             |

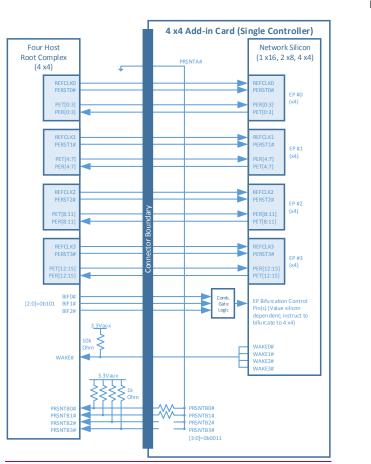

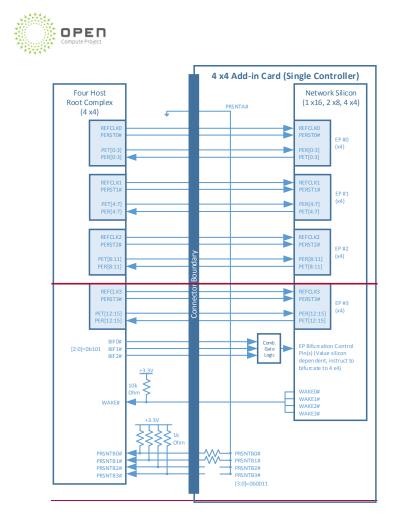

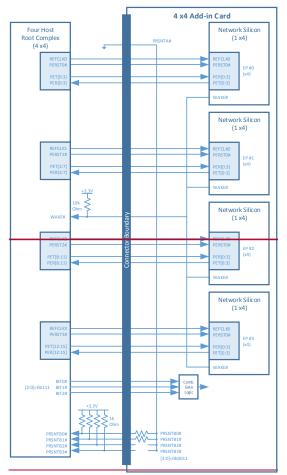

| Figure 22: Four Hosts (4 x4) and 4 x4 Add-in Card (Single Controller)                         | <u>72<del>62</del></u>   |

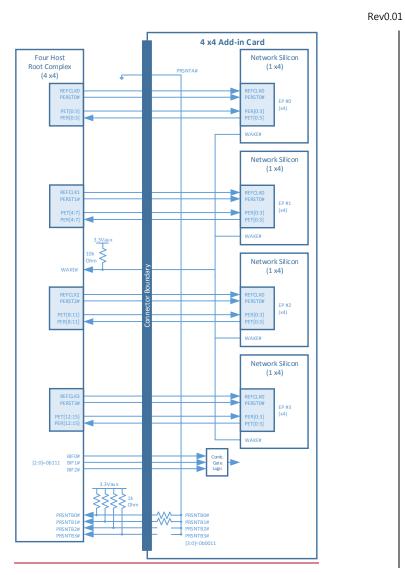

| Figure 23: Four Hosts (4 x4) and 4 x4 Add-in Card (Four Controllers)                          | <u>74<del>63</del></u>   |

| Figure 24: Single Host with no Bifurcation (1 x16) and 2 x8 Add-in Card (Two Controllers)     | <u>77<del>65</del></u>   |

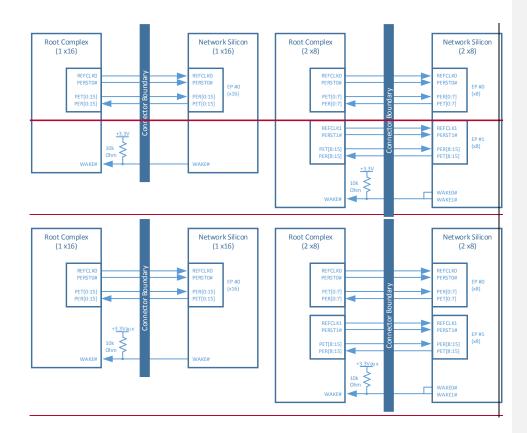

| Figure 25: PCIe Interface Connections for 1 x16 and 2 x8 Add-in Cards                         | <u>80</u> 66             |

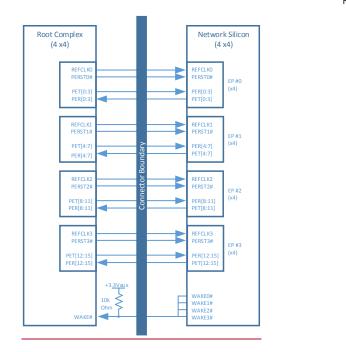

| Figure 26: PCIe Interface Connections for a 4 x4 Add-in Card                                  | <u>81</u> 67             |

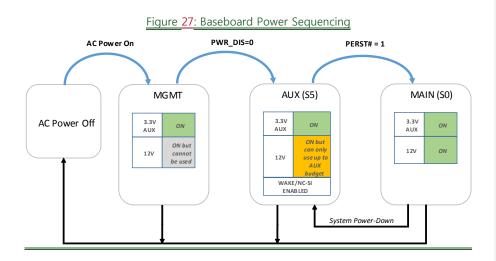

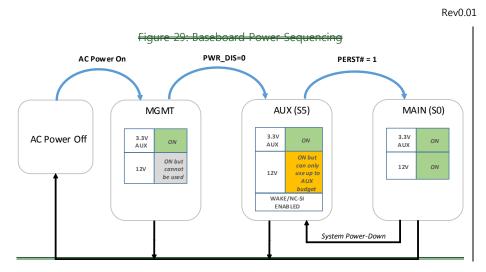

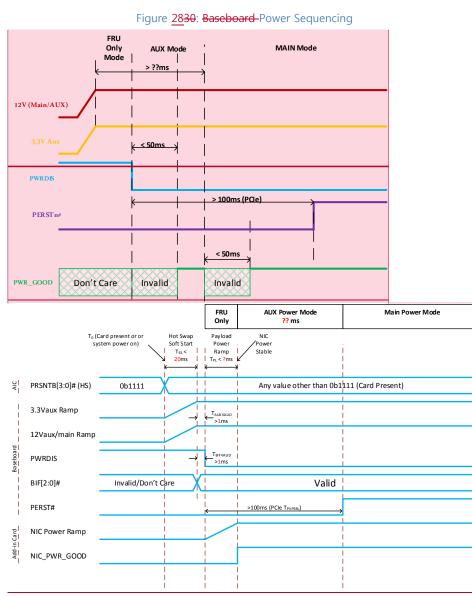

| Figure 27: Baseboard Power Sequencing                                                         | <u>92</u> 77             |

| Figure 28: Power Sequencing                                                                   | <u>95</u> 79             |

# List of Tables

| Table 1: OCP 3.0 Form Factor Dimensions                                                                         |

|-----------------------------------------------------------------------------------------------------------------|

| Table 2: Baseboard to OCP NIC Form factor Compatibility Chart                                                   |

| Table 3: OCP NIC 3.0 Card Definitions                                                                           |

| Table 4: OCP 3.0 Line Side I/O Implementations                                                                  |

| Table 5: Default LED Configuration                                                                              |

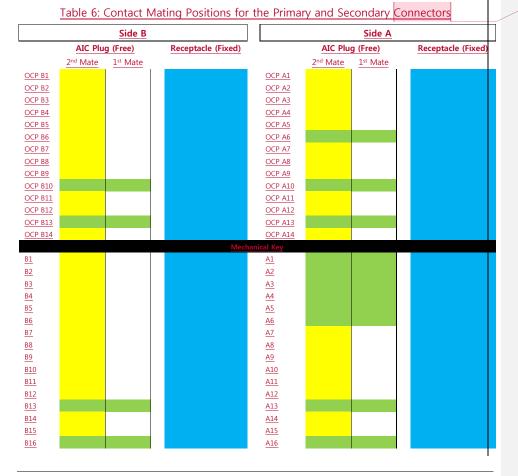

| Table 6: Contact Mating Positions for the Primary and Secondary Connectors                                      |

| Table 7: Primary Connector Pin Definition (x16) (4C + OCP Bay)                                                  |

| Table 8: Secondary Connector Pin Definition (x16) (4C)                                                          |

| Table 9: Pin Descriptions – PCIe 1                                                                              |

| Table 10: Pin Descriptions – PCIe Present and Bifurcation Control Pins                                          |

| Table 11: Pin Descriptions – SMBus                                                                              |

| Table 12: Pin Descriptions – Power                                                                              |

| Table 13: Pin Descriptions – Miscellaneous 1                                                                    |

| Table 14: Pin Descriptions – PCIe 2                                                                             |

| Table 15: Pin Descriptions – NC-SI Over RBT                                                                     |

| Table 16: Pin Descriptions – Scan Chain                                                                         |

| Table 17: Pin Descriptions – Scan Chain DATA_OUT Bit Definition                                                 |

| Table 18: Pin Descriptions – Scan Bus DATA_IN Bit Definition                                                    |

| Table 19: Pin Descriptions – Miscellaneous 2                                                                    |

| Table 20: PCIe Bifurcation Decoder for x16 and x8 Card Widths                                                   |

| Table 21: PCIe Clock Associations                                                                               |

| Table 22: Bifurcation for Single Host, Single Socket and Single Upstream Link (BIF[2:0]#=0b000)                 |

| Table 23: Bifurcation for Single Host, Single Socket and Single/Dual Upstream Links (BIF[2:0]#=0b000)           |

| Table 24: Bifurcation for Single Host, Single Socket and Single/Dual/Quad Upstream Links (BIF[2:0]#=0b000).8671 |

| Table 25: Bifurcation for Single Host, Dual Sockets and Dual Upstream Links (BIF[2:0]#=0b001)                   |

| Table 26: Bifurcation for Single Host, Four Sockets and Dual Upstream Links (BIF[2:0]#=0b010)                   |

| Table 27: Bifurcation for Dual Host, Dual Sockets and Dual Upstream Links (BIF[2:0]#=0b101)                     |

| Table 28: Bifurcation for Quad Host, Quad Sockets and Quad Upstream Links (BIF[2:0]#=0b110)                     |

| Table 29: Bifurcation for Quad Host, Quad Sockets and Quad Upstream Links (BIF[2:0]#=0b110)                     |

| Table 30: Power Envelopes                                                                                       |

| Table 31: Power Supply Rail Requirements <u>9378</u>                                                            |

| Table 32: Power Sequencing Parameters                                                                           |

|                                                                                                                 |

Rev0.01

# 1 Overview

## 1.1 License

As of April 7, 2011, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0: Facebook, Inc.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at http://opencompute.org/licensing/, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, noninfringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

#### 1.2 Background

The OCP NIC 3.0 specification is a follow-on to the OCP 2.0 form-factor for PCIe add-in cards. The OCP NIC 3.0 specification supports two basic card sizes: Small Card, and Large Card. The Small Card allows for up to 16 PCIe lanes on the card edge while a Large Card supports up to 32 PCIe-lanes on the card edge. Compared to the OCP NIC 2.0 release, the updated specification provides a broader solution space for NIC and system vendors to support the following use case<del>s</del> scenarios:

- NICs with a higher TDP

- Support up to 79W of power delivery to a single connector (Small) card; and 158W to a dual connector (Large) card

- PCIe Gen4 and Gen5 on the system and add-in card

- Support for upto 32 lanes of PCIe per add-in card

- Support for single host and multi-host environments

- Support a greater board area for more complex add-in card designs

- Support for Smart NIC implementations with on-board DRAM

- Simplification of FRU installation and removal while reducing overall down time

A representative Small Card OCP 3.0 NIC mezzanine card is shown in Figure 1 and a representative Large Card is shown in Figure  $2_{\underline{}}$

Figure 1: Representative Small OCP NIC 3.0 NIC-Card with Quad SFP Ports

Rev0.01

Figure 2: Representative Large OCP\_NIC 3.0 NIC-Card with Dual QSFP Ports and on-board

<u>In order to achieve the features outlined in this specification</u>, OCP 3.0 compliant cards are not backwards compatible to the 2.0 cards in order to achieve the features outlined in this specification.

This specification is created under OCP Server workgroup – OCP NIC subgroup. An electronic copy of this specification can be found on the Open Compute Project website:

http://www.opencompute.org/wiki/Server/Mezz#Specifications\_and\_Designs

# 1.3 Acknowledgements

<mark>Placeholder</mark>

## 1.4 Overview

#### 1.4.1 Mechanical Form factor overview

The OCP NIC 3.0 specification defines a third generation mechanical form factor that allows for interoperability between specification compliant systems-baseboards and add-in cards.

OCP NIC 3.0 cards have two form factors – Small and Large. These cards are shown in Figure 3 below. The components shown in the figures are for illustrative purposes. The Small form factor card has one connector (Primary connector) on baseboard. The Large form factor card has two connectors (Primary Connector and Secondary Connector) on the baseboard. Both the Primary and Secondary connectors are defined in and compliant to SFF-TA-1002. [Editor's note: plan to submit change back to SFF-TA-1002]. On the NIC side, the card edge is implemented with gold fingers. The gold finger design follows SFF-TA-1002 as well.

Figure 3: Small and Large Card Form-Factors (not to scale)

Open Compute Project • NIC • 3.0

The two form factor dimensions are shown in Table 1.

Table 1: OCP 3.0 Form Factor Dimensions

| Form   | Width                 | Depth          | Primary         | Secondary | Typical Use Case                            |

|--------|-----------------------|----------------|-----------------|-----------|---------------------------------------------|

| Factor |                       |                | Connector       | Connector |                                             |

| Small  | W1_=_76               | <u>L = 115</u> | 4C_+ OCP        | N/A       | Low profile and general NIC                 |

|        | <u>mm</u>             | mm             | sideband        |           | in-with a similar profile as                |

|        |                       |                | <u>168 pins</u> |           | an_OCP NIC 2.0 add-in card;                 |

|        |                       |                |                 |           | up to x16 PCIe. <del>-lanes</del>           |

| Large  | <mark>W2_=_139</mark> | <u>L = 115</u> | 4C_+ OCP        | 4C        | Largest Larger PCB width to                 |

|        | mm                    | mm             | sideband        | 140 pins  | support feature rich NICs <del>,</del>      |

|        | <del>[to be</del>     |                | 168 pins        |           | <del>and up to x32 PCIe<u>.</u> lanes</del> |

|        | confirmed]            |                |                 |           |                                             |

The OCP <u>NIC</u> 3.0 <u>NIC</u>-design allows downward compatibility between the two <u>card</u> sizes. Table 2 shows the compatibility between the baseboard and NIC combinations. <u>A small size</u> <u>baseboard slot may only accept a small sized NIC</u>. A Large size baseboard slot may accept a small or large sized NIC. <u>A small size baseboard slot may only accept a small sized NIC</u>.

Table 2: Baseboard to OCP NIC Form factor Compatibility Chart

| Baseboard | NIC Size / Supported PCIe Width |               |  |  |  |

|-----------|---------------------------------|---------------|--|--|--|

| Slot Size | Small                           | Large         |  |  |  |

| Small     | Up to x16                       | Not Supported |  |  |  |

| Large     | Up to x16                       | Up to x32     |  |  |  |

There are two baseboard connector options available for system designers: straddle mount and right angle (RA). The straddle mount connector option allows the OCP NIC and baseboard to exist in a co-planer position. To achieve this, a cutout exists on the baseboard and is defined in this specification. Alternatively, the right angle option allows the OCP NIC to be installed on top of the baseboard. A baseboard cutout is not required for the right angle connector. The right angle option allows the base-board to use this area for additional baseboard-routing or backside component placement. The straddle mount and right angle connectors are shown in Section 3.24.2.

For both the baseboard and OCP card, this specification defines the component and routing keep out areas. Refer to Section 2.63.6 for details.

Both the straddle mount and right angle implementations shall <u>use-accept</u> the same OCP <u>NIC-add-in card</u> and shall be supported in the baseboard chassis regardless of the baseboard connector selection (right angle or straddle mount) so long as the baseboard slot side and <u>NIC-add-in card</u> sizes are a supported combination as shown in Table 2.

This specification defines <u>the</u> form factor at <u>the NIC module\_add-in card</u> level, including the front panel, latch<u>inges\_mechanism</u> and card guide features [TBD; pending on the Mechanical work across stakeholders].

More details about the card form-factor is shown in Section 23.

#### 1.4.2 Electrical overview

This specification defines <u>the</u> electrical interface between baseboard<del>/system</del> and <u>the add-in</u> card<del>/NIC module</del>.

The electrical interface is implemented with a right angle or straddle mount connector on baseboard and gold finger on the add-in card. As previously noted in the mechanical overview, each card may implement a Primary Connector or Primary + Secondary Connector. Cards using only the Primary connector are suitable for both the Small and Large form-factors and may support up to x16 lanes of PCIe. The Secondary connector, when used in conjunction with the Primary <u>connector</u>, allows Large form-factor implementations and may support up to 32 lanes of PCIe.

1.4.2.1 Primary Connector

#### 1.4.2.2 Secondary connector

# 1.5 References

DMTF Standard. DSP0222, Network Controller Sideband Interface (NC-SI) Specification.

Distributed Management Task Force, Inc, Rev 1.0.1, January 24<sup>th</sup>, 2013.

**Commented [TN1]:** References need to be correctly sited per MLA standards.

Q: How do we handle references to unpublished (draft) specifications?

- EDSFF. *Enterprise and Datacenter SSD Form Factor Connector Specification*. Enterprise and Datacenter SSD Form Factor Working Group, Rev 0.9 (draft), August 2<sup>nd</sup> 2017.

- NXP Semiconductors. *PC-bus specification and user manual*. NXP Semiconductors, Rev 6, April 4<sup>th</sup>, 2014.

- Open Compute Project. *OCP NIC Subgroup*. Online. <u>http://www.opencompute.org/wiki/Server/Mezz</u>

- PCIe Base Specification. PCI Express Base Specification, Revision 4.0 (draft).

- PCIE-PCIe CEM Specification. PCI Express Card Electromechanical Specification, Revision 4.0 (draft).

- SMBus <u>Management Interface Forum</u>. System Management Bus (SMBus) specificationSpecification. System Management Interface Forum, Inc, Version 3.0, December 20<sup>th</sup>, 2014.

- SNIA. SFF-TA-1002, Specification for Protocol Agnostic Multi-Lane High Speed Connector. SNIA SFF TWG Technology Affiliate, Rev 0.0.9.1, September 9<sup>th</sup>, 2017.

Rev0.01

## 2 Card Form Factor

#### 2.1 Overview

#### 2.2 Form Factor Options

OCP3.0 provides two fundamental form factor options: a small card (76mm x 115mm) and a large card (139mm x 115mm).

These form factors support a Primary Connector and optionally, a Secondary Connector. The Primary Connector is defined to be a SFF-TA-1002 compliant 4C connector plus a 28-pin bay for OCP 3.0 specific pins. The Secondary Connector is the 4C connector as defined in SFF-TA-1002. The 4C specification supports up to 32 differential pairs for a x16 PCIe connection per connector. For host platforms, the 28-pin OCP bay is required for the Primary connector. This is also mandatory for add-in cards.

The small card uses the 4C connector for up to a x16 PCIe interface. The small cards implement the and additional 28-28-pin OCP bay for management functions and support for up to a four PCIe hosts. The small size card provides sufficient faceplate area to accommodate up to 2x QSFP modules, 4x SFP modules, or 4x RJ-45 for BASE-T operation. The small card form factor supports up to 79W of delivered power to the card edge.

Figure 4: Example Small Card Form Factor

**Commented [TN2]:** Are we going to uprev the SFF-TA spec to include these 28 pins?

The large card uses provides the same functionality as the small card, but with support up to a x32 PCIe interface. The large card utilizes both the Primary and Secondary connectors. The large size card supports higher power envelopes and provides additional board area for more complex designs. The small card form factor supports up to 158W of delivered power to the card edge at 79W per connector.

For both form-factors, an add-in card may optionally implement a subset of pins to support a x8 PCIe connection. This is implemented using a 2C <u>connector\_card edge</u> per SFF-TA-1002. The Primary Connector may support a 2C sized add<u>-</u>-in card along with the 28 pin OCP bay. The following diagram from the SFF-TA-1002 specification illustrates the supported host Primary and Secondary Connectors and add-<u>-</u>in card configurations.

Rev0.01

**Commented [TN3]:** This needs to be updated to show the OCP bay along with the secondary connector location..

#### Table 3

Table 3summarizes the supported card form factors. Small form factors cards support thePrimary Connector and up to 16 PCIe lanes. Large form factor cards support both thePrimary and Secondary Connectors and up to 32 PCIe lanes.

| Table 3: OCP <u>NIC</u> 3.0 Card Definitions |                                                            |              |                        |    |         |  |  |

|----------------------------------------------|------------------------------------------------------------|--------------|------------------------|----|---------|--|--|

| Add in Card Size and                         | Add in Card Size and Secondary Connector Primary Connector |              |                        |    |         |  |  |

| max PCIe Lane Count                          | 4C Connect                                                 | or, x16 PCIe | 4C Connector, x16 PCIe |    | OCP Bay |  |  |

| Small (x8)                                   |                                                            |              |                        | 2C | OCP Bay |  |  |

| Small (x16)                                  |                                                            |              | 4C                     |    | OCP Bay |  |  |

| Large <del>1 (</del> x24)                    |                                                            | 2C           | 4C                     |    | OCP Bay |  |  |

| Large <del>2 (</del> x32)                    | 4                                                          | С            | 4C (                   |    | OCP Bay |  |  |

#### 2.3 I/O bracket

TBD <need input from OCP mechanical groups>

## 2.4 Line Side I/O Implementations

At the time of this writing, the Small and Large form-factor cards may support the following standard line side I/O implementations:

Table 4: OCP 3.0 Line Side I/O Implementations

| Form Factor | Max Topology Connector Count |

|-------------|------------------------------|

| Small       | 2x QSFP28                    |

| Small       | 4x SFP28                     |

| Small       | 4x RJ-45                     |

| Large       | TBD                          |

| Large       | TBD                          |

| Large       | TBD                          |

Additional combinations are permissible as I/O <u>form-factor</u> technologies and thermal capabilities evolve.

#### 2.5 LED Implementation

A small form-factor OCP <u>NIC</u> 3.0 <u>NIC</u> with a fully populated I/O bracket (2x QSFP28, 4x SFP28, or 4x\_RJ-45)<del>, there is has</del> insufficient space for on-board <u>(faceplate)</u> LED indicators. In this case, the line side link and activity LED indicators are implemented on the baseboard system via the Scan Chain. The Scan Chain bit stream is defined in Section <u>3.5.34.5.3</u>.

For small form-factor low I/O count cards (such as 1x QSFP28, 2x\_SFP28, or 2x\_RJ-45), or a large form-factor OCP 3.0 NIC, where additional I/O bracket area is available, the card may optionally implement on-board link/activity indications in addition to the Scan Chain-LED.

For both cases, the OCP\_<u>NIC\_</u> 3.0 specification recommends the following LED definitions:

#### Table 5: Default LED Configuration

| LED Pin | LED Color | Description                                                                                                                                                                                                   | Commented [TN4]: The current Link/activity LED                                                                                                                                                   |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Link    | Green     | Active low. Multifunction LED.                                                                                                                                                                                | definition does not communicate the idea of "linked at<br>max rate" vs "linked at less than max rate"                                                                                            |

|         |           | When lit and solid, this LED is used to indicate the link is up at<br>the MAC level. Local and Remote Faults are clear and the link is<br>ready for data transmission. When the LED is off, the physical link | Do we optionally want to change the LED stream<br>definition such that there is "Speed A (max)" and "Speed<br>B (not max)" then multiplex the activity (via blink) on to<br>the illuminated LED? |

|         |           | is down or disabled.                                                                                                                                                                                          |                                                                                                                                                                                                  |

Rev0.01

|          |       | This LED indicator may also be used for port identification         |

|----------|-------|---------------------------------------------------------------------|

|          |       |                                                                     |

|          |       | through vendor specific link diagnostic software.                   |

|          |       |                                                                     |

|          |       | The link LED shall be located on the left hand side of each port.   |

| Activity | Green | Active low.                                                         |

|          |       |                                                                     |

|          |       | The Activity LED shall only be illuminated when the Link LED is     |

|          |       | illuminated.                                                        |

|          |       | murrinateu.                                                         |

|          |       |                                                                     |

|          |       | When lit and solid, this LED is used to indicate the port is "idle" |

|          |       | and no data is being transmitted or received.                       |

|          |       |                                                                     |

|          |       | When lit and blinking, this LED is used to indicate the port is     |

|          |       |                                                                     |

|          |       | "active" and data is either being transmitted or received.          |

|          |       |                                                                     |

|          |       | When the LED is off, no link is detected.                           |

|          |       |                                                                     |

|          |       | The activity LED shall be located on the right hand side of each    |

|          |       | port.                                                               |

|          |       | Port                                                                |

At the time of this writing, the Scan Chain definition allows for up to one link and one activity LED per port. A total of up to 8 ports are supported in the Scan Chain. The bit stream defines the LEDs to be active low (ON). The Scan Chain LED implementation allows the NIC LED indicators to be remotely located on the OCP\_3.0 compliant chassis (e.g. front LED indicators with rear I/O cards).

#### 2.6 Mechanical Keepout Zones

2.6.1 Baseboard Keep Out Zones

TBD – Need keepout drawings and envelopes for small / large size baseboard including primary/secondary/rail keepouts/cutout for straddle mount/keepout for right angle.

2.6.2 Add-in Card Keep Out Zones

TBD – need keepout drawings and envelopes for small / large size NIC including primary/secondary/rail keepouts.

# 2.7 Labeling Requirements

#### 2.8 Insulation Requirements

All cards must implement a secondary side insulator to prevent the bottom side card components from shorting out to the chassis. The recommended insulator thickness is 0.25mm and must reside within the following mechanical envelope for the Small and Large size cards:

TBD <need 2D drawings>

# 2.9 NIC Implementation Examples

2.10 Non-NIC Use Cases "PCIe interface with extra management sideband"

2.10.1 PCIe Retimer card

- 2.10.2 Accelerator card

- 2.10.3 Storage HBA / RAID card

# 3 Card Edge and Baseboard Connector Interface

# 3.1 Gold Finger Requirement

**Editor's note:** Connector vendors to provide input and all detailed views from the mechanical drawing. First stab at it is below. Diagrams are copied from SFF TA 1002.

The OCP NIC 3.0 add-in cards are compliant to the SFF-TA-1002 specification with respect to the gold fingers and connectors.

Rev0.01

Small Size cards may fit in the Primary Connector-or the Secondary Connector. Primary Connector compliant cards are 76mm x 115mm and may implement the full 168-pins. Secondary Connector compliant cards are XXXmm x 115mm and may implement the 140pin gold finger. Both tThe Primary and Secondary Connector cards may optionally implement a subset of gold finger pins if there is a reduced PCIe width requirement (such as 1 x8 and below). In this case, the card edge gold finger may implement a 2C design. The overall board thickness is 1.60mm. The gold finger dimensions for the Primary Connector and Secondary Connector-compliant cards are shown below.

Large Size Cards support up to a x32 PCIe implementation and uses both the Primary and Secondary connectors.

For additional details, refer to the card and connector mechanical drawings located in XXX.

Note: The "B" pins on the connector are associated with the top side of the add-in card. The "A" pins on the connector are associated with the bottom side of the add-in card.

**Commented [TN5]:** Drawing was pulled from SFF-TA-1002 FIGURE 5-18.

Rev0.01

application, some pin locations are used for single ended control nets or power and would benefit from a shorter pin length for staggering. As such, the recommended add-in card gold finger staging is shown in Table 6 for a two stage, first-mate, last-break functionality. The host connectors have a single stage mating and do not implement different pin lengths.

The AIC Plug (Free) side refers to the add-in card gold fingers; the receptacle (Fixed) side refers to the physical connector on the host platform. This table is based on the SFF-TA-1002 Table A-1 with modifications for OCP NIC 3.0. Refer to the mechanical drawings for pin the first-mate and second-mate lengths.

**Commented [TN11]:** (View this in Simple Markup mode to see the color coding)

| 4<br>4<br>4<br>4         | OPER<br>Compute Project |              |                          |  |  |

|--------------------------|-------------------------|--------------|--------------------------|--|--|

| <u>B17</u>               |                         |              | <u>A17</u>               |  |  |

| <u>B18</u>               |                         |              | <u>A18</u>               |  |  |

| B19                      |                         |              | <u>A19</u>               |  |  |

| <u>B20</u>               |                         |              | <u>A20</u>               |  |  |

| <u>B21</u>               |                         |              | <u>A21</u>               |  |  |

| <u>B22</u>               |                         |              | A22                      |  |  |

| <u>B23</u>               |                         |              | A23                      |  |  |

| <u>B24</u><br><u>B25</u> |                         |              | A24<br>A25               |  |  |

| B26                      |                         |              | A26                      |  |  |

| B27                      |                         |              | A27                      |  |  |

| B28                      |                         |              | A28                      |  |  |

|                          |                         | Mecha        | nical Key                |  |  |

| <u>B29</u>               |                         |              | <u>A29</u>               |  |  |

| <u>B30</u>               |                         |              | <u>A30</u>               |  |  |

| <u>B31</u>               |                         |              | <u>A31</u>               |  |  |

| <u>B32</u>               |                         |              | <u>A32</u>               |  |  |

| <u>B33</u>               |                         |              | <u>A33</u>               |  |  |

| <u>B34</u><br><u>B35</u> |                         |              | <u>A34</u><br><u>A35</u> |  |  |

| B36                      |                         |              | A36                      |  |  |

| <u>B37</u>               |                         |              | A37                      |  |  |

| B38                      |                         |              | A38                      |  |  |

| B39                      |                         |              | A39                      |  |  |

| <u>B40</u>               |                         |              | <u>A40</u>               |  |  |

| <u>B41</u>               |                         |              | <u>A41</u>               |  |  |

| <u>B42</u>               |                         |              | <u>A42</u>               |  |  |

| P.42                     |                         | <u>Mecha</u> | nical Key                |  |  |

| B43<br>B44               |                         |              | A43<br>A44               |  |  |

| B45                      |                         |              | A45                      |  |  |

| B46                      |                         |              | A46                      |  |  |

| B47                      |                         |              | A47                      |  |  |

| <u>B48</u>               |                         |              | <u>A48</u>               |  |  |

| <u>B49</u>               |                         |              | <u>A49</u>               |  |  |

| <u>B50</u>               |                         |              | <u>A50</u>               |  |  |

| <u>B51</u>               |                         |              | <u>A51</u>               |  |  |

| <u>B52</u>               |                         |              | A52                      |  |  |

| <u>B53</u>               |                         |              | A53                      |  |  |

| <u>B54</u><br><u>B55</u> |                         |              | A54<br>A55               |  |  |

| <u>B55</u>               |                         |              | A55<br>A56               |  |  |

| B57                      |                         |              | A57                      |  |  |

| B58                      |                         |              | A58                      |  |  |

| B59                      |                         |              | A59                      |  |  |

| <u>B60</u>               |                         |              | <u>A60</u>               |  |  |

| <u>B61</u>               |                         |              | <u>A61</u>               |  |  |

| <u>B62</u>               |                         |              | <u>A62</u>               |  |  |

| <u>B63</u>               |                         |              | <u>A63</u>               |  |  |

| <u>B64</u>               |                         |              | <u>A64</u>               |  |  |

| <u>B65</u>               |                         |              | <u>A65</u>               |  |  |

| <u>B66</u>               |                         |              | <u>A66</u>               |  |  |

Open Compute Project • NIC • 3.0

#### 3.2 Baseboard Connector Requirement

Editor's note: Connector vendors to provide input.

B70

A70

B70

**A**70

The OCP\_NIC\_3.0 connectors is-are compliant to the "4C connector" as defined in the SFF-TA-1002 specification for a right angle or straddle mount form-factor. The 4C connector is 140-pins in width and includes support for up to 32 differential pairs to support a x16 PCIe connection. The connector also provides 6 pins of 12V for payload power. This implementation is common between both the Primary and Secondary Connectors. In addition, the Primary Connector has a 28-pin OCP Bay to the right of pin 1. These pins are used for management and support for up to a 4 x4 multi-host configuration on the Primary Connector. The Primary and Secondary Connector drawings are shown in Figure 11Figure 13, and Figure 12Figure 14, Figure 13 and Figure 14 below.

Figure 11<del>13</del>: 168-pin Base Board Primary Connector – Right Angle

Figure 1214: 140-pin Base Board Secondary Connector – Right Angle

Figure 1315: 168-pin Base Board Primary Connector – Straddle Mount

TBD

Figure 1416: 140-pin Base Board Secondary Connector – Straddle Mount

TBD

(55.32)

4C Connector

140 Position

(55.32)

4C Connector

140 Position

**Commented [TN12]:** Note: Perhaps the SFF-TA-1002 spec needs to be updated with the 168 pin and straddle-mount definitions.

**Commented [TN13]:** Get updated drawing from TE with the straddle mount option.

**Commented [TN14]:** Get updated drawing from TE with the straddle mount option.

**Commented [TN15]:** Get updated drawing from TE with the straddle mount option.

**Commented [TN16]:** Get updated drawing from TE with the straddle mount option.

In order to the support the large form factor, systems must locate the Primary and Secondary Connectors per the mechanical drawing shown in Figure 15<del>Figure 17</del>.

http://opencompute.org

←(11.02)→

(11.02)-

(5.35)

▲

(5.35)

B

Aİ

Bi

AI

# Figure <u>15</u>17: Primary and Secondary Connector Connector Locations for Large Card Support TBD

#### 3.3 Pin definition

**Editor's note:** The pin map aligns with OCP 3.0 Pinout Proposal 20171121a\_TN.xlsx. The pin definitions of an OCP NIC 3.0 card with up to a x32 PCIe interface are shown in <u>Table 7</u>Table 6 and <u>Table 8</u>Table 7. All signal directions are shown from the perspective of the baseboard.

A baseboard system may provide a combination of Primary Connectors only, or Primary and Secondary Connectors to support multiple <u>sizes of</u> add-in cards. Both connectors share common functionality with power, SMBus, x16 PCIe Gen4 and bifurcation control. The Primary Connector has an additional OCP Bay (pins OCP\_A[1:14], OCP\_B[1:14]) with additional REFCLKs for supporting up to four PCIe hosts, NC-SI connectivity and a <u>scan-Scan</u> <u>chain\_Chain</u> for information exchange between the host and card. The NIC is required to implement the Scan Chain, while the baseboard may choose to optionally implement it. Depending on the baseboard form-factor, multiple OCP NIC 3.0 compliant cards may be designed into the system.

The pins common to the Primary and Secondary Connectors are shown in Section 3.44.4. The OCP Bay for pins on the Primary Connector only are shown in Section 3.54.5.

Cards or systems that do not require the use of a PCIe x16 connection may optionally implement a subset electrical connections as applicable to the design. (#For example, a x8 (or smaller) card using the first 8 PCIe lanes that is compliant with the Primary Connector pinout). Refer to Sections 3.14.1 and 3.24.2 for mechanical details. For these cases, the Primary Connector matches the "2C" dimensions as defined in SFF-TA-1002.

In all cases, the physical baseboard connectors shall support x16 PCIe widths and must be implemented with the Primary (4C + OCP Bay) and Secondary (4C) connectors.

Open Compute Project • NIC • 3.0

Rev0.01

|         | Table <u>7</u> 6: Primary Connecto | or <del>Card-</del> Pin Definition (x16) | (4C + OCP | Bay)                                                      |                                                          |

|---------|------------------------------------|------------------------------------------|-----------|-----------------------------------------------------------|----------------------------------------------------------|

|         | Side B                             | Side A                                   |           |                                                           |                                                          |

| OCP_B1  | NIC_PWR_GOOD                       | WAKE_N                                   | OCP_A1    | Pr                                                        | Pr                                                       |

| OCP_B2  | PWRBRK#                            | PERST2#                                  | OCP_A2    | ima                                                       | ima                                                      |

| OCP_B3  | LD#                                | PERST3#                                  | OCP_A3    | Γγ<br>Ο                                                   | ry o                                                     |

| OCP_B4  | DATA_IN                            | RBT_ARB_IN                               | OCP_A4    | onn                                                       | onn                                                      |

| OCP_B5  | DATA_OUT                           | RBT_ARB_OUT                              | OCP_A5    | ecto                                                      | lecto                                                    |

| OCP_B6  | CLK                                | GND                                      | OCP_A6    | or (x                                                     | or (x                                                    |

| OCP_B7  | SLOT_ID0                           | RBT_TX_EN                                | OCP_A7    | :16,                                                      | (8, 1                                                    |

| OCP_B8  | RBT_RXD1                           | RBT_TXD1                                 | OCP_A8    | 168                                                       | .12-                                                     |

| OCP_B9  | RBT_RXD0                           | RBT_TXD0                                 | OCP_A9    | pir                                                       | pin                                                      |

| OCP_B10 | GND                                | GND                                      | OCP_A10   | 1 ad                                                      | add                                                      |

| OCP_B11 | REFCLKn2                           | REFCLKn3                                 | OCP_A11   | Primary Connector (x16, 168-pin add-in card with OCP Bay) | Primary Connector (x8, 112-pin add-in card with OCP bay) |

| OCP_B12 | REFCLKp2                           | REFCLKp3                                 | OCP_A12   | l ca                                                      | carc                                                     |

| OCP_B13 | GND                                | GND                                      | OCP_A13   | rd w                                                      | 4 wi                                                     |

| OCP_B14 | RBT_CRS_DV                         | RBT_CLK_IN                               | OCP_A14   | lith                                                      | tho                                                      |

|         | Mechan                             | nical Key                                |           | ្ព                                                        | ČP                                                       |

| B1      | +12V/+12V_AUX                      | GND                                      | A1        | Ва                                                        | bay                                                      |

| B2      | +12V/+12V_AUX                      | GND                                      | A2        | <u>s</u>                                                  | Ŭ                                                        |

| B3      | +12V/+12V_AUX                      | GND                                      | A3        |                                                           |                                                          |

| B4      | +12V/+12V_AUX                      | GND                                      | A4        |                                                           |                                                          |

| B5      | +12V/+12V_AUX                      | GND                                      | A5        |                                                           |                                                          |

| B6      | +12V/+12V_AUX                      | GND                                      | A6        |                                                           |                                                          |

| B7      | BIFO#                              | SMCLK                                    | A7        |                                                           |                                                          |

| B8      | BIF1#                              | SMDAT                                    | A8        |                                                           |                                                          |

| В9      | BIF2#                              | SMRST#                                   | A9        |                                                           |                                                          |

| B10     | PERST0#                            | PRSNTA#                                  | A10       |                                                           |                                                          |

| B11     | +3.3V/+3.3V_AUX                    | PERST1#                                  | A11       |                                                           |                                                          |

| B12     | PWRDIS                             | PRSNTB2#                                 | A12       |                                                           |                                                          |

| B13     | GND                                | GND                                      | A13       |                                                           |                                                          |

| B14     | REFCLKn0                           | REFCLKn1                                 | A14       |                                                           |                                                          |

| B15     | REFCLKp0                           | REFCLKp1                                 | A15       |                                                           |                                                          |

| B16     | GND                                | GND                                      | A16       |                                                           |                                                          |

| B17     | PETn0                              | PERn0                                    | A17       |                                                           |                                                          |

| B18     | PETp0                              | PERp0                                    | A18       |                                                           |                                                          |

| B19     | GND                                | GND                                      | A19       |                                                           |                                                          |

| B20     | PETn1                              | PERn1                                    | A20       |                                                           |                                                          |

| B21     | PETp1                              | PERp1                                    | A21       |                                                           |                                                          |

| B22     | GND                                | GND                                      | A22       |                                                           |                                                          |

http://opencompute.org

Commented [TN17]: Jia brought up a good point about PRSNTA#

Unlike PCIe, the PRSNTA / PRSNTB indication doesn't necessarily help us with an x-axis alignment. The Present signals may still connect.

Perhaps we could connect PRSNTB pins to GND instead of PRSNTA? This would free up a pin for use. (As a bonus, pin A10 is a bidirectional pin (based on function) per EDSFF).

27

|     | r <del>† 1</del> |          |     |  |

|-----|------------------|----------|-----|--|

| B23 | PETn2            | PERn2    | A23 |  |

| B24 | PETp2            | PERp2    | A24 |  |

| B25 | GND              | GND      | A25 |  |

| B26 | PETn3            | PERn3    | A26 |  |

| B27 | PETp3            | PERp3    | A27 |  |

| B28 | GND              | GND      | A28 |  |

|     | Mechan           | ical Key |     |  |

| B29 | GND              | GND      | A29 |  |

| B30 | PETn4            | PERn4    | A30 |  |

| B31 | PETp4            | PERp4    | A31 |  |

| B32 | GND              | GND      | A32 |  |

| B33 | PETn5            | PERn5    | A33 |  |

| B34 | PETp5            | PERp5    | A34 |  |

| B35 | GND              | GND      | A35 |  |

| B36 | PETn6            | PERn6    | A36 |  |

| B37 | PETp6            | PERp6    | A37 |  |

| B38 | GND              | GND      | A38 |  |

| B39 | PETn7            | PERn7    | A39 |  |

| B40 | PETp7            | PERp7    | A40 |  |

| B41 | GND              | GND      | A41 |  |

| B42 | PRSNTB0#         | PRSNTB1# | A42 |  |

|     | Mechan           | ical Key |     |  |

| B43 | GND              | GND      | A43 |  |

| B44 | PETn8            | PERn8    | A44 |  |

| B45 | PETp8            | PERp8    | A45 |  |

| B46 | GND              | GND      | A46 |  |

| B47 | PETn9            | PERn9    | A47 |  |

| B48 | PETp9            | PERp9    | A48 |  |

| B49 | GND              | GND      | A49 |  |

| B50 | PETn10           | PERn10   | A50 |  |

| B51 | PETp10           | PERp10   | A51 |  |

| B52 | GND              | GND      | A52 |  |

| B53 | PETn11           | PERn11   | A53 |  |

| B54 | PETp11           | PERp11   | A54 |  |

| B55 | GND              | GND      | A55 |  |

| B56 | PETn12           | PERn12   | A56 |  |

| B57 | PETp12           | PERp12   | A57 |  |

| B58 | GND              | GND      | A58 |  |

| B59 | PETn13           | PERn13   | A59 |  |

|     |                  |          |     |  |

Open Compute Project • NIC • 3.0

Rev0.01

| B60 | PETp13   | PERp13   | A60 |  |

|-----|----------|----------|-----|--|

| B61 | GND      | GND      | A61 |  |

| B62 | PETn14   | PERn14   | A62 |  |

| B63 | PETp14   | PERp14   | A63 |  |

| B64 | GND      | GND      | A64 |  |

| B65 | PETn15   | PERn15   | A65 |  |

| B66 | PETp15   | PERp15   | A66 |  |

| B67 | GND      | GND      | A67 |  |

| B68 | RFU, N/C | RFU, N/C | A68 |  |

| B69 | RFU, N/C | RFU, N/C | A69 |  |

| B70 | PRSNTB3# | RFU, N/C | A70 |  |

# Table <u>8</u>7: Secondary Connector Card-Pin Definition (x16) (4C)

|     | Side B          | Side A   |     | ľ                                              |                                              |

|-----|-----------------|----------|-----|------------------------------------------------|----------------------------------------------|

| B1  | +12V/+12V_AUX   | GND      | A1  | S                                              | S                                            |

| B2  | +12V/+12V_AUX   | GND      | A2  | eco                                            | eco                                          |

| B3  | +12V/+12V_AUX   | GND      | A3  | nda                                            | nda                                          |

| B4  | +12V/+12V_AUX   | GND      | A4  | y c                                            | ny C                                         |

| B5  | +12V/+12V_AUX   | GND      | A5  | onn                                            | onn                                          |

| B6  | +12V/+12V_AUX   | GND      | A6  | ecto                                           | ecto                                         |

| B7  | BIFO#           | SMCLK    | A7  | or (x                                          | or (x                                        |

| B8  | BIF1#           | SMDAT    | A8  | 16,                                            | 8, 8                                         |

| В9  | BIF2#           | SMRST#   | A9  | 140                                            | 4-pi                                         |

| B10 | PERST0#         | PRSNTA#  | A10 | -pin                                           | n ac                                         |

| B11 | +3.3V/+3.3V_AUX | PERST1#  | A11 | ado                                            | dd-i                                         |

| B12 | PWRDIS          | PRSNTB2# | A12 | Secondary Connector (x16, 140-pin add-in card) | Secondary Connector (x8, 84-pin add-in card) |

| B13 | GND             | GND      | A13 | care                                           | rd)                                          |

| B14 | REFCLKn0        | REFCLKn1 | A14 | 3                                              |                                              |

| B15 | REFCLKp0        | REFCLKp1 | A15 |                                                |                                              |

| B16 | GND             | GND      | A16 |                                                |                                              |

| B17 | PETn0           | PERn0    | A17 |                                                |                                              |

| B18 | PETp0           | PERp0    | A18 |                                                |                                              |

| B19 | GND             | GND      | A19 |                                                |                                              |

| B20 | PETn1           | PERn1    | A20 |                                                |                                              |

| B21 | PETp1           | PERp1    | A21 |                                                |                                              |

| B22 | GND             | GND      | A22 |                                                |                                              |

| B23 | PETn2           | PERn2    | A23 |                                                |                                              |

| B24 | PETp2           | PERp2    | A24 |                                                |                                              |

| B25 | GND             | GND      | A25 |                                                |                                              |

| B26 | PETn3           | PERn3    | A26 |                                                |                                              |

| B27 | PETp3           | PERp3    | A27 |                                                |                                              |

| B28 | GND             | GND      | A28 |                                                |                                              |

|     | Mechan          | ical Key |     |                                                |                                              |

| B29 | GND             | GND      | A29 |                                                |                                              |

| B30 | PETn4           | PERn4    | A30 |                                                |                                              |

| B31 | PETp4           | PERp4    | A31 |                                                |                                              |

| B32 | GND             | GND      | A32 |                                                |                                              |

| B33 | PETn5           | PERn5    | A33 |                                                |                                              |

| B34 | PETp5           | PERp5    | A34 |                                                |                                              |

| B35 | GND             | GND      | A35 |                                                |                                              |

| B36 | PETn6           | PERn6    | A36 |                                                |                                              |

Open Compute Project • NIC • 3.0

Rev0.01

|     |          |          |     | Rev0.01 |

|-----|----------|----------|-----|---------|

| B37 | РЕТр6    | PERp6    | A37 |         |

| B38 | GND      | GND      | A38 |         |

| B39 | PETn7    | PERn7    | A39 |         |

| B40 | PETp7    | PERp7    | A40 |         |

| B41 | GND      | GND      | A41 |         |

| B42 | PRSNTB0# | PRSNTB1# | A42 |         |

|     | Mechan   | ical Key | _   |         |

| B43 | GND      | GND      | A43 |         |

| B44 | PETn8    | PERn8    | A44 |         |

| B45 | PETp8    | PERp8    | A45 |         |

| B46 | GND      | GND      | A46 |         |

| B47 | PETn9    | PERn9    | A47 |         |

| B48 | PETp9    | PERp9    | A48 |         |

| B49 | GND      | GND      | A49 |         |

| B50 | PETn10   | PERn10   | A50 |         |

| B51 | PETp10   | PERp10   | A51 |         |

| B52 | GND      | GND      | A52 |         |

| B53 | PETn11   | PERn11   | A53 |         |

| B54 | PETp11   | PERp11   | A54 |         |

| B55 | GND      | GND      | A55 |         |

| B56 | PETn12   | PERn12   | A56 |         |

| B57 | PETp12   | PERp12   | A57 |         |

| B58 | GND      | GND      | A58 |         |

| B59 | PETn13   | PERn13   | A59 |         |

| B60 | PETp13   | PERp13   | A60 |         |

| B61 | GND      | GND      | A61 |         |

| B62 | PETn14   | PERn14   | A62 |         |

| B63 | PETp14   | PERp14   | A63 |         |

| B64 | GND      | GND      | A64 |         |

| B65 | PETn15   | PERn15   | A65 |         |

| B66 | PETp15   | PERp15   | A66 |         |

| B67 | GND      | GND      | A67 |         |

| B68 | RFU, N/C | RFU, N/C | A68 |         |

| B69 | RFU, N/C | RFU, N/C | A69 |         |

| B70 | PRSNTB3# | RFU, N/C | A70 |         |

## 3.4 Signal Descriptions – Common

The pins shown in this section are common to both the Primary and Secondary Connectors. All pin directions are from the perspective of the baseboard.

The add-in card shall implement protection methods to prevent leakage paths between the Vaux and Vmain power domains in the event that a NIC is powered down in a powered up baseboard.

**Note:** Pins that are only used on Primary Connector 28-pin OCP bay are defined in Section <u>3.5</u>4.5.

#### 3.4.1 PCIe Interface Pins

This section provides the pin assignments for the PCIe interface signals. The AC/DC specifications are defined in Section XXX the PCIe CEM Specification, Rev 4.0. Example connection diagrams for are shown in Figure 26Figure 28.

| Signal Name | Pin # | Baseboard | Signal Description                              |

|-------------|-------|-----------|-------------------------------------------------|

|             |       | Direction |                                                 |

| REFCLKn0    | B14   | Output    | PCIe compliant differential reference clock #0, |

| REFCLKp0    | B15   |           | and #1. 100MHz HCSL reference clocks are        |

| REFCLKn1    | A14   | Output    | used for the add-in card PCIe core logic.       |

| REFCLKp1    | A15   |           |                                                 |

|             |       |           | For baseboards, the REFCLK0 and REFCLK1         |

|             |       |           | signals are required at the connector.          |

|             |       |           |                                                 |

|             |       |           | For add-in cards, the required REFCLKs shall be |

|             |       |           | connected per the endpoint datasheet.           |

|             |       |           |                                                 |

|             |       |           | Note: For cards that only support 1 x16,        |

|             |       |           | REFCLK0 is used. For cards that support 2 x8,   |

|             |       |           | REFCLK0 is used for the first eight PCIe lanes, |

#### Table <u>98</u>: Card Pin Descriptions – PCIe <u>1</u>

Rev0.01

|                |            |        | and REFCLK1 is used for the second eight PCIe     |

|----------------|------------|--------|---------------------------------------------------|

|                |            |        | lanes.                                            |

|                |            |        |                                                   |

|                |            |        | Refer to Section 2.1 in the PCIe CEM              |

|                |            |        | Specification, Rev 4.0 for electrical details.    |

| PETn0          | B17        | Output | Transmitter differential pairs [0:15]. These pins |

| PETp0          | B18        | Output | are connected from the baseboard transmitter      |

| PETn1          | B10<br>B20 | Output | differential pairs to the receiver differential   |

| PETp1          | B20<br>B21 | Output | pairs on the add-in card.                         |

| PETP1<br>PETn2 | B21<br>B23 | Output |                                                   |

|                |            | Output | The PCIe Transmit transmit pins are AC coupled    |

| PETp2          | B24        | 0.1.1  | on the baseboard with capacitors and are          |

| PETn3          | B26        | Output |                                                   |

| PETp3          | B27        | -      | placed next to the baseboard transmitters. The    |

| PETn4          | B30        | Output | AC coupling capacitor must be between 176nF       |

| PETp4          | B31        |        | (min) and 265nF (max).                            |

| PETn5          | B33        | Output |                                                   |

| PETp5          | B34        |        | For baseboards, the PET[0:15] signals are         |

| PETn6          | B36        | Output | required at the connector.                        |

| PETp6          | B37        |        |                                                   |

| PETn7          | B39        | Output | For add-in cards, the required PET[0:15] signals  |

| PETp7          | B40        |        | shall be connected to the endpoint silicon. For   |

| PETn8          | B44        | Output | silicon that uses less than a x16 connection, the |

| PETp8          | B45        |        | appropriate PET[0:15] signals shall be            |

| PETn9          | B47        | Output | connected per the endpoint datasheet.             |

| PETp9          | B48        |        |                                                   |

| PETn10         | B50        | Output | Refer to Section 6.1 in the PCIe CEM              |

| PETp10         | B51        |        | Specification, Rev 4.0 for details.               |

| PETn11         | B53        | Output |                                                   |

| PETp11         | B54        |        |                                                   |

| PETn12         | B56        | Output |                                                   |

| PETp12         | B57        |        |                                                   |

| PETn13         | B59        | Output | 1                                                 |

| PETp13         | B60        |        |                                                   |

|                |            | 1      |                                                   |

| PETp14B63OutputPETn15B65OutputPETp15B66PERn0A17InputReceiver differential pairs [0:15]. These pins a<br>connected from the add-in card transmitterPERp1A20Inputdifferential pairs to the receiver differential<br>pairs on the baseboard.PERp2A23InputPERp3A26InputPERp4A30InputPERp4A31On the add-in card transmitters.PERp5A34For baseboards, the PER[0:15] signals are<br>required at the connector.PERn6A36InputPERp6A37For add-in cards, the required PER[0:15] signal<br>shall be connected to the endpoint silicon. Fer                                                                                                                                                                                                                                                                                                                                                                  | PETn14 | B62 Output |                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------|----------------------------------------------------|

| PETn15B65OutputPETp15B66InputReceiver differential pairs [0:15]. These pins a<br>connected from the add-in card transmitterPERp0A18connected from the add-in card transmitterPERp1A20Inputdifferential pairs to the receiver differential<br>pairs on the baseboard.PERp2A23InputPERp3A26InputPERp3A27The PCIe Receive-receive pins are AC coupler<br>on the add-in card with capacitors and are<br>placed next to the add-in card transmitters.PERp4A31InputPERp5A33InputPERp6A37For baseboards, the PER[0:15] signals are<br>required at the connector.PERp7A40For add-in cards, the required PER[0:15] signals are<br>shall be connected to the endpoint silicon. F<br>silicon that uses less than a x16 connection, appropriate PER[0:15] signals shall be<br>connected per the endpoint datasheet.PERp9A48InputPERp9A48Refer to Section 6.1 in the PCIe CEM<br>consideration.              | PETp14 |            |                                                    |