# Honey Badger – Light Weight Compute Module in Open Vault Storage Vo.7

Authors:

Mike Yan, Storage Hardware Design Engineer, Facebook Song Liu, Storage System Software Engineer, Facebook Jon Ehlen, Mechanical Engineer, Facebook

# 1 Contents

| 1 | Contents 2 |                                           |  |  |  |  |

|---|------------|-------------------------------------------|--|--|--|--|

| 2 | Scope 5    |                                           |  |  |  |  |

| 3 | view5      |                                           |  |  |  |  |

|   | 3.1        | License                                   |  |  |  |  |

| 4 | Hone       | y Badger Overview6                        |  |  |  |  |

|   | 4.1        | Overall Design Approach6                  |  |  |  |  |

|   | 4.2        | Key Accessible Items                      |  |  |  |  |

|   | 4.3        | Functional Block Diagram 10               |  |  |  |  |

|   | 4.4        | System Block Diagram13                    |  |  |  |  |

|   | 4.5        | System I2C Topology 15                    |  |  |  |  |

| 5 | New        | Honey Badger Tray and DPB                 |  |  |  |  |

|   | 5.1        | Open Vault Storage Specification          |  |  |  |  |

|   | 5.2        | Modifications on Honey Badger Tray 18     |  |  |  |  |

|   | 5.3        | Modifications on Honey Badger DPB 19      |  |  |  |  |

| 6 | Pant       | her+ Card for Honey Badger                |  |  |  |  |

|   | 6.1        | Micro-Server Card Specification           |  |  |  |  |

|   | 6.2        | Panther+ Design Specifications            |  |  |  |  |

|   | 6.3        | Panther+ Block Diagram                    |  |  |  |  |

|   | 6.4        | Panther+ Feature List                     |  |  |  |  |

|   | 6.5        | Panther+ PCB Dimension                    |  |  |  |  |

| 7 | Hone       | y Badger Baseboard24                      |  |  |  |  |

|   | 7.1        | Baseboard Feature List                    |  |  |  |  |

|   | 7.2        | Baseboard Block Diagram25                 |  |  |  |  |

|   | 7.3        | Mechanical Requirements for the Baseboard |  |  |  |  |

|   | 7.4        | Baseboard Key Component Placement         |  |  |  |  |

|   | 7.5        | SAS Controller and SAS Expander           |  |  |  |  |

|   | 7.6        | BMC Chip                                  |  |  |  |  |

|   | 7.7        | 10GbE Mezz Card                           |  |  |  |  |

|   | 7.8        | I/O Connectors                            |  |  |  |  |

|   | 7.9        | Switch and Buttons                        |  |  |  |  |

|   | 7.10       | LEDs                                      |  |  |  |  |

|   | 7.11       | PCB Stack-up 41                           |  |  |  |  |

| 8 | Boar       | d Level Power Budget                      |  |  |  |  |

|    | 8.1   | Feature Model Power Budget 42                    |

|----|-------|--------------------------------------------------|

|    | 8.2   | Entry Model Power Budget 43                      |

| 9  | BIOS  | Feature List 43                                  |

| 10 | вмс   | and System Enclosure Management                  |

|    | 10.1  | Management Network Interface 45                  |

|    | 10.2  | Local Serial Console and SoL45                   |

|    | 10.3  | Remote Power Control and Power Policy45          |

|    | 10.4  | Port 8o POST Code                                |

|    | 10.5  | BMC Firmware Update                              |

|    | 10.6  | System Sensors                                   |

|    | 10.7  | System Event Log 47                              |

|    | 10.8  | Fan Speed Control                                |

|    | 10.9  | Thermal Protection                               |

| 11 | Stora | age Enclosure Management 50                      |

|    | 11.1  | Supported Information 50                         |

|    | 11.2  | SES Standard 51                                  |

|    | 11.3  | Extension to SES Standard                        |

|    | 11.4  | SCSI Buffer Definitions                          |

|    | 11.5  | HDD Spin-up Control 55                           |

|    | 11.6  | HDD Spin-down Control Support                    |

|    | 11.7  | Storage System Error Code                        |

| 12 | Envir | onmental Requirements and Reliability57          |

|    | 12.1  | Environmental Requirements57                     |

|    | 12.2  | Vibration and Shock57                            |

|    | 12.3  | Mean Time Between Failures (MTBF) Requirements57 |

|    | 12.4  | Regulations                                      |

| 13 | Labe  | ls and Markings                                  |

|    | 13.1  | PCBA Labels and Markings                         |

|    | 13.2  | Chassis Labels and Markings                      |

| 14 | Preso | ribed Materials                                  |

|    | 14.1  | Sustainable Materials 59                         |

|    | 14.2  | Disallowed Components 59                         |

|    | 14.3  | Capacitors and Inductors                         |

|    | 14.4  | Component De-Rating59                            |

| 15 | Hone  | ey Badger Interconnect Pin Definitions60         |

|    | 15.1 Drive Plane Board Pin Definitions6            | 50         |

|----|----------------------------------------------------|------------|

| 16 | Honey Badger Storage System Error Code Definitions | <u>5</u> 3 |

| 17 | Revision History6                                  | ŝ5         |

# 2 Scope

This document describes the technical specifications used in the design of a light weight compute module for the Open Vault Storage of Open Compute Project, known as the Honey Badger.

# 3 Overview

When data center design and hardware design move in concert, they can improve efficiency and reduce power consumption. To this end, the Open Compute Project is a set of technologies that reduces energy consumption and cost, increases reliability and choice in the marketplace, and simplifies operations and maintenance. One key objective is openness -- the project is starting with the opening of the specifications and mechanical designs for the major components of a data center, and the efficiency results achieved at facilities using Open Compute technologies.

A new component of this project is the Honey Badger, a light weight compute module that works in Open Vault Storage (Knox). By leveraging the Open Vault platform, Honey Badger turns Knox from a JBOD into a light weight storage server. It is a simple and cost-effective solution for those application software that don't request very strong compute capability. Honey Badger comes with a modularized design concept: by adopting the new version Micro-Server card, it maximizes the flexibility to accept different compute modules for different use cases, also enables the capability to upgrade the compute and the storage subsystem in different pace. For the network interface, Honey Badger also supports the same OCP mezzanine cards as the OCP servers: 10G Ethernet now and will be 40G Ethernet in future.

#### 3.1 License

As of April 7, 2011, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at

http://www.openwebfoundation.org/legal/the-owf-1-o-agreements/owfa-1-o

#### Facebook, Inc.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at http://opencompute.org/licensing/, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS". The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 4 Honey Badger Overview

#### 4.1 Overall Design Approach

The Honey Badger compute module design is based on an architecture that contains a baseboard and an add-in Micro-Server card.

- The add-in Micro-Server card should be compatible with the Micro-Server x16 card specification, supporting below interfaces in its configuration. Current design uses an Intel Avoton based Micro-Server card, known as Panther+.

- One PCI-E x4 port

- One PCI-E x8 port

- One USB 2.0 port

- o One UART port

- One I2C bus for management bridge IC (FPGA)

- Four pins for slot ID (or hardware revision)

- One pin for power button

- One pin for system reset

- The baseboard is functioning as a storage host bus adapter (HBA) with 12G SAS solution. Major components on baseboard will be: 8 port SAS IOC, 24 port SAS expander which is also responsible for storage enclosure management, external Mini-SAS connector for expansion, PCI-E Mezz Card for 10GbE port, baseboard management controller (BMC) for system enclosure management, debug header, switch buttons, LEDs, etc.

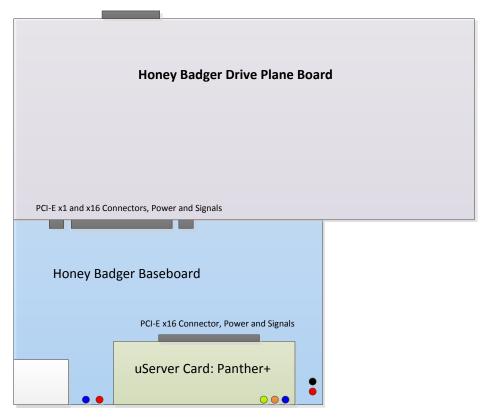

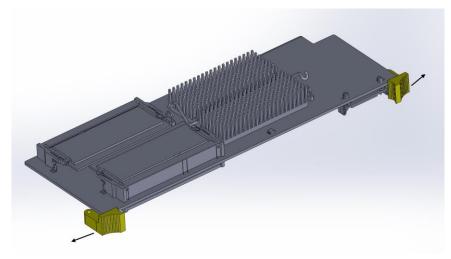

Figure 1 shows the concept of Honey Badger baseboard and Panther+ Micro-Server card:

Figure 1 Honey Badger Compute Module Overview

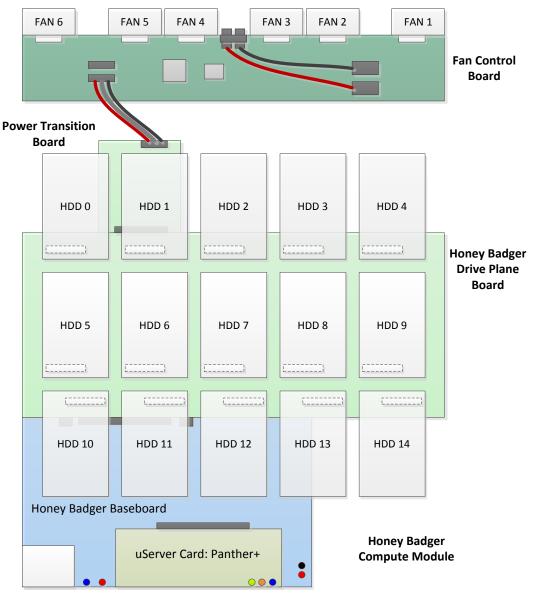

Figure 2 shows an overview of the Honey Badger compute module in a Knox system.

Figure 2 Honey Badger Compute Module in a Knox System

# 4.2 Key Accessible Items

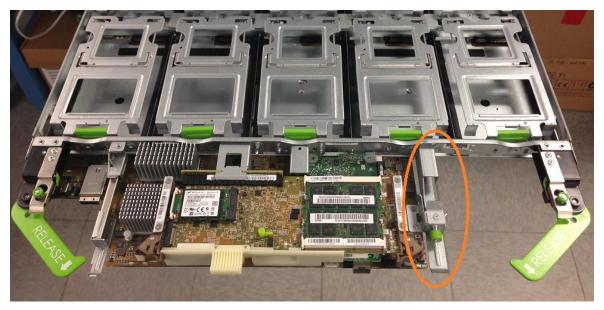

The equipment accessible on the Panther+ card of Honey Badger includes:

- Up to four DDR<sub>3</sub> ECC SO-DIMM slot, two on each side

- One mSATA SSD module, SATA<sub>3</sub> interface

- One NGFF Flash card, SATA<sub>3</sub> or PCI-E x4 interface (BOM Option)

- Three status LEDs for Micro-Server card information

Figure 3 Key Accessible Items on Panther+ Micro-Server Card, Top Side

Figure 4 Key Accessible Items on Panther+ Micro-Server Card, Bottom Side

The equipment accessible from the front of the Honey Badger baseboard includes:

- One External Mini-SAS Conn (SFF-8088 form factor)

- One Internal Mini-SAS Conn (SFF-8087 form factor), with Status LED

- One 10GbE port (SFP+ form factor, with Link / Activity Status LEDs)

- One USB 2.0 port

- One OCP Debug Header, with slide switch and LED indicator

- Two Switch Buttons for power and reset

- Two Status LEDs for system information

Figure 5 Key Accessible Items on Honey Badger Baseboard

### 4.3 Functional Block Diagram

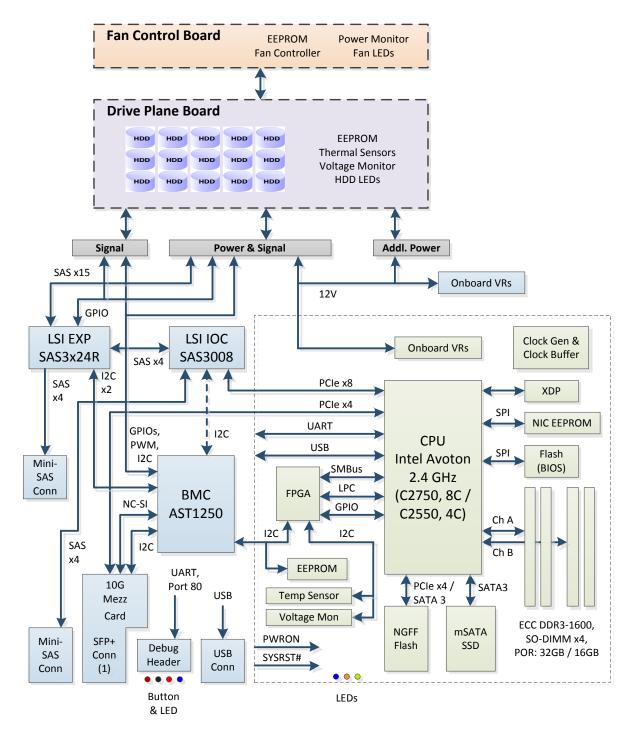

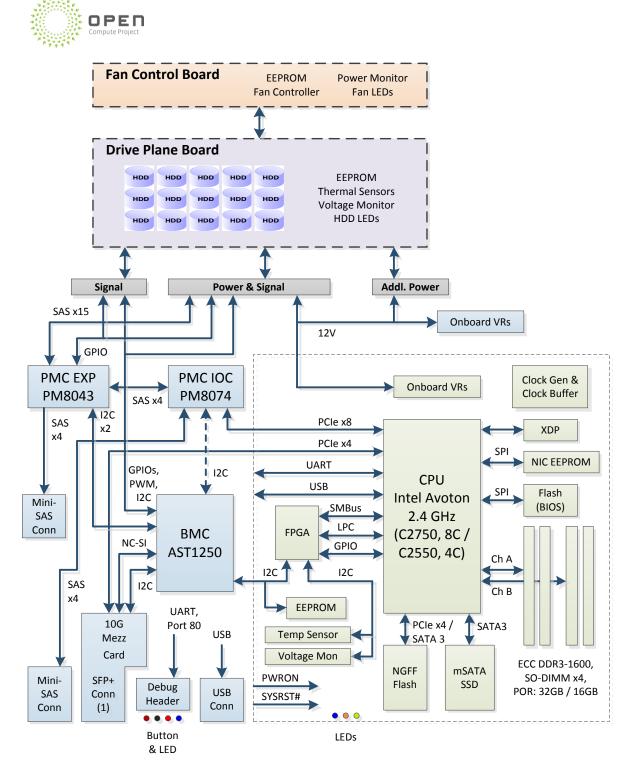

There are two solutions for the storage sub-system design on Honey Badger baseboard as below. They are dual-sourced to each other. So far solution 1 is the POR configuration, while solution 2 has also been developed and verified by the vendors.

- Solution 1: Based on Avago / LSI 12G SAS IOC and 12G SAS Expander. The part number of the 8-port IOC is *LSI SAS3008*, the part number of the 24-port expander is LSI *SAS3x24RLC1*.

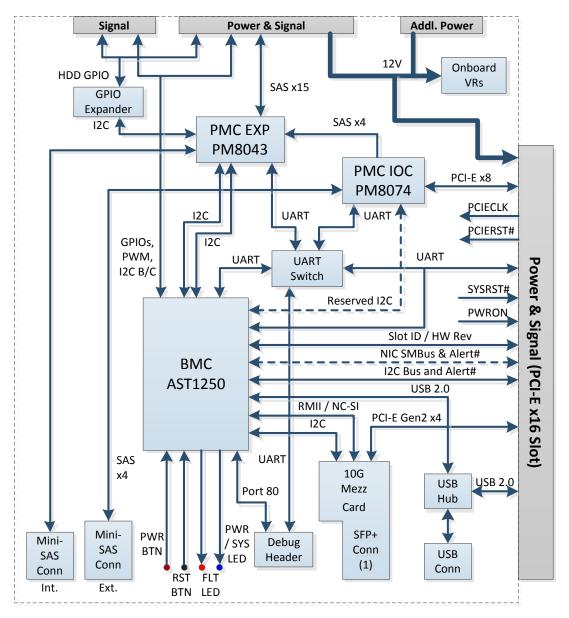

- Solution 2: Based on PMC-Sierra 12G SAS IOC and 12G SAS expander. The part number of the 8-port IOC is *PM8074*, the part number of the 24-port expander is *PM8043*.

Figure 6 shows a high-level functional block diagram of Honey Badger, with an Avago / LSI 12G SAS controller and a SAS expander.

Figure 6 Honey Badger Functional Block Diagram, LSI solution

Figure 7 shows a high-level functional block diagram of Honey Badger, with a PMC-Sierra 12G SAS controller and a SAS expander.

Figure 7 Honey Badger Functional Block Diagram, PMC solution

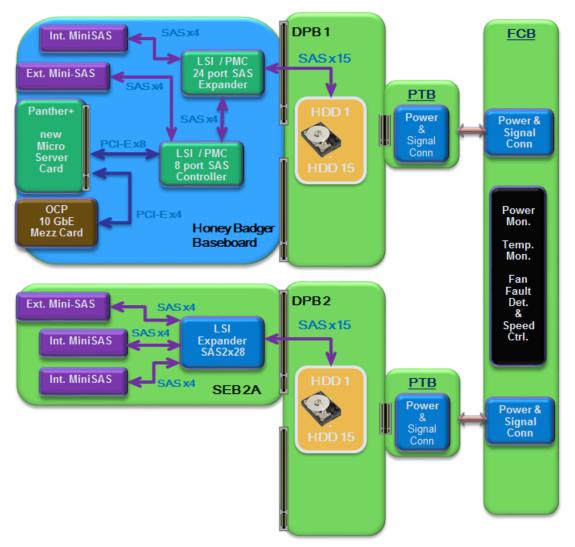

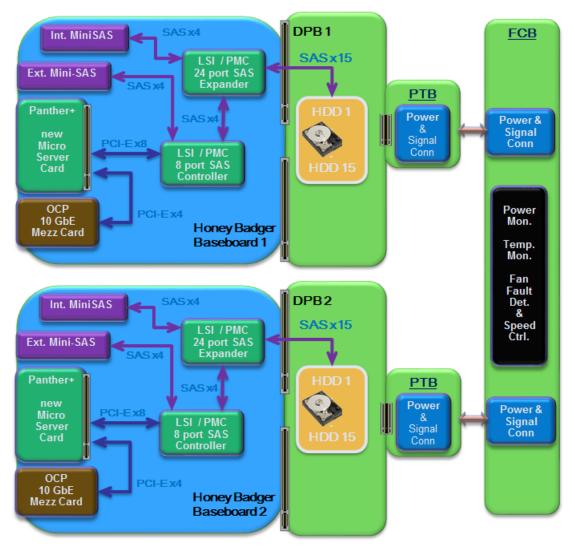

## 4.4 System Block Diagram

This section contains the system block diagrams for the Honey Badger compute module in a Knox system. It mainly addresses the PCI-E and SAS data paths. Each module has the following cable connectors, which are accessible from the cold aisle:

- One 10GbE port in SFP+ form factor, to top of rack switch

- Passive copper Ethernet cable

- o Max cable length: TBD

- One external Mini-SAS port in SFF-8088 form factor. It is connected to the Knox SEB in another tray within the same Honey Badger system:

- o External mini-SAS cable

- Max cable length: 7m

- One internal Mini-SAS port in SFF-8087 form factor. It is reserved to for cascading purpose (to connect Knox SEB in another system).

- o Internal mini-SAS cable

- Max cable length: 1.5m

Figure 8 shows the typical use case of a 1:30 compute node to hard disk drive ratio:

Figure 8 Honey Badger System Block Diagram (Use Case 1:30)

**Note**: According to the new Honey Badger tray design that to accept both Honey Badger baseboard and Knox SEB, the Knox SEB can only be placed on the A-side.

Figure 9 shows another typical use case of a 1:15 compute node to hard disk drive ratio:

Figure 9 Honey Badger System Block Diagram (Use Case 1:15)

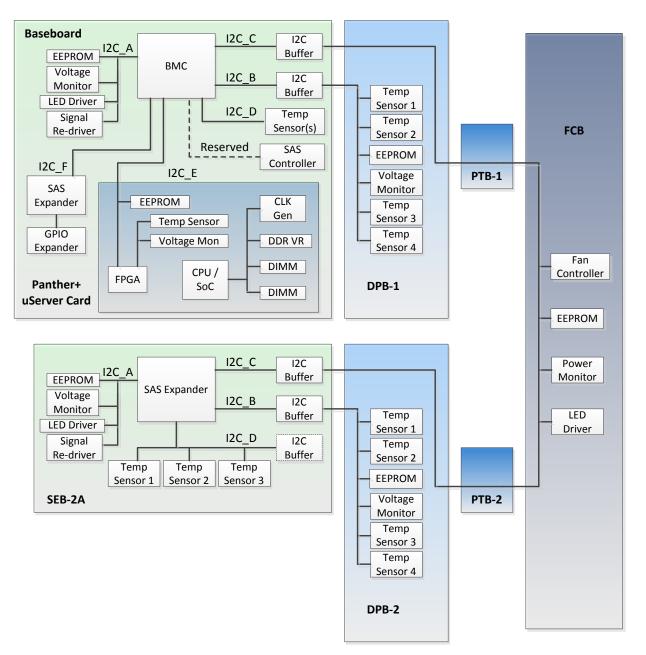

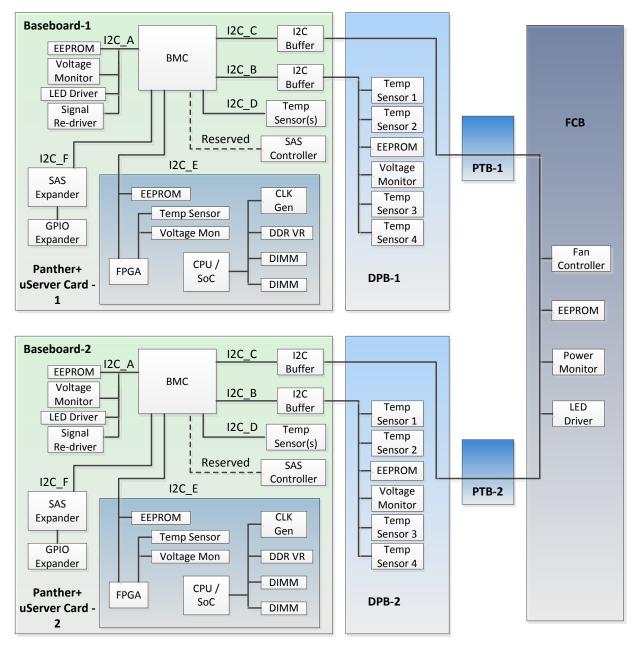

# 4.5 System I2C Topology

Figure 10 and Figure 11 show the system I2C topology of the Honey Badger compute module in a Knox system, with a 1:30 or 1:15 compute node to hard disk drive ratio, respectively. They show the enclosure management structure of the Honey Badger module and the system.

Figure 10 Honey Badger System I2C Topology (Use Case 1:30)

Figure 11 Honey Badger System I2C Topology (Use Case 1:15)

# 5 New Honey Badger Tray and DPB

#### 5.1 Open Vault Storage Specification

Honey Badger system is based on the Open Vault Storage system, known as Knox. Relevant specification can be found on the Open Compute Project website:

- Open\_Vault\_Storage\_Hardware\_vo.8.pdf

- From: <u>http://www.opencompute.org/projects/storage/</u>

- Or: <u>http://www.opencompute.org/wiki/Storage/Dev</u>

#### 5.2 Modifications on Honey Badger Tray

Below design changes have been made on Honey Badger tray from Knox tray, to accommodate to the new use case of Honey Badger:

- New card guide for Honey Badger baseboard which is wider than Knox SEB. Circled item in Figure 12 below.

- Shortened center card guide to accept both Honey Badger baseboard and Knox SEB. Circled item in Figure 13 below.

- Non-tilting tray / Fixed hinge to avoid interference between the upper tray and the lower tray when tilted down.

Figure 12 New Honey Badger Tray, Front View

Figure 13 New Honey Badger Tray, Bottom View

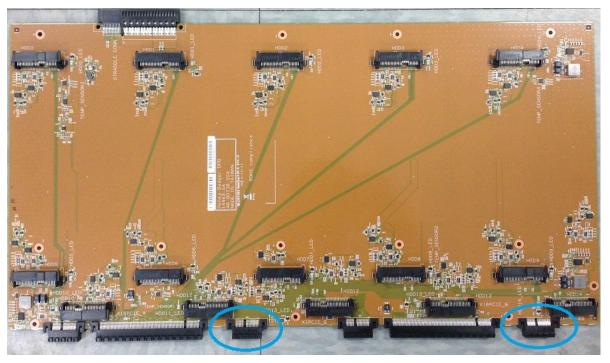

# 5.3 Modifications on Honey Badger DPB

Below design changes have been made on Honey Badger DPB (Drive Plane Board) from Knox DPB, to accommodate to the new use case of Honey Badger:

- Add one PCI-E x1 connector to provide more power / current, on both A-side and B-side. Circled items in Figure 14.

- Adopting low loss PCB material, to reserve enough margin for SATA 6G signal integrity.

Figure 14 New Honey Badger DPB

# 6 Panther+ Card for Honey Badger

### 6.1 Micro-Server Card Specification

Honey Badger adopts Panther+ Micro-Server card as compute node, but it also accepts any other Micro-Server card that meets the requirements in Section 4.1. The general design specification for a standard Micro-Server card can be found on the Open Compute Project website:

- Open\_Compute\_Project\_Micro-Server\_Card\_Specification\_vo.7.pdf

- From: http://www.opencompute.org/projects/motherboard-design/

- Or: <u>http://www.opencompute.org/wiki/Motherboard/SpecsAndDesigns</u>

#### 6.2 Panther+ Design Specifications

Panther+ is a Micro-Server card based on Intel Avoton SoC. It has been, and also will be applied to different platforms other than Honey Badger. The following sections highlight the high level design concepts of the Panther+ card in the Honey Badger compute module. For full design details, please refer to the specification for Panther+ on Open Compute Project website:

- Open\_Compute\_Project\_Panther+\_Specification\_vo.7.pdf.

- From: <u>http://www.opencompute.org/projects/motherboard-design/</u>

- Or: http://www.opencompute.org/wiki/Motherboard/SpecsAndDesigns

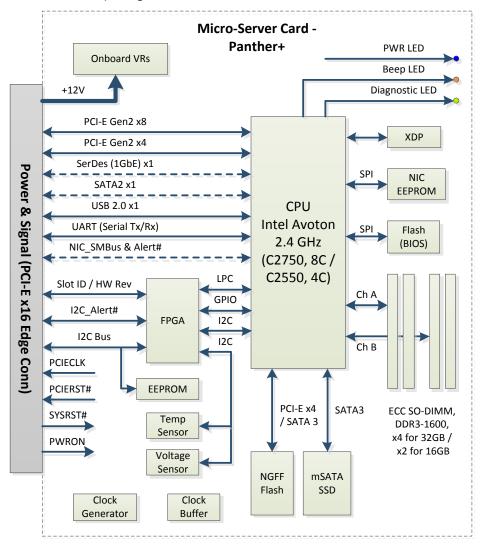

## 6.3 Panther+ Block Diagram

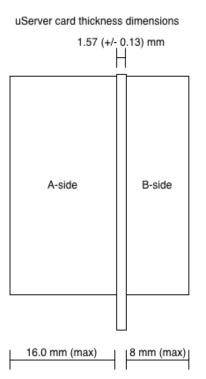

Figure 15 illustrates the functional block diagram of the Panther+ card. The dot-lined features are not used in Honey Badger.

Figure 15 Block Diagram of the Panther+ Card

### 6.4 Panther+ Feature List

The main Panther+ card feature list for the Honey Badger compute module includes:

- One Intel Avoton CPU / SoC, 2.4GHz

- o 8 cores for Feature Model

- 4 cores for Entry Model

- Up to four DDR<sub>3</sub>-1600 SO-DIMM slot, ECC enabled

- 4 DIMM modules for Feature Model, 32 GB max

- o 2 DIMM modules for Entry Model, 16 GB max

- Panther+ only support DDR<sub>3</sub>L (low-voltage)

- One mSATA SSD module, SATA3

- 256 GB POR

- One NGFF Flash module, SATA3 or PCI-E x4 (BOM Option), 2280 form factor

- 256 GB POR

- o Available only on Feature Model

- Three Status LEDs

- One Blue LED for power

- One Amber / Orange LED for beep

- One Yellow-Green LED for diagnostic

- One JTAG connector reserved for OCP test on Micro-Server card

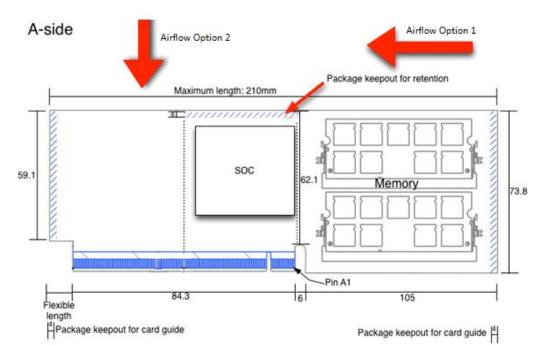

#### 6.5 Panther+ PCB Dimension

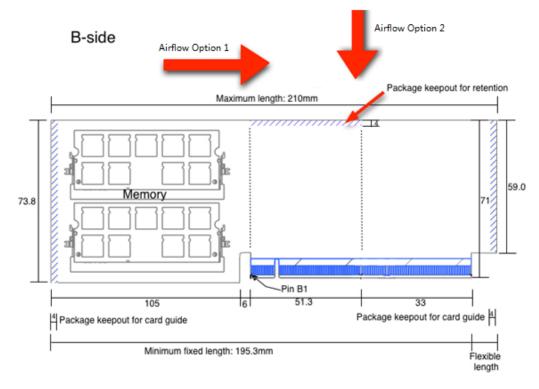

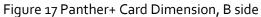

Figure 16 to Figure 18 shows the details of the Panther+ PCB dimension. The A-side is also referred as the top side, while the B-side is referred to as the bottom side.

Instead of a flexible length for the generic Micro-Server card specification, Panther+ adopts the fixed length at the maximum (210mm). Its dimensions are as below:

- Width: 73.8mm

- Length: 210mm

Because Panther+ will be used in different platforms and systems, Figure 16 and Figure 17 show the two possible airflow options for cooling. Honey Badger adopts the Airflow Option 2.

Figure 16 Panther+ Card Dimension, A side

Figure 18 Panther+ Card Height Limitation

# 7 Honey Badger Baseboard

#### 7.1 Baseboard Feature List

The Honey Badger baseboard functions as a storage HBA card. It also contains a server management module. The main feature list of the Honey Badger baseboard appears below:

- One 12G SAS controller with one 12G SAS expander, to provide non-blocking throughput and IOPS from CPU to 15 or 30 NL-SAS HDDs or Cloud SATA HDDs

- SAS expander is responsible for storage enclosure management services (inband)

- One BMC is responsible for system enclosure management services (out-band), such as fan control and all standard IPMI related functions

- One or two I2C buses are necessary between the SAS expander and the BMC to exchange related information

- A hardware approach is reserved for future exploration of "BMC as Virtual SEP," with a BOM option

- Reserve path for BMC as storage enclosure management services: BOM option to connect a drive's GPIO to the BMC

- Reserve I2C bus between a SAS controller and the BMC (one or two as needed): for "BMC as Virtual SEP" software investigation

- One Mini-SAS connector in SFF-8088 form factor

- From SAS controller, to connect Knox SEB in the another tray within the same Honey Badger system

- One reserved Mini-SAS connector in SFF-8087 form factor

- From SAS expander, for cascading purpose (to connect Knox SEB in another Knox system)

- One 10GbE mezzanine card to support one 10GbE port (SFP+)

- Shared NIC feature support on the 10GbE mezzanine card for in-band management. This will occur by connecting both the NC-SI/RMII and the I2C between the 10GbE card and the BMC

- Compatible for future 40GbE mezzanine card, single port (QSFP) only

- One USB port for on-site management/service/debug

- One debug header to accept an existing OCP debug card

- With a slide switch to select either the CPU sub-system or the storage subsystem to be debugged

- With a Red LED to indicate when storage sub-system is being debugged

- Two Switch Buttons

- o Power

- o Reset

- Four Status LEDs:

- One for power and system identify

- One for enclosure fault status

- Two 10GbE SFP+ port link status LEDs on the 10GbE Mezz Card

- Manufacturing Test Requirements

- One JTAG connector reserved for OCP test on baseboard

- JTAG scan chain is available for key ICs on board: BMC, SAS controller, SAS expander

- o Enable BIST for manufacturing test

# 7.2 Baseboard Block Diagram

Figure 19 illustrates the functional block diagram of the Honey Badger baseboard with an LSI solution.

Figure 19 Honey Badger baseboard Block Diagram – LSI solution

Figure 20 shows the functional block diagram of the Honey Badger baseboard with a PMC-Sierra solution.

# 7.3 Mechanical Requirements for the Baseboard

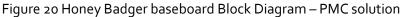

Figure 21 illustrates the Baseboard PCB dimensions of the Honey Badger compute module.

- Extended width to 354 mm, and a maximum depth not to exceed 251 mm.

- The dotted line shows the original Knox SEB dimension (start from the top left corner).

- The notch on the top right area is to engage with the shortened center card guide on new Honey Badger tray, as shown in Figure 13.

- The height limitation area on the top side is marked with an "X". It only allows components less than 2 mm in height.

- The component height limitation for the entire bottom side is 1.6 mm.

- The Keep out area is also marked with an "X" as labeled in the figure below. It is suggested that the vendor cut out this area to keep free space for the Honey Badger tray latch / handle.

• Latches on the left and right side of the Panther+ PCB shall restrain it. These latches, shown below in Figure 22, will rotate horizontally, and will not be spring-loaded. If a latch is opened it will stay open until it is manually closed. These latches will have features that will impart a tactile feedback ("click") when in the fully open and fully closed positions. They must pass transportation shock and vibration testing in the closed position, without additional parts or packing material. There will be a hard stop to restrain the latch from opening wider than necessary to allow the card to pass by, thus eliminating difficulty in retrieving a latch that has over-rotated into the chassis. The design of the latches shall copy as closely as space allows, the shape and size of the example. The pivot features are TBD by the vendor.

Figure 22 Concept of Latch Mechanism for Panther+

- The lower HDD tray's HDD latches shall be confirmed to clear all cables, connectors, features and components.

- Facebook shall define the mechanical fixturing to the chassis. The company will share CAD files.

- Baseboard to chassis fasteners: "quarter turn" thumbscrew fasteners shall be used. Facebook shall supply a specific Southco brand part number and drawing so the vendor can supply their own mating thumbscrew. Facebook will also supply a reference part number for the thumbscrew. Facebook must also approve any deviations from this size and form factor. If a quarter turn fastener part number is not available in time, a standard M<sub>3</sub> thumbscrew shall be used.

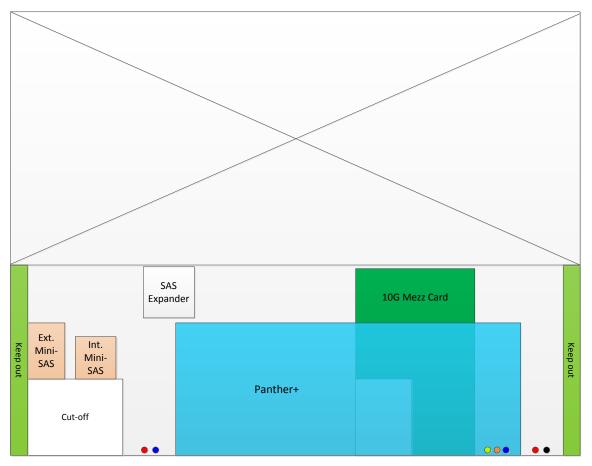

# 7.4 Baseboard Key Component Placement

Figure 23 below illustrates the key component placement of the Honey Badger baseboard.

- For rack level cable routing, it is preferred that the Mini-SAS connector (and cable) is to the left side of the Panther+ card

- For rack level cable routing, it is preferred that the 10GbE Mezz Card (and cable) is to the right side of the Panther+ card

- It is preferred that the Mini-SAS connector is recessed a certain distance from the front edge, so that when a Mini-SAS cable with a long connector head is plugged in, it won't stretch out too far in the front. The goal should be keep the cable (with bent radius) at a similar depth (to the front) between the Mini-SAS cable and 10G Ethernet cable.

- Try to put the SAS expander in the suggested location or as close as possible. The main purpose is to shorten the total SAS trace length (similar to the Knox SEB and DPB).

- To keep the Honey Badger baseboard width as small as possible, it is suggested to stack the 10GbE mezzanine card under the Panther+ Micro-Server card.

- The placement is for reference only. The vendor can adjust it accordingly for better design implementation.

Figure 23 Honey Badger baseboard Key Component Placement

# 7.5 SAS Controller and SAS Expander

The Honey Badger baseboard has two solutions for a storage sub-system. Both are 12G SAS solutions, with one 8-port SAS controller and one 24-port SAS expander. One solution is from Avago / LSI, the other solution is from PMC-Sierra.

#### 7.5.1 LSI SAS Controller and Expander Solution

The Avago / LSI 12G SAS solution includes an 8-port SAS controller and a 24-port SAS expander.

*LSISAS3008* is a 12G SAS / 6G SATA controller with a PCI-E Gen3 interface. It's based on Avago / LSI Fusion-MPT architecture, and provides a full-featured host bus adapter solution for SAS and SATA devices. It also comes with a hardware-based RAID solution that supports RAID levels 0, 1, 1E, and 10. The main features implemented in Honey Badger are:

- Eight-lane 8 Gt/s PCI-E Gen3 host interface

- Eight-port 12 Gb/s SAS and 6 Gb/s SATA interface

- 896 pin, 25 mm x 25 mm FPBGA package, 0.8mm ball pitch

*LSISAS*<sub>3</sub>*x*<sub>2</sub>*4R* is a 24-port, 12G SAS expander device that can connect up to 24 directly attached SAS or SATA devices. It supports both initiator and target connections on any link. All of the

expander ports contain the DataBolt technology feature used to match the bandwidth between fast hosts and slower SAS or SATA devices. *LSISAS3x24R* also provides an ARM-core-based CPU complex with sufficient memory capacity to implement full enclosure management functionality within the expander. The main features are listed below:

- 51 I/O pins for Link Status LEDs or GPIO

- 16 dedicated GPIO

- 5 I2C buses for master or slave operation

- 2 UART ports

- Drive spin-up and sequencing control

- DataBolt technology for End Device Frame Buffering

- Low power version selected (*LSISAS<sub>3x24</sub>RLC*<sub>1</sub>)

- 672 pin, 27 mm x 27 mm FPBGA package, 1.0 mm ball pitch

#### 7.5.2 PMC SAS Controller and Expander Solution

The PMC 12G SAS solution also includes an 8 port SAS controller and a 24 port SAS expander.

The *PM8074* is a high-performance 8-port, 12 Gb/s SAS protocol controller intended for the server and data center solutions market. The *PM8074* complies with the PCI-E Gen3 standard and supports up to 8 Gt/s per lane. It comes with proven system performance, availability and manageability, as well as a turnkey solution for production host software drivers. The main features implemented in Honey Badger are:

- Eight-lane PCI-E Gen3 interface

- Eight SAS-3 compliant PHYs

- Independent per-channel selectable high-speed outputs support multiple programmable levels of pre-emphasis and output swing

- Multiple programmable levels of receive equalization

- Decision Feedback Equalizer provides robust recovery of 12 Gb/s SAS signals over lossy channels

- Integrated resistive termination

- 1071 pin, 27 mm x 27 mm FCBGA package, 0.8 mm ball pitch

*PM8043* is a 24-port SAS expander that features SAS 3 T10 zoning, self-configuration, table-totable routing, and an integrated MIPS processor for SES and enclosure management support. It has a small footprint that enables space-constrained designs. It also has ultra-low switching latency for improved system performance. *PM8043* provides SAS and SATA edge-buffering functionality to improve performance with existing 3G and 6G drives. It also has an integrated MIPS processor for enclosure management. Its main features are:

- Up to 62 GPIO pins

- 8 dedicated I2C buses (up to 12 total) for master or slave operation

- Up to 4 UART ports

- Disk spin-up control and disk qualification API

- Edge-buffering functionality

- 896 pin, 25 mm x 25 mm FCBGA package, 0.8 mm ball pitch

## 7.6 BMC Chip

Aspeed AST1250 is a new Integrated Remote Management Processor (IRMP), functioning as a BMC on the Honey Badger baseboard. It's a vastly integrated SoC device playing as a service processor to support various functions required for highly manageable server platforms. Its highlighted features are:

- Embedded an ARM926EJ 32-bit RISC CPU, and a ColdFire V1 CPU

- Internal SRAM and external DDR2 / DDR3 ECC SDRAM

- 14 sets Multi-Function I2C/SMBus bus controllers

- 5 sets UART I/O interface, 4 sets with full flow control

- Up to 216 GPIO pins

- Support 8 PWM outputs, with 3 types of frequency mode PWM for fan speed control

- Up to 16 fan tachometer inputs

- PECI controller, Intel PECI 3.0/2.0/1.1 compliant

- Up to 16 integrated 10-bit ADCs, low-leakage inputs to measure voltage rails

- Adopt full-scan-chain design methodology for testing internal logic by Automatic Test Pattern Generation (ATPG)

- Support Built-In-Self-Test (BIST) and JTAG-compliant boundary scan

- 408 pin, 19 mm x 19 mm TFBGA package, 0.8 mm ball pitch

#### 7.6.1 Voltage Monitor by BMC ADC

To ensure proper operation of all power rails at all times, Honey Badger baseboard adopts the ADC integrated in BMC for voltage monitor. Voltages are reported as part of the system enclosure status. The voltage rails to be monitored are shown as below, Table 1 for the LSI solution, and Table 2 for the PMC solution.

Table 1 Monitored Voltage Rails on Honey Badger baseboard, LSI Solution

| Power Rail                            | Voltage |

|---------------------------------------|---------|

| PoV9 Controller                       | 0.9V    |

| PoV9 Expander                         | 0.9V    |

| P1V5 Controller                       | 1.5V    |

| P1V5 Expander                         | 1.5V    |

| P1V8 Standby                          | 1.8V    |

| P <sub>3</sub> V <sub>3</sub> Standby | 3.3V    |

| P5V Standby                           | 5.0V    |

| Input 12V                             | 12.5V   |

Table 2 Monitored Voltage Rails on Honey Badger baseboard, PMC Solution

| Power Rail        | Voltage |

|-------------------|---------|

| PoV925 Controller | 0.925V  |

| PoV925 Expander   | 0.925V  |

| P1Vo Controller   | 1.0V    |

| P1Vo Expander     | 1.0V    |

| P1V8 Standby      | 1.8V    |

| P <sub>3</sub> V <sub>3</sub> Standby | 3.3V  |

|---------------------------------------|-------|

| P <sub>5</sub> V Standby              | 5.0V  |

| Input 12V                             | 12.5V |

#### 7.7 10GbE Mezz Card

Honey Badger adopts the existing OCP 10GbE Mezz Card as its primary data network interface at I/O side. There is an option to select a single port or dual port card as per the OCP standard. But for Honey Badger, due to mechanical interference between the 2<sup>nd</sup> port (both the SFP+ connector and the cable) with the HDD cover on the lower tray when pulled out for service, only a single port 10GbE Mezz Card will be supported.

P/N of single port 10GbE Mezz cards:

- Mellanox MCX341A-XCGN

- Intel FBKX520DA1OCP4

Both of the above Mezz cards have the NC-SI connection to BMC to support OOB function (or "shared-NIC" function).

The Honey Badger baseboard has one PCI-E x8 Mezzanine Card connector that holds x4 PCI-E signal from the Panther+ card (from the Avoton CPU). The Mezzanine connector on the baseboard should use P/N *FCI 61082-121402LF* or its equivalent, with mating P/N *FCI 61083-124402LF* or its equivalent on the Mezzanine card. Pin definitions are in Table 3.

There are two single color LEDs for each SFP+ port. Their definitions follow the standard Ethernet port status LED behaviors.

| Signal             | Description         | Pin | Pin | Signal        | Description                                |

|--------------------|---------------------|-----|-----|---------------|--------------------------------------------|

| P12V_AUX           | Aux Power           | 61  | 1   | MEZZ_PRSNT1_N | Present pin1, short to Pin120 on Mezz card |

| P12V_AUX           | Aux Power           | 62  | 2   | P5V_AUX       | Aux Power                                  |

| P12V_AUX           | Aux Power           | 63  | 3   | P5V_AUX       | Aux Power                                  |

| GND                | Ground              | 64  | 4   | P5V_AUX       | Aux Power                                  |

| GND                | Ground              | 65  | 5   | GND           | Ground                                     |

| P3V3_AUX           | Aux Power           | 66  | 6   | GND           | Ground                                     |

| GND                | Ground              | 67  | 7   | P3V3_AUX      | Aux Power                                  |

| GND                | Ground              | 68  | 8   | GND           | Ground                                     |

| P3V3               | Power               | 69  | 9   | GND           | Ground                                     |

| P3V3               | Power               | 70  | 10  | P3V3          | Power                                      |

| P3V3               | Power               | 71  | 11  | P3V3          | Power                                      |

| P3V3               | Power               | 72  | 12  | P3V3          | Power                                      |

| GND                | Ground              | 73  | 13  | P3V3          | Power                                      |

| LAN_3V3STB_ALERT_N | SMBus Alert for OOB | 74  | 14  | NC-SI_RCSDV   | BMC NC-SI                                  |

| SMB_LAN_3V3STB_CLK | SMBus Clock for OOB | 75  | 15  | NC-SI_RCLK    | BMC NC-SI                                  |

| SMB_LAN_3V3STB_DAT | SMBus Data for OOB  | 76  | 16  | NC-SI_TXEN    | BMC NC-SI                                  |

Table 3 Pin Definition of 10GbE Mezz Card Connector

## Open Compute Project • Honey Badger • Compute Module vo.7

| PCIE_WAKE_N                        | PCI-E wake up                      | 77  | 17 | RST_PLT_MEZZ_N              | PCI-E reset signal                                 |

|------------------------------------|------------------------------------|-----|----|-----------------------------|----------------------------------------------------|

| NC-SI_RXER                         | BMC NC-SI                          | 78  | 18 | RSVD (MEZZ_SMCLK)           | RSVD(PCI-E slot SMBus Clock)                       |

| GND                                | Ground                             | 79  | 19 | RSVD (MEZZ_SMDATA)          | RSVD(PCI-E slot SMBus Data)                        |

| NC-SI_TXD0                         | BMC NC-SI                          | 80  | 20 | GND                         | Ground                                             |

| NC-SI_TXD1                         | BMC NC-SI                          | 81  | 21 | GND                         | Ground                                             |

| GND                                | Ground                             | 82  | 22 | NC-SI_RXD0                  | BMC NC-SI                                          |

| GND                                | Ground                             | 83  | 23 | NC-SI_RXD1                  | BMC NC-SI                                          |

| CLK_100M_MEZZ1_DP                  | 100MHz PCI-E clock                 | 84  | 24 | GND                         | Ground                                             |

| CLK_100M_MEZZ1_DN                  | 100MHz PCI-E clock                 | 85  | 25 | GND                         | Ground                                             |

| GND                                | Ground                             | 86  | 26 | RSVD(CLK_100M_MEZZ<br>2_DP) | RSVD(2 <sup>nd</sup> set of 100MHz PCI-E<br>clock) |

| GND                                | Ground                             | 87  | 27 | RSVD(CLK_100M_MEZZ<br>2_DN) | RSVD(2 <sup>nd</sup> set of 100MHz PCI-E clock)    |

| MEZZ_TX_DP_C<0>                    | PCI-E TX signal                    | 88  | 28 | GND                         | Ground                                             |

| MEZZ_TX_DN_C<0>                    | PCI-E TX signal                    | 89  | 29 | GND                         | Ground                                             |

| GND                                | Ground                             | 90  | 30 | MEZZ_RX_DP<0>               | PCI-E RX signal                                    |

| GND                                | Ground                             | 91  | 31 | MEZZ_RX_DN<0>               | PCI-E RX signal                                    |

| MEZZ_TX_DP_C<1>                    | PCI-E TX signal                    | 92  | 32 | GND                         | Ground                                             |

| MEZZ_TX_DN_C<1>                    | PCI-E TX signal                    | 93  | 33 | GND                         | Ground                                             |

| GND                                | Ground                             | 94  | 34 | MEZZ_RX_DP<1>               | PCI-E RX signal                                    |

| GND                                | Ground                             | 95  | 35 | MEZZ_RX_DN<1>               | PCI-E RX signal                                    |

| MEZZ_TX_DP_C<2>                    | PCI-E TX signal                    | 96  | 36 | GND                         | Ground                                             |

| MEZZ_TX_DN_C<2>                    | PCI-E TX signal                    | 97  | 37 | GND                         | Ground                                             |

| GND                                | Ground                             | 98  | 38 | MEZZ_RX_DP<2>               | PCI-E RX signal                                    |

| GND                                | Ground                             | 99  | 39 | MEZZ_RX_DN<2>               | PCI-E RX signal                                    |

| MEZZ_TX_DP_C<3>                    | PCI-E TX signal                    | 100 | 40 | GND                         | Ground                                             |

| MEZZ_TX_DN_C<3>                    | PCI-E TX signal                    | 101 | 41 | GND                         | Ground                                             |

| GND                                | Ground                             | 102 | 42 | MEZZ_RX_DP<3>               | PCI-E RX signal                                    |

| GND                                | Ground                             | 103 | 43 | MEZZ_RX_DN<3>               | PCI-E RX signal                                    |

| MEZZ_TX_DP_C<4>                    | PCI-E TX signal                    | 104 | 44 | GND                         | Ground                                             |

| MEZZ_TX_DN_C<4>                    | PCI-E TX signal                    | 105 | 45 | GND                         | Ground                                             |

| GND                                | Ground                             | 106 | 46 | MEZZ_RX_DP<4>               | PCI-E RX signal                                    |

| GND                                | Ground                             | 107 | 47 | MEZZ_RX_DN<4>               | PCI-E RX signal                                    |

| MEZZ_TX_DP_C<5>                    | PCI-E TX signal                    | 108 | 48 | GND                         | Ground                                             |

| MEZZ_TX_DN_C<5>                    | PCI-E TX signal                    | 109 | 49 | GND                         | Ground                                             |

| GND                                | Ground                             | 110 | 50 | MEZZ_RX_DP<5>               | PCI-E RX signal                                    |

| GND                                | Ground                             | 111 | 51 | MEZZ_RX_DN<5>               | PCI-E RX signal                                    |

| MEZZ_TX_DP_C<6>                    | PCI-E TX signal                    | 112 | 52 | GND                         | Ground                                             |

| MEZZ_TX_DN_C<6>                    | PCI-E TX signal                    | 113 | 53 | GND                         | Ground                                             |

| GND                                | Ground                             | 114 | 54 | MEZZ_RX_DP<6>               | PCI-E RX signal                                    |

| GND                                | Ground                             | 115 | 55 | MEZZ_RX_DN<6>               | PCI-E RX signal                                    |

|                                    |                                    | 110 | 56 | GND                         | Ground                                             |

| MEZZ_TX_DP_C<7>                    | PCI-E TX signal                    | 116 | 50 | GND                         | Ground                                             |

| MEZZ_TX_DP_C<7><br>MEZZ_TX_DN_C<7> | PCI-E TX signal<br>PCI-E TX signal | 116 | 57 | GND                         | Ground                                             |

|                                    |                                    |     |    |                             |                                                    |

#### 7.8 I/O Connectors

Sections 7.8.1 through 7.8.5 describe the I/O connectors that reside on the Honey Badger baseboard.

#### 7.8.1 Power and Signal Connectors to Knox DPB

The new Honey Badger DPB has six PCI-E connectors, three on the A-side are adopted to interface with the system through the Honey Badger baseboard. Three on the B-side are reserved for future use. These straddle-type connectors are mated with 1mm pitch gold finger contacts and are PCI-E Gen3 capable. From left to right, the connectors are:

- A-side: An x1 connector (36 pin from Amphenol, P/N *G630H3612248EU*), mainly for low speed signals and ground pins.

- A-side: An x16 connector (164 pin from Amphenol, P/N *G630HAA12248EU*), for the rest of the low speed signals, all high speed signals, power and ground pins.

- A-side: An x1 connector (36 pin from Amphenol, P/N *G630H3612248EU*), only for power and ground pins.

- B-side: An x1 connector, an x16 connector, and an x1 connector.

Due to the large number of signals, the full connector pin definition is provided in Section 15.1. The following pin assignments are fixed for Honey Badger DPB and FCB:

- DPB Hardware Revision = o

- FCB Hardware Revision = o

#### 7.8.2 PCI-E x16 Connector to Panther+

A standard PCI-E x16 card edge connector on the Honey Badger baseboard provides the interface to and from the Panther+ Micro-Server card. Depending on the architecture and board layout, it can be a vertical type connector, such as AAA-PCI-006-G05 from Lotes; or a right-angled connector, such as ASP-177154-01 from Samtec.

Panther+ follows the x16 version of Micro-Server card specification, which can support two configurations.

- 1. Supports 3x PCI-E x4 + 1x Eth + 1x SATA + 8oW cards

- 2. Supports 1x PCI-E x4 + 1x PCI-E x8 + 1x Eth + 1x SATA + 8oW cards

Panther+ for Honey Badger (and later on storage projects) follows the 2<sup>nd</sup> configuration, but Honey Badger doesn't utilize the Ethernet port and the SATA port. Table 4 shows the draft pin assignments for this configuration.

The following pin assignments are applied to the Honey Badger baseboard for different storage solutions:

- Slot ID 12 (SVR\_ID = 0x1100) for Honey Badger baseboard, LSI solution

- Slot ID 13 (SVR\_ID = 0x1101) for Honey Badger baseboard, PMC solution

| Pin Name       | Side B | Side A | Pin Name       |

|----------------|--------|--------|----------------|

| P12V           | 1      | 1      | PRSNT#         |

| P12V           | 2      | 2      | P12V           |

| P12V           | 3      | 3      | P12V           |

| GND            | 4      | 4      | GND            |

| l2C_SCL        | 5      | 5      | SVR_IDo/GPIOo  |

| <br>I2C_DATA   | 6      | 6      | SVR_ID1/GPIO1  |

| GND            | 7      | 7      | COM_TX         |

| PWR_BTN#       | 8      | 8      | COM_RX         |

| USB_P          | 9      | 9      | SVR_ID2/GPIO2  |

| USB_N          | 10     | 10     | SVR_ID3/GPIO3  |

| SYS_RESET#     | 11     | 11     | PCIE_RESET#    |

|                |        |        |                |

| I2C_ALERT#     | 12     | 12     | GND            |

| GND            | 13     | 13     | PCIEo_REFCLK_P |

| GND            | 14     | 14     | PCIEo_REFCLK_N |

| PCIEo_TXo_P    | 15     | 15     | GND            |

| PCIEo_TXo_N    | 16     | 16     | GND            |

| GND            | 17     | 17     | PCIEo_RXo_P    |

| GND            | 18     | 18     | PCIEo_RXo_N    |

| PCIEo_TX1_P    | 19     | 19     | GND            |

| PCIEo_TX1_N    | 20     | 20     | GND            |

| GND            | 21     | 21     | PCIEo_RX1_P    |

| GND            | 22     | 22     | PCIEo_RX1_N    |

| PCIEo_TX2_P    | 23     | 23     | GND            |

| PCIEo_TX2_N    | 24     | 24     | GND            |

| GND            | 25     | 25     | PCIE0_RX2_P    |

| GND            | 26     | 26     | PCIEo_RX2_N    |

| PCIEo_TX3_P    | 27     | 27     | GND            |

| PCIEo_TX3_N    | 28     | 28     | GND            |

| GND            | 29     | 29     | PCIEo_RX3_P    |

| GND            | 30     | 30     | PCIEo_RX3_N    |

| SATAo_TX_P     | 31     | 31     | GND            |

| SATAo_TX_N     | 32     | 32     | GND            |

| GND            | 33     | 33     | SATAo_RX_P     |

| GND            | 34     | 34     | SATAo_RX_N     |

| PCIE1_REFCLK_P | 35     | 35     | GND            |

| PCIE1_REFCLK_N | 36     | 36     | GND            |

| GND            | 37     | 37     | RSVD           |

| GND            | 38     | 38     | RSVD           |

| PCIE1_RESET#   | 39     | 39     | GND            |

| RSVD           | 40     | 40     | GND            |

| GND            | 41     | 41     | RSVD           |

| GND            | 42     | 42     | RSVD           |

| RSVD           | 43     | 43     | GND            |

| RSVD           | 44     | 44     | GND            |

Table 4 Pin Assignments for Panther+ PCI-E Golden Finger

| GND         | 45 | 45 | RSVD        |

|-------------|----|----|-------------|

| GND         | 46 | 46 | RSVD        |

| RSVD        | 47 | 47 | GND         |

| RSVD        | 48 | 48 | GND         |

| GND         | 49 | 49 | PCIEo_RX4_P |

| GND         | 50 | 50 | PCIEo_RX4_N |

| PCIEo_TX4_P | 51 | 51 | GND         |

| PCIEo_TX4_N | 52 | 52 | GND         |

| GND         | 53 | 53 | PCIEo_RX5_P |

| GND         | 54 | 54 | PCIEo_RX5_N |

| PCIEo_TX5_P | 55 | 55 | GND         |

| PCIEo_TX5_N | 56 | 56 | GND         |

| GND         | 57 | 57 | PCIEo_RX6_P |

| GND         | 58 | 58 | PCIEo_R6_N  |

| PCIEo_TX6_P | 59 | 59 | GND         |

| PCIEo_TX6_N | 60 | 60 | GND         |

| GND         | 61 | 61 | PCIEo_RX7_P |

| GND         | 62 | 62 | PCIEo_RX7_N |

| PCIEo_TX7_P | 63 | 63 | GND         |

| PCIEo_TX7_N | 64 | 64 | GND         |

| GND         | 65 | 65 | PCIE1_RX0_P |

| GND         | 66 | 66 | PCIE1_RX0_N |

| PCIE1_TX0_P | 67 | 67 | GND         |

| PCIE1_TX0_N | 68 | 68 | GND         |

| GND         | 69 | 69 | PCIE1_RX1_P |

| GND         | 70 | 70 | PCIE1_RX1_N |

| PCIE1_TX1_P | 71 | 71 | GND         |

| PCIE1_TX1_N | 72 | 72 | GND         |

| GND         | 73 | 73 | PCIE1_RX2_P |

| GND         | 74 | 74 | PCIE1_RX2_N |

| PCIE1_TX2_P | 75 | 75 | GND         |

| PCIE1_TX2_N | 76 | 76 | GND         |

| GND         | 77 | 77 | PCIE1_RX3_P |

| GND         | 78 | 78 | PCIE1_RX3_N |

| PCIE1_TX3_P | 79 | 79 | GND         |

| PCIE1_TX3_N | 80 | 80 | GND         |

| GND         | 81 | 81 | P12V        |

| GND         | 82 | 82 | P12V        |

#### 7.8.3 Debug Header

The Honey Badger baseboard includes a debug header on the front side. It supports hot plugging for an existing debug card. The debug card has been used in Open Compute servers and Open Vault storage system (Knox). It contains the following functionalities:

• Two 7-segment LED displays. Shows BIOS POST information and CPU system error codes, or storage system error codes.

- One RS-232 serial connector. Provides console redirection.

- One reset button. When pressed, triggers either a CPU system reset or a storage system (expander) reset.

- One UART channel selection button. Sends a positive pulse to the Honey Badger baseboard to select and rotate the UART console in a loop of:

- Host console -> BMC debug console -> SAS controller console -> SAS expander console.

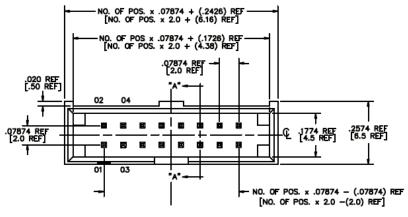

The connector for the debug header is a 14-pin, shrouded, right-angled, 2 mm pitch connector. Figure 24 shows an illustration. The debug card has a key to match with the notch to avoid pin shift when plugging it in.

Figure 24 Debug Header Illustration

Table 5 lists the pin definition of the debug header.

Table 5 Debug Header Pin-out

| Pin (CKT) | Function                                     |

|-----------|----------------------------------------------|

| 1         | Low HEX character [o] least significant bit  |

| 2         | Low HEX character [1]                        |

| 3         | Low HEX character [2]                        |

| 4         | Low HEX character [3] most significant bit   |

| 5         | High HEX character [o] least significant bit |

| 6         | High HEX character [1]                       |

| 7         | High HEX character [2]                       |

| 8         | High HEX character [3] most significant bit  |

| 9         | Serial Transmit                              |

| 10        | Serial Receive                               |

| 11        | System Reset                                 |

| 12        | UART Channel Selection                       |

| 13        | GND                                          |

| 14        | VCC (5VDC)                                   |

## 7.8.4 External Mini-SAS Connector

The external Mini-SAS connector is to connect Knox SEB in another tray within the same Honey Badger system, so that to support the use case of 1:30 compute to HDD ratio. The Mini-SAS connector is in SFF-8088 standard form factor, and it's referred to as a Mini-SAS-4x connector. Its part number is  $G_{40}BR_{261}BEU$  from AMPHENOL, or equivalent. The connector pin-out is shown in Table 6.

| Pin            | Assignment        | Pin | Assignment |

|----------------|-------------------|-----|------------|

| Aı             | GND               | Bı  | GND        |

| A2             | RxoP              | B2  | ТхоР       |

| A <sub>3</sub> | RxoN              | B3  | TxoN       |

| A4             | GND               | В4  | GND        |

| A5             | Rx1P              | B5  | Tx1P       |

| A6             | Rx1N              | B6  | Tx1N       |

| A7             | GND               | B7  | GND        |

| A8             | Rx2P              | B8  | Tx2P       |

| Ag             | Rx2N              | B9  | Tx2N       |

| A10            | GND               | B10 | GND        |

| A11            | Rx3P              | B11 | ТхзР       |

| A12            | Rx <sub>3</sub> N | B12 | Tx3N       |

| A13            | GND               | B13 | GND        |

Table 6 External Mini-SAS-4x Connector Pin-out

The part number of EMI cage for Mini-SAS connector is Molex 74548-0211, or equivalent.

#### 7.8.5 Internal Mini-SAS Connector

The internal Mini-SAS connector is reserved for cascading purpose (to connect Knox SEB in another system). This connector is in SFF-8087 standard form factor, or referred to as Mini-SAS-4i connectors. The part number is 75783-0012 from Molex, or equivalent. The connector pin-out is shown in Table 7.

| Pin            | Assignment | Pin | Assignment |

|----------------|------------|-----|------------|

| Aı             | GND        | B1  | GND        |

| A2             | RxoP       | B2  | ТхоР       |

| A <sub>3</sub> | RxoN       | B3  | TxoN       |

| A4             | GND        | В4  | GND        |

| A5             | Rx1P       | B5  | Tx1P       |

| A6             | Rx1N       | B6  | Tx1N       |

| A7             | GND        | B7  | GND        |

| A8             | NC         | B8  | NC         |

| Ag             | NC         | B9  | NC         |

Table 7 Internal Mini-SAS-4x Connector Pin-out

| A10 | NC   | B10 | NC   |

|-----|------|-----|------|

| A11 | NC   | B11 | NC   |

| A12 | GND  | B12 | GND  |

| A13 | Rx2P | B13 | Tx2P |

| A14 | Rx2N | B14 | Tx2N |

| A15 | GND  | B15 | GND  |

| A16 | Rx3P | B16 | Tx3P |

| A17 | Rx3N | B17 | Tx3N |

| A18 | GND  | B18 | GND  |

### 7.8.6 USB Hub and Connector

The Honey Badger baseboard requires one external USB port located in the front. It should be a standard Type-A USB connector, to support the following devices.

- USB keyboard and mouse

- USB flash drive (bootable)

- USB hard drive (bootable)

- USB optical drive (bootable)

The Honey Badger baseboard also requests an USB hub, which routes the USB port from the Panther+ to both the USB connector and the BMC chip. This was shown in the block diagrams of Figure 19 and Figure 20, in Section 7.2.

## 7.9 Switch and Buttons

### 7.9.1 Sub-System Selection for Debug Card

As a storage server, Honey Badger contains two sub-systems. One is the CPU system, the other is the storage system. Each sub-system has both of the debug features mentioned in Section 7.8.3: two digit error codes displayed on a 7-Segment LED, and the reset switch to trigger a sub-system reset.

On a Honey Badger baseboard, there is a slide switch located besides the debug header. It will be used to select which sub-system is to be debugged.

- When the CPU sub-system is selected (default setting):

- The debug card displays a POST 80 code from the Panther+ card (through I<sub>2</sub>C to BMC), driven by the BMC

- The reset button on the debug card will trigger a CPU system reset

- When the storage sub-system is selected:

- The debug card displays the storage system error code as defined in Knox (Open Vault Storage), driven by SAS expander

- $\circ$  ~ The reset button on debug card will trigger a SAS expander reset

A red LED is located close to the slide switch, to indicate when storage sub-system is selected and debugged.

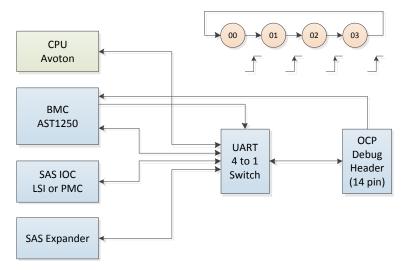

#### 7.9.2 UART Switch Button

Also, as mentioned in Section 7.8.3, the debug card has a push button that's used for UART channel selection. A related functional diagram is shown in Figure 25.

Figure 25 Concept of UART Channel Selection

### 7.9.3 Power and Reset Buttons

On the Honey Badger baseboard, there are two switch buttons for the whole compute module:

- Power switch (red)

- System reset switch (black)

The vertical tactile switch buttons must be placed in an easy accessible area. The push button actuator must have a minimum 2.5 mm diameter and must protrude 7 mm to 9 mm from top of the actuator to the PCB surface.

- When only one button can be placed to the front edge, the power switch is the outer one, and the systems reset switch is the inner one.

- If the power switch is depressed for durations less than four seconds, a power management event will occur. This event indicates that the power switch has been triggered.

- If the power switch is depressed for longer than four seconds, the Honey Badger baseboard and Panther+ card shall perform a hard power off.

- If the reset switch is depressed for any duration of time, the Honey Badger baseboard and Panther+ card shall perform a hard reset and begin executing BIOS initialization code.

The functionality of each switch shall be indicated by a label on the Honey Badger baseboard's silk screen. The labels PWR and RST are acceptable.

### 7.10 LEDs

The Honey Badger baseboard has two LEDs on its front edge, to display various types of information:

- One single color in blue, for power and system identify

- One single color in red, for enclosure fault status

Table 8 summarizes the power and system identify LED behaviors.

Table 8 Power and System Identify LED

| Power and System Identify      | Blue LED                        |  |  |

|--------------------------------|---------------------------------|--|--|

| Power off, System Identify off | Consistently off                |  |  |

| Power off, System Identify on  | On o.1sec, off o.9sec, and loop |  |  |

| Power on, System Identify off  | Consistently on                 |  |  |

| Power on, System Identify on   | On 0.9sec, off 0.1sec, and loop |  |  |

Table 9 summarizes the enclosure fault status LED behaviors.

Table 9: Enclosure Fault Status LED

| Enclosure Fault Status       | Red LED  |

|------------------------------|----------|

| Normal system operation      | Off      |

| Any fault in whole enclosure | On       |

| Reserved for future use      | Blinking |

#### PCB Stack-up 7.11

PCB thickness of Honey Badger baseboard is 1.6mm. For a typical 8 layers' PCB stack-up, Table 10 shows one example with details. Table 11 shows the impedance control accordingly. Based on different PCB material, placement and routing strategies, vendor may adjust the stack-up slightly. But it should be communicated with Facebook and get approval in advance.

|--|

| Layer          | Plane Description |             | Copper Weight<br>(oz) | Thickness<br>(mil) | Dielectric (er) |

|----------------|-------------------|-------------|-----------------------|--------------------|-----------------|

|                |                   | Solder Mask |                       | 0.5                | 3.7             |

| Lı             | TOP               | Signal      | 0.5 + 1.0             | 1.9                |                 |

|                |                   | PrePreg     |                       | 2.7                | 3.5             |

| L2             | GND1              | Ground      | 1.0                   | 1.3                |                 |

|                |                   | Core        |                       | 4.0                | 3.6             |

| L <sub>3</sub> | IN1               | Signal      | 1.0                   | 1.3                |                 |

|                |                   | PrePreg     |                       | 17.0               | 4.5             |

| L4             | VCC1              | Power       | 1.0                   | 1.3                |                 |

|                |                   | Core        |                       | 3.0                | 3.5             |

| L5             | VCC2              | Power       | 1.0                   | 1.3                |                 |

|                |                   | PrePreg     |                       | 17.0               | 4.5             |

| L6             | IN2               | Signal      | 1.0                   | 1.3                |                 |

|                |                   | Core        |                       | 4.0                | 3.6             |

| L7             | GND2              | Ground      | 1.0                   | 1.3                |                 |

|    |     | PrePreg                        |           | 2.7  | 3.5     |

|----|-----|--------------------------------|-----------|------|---------|

| L8 | BOT | Signal                         | 0.5 + 1.0 | 1.9  |         |

|    |     | Solder Mask                    |           | 0.5  | 3.7     |

|    |     | Total Thickness and Tolerance: |           | 63.0 | +/-6mil |

Table 11: PCB Impedance Control for Honey Badger Baseboard

| Trace Width<br>(mil) | Air Gap<br>Spacing (mil) | Impedance<br>Type | Layer | Impedance<br>Target (ohm) | Tolerance<br>(+/-) |

|----------------------|--------------------------|-------------------|-------|---------------------------|--------------------|

| 4.5                  |                          | Single            | 1,8   | 50                        | 5 ohm              |

| 5.5                  | 8.0                      | Differential      | 1,8   | 85                        | 10%                |

| 4.0                  | 9.5                      | Differential      | 1,8   | 100                       | 10%                |

| 5.0                  |                          | Single            | 3,6   | 50                        | 5 ohm              |

| 5.0                  | 6.0                      | Differential      | 3, 6  | 85                        | 10%                |

| 4.0                  | 9.0                      | Differential      | 3,6   | 100                       | 10%                |

## 8 Board Level Power Budget

This section lists the PCBA level power budget for Honey Badger, both the feature and the entry models.

## 8.1 Feature Model Power Budget

Board level power budget of Honey Badger feature model is about 75W. Table 12 shows the details of calculation estimated as of now.

| Major Device                   | TDP max (W)     | Qty   | Utilization (%) | Power (W) |

|--------------------------------|-----------------|-------|-----------------|-----------|

| Processor (Avoton) 8 core      | 20              | 1     | 90%             | 18        |

| DDR3 U-DIMM / SO-DIMM          | 5               | 4     | 70%             | 14        |

| M-SATA SSD                     | 2.3             | 1     | 70%             | 1.61      |

| PCI-E NGFF Flash               | 3               | 1     | 70%             | 2.1       |

| Other uServer Card Logic/IC    | 2               | 1     | 80%             | 1.6       |

| Power Buidget for Panth        | ner+ Card, High | n Cor | nfiguration     | 37.31     |

| 12G 8 port SAS Controller      | 17              | 1     | 80%             | 13.60     |

| 12G 24 port SAS Expander       | 12.5            | 1     | 80%             | 10.00     |

| 10G Card (Ethernet controller) | 10              | 1     | 80%             | 8         |

| BMC AST1250                    | 2               | 1     | 80%             | 1.6       |

| Other Baseboard Logic/IC       | 90%             | 3.6   |                 |           |

| USB2.0                         | 50%             | 1.25  |                 |           |

| Board Power Buidget for        | Baseboard       | 38.05 |                 |           |

| Total Power Buidge             | 75.36           |       |                 |           |

Table 12 Honey Badger Power Budget for Feature Model

## 8.2 Entry Model Power Budget

The board level power budget of Honey Badger X86 entry model is about 59W. Table 13 shows the details of calculation estimated as of now.

| Major Device                   | Power (W) |       |     |       |

|--------------------------------|-----------|-------|-----|-------|

| Processor (Avoton) 4 core      | 14        | 1     | 90% | 12.6  |

| DDR3 U-DIMM / SO-DIMM          | 5         | 2     | 70% | 7     |

| M-SATA SSD                     | 2.3       | 1     | 70% | 1.61  |

| PCI-E NGFF Flash               | 3         | 0     | 70% | 0     |

| Other uServer Card Logic/IC    | 2         | 1     | 80% | 1.6   |

| Power Buidget for Panthe       | 22.81     |       |     |       |

| 12G 8 port SAS Controller      | 17        | 1     | 70% | 11.90 |

| 12G 24 port SAS Expander       | 80%       | 10.00 |     |       |

| 10G Card (Ethernet controller) | 10        | 1     | 80% | 8     |

| BMC AST1250                    | 2         | 1     | 80% | 1.6   |

| Other Baseboard Logic/IC       | 4         | 1     | 90% | 3.6   |

| USB2.0                         | 1.25      |       |     |       |

| Board Power Buidget for        | 36.35     |       |     |       |

| Total Power Buide              | 59.16     |       |     |       |

Table 13 Honey Badger Power Budget for X86 Entry Model

## 9 BIOS Feature List

The Honey Badger BIOS design will follow the same requirements as the Panther+, or the generic Micro-Server card. Please refer to the documents as described in Section 6.1 or Section 6.2. Highlighted key items as below:

- UEFI compatible

- Configuration and features

- Disable unused devices

- o BIOS setup menu

- SoC settings to allow tuning to achieve the optimal combination of performance and power consumption

- BIOS settings tools

- Default boot device priority

- Network / PXE -> mSATA SSD module -> NGFF flash card -> Other removable devices

- PXE boot

- Supports PXE boot and provide the ability to modify the boot sequence. When PXE booting, the card first attempts to boot from the first Ethernet device (etho). If this fails, the PXE boot will attempt on the next Ethernet device.

- PXE timeout timer set to 10 seconds (only for booting from OCP Mezz Card)

- iSCSI network boot

- Other boot options

- Also supports booting from SATA/SAS and USB interfaces

- o Provides the capability to select boot options

- Remote BIOS update

- Scenario 1: Sample/audit BIOS settings

- Scenario 2: Update BIOS with pre-configured set of BIOS settings

- Scenario 3: BIOS/firmware update with a new revision

- Update from the operating system over the LAN

- Can complete BIOS update or setup change with a single reboot (no PXE boot, no multiple reboots)

- No user interaction (e.g., prompts)

- BIOS updates and option changes do not take longer than five minutes to complete

- Can be scripted and propagated to multiple machines

- Event log

- Implement SMBIOS type 15 per SMBIOS specification Rev 2.6

- Hold more than 500 event records (assuming the maximum event record length is 24 bytes, then the size will be larger than 12KB)

- Each event record includes enhanced information identifying the error source device's vendor ID, card slot ID, and device ID

- A system access interface and application software to retrieve and clear the event log from the BIOS

- Logged errors

- o CPU/memory errors

- o PCI-E errors

- o POST errors

- o SATA errors

- System reboot events

- Sensor values exceeding warning or critical thresholds

- Error thresholds

- Setting must be enabled for both correctable and uncorrectable errors

- Threshold for Memory Correctable ECC is TBD

- PCI-E error, follow chipset vendor's suggestion

- POST codes

- To be displayed on debug card

- To be provided on the serial console

## 10 BMC and System Enclosure Management

The Honey Badger baseboard has a BMC for various platform management services and interfaces. Storage sub-system is on the baseboard. The compute module is on the Panther+Micro-Server card.

The BMC should be a standalone system operating in parallel to host (Honey Badger baseboard and Panther+ card). The health status of the host system should not affect the normal operation and network connectivity of the BMC. The BMC cannot share memory with the host system. Management connectivity for the BMC should work independently from the host, and have no NIC driver dependency for Out-Of-Band (OOB) communication while using a shared-NIC.

The BMC firmware must support IPMI 2.0 compliant features. All features must be remotely accessible.

## 10.1 Management Network Interface

The BMC should have both an I<sub>2</sub>C port and a RMII/NC-SI port for OOB access.

The BMC firmware needs to be flexible about which interface and device to activate by either hardware strapping or via a preset priority policy. The BMC firmware needs to make sure the unused interfaces and devices are disabled and do not interfere with the activated management interface and device.

The BMC management network firmware and utilities need to support all features defined in this specification in both an IPv4 and IPv6 network environment.

## 10.2 Local Serial Console and SoL

The BMC needs to support two paths to access the serial console. It is preferred that both interfaces are functional at all stages of system operation.

- A local serial console on debug header/debug card, as described in Section 7.8.3 and Section 7.9.2

- A remote console, also known as Serial-over-LAN (SoL) through management network described in Section 10.1.

The BMC firmware and baseboard circuitry design should enable the Local console and remote SoL in the same time, which includes both input and output, bidirectional.

When the system boots, POST codes are sent to Port 80 and decoded by the BMC to drive the LED display on the debug card. POST codes should be displayed in the SoL console during system POST. Before the system displays the first screen, POST codes are dumped to and displayed in the SoL console in sequence. After the system shows the first screen in the SoL console, the last POST code received on Port 80 is displayed in the lower right corner of the SoL console screen.

A serial console buffer feature is required. The buffer needs to save at least last five screens of local and five screens of remote console output; 80 columns x 24 rows for each screen. OOB raw command is used to extract and display the buffer. The buffer has to be stored in volatile media such as internal or external SDRAM of the BMC. Buffer data is cleared within five seconds of the removal of standby power. Buffer should NOT be stored in any non-volatile media.

## 10.3 Remote Power Control and Power Policy

The vendor should implement BMC firmware to support remote system power on/off/cycle and warm reboot through the In-Band or Out-Of-Band IPMI command.

The vendor should implement BMC firmware to support the power on policy to be last-state, always-on, and always-off. The default setting is last-state. The change of power policy should be supported by IPMI command and take effect without BMC firmware cold reset or a system reboot.

It should take less than 3 seconds from AC on for the BMC to process the power button signal and power up the system for POST. A long waiting period from AC on, for BMC firmware to get ready before allowing system POST start is NOT allowed.

## 10.4 Port 80 POST Code

The vendor should implement BMC to support Port 80 POST code display to drive 8 bit HEX GPIO to debug header. The BMC post function need to be ready before system BIOS starts to send 1<sup>st</sup> POST code to Port 80. POST code should also be sent to SoL as well.

BMC should have access to POST code and record up to 20x POST codes. OOB raw command can be used to retrieve last 20x POST code from BMC.

### 10.5 BMC Firmware Update

Vendors should provide tool(s) to implement a remote BMC firmware update. The firmware update should not require any physical input at the system. Remote update means either by OOB by the management network or by logging into the local OS (CentOS) through the data network. Tool(s) shall support CentOS 5.2 / CentOS 6.4 and the updated Facebook Kernel (FBK).

A remote BMC firmware update may take a maximum of five minutes to complete. The BMC firmware update process and the BMC reset process require that the host system neither reboot nor power down. The reset should have no impact to host system's normal operation. The BMC needs to be fully functional with updated firmware after the update. It must reset without further configuration.

The default update should recover the BMC to the factory default settings. There must be an option to preserve SEL and configuration. The MAC address should not be cleared with any BMC firmware update.

### 10.6 System Sensors

The BMC has access to all analog sensors, discrete sensors and event only sensors on the Honey Badger baseboard, Panther+ card (through the I2C management interface from FPGA), and the Knox system (DPB and FCB). All connected sensors need to be displayed in the sensor data record (SDR) repository.

The sensors required are below. The related lower and upper critical thresholds are listed for system event logging purposes.

- Analog sensors

- CPU Temp sensor(s)

- CPU Package Power (PECI)

- DIMM Temperature(s)

- Panther+ on-board Temp sensor(s)

- Panther+ on-board Voltage(s)

- o SAS Controller Temp sensor

- o SAS Expander Temp sensor

- Baseboard on-board Temp sensor(s)

- Baseboard on-board Voltage(s)

- Knox FCB HSC Input Voltage

- o Knox FCB HSC Output Voltage

- Knox FCB HSC Output Current

- Knox FCB HSC Output Power

- Knox FCB BJT Temp sensor(s)

- Knox DPB Voltage(s)

- Knox DPB on-board Tem sensor(s)

- Knox Fan Speed(s)

- Discrete sensors

- System Status: Thermal trip, CATERR, System throttle

- SEL Status: Clear, Rollover

- DCMI Watchdog

- Processor Fail

- Chassis Power Status

- o System Booting Status

- o Thermal Limit 1

- o VR HOT

- CPU / DIMM HOT

- CPU Error

- PMBus Status Word: High, Low

- DIMM UCE

- Event only sensors

- o POST Error

- Proc Hot Ext

- o Mem Hot Ext

- Machine Check Error

- o PCI-E Error

- Voltage Error

- Memory ECC Error

### 10.7 System Event Log

The vendor should implement BMC to support the System Event Log (SEL).

- Errors to be logged

- o I2C bus status error

- o Power error

- Fan failure

- o Voltage failure

- o Thermal events

- HDD fault

- Mini-SAS link error

- Tray pulled out

- System reboot events

- Critical SEL filter

- OEM commands are required to set and display two different level of SEL filtering. The default is to log all errors during EVT/DVT/PVT with the option to log only critical SELs that need service or indicate power cycle state change, and SEL clear and overflow

- The scope of the critical SEL list is TBD

## 10.8 Fan Speed Control

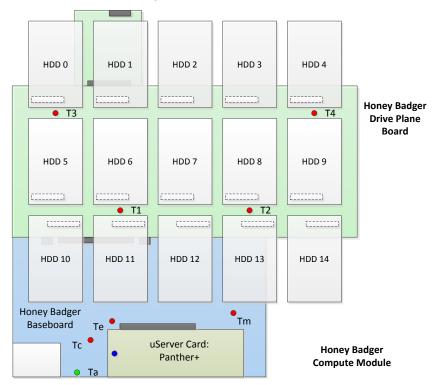

The Honey Badger baseboard BMC is responsible for fan speed control. The control algorithm should be based on all temperature sensors' information and thermal profile. Temperature sensors' location are shown in Figure 26 below.

Figure 26 Honey Badger System Thermal Sensor Locations

Consider these key sensors for the fan speed control algorithm:

- Honey Badger compute module

- CPU core temperature from PECI

- One ambient temperature sensor on the Panther+ card

- One ambient temperature sensor on the Honey Badger baseboard, for inlet temperature

- Ta is the ambient temperature sensor for inlet.

- Three ambient temperature sensors on the Honey Badger baseboard, for hot spot temperatures

- Please refer to Tc, Te and Tm respectively

- Knox storage system enclosure

- Four ambient temperature sensors on the drive plane board

Please refer to T1, T2, T3 and T4 respectively

The Honey Badger thermal design should meet these two targets at the same time:

- Ensure all Honey Badger on-board key component temperatures meet thermal requirements with enough margin in all operating environment temperature ranges (e.g., Avoton CPU, SAS controller, SAS expander, etc.)

- Ensure all Knox system component temperatures meet thermal requirements with enough margin in all operating environment temperature ranges. For example, all hard disk drives.

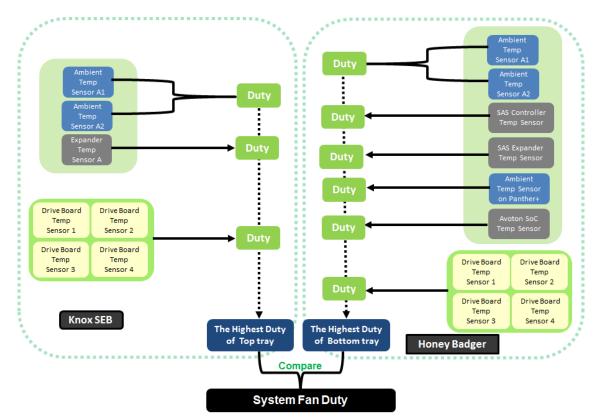

The ODM should be responsible to provide a detailed implementation of the fan speed control requirements. Figure 27 shows the high-level strategy of the fan speed control for Knox systems with Honey Badger, executed by firmware in the existing Knox SEB (SAS expander), and the new Honey Badger baseboard (BMC).

The fan control tables must be upgradeable on the fly (i.e., no system reboot required). Or, an override mechanism must be provided to set fan speed manually without requiring a system reboot.

Figure 27 Honey Badger System Fan Speed Control Strategy

## 10.9 Thermal Protection

There are different levels of consideration for software and hardware thermal protection for the Honey Badger system. They include:

• Setting a Warning level for each monitored parameter (including all temperatures,

voltages and input power). When any one of the parameters reaches its warning value, the firmware should report an alarm status to the host server. The host server can predictively perform some actions to avoid actual (both hardware and software) protection in advance.