# Twin Lakes 1S Server Design Specification

V0.<u>95</u>

Deleted: 5

Author:

Yan Zhao, Hardware Engineer, Facebook Jon Ehlen, Mechanical Engineer, Facebook Damien Chong, Hardware Engineer, Facebook Ben Wei, Software Engineer, Facebook Jarrod Clow, Thermal Engineer, Facebook

# Copyrights and Trademarks

Intel® is a trademark of Intel Corporation in the U.S. and/or other countries. Xeon® is a trademark of Intel Corporation in the U.S. and/or other countries. Texas Instruments<sup>TM</sup> is a trademark of Texas Instruments Incorporated. Tiva<sup>TM</sup> is a trademark of Texas Instruments Incorporated.

Deleted: Feb

Nov, 2, 2017

2

Deleted: 1

# 1 Scope

This specification describes the design of the Twin Lakes 1S server based on the Intel® Next Gen Xeon® Processor D System-on-a-Chip (SoC).

# 2 Contents

| Со | pyrights | and Trademarks                        | 2 |             |

|----|----------|---------------------------------------|---|-------------|

| 1  | Scope .  |                                       | 3 |             |

| 2  | Conten   | ts                                    | 3 |             |

| 3  | Overvie  | ew                                    | 5 |             |

| 4  | License  | ,                                     | 8 |             |

| 5  | Mecha    | nical                                 | 9 |             |

|    | 5.1      | Mechanical Outline                    | 9 |             |

|    | 5.2      | PCIe Edge Connector1                  | 5 | Deleted: 13 |

|    | 5.3      | Platform Design <u>1</u>              | 5 | Deleted: 13 |

| 6  | Therma   | al <u>1</u>                           | 5 | Deleted: 14 |

|    | 6.1      | Data Center Environmental Conditions1 | 5 | Deleted: 14 |

|    | 6.2      | Server Operational Conditions1        | 5 | Deleted: 14 |

|    | 6.3      | CPU cooling solution1                 | 7 | Deleted: 15 |

|    | 6.4      | M.2 Cooling Solution1                 | 8 | Deleted: 17 |

|    | 6.5      | Temperature and Power Sensors1        | 9 | Deleted: 17 |

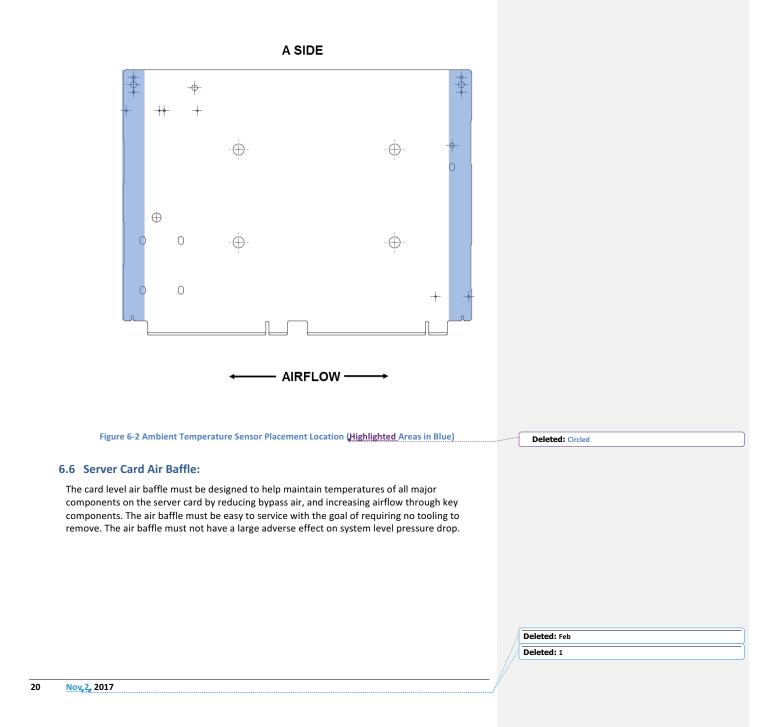

|    | 6.6      | Server Card Air Baffle:2              | 0 | Deleted: 18 |

| 7  | Electric | al2                                   | 1 | Deleted: 19 |

|    | 7.1      | Design Guidelines2                    | 1 | Deleted: 19 |

|    | 7.2      | Primary X16 Edge Connector A 2        | 1 | Deleted: 19 |

|    | 7.3      | Extension X16 Edge Connector B 2      | 4 | Deleted: 22 |

|    | 7.4      | Pin Definitions2                      | 7 | Deleted: 24 |

|    | 7.5      | Ethernet                              | 2 | Deleted: 30 |

|    | 7.6      | SATA3                                 | 2 | Deleted: 30 |

|    | 7.7      | USB <u>3</u>                          | 2 | Deleted: 30 |

|    | 7.8      | Serial port3                          | 3 | Deleted: 30 |

|    | 7.9      | PCIe                                  | 3 | Deleted: 30 |

|    | 7.10     | I <sup>2</sup> C <u>3</u>             | B | Deleted: 30 |

|    | 7.11     | NIC Sideband                          | B | Deleted: 31 |

|    |          |                                       | • |             |

## Open Compute Project • Twin Lakes 1S Server Design Specification

|    | 7.12     | Slot ID and GPIO                |    | Deleted: 31 |

|----|----------|---------------------------------|----|-------------|

| 8  | Power.   |                                 |    | Deleted: 32 |

|    | 8.1      | Input                           | -1 | Deleted: 32 |

|    | 8.2      | VR Efficiency                   | -1 | Deleted: 32 |

|    | 8.3      | Input Capacitance               |    | Deleted: 32 |

|    | 8.4      | Power reading and power capping | -  | Deleted: 32 |

| 9  | Functio  | nal                             | -  | Deleted: 34 |

|    | 9.1      | System on a Chip                |    | Deleted: 34 |

|    | 9.2      | Memory                          |    | Deleted: 34 |

|    | 9.3      | Debug headers                   |    | Deleted: 34 |

|    | 9.4      | Storage                         |    | Deleted: 34 |

|    | 9.5      | EEPROM                          |    | Deleted: 34 |

|    | 9.6      | BIOS                            |    | Deleted: 35 |

|    | 9.7      | Twin Lakes 1S Server Management |    | Deleted: 38 |

|    | 9.8      | LEDs                            |    | Deleted: 56 |

| 10 | Enviror  | mental Requirements             |    | Deleted: 57 |

|    | 10.1     | Vibration and Shock             |    | Deleted: 57 |

| 11 | Prescril | ped Materials                   |    | Deleted: 58 |

|    | 11.1     | Disallowed Components           |    | Deleted: 58 |

|    | 11.2     | Capacitors and Inductors        |    | Deleted: 58 |

|    | 11.3     | Component De-rating             |    | Deleted: 58 |

| 12 | Labels   | Ind Markings                    | -  | Deleted: 59 |

| 13 | Revisio  | n History                       |    | Deleted: 60 |

Deleted: Feb

Deleted: 1

<u>Nov, 2,</u> 2017

4

# 3 Overview

This document describes a single socket server design based on the Intel® Next Gen Xeon® Processor D, which is referred to hereinafter as Twin Lakes 1S server.

The Twin Lakes 1S server is designed to use a next generation Intel<sup>®</sup> Xeon<sup>®</sup> Processor D utilizing the performance and advanced Intelligence of Intel<sup>®</sup> Xeon<sup>®</sup> processors packaged into a dense, low-power SoC.

Fueled by Intel<sup>®</sup> Xeon<sup>®</sup> Processor D SoC, integrating a multi-core CPU, memory controller, and input/output (IO) device capabilities, the Twin Lakes 1S server is great for single or multimode platforms where a solid balance of performance and IO density are key criteria. However, platform designers must provide adequate power and cooling to properly handle the SoC's power and thermal requirements.

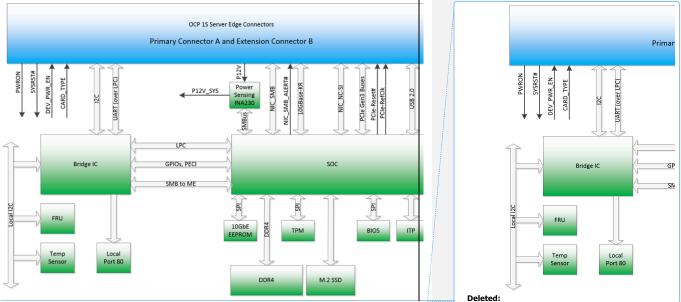

Figure 3-1 illustrates the Twin Lakes 1S server block diagram.

Figure 3-1 Twin Lakes 1S Server Block Diagram

The Twin Lakes 1S server implements primary and extension x16 PCIe edge connectors as defined in the 1S server specification. The primary x16 PCIe edge connector supports:

- PCle Gen3 ports

- A 10GBase-KR

- A SATA port

- A USB 2.0 port

- A Universal Asynchronous Receiver/Transmitter (UART)

- An I<sup>2</sup>C bus for server management

- A System Management Bus (SMBus) as the sideband of the integrated network controller

The extension x16 PCIe edge connector supports:

- A Network Controller Sideband Interface (NC-SI) as an alternative sideband of the integrated network controller

- PCle Gen3 ports

The Twin Lakes 1S server supports three on-card Solid State Drives (SSDs) in the 2280 or 22110 M.2 form factor. One of the M.2 SSD drives is used as boot drive, which is on bottom side of the card next to the SOC. The x4 PCIe link to the boot drive is connected to the PCH portion of the SOC. The boot M.2 drive can be configured to use SATA as the electrical interface through BOM option. Regardless of the electrical interface, the recommended minimum capacity of the boot drive is 256GB. Due to the usage model and capacity of the boot M.2 drive, only 2280 form factor is supported.

The other two M.2 SSD drives are targeted for high performance use case thus only PCIe X4 links from the CPU portion of the SOC are connected to them. Both of them support 2280 or 22110 form factors.

The Twin Lakes 1S server can use either an external network interface controller on the platform through its PCIe interface, or the SoC's own integrated network controller. Generally, the Twin Lakes 1S server assumes a Baseboard Management Controller (BMC) is used on the platform. When the integrated network controller on the SoC is used as a shared NIC, it will support SMBus as the sideband to the BMC on the platform in all power states.

The Twin Lakes 1S server receives 12.5V from the platform with a maximum current load of 7.7A from the primary edge connector and an additional 7.7A from the extension edge connector. The platform, however, defines and controls the maximum power used by the Twin Lakes 1S server. The Twin Lakes 1S server uses the INA230 power sensor at the power input to measure the total card power consumption of the whole server with +/-1% accuracy. The power data measured by this sensor can be used by the platform for power management purposes. When the power consumption has exceeded the power limit, the Bridge IC will generate a throttle event to force the SoC throttle to the lowest power state. The Twin Lakes 1S server supports an Advanced Configuration Power Interface (ACPI)-compliant power button and reset signals from the platform.

A Bridge IC (Texas Instrument's Tiva microcontroller) is used as the management controller on the 1S server and the bridge between the BMC and the SoC. The Bridge IC manages the 1S server on behalf of the BMC on the platform and bridges the BMC and Intel® Next Gen Xeon® Processor D SoC's internal management controller Intel® Manageability Engine. To maximize the communication bandwidth between the BMC and the Bridge IC, a dedicated point-to-point I<sup>2</sup>C bus shall be used.

Twin Lakes 1S server's Field Replaceable Unit (FRU) <u>EEPROM</u> and thermal sensors are connected to the Bridge IC's other I<sup>2</sup>C buses. There are multiple General Purpose Input/Output connections (GPIOs) between the Bridge IC and Intel® Next Gen Xeon® Processor D SoC for error reporting and other management purposes. Intel® Next Gen Xeon® Processor D SoC's Intel® Manageability Engine is connected to the Bridge IC via an I<sup>2</sup>C interface so that the Bridge IC can poll information from the Intel® Manageability Engine. A Low Pin Count (LPC) bus between the

Deleted: Feb

Nov, 2, 2017

6

Bridge IC and the Intel® Next Gen Xeon® Processor D SoC is connected to enable in-band communications. The BMC can access the Twin Lakes 1S server's thermal sensors, FRU, Intel® Next Gen Xeon® Processor D SoC's GPIOs and Intel® Manageability Engine via the Bridge IC with standard IPMI commands.

BIOS, network controller and boot ROM of Bridge IC on the Twin Lakes 1S server, can be updated from in-band connectivity by the SoC or out-of-band thru BMC. While other firmwares (CPLD and VRs) are programmable from out-of-band connectivity by the Bridge IC and BMC.

# 4 License

#### © 2016 Facebook.

As of July 26, 2016, the following persons or entities have made this Specification available under the Open Compute Project Hardware License (Permissive) Version 1.0 (OCPHL-P), which is available at <a href="http://www.opencompute.org/../spec-submission-process/">http://www.opencompute.org/../spec-submission-process/</a>.

#### Facebook, Inc.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The Specification implementer and user assume the entire risk as to implementing or otherwise using the Specification. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS

GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE."

<u>Nov, 2,</u> 2017

8

Deleted: Feb Deleted: 1

# 5 Mechanical

# 5.1 Mechanical Outline

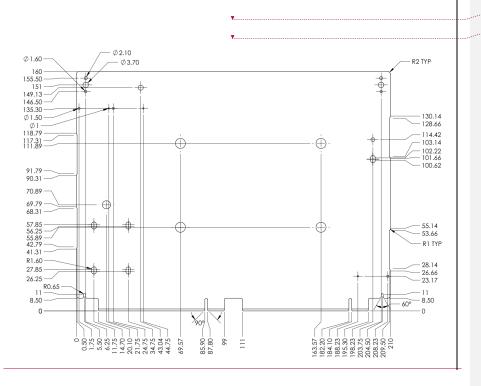

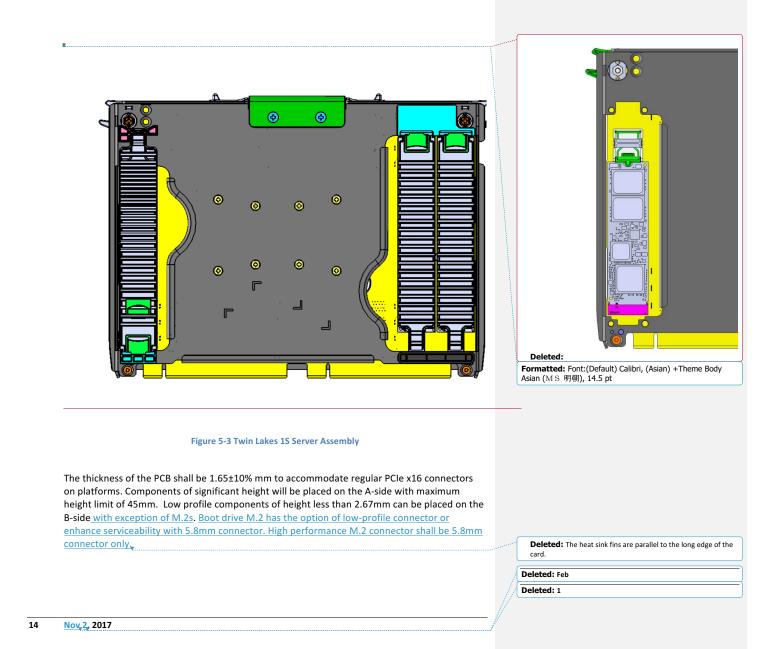

The Twin Lakes 1S Server card uses a primary x16 PCle edge connector and an additional extension x16 PCle edge connector as the interfaces to the platform.

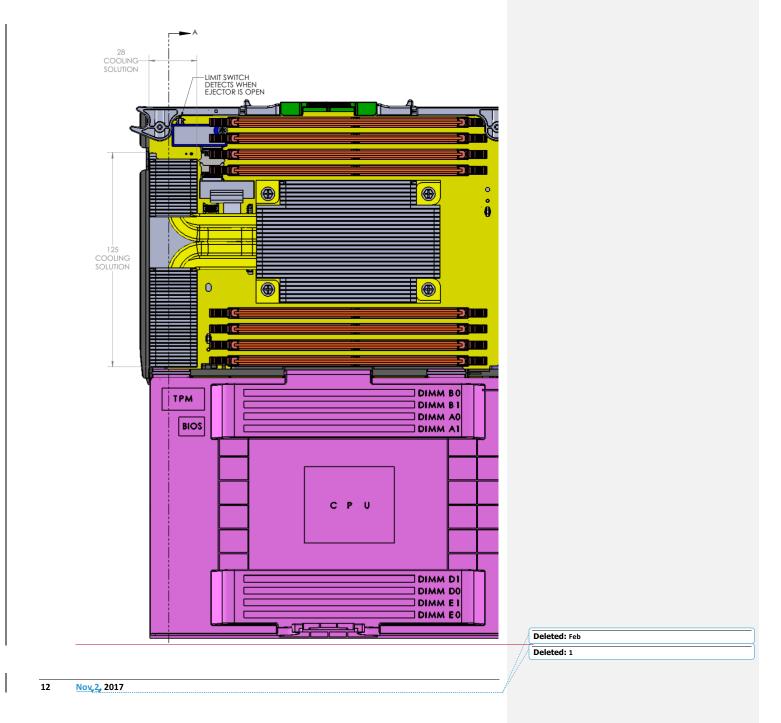

The overall dimentions of the general card is 210mmx160mm. See Figure 5-1 for the specificaiton drawing inlcuding keep-out zones and component restrictions.

The PCB is mounted to a sheet metal carrier which includes flanges on each perpendicular edge that engage the card\_guides in the chassis. There are no card guide keep\_outs on the PCB edge since all available space is needed for traces and components.

The carrier assembly includes 2x ejectors which are used for card injection/ejection into the PCI connectors. These ejectors rotate horizontally before being allowed to swing open, and they

include finger access cutouts. One ejector claw engages a limit switch, which allows the BMC to detect if the ejector has been opened. The air duct rotates about a fixed support wall.

A high performance passive cooling solution chosen to cool the SoC effectively.

Comment [BJ2]: This appears to be an artifact from a previous revision. Cooling solution is now shown in the diagrams.

Comment [DWKC3R2]: Edited. Thanks.

Deleted: The

**Deleted:** space is noted, and may be occupied by either an active (liquid hybrid) or passive solution.

Deleted: The keepout space is the same in either design.

Deleted: Feb

Deleted: 1

10 <u>Nov, 2, 2017</u>

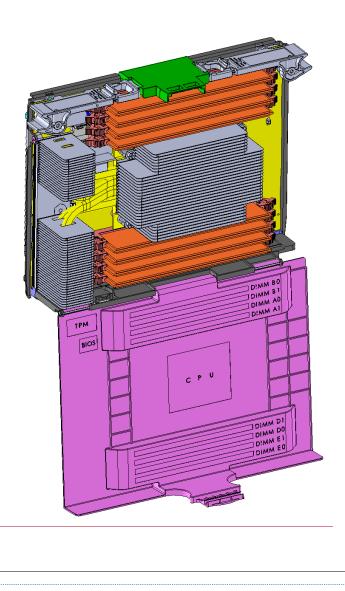

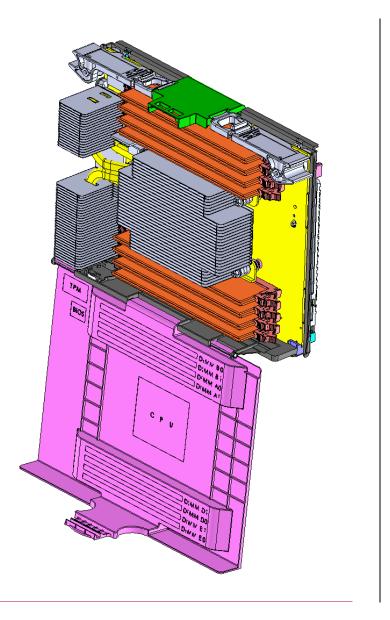

Figure 5-2 Isometric Views of Twin Lakes 1S Server Assembly

#### Open Compute Project • Twin Lakes 1S Server Design Specification

Open Compute Project • Twin Lakes 1S Server Design Specification

# 5.2 PCIe Edge Connector

The key dimensions, edge chamfer, pad layout (including a shorter pad for PRSNT# signal), placement, and dimensions of the card edge connector match the PCI Express Card electromechanical specification.

The GND planes underneath the pads for the card's edge connector must be recessed according to the PCI Express Card electromechanical specification to improve signal integrity.

# 5.3 Platform Design

Platform design details are not discussed in this specification.

#### 6 Thermal

#### 6.1 Data Center Environmental Conditions

This section outlines Facebook data center operational conditions.

#### 6.1.1 Location of Data Center/Altitude

Maximum altitude is 6,000 ft above sea level. Any variation of air properties or environmental difference due to the high altitude needs to be deliberated into the thermal design.

#### 6.1.2 Cold-Aisle Temperature

Data centers generally maintain cold aisle temperatures between 18°C and 30°C (65°F to 85°F). The mean temperature in the cold aisle is usually 25°C with 3°C standard deviation. The cold aisle temperature in a data center may fluctuate minutely depending to the outside air temperature. Every component must be cooled and must maintain a temperature below its maximum specification temperature in the cold aisle.

#### 6.1.3 Cold-Aisle Pressurization

Data centers generally maintain cold aisle pressure between 0 inches  $H_2O$  and 0.005 inches  $H_2O$ . The thermal solution of the system should consider the worst operational pressurization possible, which generally is 0 inches  $H_2O$  and 0.005 inches  $H_2O$  with a single fan (or rotor) failure.

#### 6.1.4 Relative Humidity

Data centers usually maintains a relative humidity between 20% and 90%.

#### 6.2 Server Operational Conditions

#### 6.2.1 System Volumetric Flow

The unit of airflow (or volumetric flow) used for this spec is cubic feet per minute (CFM). The CFM can be used to determine the thermal expenditure or to calculate the approximate Delta T of the system. The thermal expenditure is quantified by the metric CFM/W, which is calculated by the following formula:

The required airflow is 0.115 airflow per watt in the system level at sea level. The desired airflow per watt is 0.1 or lower up to  $45^{\circ}C$  ( $113^{\circ}F$ ) ambient temperature at sea level.

#### 6.2.2 Thermal Margin

The thermal margin is the difference between the maximum theoretical safe temperature and the actual temperature. The board design operates at an inlet temperature of  $45^{\circ}$ C ( $113^{\circ}$ F) outside of the system with a minimum 5% thermal margin for every component on the card.

#### 6.2.3 Upper Critical Threshold

The upper critical threshold (UCT) setting should allow the detection of abnormal thermal behaviors in the system. The UCT values for the sensors that are not used in Fan Speed Control

| Deleted: Feb |  |

|--------------|--|

| Deleted: 1   |  |

(FSC) should use a 15% thermal margin from the worst experiment data. The UCT values for the sensors used in FSC, except for CPU, inlet, and outlet sensors, should use a 20% thermal margin from the worst experiment data.

## 6.2.4 Thermal Testing

Thermal testing must be performed at a low inlet temperature  $15^{\circ}C$  (59°F) and up to 50°C (122°F) inlet temperature to guarantee the design is free of thermal defect and has high temperature reliability.

# 6.3 CPU cooling solution

#### 6.3.1 Orientation

The CPU cooling solution must be designed such that performance is not impacted by server card orientation. All vapor chamber, or heat pipe components must operate in any orientation.

#### 6.3.2 Solution Footprint

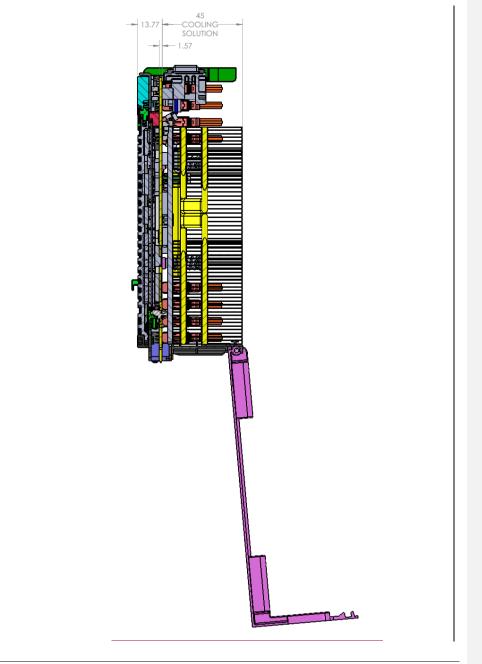

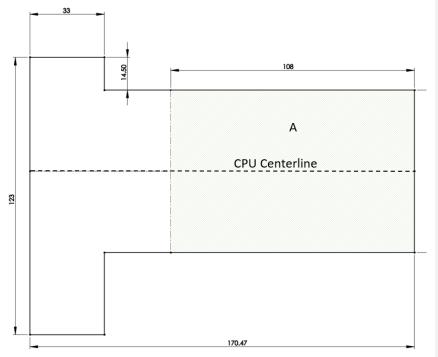

The CPU cooling solution must fit within the available space on the server card. A figure showing the total available footprint can be seen below in Figure 6-1. Section A in Figure 6-1 is centered over the CPU. The total height of the solution and CPU stack up must be less than 45mm. The CPU cooling solution must not interfere with any tall electrical components on the server card.

Deleted: liquid cooling,

Figure 6-1 CPU cooling solution footprint. All dimensions in mm

#### 6.3.3 Passive Cooling Solution

The heat sink must be a thermally optimized design at the lowest cost. Heat sink installation must be uncomplicated. Passive cooling is desired. Heat sinks must not block debug headers or connectors. The heat sink fins should be aligned with the airflow direction, which is shown in Figure 6-2. The heat sink may require cutouts in order to avoid tall electrical components on the server card.

#### 6.3.4 Reliability Requirements

The operating life of the server card is a minimum of 3 years with target life of 5 years. All pertinent reliability data for CPU cooling solution must be provided to meet this MTBF.

# 6.4 M.2 Cooling Solution

Each card must support up to 3 M.2s. Two high power M.2s on the bottom side of the card at the front of the card, and one boot drive M.2 on the bottom side at the rear of the card.

Deleted: Feb Deleted: 1

18 <u>Nov 2, 2017</u>

÷

Deleted: <#>Hybrid Cooling Overall Requirements • .....[1]

#### 6.4.1 Bottom Side M.2 Cooling Requirements

The cooling solution for M.2 cooling must be thermally optimized design at the lowest cost. Passive cooling is required with a gap pad and heat sink solution being desired. The solution must maintain all M.2 component temperatures within their operational limits during all stress conditions. 5.8mm M.2 connectors must be used to allow spacing for gap pads between M.2 and sever card. The total solution stack up must be 12mm or shorter.

#### 6.4.2 Gap Pad Requirements

The gap pads must be soft and elastic as the application will be between two PCBs. The gap pads must not leave any residue when replaced. The Gap pads must have a thermal conductivity of 2 W/m-k or higher. Gap pad thickness is determined by compression vs pressure that gives the lowest loading force while supporting tolerance of components sandwiching the gap pad. Gap pad AVL provided as needed.

#### 6.4.3 Bottom Side boot M.2 Requirements

Bottom side boot M.2 must maintain operation conditions for all components under all stress conditions. The bottom side boot M.2 is downstream from the high speed M.2s in standard orientation and may experience high temperatures due to pre-heating from upstream M.2s. A heat sink with gap pad solution may be required in order to meet bottom side boot M.2 cooling requirements.

#### 6.5 Temperature and Power Sensors

Each card must provide following sensors:

- Temperature sensors for SOC, DIMM, voltage regulators and other critical chips

- Power sensors for the SOC and the whole card

- Voltage sensors for all voltage rails

- One inlet ambient temperature sensor and one outlet ambient temperature sensor

The BMC on the platform must be able to read all these sensors via the Bridge IC. Additionally, over-temperature thresholds must be configurable and an alert mechanism must be provided to enable thermal shutdown and/or an increase in airflow. The sensors are accurate to  $+/-2^{\circ}C$  and desired to be within 2% tolerance across whole operation temperature range. The goal sensor accuracy is  $+/-1^{\circ}C$ .

Two ambient temperature sensors are placed along the edges of the card on the A-side. Figure 6-1 depicts the desired areas for ambient temperature sensor placement.

**Deleted:** Bottom side boot M.2 must maintain operation conditions for all components under all stress conditions. The bottom side boot M.2 is downstream from the CPU in standard orientation and may experience high temperatures due to preheating from CPU. A heat sink solution may be required in order to meet bottom side boot M.2 cooling requirements.

I

# 7 Electrical

# 7.1 Design Guidelines

Refer to Intel® Next Gen Xeon® Processor D SoC documents for design guidelines.

# 7.2 Primary X16 Edge Connector A

The Twin Lakes 1S server uses both primary and extension edge connectors as defined below. There are two changes from 1S server spec 0.5. First, the original KR4 interface on extension edge connector has been reassigned as 7<sup>th</sup> PCIe Gen3 X4 link, which does not have its own PCIe reference clock and PCIe reset signal. Secondly, 4 of the GPIO pins on primary connector have been redefined with specific purpose now. Last but not least, we also converted the SATA pins to PCIe x1 link to make it possible to add a VGA controller on platform side.

|             | Default | Pin-Out | 1                |

|-------------|---------|---------|------------------|

| Pin Name    | B Side  | A Side  | Pin Name         |

| P12V        | 1       | 1       | PRSNT_A#         |

| P12V        | 2       | 2       | P12V             |

| P12V        | 3       | 3       | P12V             |

| GND         | 4       | 4       | GND              |

| I2C_SCL     | 5       | 5       | CARD_TYPE        |

| I2C_DATA    | 6       | 6       | DEV_PWR_EN       |

| GND         | 7       | 7       | COM_TX           |

| PWR_BTN#    | 8       | 8       | COM_RX           |

| USB_P       | 9       | 9       | EJCT_LATCH_DET_N |

| USB_N       | 10      | 10      | RESET_BMC        |

| SYS_RESET#  | 11      | 11      | PCIE0_RESET#     |

|             |         |         |                  |

| I2C_ALERT#  | 12      | 12      | GND              |

| GND         | 13      | 13      | PCIE0_REFCLK_P   |

| GND         | 14      | 14      | PCIE0_REFCLK_N   |

| PCIE0_TX0_P | 15      | 15      | GND              |

| PCIE0_TX0_N | 16      | 16      | GND              |

| GND         | 17      | 17      | PCIE0_RX0_P      |

| GND         | 18      | 18      | PCIE0_RX0_N      |

| PCIE0 TX1 P | 19      | 19      | GND              |

Table 1: Twin Lakes 1S Server Primary X16 OCP Edge Connector A Pin-Out

Deleted: Deleted: a

| PCIE0_TX1_N    | 20 | 20 | GND              |

|----------------|----|----|------------------|

| GND            | 21 | 21 | PCIE0_RX1_P      |

| GND            | 22 | 22 | PCIE0_RX1_N      |

| PCIE0_TX2_P    | 23 | 23 | GND              |

| PCIE0_TX2_N    | 24 | 24 | GND              |

| GND            | 25 | 25 | PCIE0_RX2_P      |

| GND            | 26 | 26 | PCIE0_RX2_N      |

| PCIE0_TX3_P    | 27 | 27 | GND              |

| PCIE0_TX3_N    | 28 | 28 | GND              |

| GND            | 29 | 29 | PCIE0_RX3_P      |

| GND            | 30 | 30 | PCIE0_RX3_N      |

| PCIE7_TX_P     | 31 | 31 | GND              |

| PCIE7_TX_N     | 32 | 32 | GND              |

| GND            | 33 | 33 | PCIE7_RX_P       |

| GND            | 34 | 34 | PCIE7_RX_N       |

| PCIE1_REFCLK_P | 35 | 35 | GND              |

| PCIE1_REFCLK_N | 36 | 36 | GND              |

| GND            | 37 | 37 | PCIE2_REFCLK_P   |

| GND            | 38 | 38 | PCIE2_REFCLK_N   |

| PCIE1_RESET#   | 39 | 39 | GND              |

| PCIE2_RESET#   | 40 | 40 | GND              |

| GND            | 41 | 41 | FAST_THROTTLE_N  |

| GND            | 42 | 42 | NIC_SMBUS_ALERT# |

| NIC_SMBUS_SCL  | 43 | 43 | GND              |

| NIC_SMBUS_SDA  | 44 | 44 | GND              |

| GND            | 45 | 45 | KRØ_RX_P         |

| GND            | 46 | 46 | KR0_RX_N         |

| KRØ_TX_P       | 47 | 47 | GND              |

| KRØ_TX_N       | 48 | 48 | GND              |

| GND            | 49 | 49 | PCIE1_RX0_P      |

| GND            | 50 | 50 | PCIE1_RX0_N      |

| PCIE1_TX0_P    | 51 | 51 | GND              |

| PCIE1_TX0_N    | 52 | 52 | GND              |

|                |    |    |                  |

Deleted: Feb

Deleted: 1

22

Nov, 2, 2017

| GND         | 53 | 53 | PCIE1_RX1_P |

|-------------|----|----|-------------|

| GND         | 54 | 54 | PCIE1_RX1_N |

| PCIE1_TX1_P | 55 | 55 | GND         |

| PCIE1_TX1_N | 56 | 56 | GND         |

| GND         | 57 | 57 | PCIE1_RX2_P |

| GND         | 58 | 58 | PCIE1_RX2_N |

| PCIE1_TX2_P | 59 | 59 | GND         |

| PCIE1_TX2_N | 60 | 60 | GND         |

| GND         | 61 | 61 | PCIE1_RX3_P |

| GND         | 62 | 62 | PCIE1_RX3_N |

| PCIE1_TX3_P | 63 | 63 | GND         |

| PCIE1_TX3_N | 64 | 64 | GND         |

| GND         | 65 | 65 | PCIE2_RX0_P |

| GND         | 66 | 66 | PCIE2_RX0_N |

| PCIE2_TX0_P | 67 | 67 | GND         |

| PCIE2_TX0_N | 68 | 68 | GND         |

| GND         | 69 | 69 | PCIE2_RX1_P |

| GND         | 70 | 70 | PCIE2_RX1_N |

| PCIE2_TX1_P | 71 | 71 | GND         |

| PCIE2_TX1_N | 72 | 72 | GND         |

| GND         | 73 | 73 | PCIE2_RX2_P |

| GND         | 74 | 74 | PCIE2_RX2_N |

| PCIE2_TX2_P | 75 | 75 | GND         |

| PCIE2_TX2_N | 76 | 76 | GND         |

| GND         | 77 | 77 | PCIE2_RX3_P |

| GND         | 78 | 78 | PCIE2_RX3_N |

| PCIE2_TX3_P | 79 | 79 | GND         |

| PCIE2_TX3_N | 80 | 80 | GND         |

| GND         | 81 | 81 | P12V        |

| GND         | 82 | 82 | P12V        |

# 7.3 Extension X16 Edge Connector B

The Twin Lakes 1S server also implements an extension x16 edge connector to bring out additional x16 PCIe lanes and one NC-SI (pin assignments shown in Table 2). This extension X16 Edge connector is referred to as Connector B.

Deleted: 2 Deleted: , one 10GBase-KR,

| ble 2: Twin Lakes 1S | Server Exte | nsion X16 C | OCP Edge Connector B Pir |  |  |  |

|----------------------|-------------|-------------|--------------------------|--|--|--|

| Default Pin-Out      |             |             |                          |  |  |  |

| Pin Name             | B Side      | A Side      | Pin Name                 |  |  |  |

| P12V                 | 1           | 1           | PRSNT_B#                 |  |  |  |

| P12V                 | 2           | 2           | P12V                     |  |  |  |

| P12V                 | 3           | 3           | P12V                     |  |  |  |

| GND                  | 4           | 4           | GND                      |  |  |  |

| NCSI_TXEN            | 5           | 5           | NCSI_RCLK                |  |  |  |

| NCSI_TXD0            | 6           | 6           | NCSI_RXD0                |  |  |  |

| NCSI_TXD1            | 7           | 7           | NCSI_RXD1                |  |  |  |

| NCSI_CRSDV           | 8           | 8           | GND                      |  |  |  |

| NCSI_RXER            | 9           | 9           | PCIE4_REFCLK_P           |  |  |  |

| GND                  | 10          | 10          | PCIE4_REFCLK_N           |  |  |  |

| PCIE3_RESET#         | 11          | 11          | GND                      |  |  |  |

|                      |             |             |                          |  |  |  |

| PCIE4_RESET#         | 12          | 12          | GND                      |  |  |  |

| PCIE5_RESET#         | 13          | 13          | PCIE5_REFCLK_P           |  |  |  |

| GND                  | 14          | 14          | PCIE5_REFCLK_N           |  |  |  |

| PCIE6_TX0_P          | 15          | 15          | GND                      |  |  |  |

| PCIE6_TX0_N          | 16          | 16          | GND                      |  |  |  |

| GND                  | 17          | 17          | PCIE6_RX0_P              |  |  |  |

| GND                  | 18          | 18          | PCIE6_RX0_N              |  |  |  |

| PCIE6_TX1_P          | 19          | 19          | GND                      |  |  |  |

| PCIE6_TX1_N          | 20          | 20          | GND                      |  |  |  |

| GND                  | 21          | 21          | PCIE6_RX1_P              |  |  |  |

| GND                  | 22          | 22          | PCIE6_RX1_N              |  |  |  |

| PCIE6_TX2_P          | 23          | 23          | GND                      |  |  |  |

| PCIE6_TX2_N          | 24          | 24          | GND                      |  |  |  |

| GND                  | 25          | 25          | PCIE6_RX2_P              |  |  |  |

24 <u>Nov.2, 2017</u>

Deleted: Feb

Deleted: 1

| 26 | 26                                                                                                                                                                                                                                           | PCIE6_RX2_N                                                                                                          |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 27 | 27                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 28 | 28                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 29 | 29                                                                                                                                                                                                                                           | PCIE6_RX3_P                                                                                                          |

| 30 | 30                                                                                                                                                                                                                                           | PCIE6_RX3_N                                                                                                          |

| 31 | 31                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 32 | 32                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 33 | 33                                                                                                                                                                                                                                           | PCIE3_RX0_P                                                                                                          |

| 34 | 34                                                                                                                                                                                                                                           | PCIE3_RX0_N                                                                                                          |

| 35 | 35                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 36 | 36                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 37 | 37                                                                                                                                                                                                                                           | PCIE3_RX1_P                                                                                                          |

| 38 | 38                                                                                                                                                                                                                                           | PCIE3_RX1_N                                                                                                          |

| 39 | 39                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 40 | 40                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 41 | 41                                                                                                                                                                                                                                           | PCIE3_RX2_P                                                                                                          |

| 42 | 42                                                                                                                                                                                                                                           | PCIE3_RX2_N                                                                                                          |

| 43 | 43                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 44 | 44                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 45 | 45                                                                                                                                                                                                                                           | PCIE3_RX3_P                                                                                                          |

| 46 | 46                                                                                                                                                                                                                                           | PCIE3_RX3_N                                                                                                          |

| 47 | 47                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 48 | 48                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 49 | 49                                                                                                                                                                                                                                           | PCIE4_RX0_P                                                                                                          |

| 50 | 50                                                                                                                                                                                                                                           | PCIE4_RX0_N                                                                                                          |

| 51 | 51                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 52 | 52                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 53 | 53                                                                                                                                                                                                                                           | PCIE4_RX1_P                                                                                                          |

| 54 | 54                                                                                                                                                                                                                                           | PCIE4_RX1_N                                                                                                          |

| 55 | 55                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 56 | 56                                                                                                                                                                                                                                           | GND                                                                                                                  |

| 57 | 57                                                                                                                                                                                                                                           | PCIE4_RX2_P                                                                                                          |

| 58 | 58                                                                                                                                                                                                                                           | PCIE4_RX2_N                                                                                                          |

|    | 27<br>28<br>29<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>40<br>41<br>42<br>43<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50<br>51<br>48<br>49<br>50<br>51<br>52<br>53<br>54<br>55<br>56<br>56 | 27272828292930303131323233333434353536363737383839394040414142424343444445454646474748484950515152525353545556565757 |

| PCIE4_TX2_P  | 59 | 59 | GND         |

|--------------|----|----|-------------|

| PCIE4_TX2_N  | 60 | 60 | GND         |

| GND          | 61 | 61 | PCIE4_RX3_P |

| GND          | 62 | 62 | PCIE4_RX3_N |

| PCIE4_TX3_P  | 63 | 63 | GND         |

| PCIE4_TX3_N  | 64 | 64 | GND         |

| GND          | 65 | 65 | PCIE5_RX0_P |

| GND          | 66 | 66 | PCIE5_RX0_N |

| PCIE5_TX0_P  | 67 | 67 | GND         |

| PCIE5_TX0_N  | 68 | 68 | GND         |

| GND          | 69 | 69 | PCIE5_RX1_P |

| GND          | 70 | 70 | PCIE5_RX1_N |

| PCIE5_TX1_P  | 71 | 71 | GND         |

| PCIE5_TX1_N  | 72 | 72 | GND         |

| GND          | 73 | 73 | PCIE5_RX2_P |

| GND          | 74 | 74 | PCIE5_RX2_N |

| PCIE5_TX2_P  | 75 | 75 | GND         |

| PCIE5_TX2_N  | 76 | 76 | GND         |

| GND          | 77 | 77 | PCIE5_RX3_P |

| GND          | 78 | 78 | PCIE5_RX3_N |

| PCIE5_TX3_P  | 79 | 79 | GND         |

| PCIE5_TX3_N  | 80 | 80 | GND         |

| GND          | 81 | 81 | P12V        |

| POWER_FAIL_N | 82 | 82 | P12V        |

Deleted: Feb Deleted: 1

Nov, 2, 2017

26

# 7.4 Pin Definitions

Table 3 provides a detailed explanation of the pins. The direction of the signals is always defined from the perspective of the Twin Lakes 1S Server module.

| Pin              | Direction    | ailed Pin Definition<br>Required/ | Pin Definition                                                                                                                                                                          |

|------------------|--------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin              | Direction    | Configurable                      | Pin Definition                                                                                                                                                                          |

| P12V             | Input        | Required                          | 12VAUX power from platform                                                                                                                                                              |

| I2C_SCL          | Input/Output | Required                          | I <sup>2</sup> C clock signal. I <sup>2</sup> C is the primary<br>sideband interface for server<br>management functionality. 3.3VAUX<br>signal. Pull-up is provided on the<br>platform. |

| I2C_SDA          | Input/Output | Required                          | I <sup>2</sup> C data signal. I <sup>2</sup> C is the primary<br>sideband interface for server<br>management functionality. 3.3VAUX<br>signal. Pull-up is provided on the<br>platform.  |

| I2C_ALERT#       | Output       | Required                          | I <sup>2</sup> C alert signal. Alerts the BMC that<br>an event has occurred that needs to<br>be processed. 3.3VAUX signal. Pull-<br>up is provided on the platform.                     |

| NIC_SMBUS_SCL    | Input/Output | Required                          | Dedicated SMBus clock signal for<br>network sideband traffic between<br>the BMC and the NIC. 3.3VAUX<br>signal. Pull-up is provided on the<br>platform.                                 |

| NIC_SMBUS_SDA    | Input/Output | Required                          | Dedicated SMBus data signal for<br>network sideband traffic between<br>the BMC and the NIC. 3.3VAUX<br>signal. Pull-up is provided on the<br>platform.                                  |

| NIC_SMBUS_ALERT# | Output       | Required                          | Dedicated SMBus alert signal for<br>network sideband traffic between<br>the BMC and the NIC. 3.3VAUX<br>signal. Pull-up is provided on the<br>platform.                                 |

| NCSI_RCLK        | Input        | Required                          | NC-SI reference clock for NIC                                                                                                                                                           |

| NCSI_CRSDV       | Output       | Required                          | Carrier Sense/Receive Data Valid<br>from NIC to BMC.                                                                                                                                    |

| NCSI_RXER        | Output       | Required                          | Receive error from NIC to BMC                                                                                                                                                           |

| NCSI_TXEN        | Input        | Required                          | Transmit enable from BMC to NIC                                                                                                                                                         |

| NCSI_RXD[0:1]    | Output       | Required                          | Receive data from NIC to BMC                                                                                                                                                            |

Table 3:Detailed Pin Definitions

| NCSI_TXD[0:1]         | Input  | Required | Transmit data from BMC to NIC                                                                                                                                                                                                                                                                                            |

|-----------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR_BTN#              | Input  | Required | Power on signal. When driven low, it<br>indicates that the server will begin its<br>power-on sequence. 3.3VAUX signal.<br>Pull-up is provided on the platform. If<br>PWR_BTN# is held low for greater<br>than 4 seconds, then this indicates a<br>soft (graceful) power off. Otherwise,<br>a hard shutdown is initiated. |

| SYS_RESET#            | Input  | Required | System reset signal. When driven<br>low, it indicates that the server will<br>begin its warm reboot process.<br>3.3VAUX signal. Pull-up is provided<br>on the platform.                                                                                                                                                  |

| PRSNT_A#              | Output | Required | Present signal. This is pulled low on<br>the card to indicate that a card is<br>installed. 3.3VAUX signal.<br>Pull-up is provided on the platform.                                                                                                                                                                       |

| PRSNT_B#              | Output | Required | Extension edge connector Present<br>signal. This is pulled low on the card<br>to indicate that a card is installed.<br>3.3VAUX signal. Pull-up is provided<br>on the platform.                                                                                                                                           |

| сом_тх                | Output | Required | Serial transmit signal. Data is sent<br>from the 1S Server module to the<br>BMC. 3.3VAUX signal.                                                                                                                                                                                                                         |

| COM_RX                | Input  | Required | Serial receive signal. Data is sent<br>from the BMC to the 1S Server<br>module. 3.3VAUX signal.                                                                                                                                                                                                                          |

| CARD_TYPE<br>(GPIO0)  | Output | Required | CARD_TYPE is an output signal to<br>inform platform that if this card is a<br>server or a device. For a server, this<br>pin should be tied to GND through a<br>10K resistor on the 1S server card.                                                                                                                       |

| DEV_PWR_EN<br>(GPIO1) | Output | Required | CARD_TYPE is an output signal from<br>a 1S server to enable active power<br>on device side. It is useful when 1S<br>server is going through DC cycling or<br>AC cycling but the server and devices<br>are not in the same power domain.<br>Active high, 3.3VAUX signal.                                                  |

Deleted: Feb

Deleted: than 4

Deleted: 1

28 Nov 2, 2017

I

| EJCT_LATCH_DET_N<br>(GPIO2) | Output | Required | EJCT_LATCH_DET_N is an output<br>signal to indicate if the 1S server is<br>fully seated with ejector latch closed<br>and ready for power on. Platform<br>designer can use this signal to<br>control the power to the 1S server<br>and avoid surprise 1S server<br>insertion/removal to/from a hot slot.<br>Active low, 3.3VAUX signal, pull-up<br>should be provided on the platform. |

|-----------------------------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_BMC<br>(GPIO3)        | Output | Required | RESET_BMC is an output signal to<br>reset BMC on the platform. Active<br>high, 3.3VAUX signal, pull-down on<br>the platform.                                                                                                                                                                                                                                                          |

| KRO_TX_P/N                  | Output | Required | Primary 10GBase-KR Ethernet<br>transmit signal. Data is sent from the<br>1S Server module to the platform.                                                                                                                                                                                                                                                                            |

| KR0_RX_P/N                  | Input  | Required | Primary 10GBase-KR Ethernet<br>receive signal. Data is sent from the<br>platform to the 1S Server module.                                                                                                                                                                                                                                                                             |

| PCIE0_RESET#                | Output | Required | PCIe reset signal. If a PCIe bus is<br>connected, this signal provides the<br>reset signal indicating the card VRs<br>and clocks are stable when driven<br>high to 3.3V.                                                                                                                                                                                                              |

| PCIE0_TX0/1/2/3_P/N         | Output | Required | PCIe x4 bus transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.                                                                                                                                                                                                                          |

| PCIE0_RX0/1/2/3_P/N         | Input  | Required | PCle x4 bus receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.                                                                                                                                                                                                                           |

| PCIE0_REFCLK_P/_N           | Output | Required | PCle reference clock. This signal may<br>or may not be connected on the<br>platform.                                                                                                                                                                                                                                                                                                  |

| PCIE1/2_RESET#              | Output | Required | PCle reset signals. If a PCle bus is<br>connected, this signal provides the<br>reset signal indicating the card VRs<br>and clocks are stable when driven<br>high to 3.3V.                                                                                                                                                                                                             |

| PCIE1_TX0/1/2/3_P/N         | Output | Required | PCIe x4 bus transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.                                                                                                                                                                                                                          |

| PCIE1_RX0/1/2/3_P/N | Input  | Required | PCle x4 bus receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.               |

|---------------------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIE1_REFCLK_P/_N   | Output | Required | PCIe reference clock. These signals<br>may or may not be connected on the<br>platform.                                                                                    |

| PCIE8_TX_P/N        | Output | Required | PCle Gen2 transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.                |

| PCIE2_RESET#        | Output | Required | PCle reset signals. If a PCle bus is<br>connected, this signal provides the<br>reset signal indicating the card VRs<br>and clocks are stable when driven<br>high to 3.3V. |

| PCIE2_TX0/1/2/3_P/N | Output | Required | PCIe x4 bus transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.              |

| PCIE2_RX0/1/2/3_P/N | Input  | Required | PCIe x4 bus receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.               |

| PCIE2_REFCLK_P/_N   | Output | Required | PCle reference clocks. These signals<br>may or may not be connected on the<br>platform.                                                                                   |

| PCIE3_RESET#        | Output | Required | PCIe reset signal. If a PCIe bus is<br>connected, this signal provides the<br>reset signal indicating the card VRs<br>and clocks are stable when driven<br>high to 3.3V.  |

| PCIE3_TX0/1/2/3_P/N | Output | Required | PCIe x4 bus transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.              |

| PCIE3_RX0/1/2/3_P/N | Input  | Required | PCle x4 bus receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.               |

| PCIE3_REFCLK_P/_N   | Output | Required | PCIe reference clocks. These signals<br>may or may not be connected on the<br>platform.                                                                                   |

Deleted: Feb

Deleted: 1

30

Nov, 2, 2017

| PCIE4_RESET#        | Output | Required | PCIe reset signal. If a PCIe bus is<br>connected, this signal provides the<br>reset signal indicating the card VRs<br>and clocks are stable when driven<br>high to 3.3V. |

|---------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIE4_TX0/1/2/3_P/N | Output | Required | PCIe x4 bus transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.             |

| PCIE4_RX0/1/2/3_P/N | Input  | Required | PCIe x4 bus receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.              |

| PCIE4_REFCLK_P/_N   | Output | Required | PCIe reference clock. These signals<br>may or may not be connected on the<br>platform.                                                                                   |

| PCIE5_RESET#        | Output | Required | PCIe reset signal. If a PCIe bus is<br>connected, this signal provides the<br>reset signal indicating the card VRs<br>and clocks are stable when driven<br>high to 3.3V. |

| PCIE5_TX0/1/2/3_P/N | Output | Required | PCIe x4 bus transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.             |

| PCIE5_RX0/1/2/3_P/N | Input  | Required | PCle x4 bus receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.              |

| PCIE5_REFCLK_P/_N   | Output | Required | PCIe reference clock. These signals<br>may or may not be connected on the<br>platform.                                                                                   |

| PCIE6_TX0/1/2/3_P/N | Output | Required | PCIe x4 bus transmit signals. Data is<br>sent from the 1S Server module to<br>the platform. These signals may or<br>may not be connected on the<br>platform.             |

| PCIE6_RX0/1/2/3_P/N | Input  | Required | PCIe x4 bus receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.              |

| PCIE8_RX_P/N    | Input        | Required | PCle Gen2 receive signals. Data is<br>sent from the platform to the 1S<br>Server module. These signals may or<br>may not be connected on the<br>platform.                                                                                                                                                                                                 |  |  |

|-----------------|--------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| USB_P/N         | Input/Output | Required | USB 2.0 differential pair.                                                                                                                                                                                                                                                                                                                                |  |  |

| FAST_THROTTLE_N | Input        | Required | Active low open drain signal with<br>pull-up on 1S server. Platform<br>generates this signal and uses it as a<br>big hammer to throttle 1S server<br>down to lowest possible power state<br>as fast as possible.                                                                                                                                          |  |  |

| POWER_FAIL_N    | Input        | Required | Active low open drain signal with<br>pull-up on 1S server. When this<br>signal is asserted by platform, it<br>informs 1S server that base system is<br>going to cut 12V power to 1S server<br>in certain amount of time, which is<br>pre-defined by base system. It is<br>possible for 1S server to perform<br>graceful shutdown based on this<br>signal. |  |  |

# 7.5 Ethernet

The Twin Lakes 1S server uses the 10GBase-KR as its optional Ethernet connection. Auto-negotiation and link training are required to work with either the re-timer or the physical layer (PHY) on the platform.

#### 7.5.1 Routing guidelines

To support 10Gb speeds, it is critical that the differential pairs for transmit and receive adhere to the following Intel's strict route guideline.

It is strongly recommended to perform comprehensive signal integrity simulation, analysis and validation for 10GBase-KR on a platform, including the 1S server, platform, connectors and vias, to determine if all the signal integrity related parameters are within the limit defined by the standards.

As a general guideline, 5dB or less channel loss budget is reserved for 10GBase-KR differential signals on the 1S server card.

|   | 7.6 USB                        |      | Deleted: SATA . | [2] |

|---|--------------------------------|------|-----------------|-----|

|   | The USB connection is USB 2.0. |      |                 |     |

|   |                                | Å    | Deleted: Feb    | ]   |

|   |                                | - /) | Deleted: 1      |     |

|   |                                |      |                 |     |

| 2 | Nov,2, 2017                    | /    |                 |     |

#### 7.7 Serial port

The serial port shall be routed to the BMC on the platform. Thus, the user can access the SoC's serial console through the BMC locally or remotely via Serial Over Lan (SOL).

# 7.8 I<sup>2</sup>C

A single I<sup>2</sup>C connection is used to connect the BMC on the platform to the Bridge IC on the 1S server as the primary server management interface. It shall support a minimum speed of 400kHz. However, 1MHz or higher is strongly recommended. The I<sup>2</sup>C alert signal is required and is used as an interrupt for both the Bridge IC and the BMC.

Both the BMC and the Bridge IC are  $I^2C$  master devices on the bus and they communicate with each other via the Intelligent Platform Management Bus (IPMB) protocol. To achieve maximum bandwidth and avoid conflicts, no other devices should use this bus except for the BMC and the Bridge IC.

# 7.9 NIC Sideband

## 7.9.1 SMBus

When the SoC's integrated network controller is used as a shared NIC, its SMBus is routed to Connector A as the sideband interface. The BMC on the platform can leverage this SMBus as its out-of-band access path.

## 7.9.2 NC-SI

When the SoC's integrated network controller is used as a shared NIC, its NC-SI is an alternative sideband interface to the SMBus. It can run at a significantly higher speed compared to the SMBus, but it requires more signals and a more complicated protocol. The BMC could use NC-SI as an alternative high-speed sideband if both the SoC and the BMC support this feature.

#### 7.10 Slot ID and GPIO

Due to the nature of the 1S server architecture, a BMC is always preferred on the platform side to work with the 1S server. When a BMC is present in the system, the Bridge IC shall always request its slot ID from the BMC but not probe the slot ID by itself.

There are four slot ID bits defined in 1S server spec. These pins can be used as GPIO pins if they are not used as slot IDs.

Twin Lakes 1S server redefined all 4 GPIO pins with specific functions. Please refer to pin definition table above for details.

33 http://opencompute.org

Deleted:

[... [3]

#### 8 Power

#### 8.1 Input

Power for the card is provided via seven 12V pins on the primary connector and seven more 12V pins on the extension connector. Each pin supports a maximum 1.1A of current.

The nominal 12V input voltage is defined as 12.5V, +/-7%.

#### 8.1.1 Twin Lakes 1S server power capacity

The Twin Lakes 1S server's maximum power is <u>180W</u> with full configuration. It is critical to develop a sophisticated thermal solution for the platform to keep the Twin Lakes 1S server operating at a safe condition when it runs with a maximum power load.

#### 8.1.2 Power sequence and standby power

Because there is only one 12V power input to the 1S server, there is not a power sequence requirement to power on the Twin Lakes 1S server card from the platform perspective. However, a standby 3.3V\_AUX power rail on the card is required to power the Bridge IC at all power states. The SoC also requires some stand-by power rails. For example, the SoC's integrated network controller requires stand-by power rails to keep the out-of-band function alive when the SoC is in standby mode. A power CPLD that controls the power sequencing of the entire server is also powered by the 3.3V\_AUX standby power rail.

It is the designer's responsibility to provide proper standby power rails from the main 12V\_AUX input with possible specific power sequencing. Care must be taken to avoid any leakage path among the power domains including 1S server stand-by, 1S server <u>core</u>, and <u>baseboard</u> platform power.

#### 8.1.3 Standby power budget

The Twin Lakes 1S server consumes minimal power when it operates in standby mode.

Nov, 2, 2017

34

Deleted: Feb

#### 8.2 VR Efficiency

All Voltage Regulators (VRs) providing over 15W on the card are at least 91% efficient when loaded between 30% and 90% of the full load.

#### 8.3 Input Capacitance

The capacitance on the input 12V rail of the Twin Lakes 1S server shall be optimized. Platform designers must ensure overall capacitance on the 12.5V rail of the entire platform meets the system's power supply requirement and does not cause instability.

#### 8.4 Power reading and power capping

The Twin Lakes 1S server implements sophisticated power management features.

The Twin Lakes 1S server shall have the power monitoring capability to read power consumption reliably and accurately and can report a one-second average power reading with 3% accuracy. As shown in figure 3-1, a power sensor with  $1^{2}$ C interface is used at the 12.5V power input to the card and is readable by the Bridge IC. Both the BMC and SoC can obtain the whole-card power consumption information from the Bridge IC.

The Twin Lakes 1S server can throttle itself down to lowest possible power state as quickly as possible when the platform asserts the FAST\_THROTTLE\_N signal or it receives request from BMC, or over power event reported by on-card power monitor.

A preferred power-capping implementation is to reduce the 1S server's power consumption gradually with fine-grained power control by steps as small as 5 watts and to reach the control target power limit within 3 seconds. This process shall be smooth but fast, and the settled power value shall be within -3% of the target power limit set by the platform.

The platform can generate a POWER\_FAIL\_N signal to inform the 1S server that the 12V input power to the server is going to be cut off in certain amount of time (which is pre-defined by the platform). The 1S server can leverage this signal to develop mechanisms to protect critical data prior to a power outage.

# 9 Functional

#### 9.1 System on a Chip

The Twin Lakes 1S server uses an Intel® Next Gen Xeon® Processor D SoC that incorporates a multi-core CPU, memory controller, and other IO devices.

#### 9.2 Memory

The Twin Lakes 1S server uses DDR4 memory bus.

#### 9.3 Debug headers

The Twin Lakes 1S server shall support traditional ITP/XDP debug headers.

#### 9.4 Storage

The Twin Lakes 1S server supports three M.2 solid-state drives in 2280 or 22110 form <u>factors</u>. Boot M.2 slot is only available in 2280 form factor and it can be configured as either SATA or PCIe interface through BOM options, but not both. A minimum 256GB M.2 SATA or NVMe SSD is required as a boot device and for logging purpose. Two additional SSD drives are designed in to support applications that require high disk performance. These two M.2 slots only support PCIe X4 links but both support SSD drives in 2280 or 22110 form <u>factors</u>.

#### 9.5 EEPROM

The Twin Lakes 1S server includes a 128Kbits I<sup>2</sup>C-accessible Electrically Erasable Programmable Read-Only Memory (EEPROM). The EEPROM is accessible from the platform via the Bridge IC. The EEPROM contains the Field Replaceable Unit Identification (FRU ID) information and any additional configuration information that may be required. The FRU ID is formatted in accordance with the IPMI Platform Management FRU Information Storage Definition document.

The EEPROM must contain the following entries:

- Board Manufacturer

- Board Name

- Board Serial Number

- Board Part Number

- Product Manufacturer

- Product Name

- Product Part Number

- Product Serial Number

- Product Asset Tag

- Product Build: e.g. EVT, DVT, PVT, MP

- Product Version: e.g. C1

- Manufacturing Date and Time

- Manufacturing Lot Code: (preferred, but optional)

- Manufacturing Work Order: (preferred, but optional)

- PCB Revision

- SoC Model Name/Number

- SoC Revision

Nov, 2, 2017

36

Deleted: factor

Deleted: factor

Deleted: Feb

• SoC Tj<sub>MAX</sub> (Maximum Junction Temperature)

### 9.6 **BIOS**

The card supplier is responsible for supplying and customizing the BIOS for the SoC. The requirements are outlined in this section.

### 9.6.1 UEFI

The BIOS shall be a UEFI compatible BIOS.

### 9.6.2 Configuration and Features

The BIOS is tuned to minimize card power consumption. It has the following features:

- Disables unused devices, including PCIe lanes, USB ports, SATA/SAS ports, etc.

- A BIOS setup menu

- The SoC settings can be tuned to achieve the optimal combination of performance and power consumption.

### 9.6.3 BIOS Settings Tools

The card supplier shall provide a tool to make BIOS setting changes without requiring a BIOS re-flash. The BIOS settings update tool must also support success and failure codes so that updates can be easily scripted.

# 9.6.4 PXE Boot

The BIOS supports PXE boot and provides the ability to modify the boot sequence. When PXE booting, the card first attempts to boot from the first available Ethernet device.

The default boot device priority is:

- 1. Network (search all configured network interfaces)

- 2. HDD, SSD, or flash device (local or remote)

- 3. CD-ROM

- 4. Removable Device

This process loops indefinitely and requires no user intervention.

# 9.6.5 iSCSI Boot

The BIOS shall be capable of iSCSI network boot.

#### 9.6.6 Other Boot Options

The BIOS also supports booting from SATA/SAS and USB interfaces. The BIOS provides the capability to select different boot options.

## 9.6.7 BIOS Update

The BIOS can be updated from the OS under these scenarios:

- Scenario 1: Sample/Audit BIOS settings

- Return current BIOS settings, or

- Save/export BIOS settings in a human-readable form that can be restored/imported (as in Scenario 2)

- Scenario 2: Update BIOS with pre-configured set of BIOS settings

- Update/change multiple BIOS settings

- Reboot

- Scenario 3: BIOS/firmware update with a new revision

- $\circ$   $\;$  Load new BIOS/firmware on machine and update, retain the current BIOS

- settings

- o Reboot

Additionally, the update tools have the following capabilities:

- Update from the operating system.

- Can complete BIOS update or setup change with a single reboot (no PXE boot, no multiple reboots)

- No user interaction (such as prompts)

- BIOS updates and option changes do not take longer than five minutes to complete

# 9.6.8 Remote BIOS Update

The BIOS can be updated remotely under these scenarios:

- Scenario 1: Sample/Audit BIOS settings

- Return current BIOS settings, or

- Save/export BIOS settings in a human-readable form that can be restored/imported (as in Scenario 2)

- Scenario 2: Update BIOS with a pre-configured set of BIOS settings

- o Update/change multiple BIOS settings

- Reboot

- Scenario 3: BIOS/firmware update with a new revision

- Load new BIOS/firmware on machine and update, retain the current BIOS settings

- Reboot

Additionally, the update tools have the following capabilities:

- Update from the remote host over the LAN connection to BMC

- Can complete BIOS update or setup change with a single reboot (no PXE boot, no multiple reboots)

- No user interaction (like prompts)

- BIOS updates and option changes do not take longer than 20 minutes to complete

- Can be scripted and propagated to multiple machines

# 9.6.9 SMBIOS Event Log

Per the SMBIOS specification Version 2.6, the BIOS implements SMBIOS Type 15 for an event log and the assigned area is large enough to hold more than 500 event records (assuming the

Deleted: Feb

38 <u>Nov, 2,</u> 2017

maximum event record length is 24 bytes, then the size will be larger than 12KB) and follows the SMBIOS event log organization format for the event log.

A system access interface and application software must be provided to retrieve and clear the event log from the BIOS, including, at minimum, a Linux application for the CentOS operating system and driver as needed. The event log must be retrieved and stored as a readable text file that is easy to handle by a scripting language under Linux. Each event record includes enhanced information identifying the error source device's vendor ID, card slot ID, and device ID.

### 9.6.10 Logged Errors

The following list of errors is logged by the BIOS or Bridge IC. These errors must include the date, time, and location information so that failing components can be easily identified.

- CPU/Memory errors: Both correctable ECC and uncorrectable ECC errors are logged into the event log. Error categories include DRAM, Link, and others.

- PCle\* errors: Any errors that have a status register are logged into the event log, including root complex, endpoint device, and any switch upstream/downstream ports if available. Link disable on errors are also be logged. Fatal, non-fatal, or correctable error classification follows the chipset vendor's recommendation.

- POST errors: All POST errors detected by the BIOS during POST are logged into the event log.

- SATA or SAS errors: All correctable and uncorrectable errors are logged.

- System reboot events

- Sensor values exceeding warning or critical thresholds

### 9.6.11 Error Thresholds

An error threshold setting must be enabled for both correctable and uncorrectable errors. Once the programmed threshold is reached, an event is triggered and logged.