# Barreleye G1 Specification Chassis, Motherboard, IO Board, Lunchbox Power Supply Revision 1.0.1

### **Authors:**

Aaron Sullivan, Distinguished Engineer, Rackspace Hosting Inc.

Norman James, Distinguished Engineer, IBM

Poly Yeh, Hardware Engineer, Ingrasys

# 1 License and Notices

# 1.1 Open Compute License Notice

This content contained herein, excluding items listed explicitly otherwise, is licensed under an Open Compute Project Hardware License-Permissive (OCPHL-P) license, version 1.0. A copy of that license is available here:

http://files.opencompute.org/oc/public.php?service=files&t=4ff92fa7622a58051e1e1bd12db5 3267&download

This content is distributed in the hope that it will be useful, but WITHOUT ANY WARRANTY; without even the implied warranty of MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

All copyrights and trademarks listed herein are property of their respective organization.

# 1.2 IBM and OpenPOWER Notice Page

© Copyright International Business Machines Corporation 2015

IBM, the IBM logo, and ibm.com are trademarks or registered trademarks of International Business Machines Corp., registered in many jurisdictions worldwide. Other product and service names might be trademarks of IBM or other companies. A current list of IBM trademarks is available on the Web at "Copyright and trademark information" at <a href="https://www.ibm.com/legal/copytrade.shtml">www.ibm.com/legal/copytrade.shtml</a>.

The OpenPOWER word mark and the OpenPOWER Logo mark, and related marks, are trademarks and service marks licensed by OpenPOWER.

Other company, product, and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

Note: This document contains information on products in the design, sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

This document and the files listed in this document as components, if any, are intended for development of technology products compatible with Power Architecture®. You may use this document and any files listed in this document as components, for any purpose (commercial or personal) and make modifications and distribute; however, modifications to this document or any files listed in this document as components may violate Power Architecture and should be carefully considered. Any distribution of this document or

the files listed in this document as components, if any, or their derivative works shall include this Notice page including but not limited to the IBM warranty disclaimer and IBM liability limitation, and all copyright notices, intellectual property notices, acknowledgments of contributions, and confidentiality notices of any party. No other licenses, expressed or implied, by estoppel or otherwise, to any intellectual property rights are granted by this document.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. IBM makes no representations or warranties, either express or implied, including but not limited to, warranties of merchantability, fitness for a particular purpose, or non-infringement, or that any practice or implementation of the IBM documentation will not infringe any third party patents, copyrights, trade secrets, or other rights. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems 294 Route 100, Building SOM4 Somers, NY 10589-3216

The IBM home page can be found at ibm.com®.

# 2 Recognition & Logos

This specification and its associated first implementations in hardware were developed and tested by engineers and software developers at Ingrasys (a Foxconn / Hon Hai Industries subsidiary), Rackspace, and IBM, based in part upon material made available through the OpenPOWER Foundation and community members.

# 3 Revision History

| Revision | Date       | Name | Description                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0.1      | 04/28/2015 |      | Preliminary Release                                                                                                                                                                                                                                                                                                                            |  |  |

| 0.2      | 05/12/2015 |      | Update POWER8 DIMM Support                                                                                                                                                                                                                                                                                                                     |  |  |

| 0.3      | 07/18/2015 |      | Update Sled Block Diagram     Update PCB information                                                                                                                                                                                                                                                                                           |  |  |

| 0.4      | 08/20/2015 |      | Add PEB and BP placement     Update Chapter 9 Mechanical                                                                                                                                                                                                                                                                                       |  |  |

| 0.5      | 08/25/2015 |      | Add 9.9 Rack and 9.10 Rack Knife section                                                                                                                                                                                                                                                                                                       |  |  |

| 0.6      | 08/25/2015 |      | Edits for grammar and flow                                                                                                                                                                                                                                                                                                                     |  |  |

| 0.7      | 08/28/2015 |      | <ol> <li>Add MB and IO stack-up</li> <li>Add board to board connector section</li> <li>Add Lunch Box Chapter</li> </ol>                                                                                                                                                                                                                        |  |  |

| 0.7.1    | 09/08/2015 |      | Additional edits for grammar and flow                                                                                                                                                                                                                                                                                                          |  |  |

| 0.7.2    | 09/18/2015 |      | Additional edits for grammar and flow                                                                                                                                                                                                                                                                                                          |  |  |

| 0.8      | 11/23/2015 |      | <ol> <li>Add 9.9 HDD tray dimension</li> <li>Correct the number of CPU pin to 2296 pins</li> <li>Update mSATA to M.2 SATA due to design change</li> <li>Update APSS function description</li> <li>Correct the location of fan connectors which are all on MB</li> <li>BMC firmware update methoed</li> <li>Add connector pin define</li> </ol> |  |  |

# Open Compute Project • Barreleye G1 Specification, Chassis, Motherboard, IO Board

|       |            | 8. Update Lunch Box picture                        |                                              |  |  |

|-------|------------|----------------------------------------------------|----------------------------------------------|--|--|

|       |            |                                                    |                                              |  |  |

|       |            | 9. Remove original section, 7.3.2 and 7.4.2 for VR |                                              |  |  |

|       |            | optimiz                                            | ztions, since VR doesn't support auto-phase  |  |  |

|       |            | droppii                                            | ng for light loading                         |  |  |

|       |            | 1.                                                 | 8.9.2, Add Beep LED behavior                 |  |  |

| 0.8.1 | 01/22/2016 | 2.                                                 | Remove 8.11 TPM connector                    |  |  |

|       |            | 3.                                                 | Update ME drawing to PVT version             |  |  |

|       |            | Numer                                              | ous Edits:                                   |  |  |

|       |            | 1.                                                 | Added IBM / OpenPOWER notice page            |  |  |

| 0.8.2 | 01/25/2015 | 2.                                                 | Added recognition & logos page               |  |  |

|       |            | 3.                                                 | Added OCP-HL-P license information           |  |  |

|       |            | 4.                                                 | Updated authors information                  |  |  |

|       |            | 1.                                                 | 1. Update BMC chapter                        |  |  |

|       |            | 2.                                                 | 2. 8.9.2, Update Power/ID, Beep and M.2 SATA |  |  |

| 0.9   | 05/04/2016 |                                                    | LED behavior                                 |  |  |

|       |            | 3.                                                 | 3. 8.10.2, Update Fan LED behavior           |  |  |

|       |            | 4.                                                 | 4. Add DIMM population Rule in 3.5.4         |  |  |

|       |            | 1.                                                 | Edits for grammar and flow                   |  |  |

|       |            | 2.                                                 | Added various BMC-based firmware update      |  |  |

| 1.0   | 08/05/2016 |                                                    | methods.                                     |  |  |

|       |            | 3.                                                 | Added host-based CPLD firmware update        |  |  |

|       |            |                                                    | methods.                                     |  |  |

| 1.0.1 | 10/23/2016 | Change in attribution for Poly Yeh                 |                                              |  |  |

# **Table of Contents**

| 1 | License | e and Notices                                   | 2  |

|---|---------|-------------------------------------------------|----|

|   | 1.1     | Open Compute License Notice                     | 2  |

|   | 1.2     | IBM and OpenPOWER Notice Page                   | 3  |

| 2 | Recogr  | nition & Logos                                  | 5  |

| 3 | Revisio | n History                                       | 6  |

| 4 | Scope . |                                                 | 12 |

| 5 | System  | Block Diagram                                   | 13 |

| 6 | Produc  | t Features                                      | 15 |

|   | 6.1     | Feature List                                    | 15 |

|   | 6.2     | Power Distribution from Each Bus Bar            | 17 |

|   | 6.3     | MB Placement                                    | 18 |

|   | 6.4     | I/O Board Placement                             | 19 |

|   | 6.5     | Processor and Memory                            | 19 |

|   | 6.5.1   | Processor Feature Set                           | 19 |

|   | 6.5.2   | Memory Buffer                                   | 19 |

|   | 6.5.3   | Memory Support                                  | 20 |

|   | 6.5.4   | DIMM Population Rule                            | 21 |

|   | 6.6     | Storage                                         | 23 |

|   | 6.6.1   | Power Expander board Placement                  | 23 |

|   | 6.6.2   | BPX15 Placement                                 | 23 |

|   | 6.7     | Printed Circuit Board Information               | 25 |

|   | 6.6.1   | MB 20-Layer Stack-up                            | 26 |

|   | 6.6.2   | IO 14-layer Stack-up                            | 27 |

| 7 | System  | n Firmware (System BIOS) & CPLD                 | 28 |

|   | 7.1     | Update Complex Programmable Logic Device (CPLD) | 28 |

| 8  | вмс    |                                                 | . 29 |

|----|--------|-------------------------------------------------|------|

|    | 8.1    | Management Network Interface                    | . 29 |

|    | 8.2    | Local Serial Console and Serial-Over-LAN(SOL)   | . 29 |

|    | 8.3    | Graphic and GUI                                 | . 30 |

|    | 8.4    | Remote Power Control and Power Policy           | . 30 |

|    | 8.5    | Power and System Identification LED             | . 30 |

|    | 8.6    | BMC Heartbeat LED                               | . 31 |

|    | 8.7    | Power and Thermal Monitoring and Power Limiting | . 31 |

|    | 8.8    | Sensors                                         | . 32 |

|    | 8.9    | System Event Log (SEL)                          | . 32 |

|    | 8.10   | Fan Speed Control in BMC                        | . 32 |

|    | 8.11   | BMC Firmware                                    | . 33 |

|    | 8.12   | BMC Firmware Update Methods                     | . 34 |

|    | 8.12.1 | Physical Method                                 | . 34 |

|    | 8.12.2 | Host Operating System Method                    | . 34 |

|    | 8.12.3 | Direct-to-BMC-Over-Network-Interface Method     | . 35 |

|    | 8.13   | BMC Update BIOS                                 | . 35 |

| 9  | Therma | al Design Requirements                          | . 36 |

| 10 | Mother | board Power system                              | . 37 |

|    | 10.1   | Input Voltage                                   | . 37 |

|    | 10.2   | Hot Swap Controller (HSC) Circuit               | . 37 |

|    | 10.3   | CPU Voltage Regulator (VR)                      | . 37 |

|    | 7.3.1  | CPU Maximum Power                               | . 37 |

|    | 7.3.2  | CPU VRM Efficiency                              | . 38 |

|    | 7.3.3  | CPU Core VR Configuration                       | . 38 |

|    | 7.4    | Memory Buffer Voltage Regulator                 | . 38 |

|   | 7.4.1   | DIMM Power Rails                          | . 38 |

|---|---------|-------------------------------------------|------|

|   | 7.4.2   | DIMM VR Configuration                     | . 38 |

|   | 7.5     | Voltage Regulator Module Design Guideline | . 38 |

|   | 7.6     | Hard Drive Power                          | . 39 |

|   | 7.7     | System VRM Efficiency                     | . 39 |

|   | 7.8     | Power On                                  | . 39 |

|   | 7.9     | APSS                                      | . 39 |

| 8 | I/O Sys | tem                                       | . 40 |

|   | 8.1     | Impact Board to Board Connector           | . 40 |

|   | 8.2     | DIMM Connector                            | . 41 |

|   | 8.3     | PCIe Slot Connector/Riser Card            | . 42 |

|   | 8.4     | OCP PCI-E Mezzanine Card                  | . 42 |

|   | 8.5     | Network                                   | . 48 |

|   | 8.6     | USB                                       | . 49 |

|   | 8.7     | SATA                                      | . 50 |

|   | 8.8     | Debug Header                              | . 52 |

|   | 8.9     | Switches and LEDs                         | . 53 |

|   | 8.9.1   | Switches                                  | . 53 |

|   | 8.9.2   | Power, M.2 SATA HDD & BEEP LEDs           | . 55 |

|   | 8.9.3   | HDD Carrier & Tray LEDs                   | . 56 |

|   | 8.10    | Fan Connector & LEDs                      | . 58 |

|   | 8.10.1  | Fan Connector                             | . 58 |

|   | 8.10.2  | Fan LEDs                                  | . 59 |

|   | 8.11    | UART Connector                            | . 60 |

|   | 8.11.1  | System UART                               | . 60 |

# Open Compute Project • Barreleye G1 Specification, Chassis, Motherboard, IO Board

|    | 8.11.2  | BMC Debug UART             | . 60 |

|----|---------|----------------------------|------|

| 9  | Mecha   | nical                      | . 61 |

|    | 9.1     | Sled                       | . 61 |

|    | 9.2     | Top View                   | . 62 |

|    | 9.3     | Front View                 | . 63 |

|    | 9.4     | Rear View                  | . 64 |

|    | 9.5     | MB                         | . 65 |

|    | 9.6     | I/O Board                  | . 66 |

|    | 9.7     | Power Expander Board       | . 66 |

|    | 9.8     | BPx15                      | . 67 |

|    | 9.9     | Hard Drive Tray            | . 67 |

|    | 9.9.1   | Top View                   | . 68 |

|    | 9.9.2   | Front View                 | . 69 |

|    | 9.10    | Rack                       | . 69 |

|    | 9.11    | Rack Knife                 | . 70 |

| 10 | Lunch E | 3ox                        | . 72 |

|    | 10.1    | Lunch Box Feature          | 72   |

|    | 10.1.1  | Top View                   | . 72 |

|    | 10.2    | Power Supply Specification | . 72 |

|    | 10.2.1  | Power Supply Overview      | 73   |

# 4 Scope

This document describes the specification of Barreleye, an OpenPOWER-based Open Compute server, with a mechanical & electrical package designed for Open Rack.

The hardware engineering specification provides technical details for the server board's functional architecture and feature set, and some mechanical design details.

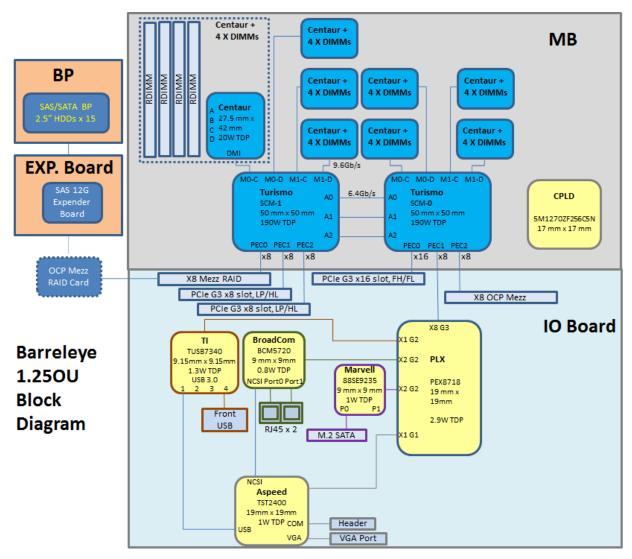

# 5 System Block Diagram

The Barreleye platform consists of IBM POWER8 "Turismo" SCM (Single Chip Module) Processor with IBM "Centaur" Memory Buffers, with PCI-E Gen 3 integrated on chip. Additional details follow.

- IBM POWER8 "Turismo" SCM Processors connects directly to Memory Buffers through a DMI interface operating at 9.6 GTs x 3B.

- Each processor is directly connected to four buffers, with 8 total buffers on board.

- Each buffer connects to 4 DIMM slots

- o Each buffer also functions as a 16MiB L4 cache (128 MiB of cache, total)

- Each buffer provides an additional 9.6 GTs x 3B of memory bandwidth, to the system

- o In this configuration, maximum bandwidth to DRAM is 115.2 GiBps, per socket, and 230.4 GiBps per system.

- The communication between each CPU is A-Bus, operating at 6.4 GTs x 2B.

- There are three A-Bus links between the CPUs, providing a total bandwidth of 38.4 GiBps

- POWER8 "Turismo" includes an integrated PCI Gen 3 interface, with a total of 56 lanes spread between processors.

# 6 Product Features

# 6.1 Feature List

| Project<br>name    | Barreleye                                                                                                                                    |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--|

| Chassis Size       | 1.25OU                                                                                                                                       |  |

| СРИ                | IBM POWER8 "Turismo" SCM Processor x 2, 2296 pins Socket (support up to 12-core, 190W CPU)                                                   |  |

| Memory<br>Buffer   | IBM Centaur, 4 Memory buffers per Processor, total 8 memory buffer                                                                           |  |

| Memory             | 4 DDR3 Memory channels per memory buffer; total 32 DDR3 RDIMMs,1333 MHz(1DPC), 8/16/32GB                                                     |  |

| Storage            | 15x 12Gb/s SAS or 6Gb/s SATA 2.5" drive slots, up to 15mm thickness, connected via SEB, to an onboard HBA. One M.2 SATA slot, also on board. |  |

| Graphic            | Integrated in iBMC (ASPEED AST2400) chip                                                                                                     |  |

| Onboard<br>Network | BroadCom BCM5720, GbE Controller, dual ports                                                                                                 |  |

| PCIE Bridge        | PLX PEX 8718                                                                                                                                 |  |

| USB<br>Controller  | TI TUSB 7340, support USB 3.0                                                                                                                |  |

| SATA<br>Controller | Marvell 88SE9235, support for M.2 SATA                                                                                                       |  |

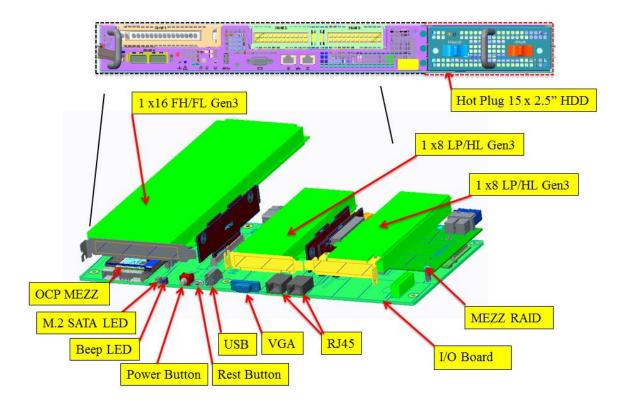

| Front I/O  | VGA, 2x RJ45 connector, 1x USB3.0(Front side), Power/Reset button, Power/ID LED, M.2 SATA HDD LED, BEEP LED                                                                                                                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Management | iBMC ASPEED AST2400 with a share NIC 1GbE LAN port(BroadCom BCM5720)                                                                                                                                                                                                                                                                                                      |

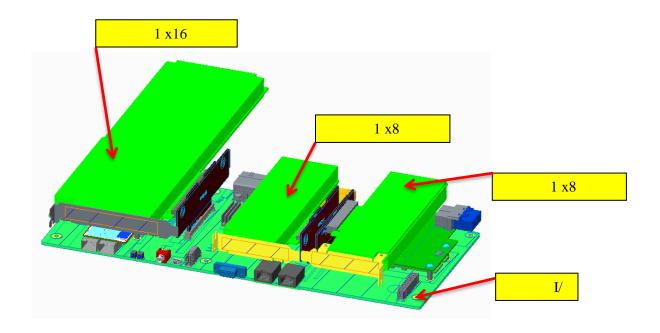

| PCI-e Slot | 1 x 16 Gen3 FH/FL, 2 x8 Gen3 LP/HL, 1 x8 OCP Mez with front Panel access, 1 x8 PCIe OCP Mez in a non-front-accessible internal slot to support SAS HBA or Raid-on-Chip with SuperCap.                                                                                                                                                                                     |

| Board Size | MB: 600mm x380mm(20-Layer);  I/O Board: 367.5mm x 161.74mm(14-Layer);  BPx15: 485.5mmx50mm(14-Layer);  Power Expander Board: 130mmx120mm(10-Layer);  PCIEx16 Riser: 137.9mm x 40.3 mm(4-Layer);  PCIEx8 Right Riser: 98.09mm x 44.10mm(6-Layer);  PCIEx8 Left Riser: 97.65 x 44.0 mm(4-Layer);  Mez RAID Card: 110.5 mm x 68mm(10-Layer)  RMC: 358.3 mm x 76 mm (6-Layer) |

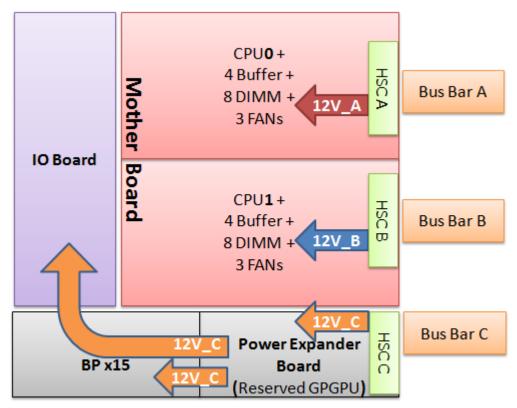

### 6.2 Power Distribution from Each Bus Bar

Bus Bar A: Max. 522.36W, Typical 464.62W, Usage Power 394.73W

Bus Bar B : Max. 522.36W, Typical 464.62W, Usage Power 394.73W

Bus Bar C: Max. 516.07W, Typical 490.22W, Usage Power 336.52W

Total usage power: ~1.2KW, attachment is power budget.

HSC: Hot Swap Controller

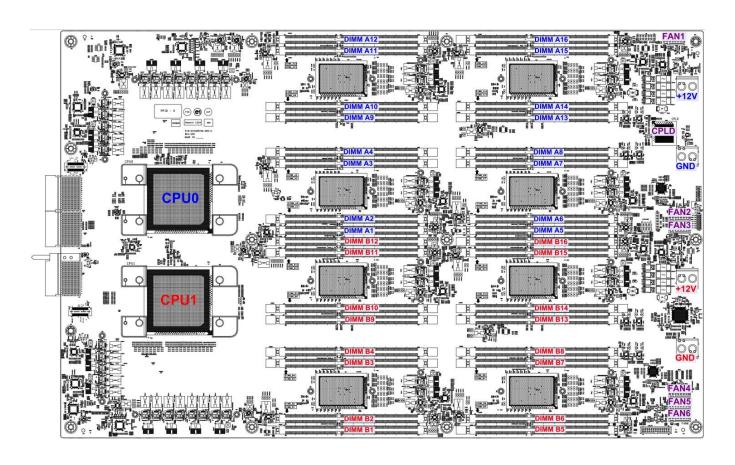

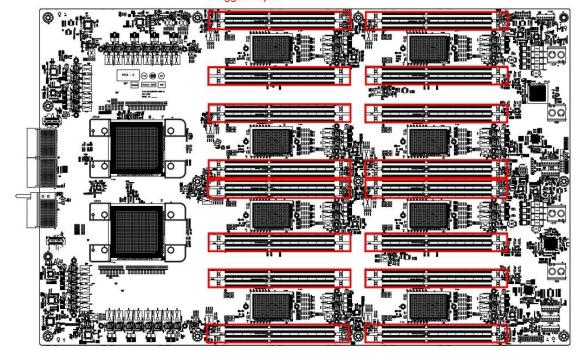

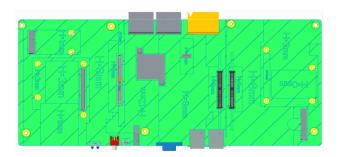

# 6.3 MB Placement

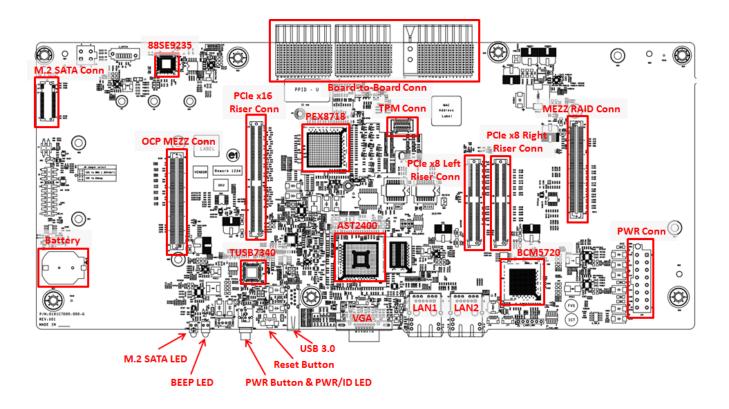

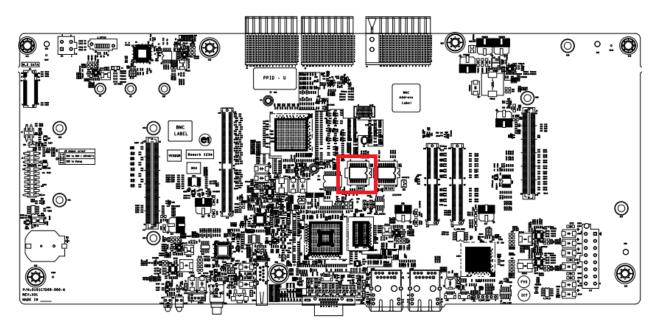

# 6.4 I/O Board Placement

# 6.5 Processor and Memory

### **6.5.1** Processor Feature Set

IBM POWER8 "Turismo" SCM Processor x 2, 2296 pins Socket, support up to 12-core, 190W CPU.

# 6.5.2 Memory Buffer

IBM Centaur, 4 Memory buffers per Processor, total 8 memory buffer connect to CPU0/1 through DMI interface.

# 6.5.3 Memory Support

The OpenPOWER memory subsystem supports IS RDIMM DDR3 memory of sizes 4 GB, 8 GB, 16 GB, and 32 GB. All memory configurations run at 1333 Mbps with the exception of the 4-rank dual-drop configuration which runs at 1066 Mbps. Below table shows the configuration of the supported DIMMs.

### POWER8 DIMM Support

|          |           |                       |           | 4 Gb DRAM Density |                      |                                         |

|----------|-----------|-----------------------|-----------|-------------------|----------------------|-----------------------------------------|

| Raw Card | DRAM Type | DIMM<br>Configuration | DIMM Type | DIMM<br>Capacity  | DRAM V <sub>DD</sub> | DRAM Speed<br>(MHz)                     |

| Α        | DDR3      | 1Rx8                  | RDIMM     | 4 GB              |                      | 1333                                    |

| С        |           | 1Rx4                  |           | 8 GB              |                      | 1333                                    |

| В        |           | 2Rx8                  |           | 8 GB              | 1.35                 | 1333                                    |

| Е        |           | 2Rx4                  |           | 16 GB<br>32 GB    | 1333                 |                                         |

| F,<br>AB |           | 4Rx4                  |           |                   |                      | 1333 (single drop),<br>1066 (dual drop) |

### **6.5.4 DIMM Population Rule**

The following rules for attaching memory to the memory buffer ports must be followed at all times:

- 1. All memory attached to a port pair must be of the same speed, type, size, and technology.

- 2. Port pairs can contain different sizes and types of the same SDRAM generation. For example, port A/B (0/1) can attach to 2 GB industry standard (IS) DIMMs while port C/D (2/3) is attached to 4 GB IS DIMMs.

- 3. All memory across all the ports must operate at the same frequency.

In summary, the minimum requirement for IPL is at least one port pair behind a memory buffer in the system has 2 DIMMs (the 2 DIMMs must be the same), because Power8 supports only 2 DIMMs behind a port pair to IPL.

Barreleye enables a memory interleave feature by default. Unless this setting is changed in firmware, the default minimum requirement for IPL is 4 DIMMs because the paired port pair needs at least 2 DIMMs in each. The following table shows the DIMM label of paired port pair.

# DIMM Population Rule

|          | DIMM Labels        |

|----------|--------------------|

| Paired 1 | A1, A2, A5, A6     |

| Paired 2 | A3, A4, A7, A8     |

| Paired 3 | A9, A10, A13, A14  |

| Paired 4 | A11, A12, A15, A16 |

| Paired 5 | B1, B2, B5, B6     |

| Paired 6 | B3, B4, B7, B8     |

| Paired 7 | B9, B10, B13, B14  |

| Paired 8 | B11, B12, B15, B16 |

# Plugged in pair

# 6.6 Storage

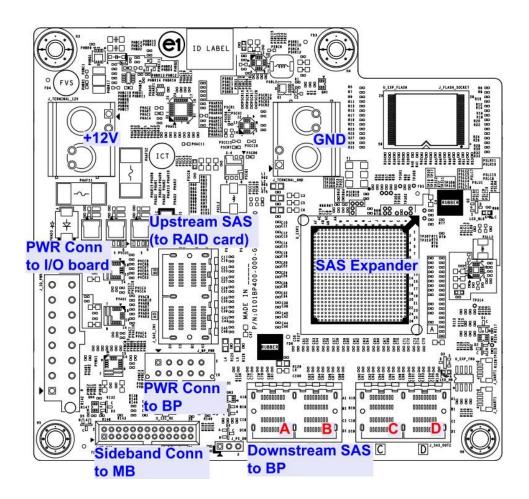

# **6.6.1** Power Expander board Placement

# 6.6.2 BPX15 Placement

# 6.7 Printed Circuit Board Information

Each PCB material and stack-up are defined in the figure below.

|                         |                                | PCBA Dimension    |

|-------------------------|--------------------------------|-------------------|

| Board                   | PCB Material                   | (L*W*H) (mm)      |

| МВ                      | IT-150DA (VLP + RTF<br>copper) | 600*380*2.65      |

| IO Board                | TU-862HF (RTF copper)          | 367.5*161.73*2.65 |

| BPX15                   | IT-150DA (VLP + RTF<br>copper) | 485.5*50 *2.82    |

| Power Expander<br>Board | TU-862HF (RTF + HTE copper)    | 120 *130*2.37     |

| Power Fixture Board     | Standard FR4 (HTE copper)      | 208.45*94*1.59    |

| PCIEx16 Riser           | TU-862HF (RTF copper)          | 137.9*40.3*1.58   |

| PCIEx8 Right Riser      | TU-862HF (RTF copper)          | 98.09*44.109*1.58 |

| PCIEx8 Left Riser       | TU-862HF (RTF copper)          | 97.65*44.0*1.58   |

| Mez RAID                | Standard FR4                   | 110.05*68*1.57    |

| RMC board               | Standard FR4 (HTE copper)      | 358.3*76          |

# 6.6.1 MB 20-Layer Stack-up

### 20-Layer Board Stack-Up (2.91 mm)

| Layer Name | Layer Description            | Material    | DK          | Layer Thickness (mil) | Copper Weight (oz) |

|------------|------------------------------|-------------|-------------|-----------------------|--------------------|

|            | SOLDER MASK                  | Solder Mask | 3.80        | 0.50                  |                    |

| Signal1    | SIGNAL                       | Copper      |             | 1.90                  | 0.5 + 1 (plating)  |

|            | PREPREG                      | FR4         | 3.50        | 2.59                  |                    |

| PPlane2    | GND                          | Copper      |             | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.50        | 4.00                  |                    |

| Signal3    | SIGNAL                       | Copper      |             | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.50        | 3.85                  |                    |

| PPlane4    | GND/PWR                      | Copper      |             | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.50        | 4.00                  |                    |

| Signal5    | SIGNAL                       | Copper      |             | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.50        | 3.85                  |                    |

| PPlane6    | GND/PWR                      | Copper      |             | 1.30                  | 1.0                |

|            | CORE                         | FR4         | 3.50        | 10.50                 |                    |

| Signal7    | SIGNAL                       | Copper      |             | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.50        | 3.50                  |                    |

| PPlane8    | GND/PWR                      | Copper      |             | 1.20                  | 1.0                |

| 67         | CORE                         | FR4         | 3.50        | 4.00                  |                    |

| PPlane9    | GND/PWR                      | Copper      |             | 2.40                  | 2.0                |

|            | PREPREG                      | FR4         | 3.50        | 4.00                  |                    |

| PPlane10   | GND/PWR                      | Copper      |             | 2.40                  | 2.0                |

|            | CORE                         | FR4         | 3.50        | 4.00                  |                    |

| PPlane11   | GND/PWR                      | Copper      |             | 2.40                  | 2.0                |

|            | PREPREG                      | FR4         | 3.50        | 4.00                  |                    |

| PPlane12   | GND/PWR                      | Copper      |             | 2.40                  | 2.0                |

|            | CORE                         | FR4         | 3.50        | 4.00                  |                    |

| PPlane13   | GND/PWR                      | Copper      | at a second | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.50        | 3.50                  |                    |

| Signal14   | SIGNAL                       | Copper      |             | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.50        | 10.50                 |                    |

| PPlane15   | GND/PWR                      | Copper      |             | 1.30                  | 1.0                |

|            | PREPREG                      | FR4         | 3.50        | 3.85                  |                    |

| Signal16   | SIGNAL                       | Copper      | ٠           | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.50        | 4.00                  |                    |

| PPlane17   | GND/PWR                      | Copper      |             | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.50        | 3.85                  |                    |

| Signal18   | SIGNAL                       | Copper      |             | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.50        | 4.00                  |                    |

| PPlane19   | GND                          | Copper      |             | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.50        | 2.59                  |                    |

| Signal20   | SIGNAL                       | Copper      |             | 1.90                  | 0.5 + 1 (plating)  |

|            | SOLDER MASK                  | Solder Mask | 3.80        | 0.50                  |                    |

| ~          | Overall Board Thickness w/SI | Л           |             | 115.98                | mils Tol: +/-10%   |

# 6.6.2 IO 14-layer Stack-up

| 14-Laver Board Stack-L | 'n |

|------------------------|----|

| Layer Name | Layer Description            | Material    | DK               | Layer Thickness (mil) | Copper Weight (oz) |

|------------|------------------------------|-------------|------------------|-----------------------|--------------------|

| Layer Name | SOLDER MASK                  | Solder Mask | 3.80             | 0.50                  | Sopper Weight (02) |

| Signal1    | SIGNAL                       | Copper      |                  | 1.90                  | 0.5 + 1 (plating)  |

| Oigna. i   | PREPREG                      | FR4         | 3.70             | 4.00                  | , (p.m.n.s)        |

| GPlane2    | GND                          | Copper      |                  | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.70             | 4.00                  |                    |

| Signal3    | SIGNAL                       | Copper      |                  | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.70             | 11.56                 |                    |

| GPlane4    | GND                          | Copper      |                  | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.70             | 4.00                  | 30000              |

| Signal5    | SIGNAL                       | Copper      |                  | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.70             | 11.56                 |                    |

| GPlane6    | GND                          | Copper      |                  | 1.20                  | 1.0                |

|            | CORE (2-ply)                 | FR4         | 3.70             | 4.00                  |                    |

| PPlane7    | GND/PWR                      | Copper      |                  | 2.40                  | 2.0                |

|            | PREPREG (2-ply)              | FR4         | 3.70             | 16.14                 |                    |

| PPlane8    | GND/PWR                      | Copper      |                  | 2.40                  | 2.0                |

|            | CORE (2-ply)                 | FR4         | 3.70             | 4.00                  |                    |

| GPlane9    | GND                          | Copper      |                  | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.70             | 11.56                 |                    |

| Signal10   | SIGNAL                       | Copper      |                  | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.70             | 4.00                  |                    |

| GPlane11   | GND                          | Copper      |                  | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.70             | 11.56                 |                    |

| Signal12   | SIGNAL                       | Copper      |                  | 1.20                  | 1.0                |

|            | CORE                         | FR4         | 3.70             | 4.00                  |                    |

| GPlane13   | GND                          | Copper      |                  | 1.20                  | 1.0                |

|            | PREPREG                      | FR4         | 3.70             | 4.00                  |                    |

| Signal14   | SIGNAL                       | Copper      |                  | 1.90                  | 0.5 + 1 (plating)  |

| 8          | SOLDER MASK                  | Solder Mask | 3.80             | 0.50                  |                    |

|            | Overall Board Thickness w/SI | 115.98      | mils Tol: +/-10% |                       |                    |

# 7 System Firmware (System BIOS) & CPLD

Barreleye uses OpenPOWER's open source system firmware, made available under open source licensing schemes, available at https://github.com/open-power.

Barreleye machine configuration data files are available here: https://github.com/open-power/barreleye-xml

Barreleye also includes a Complex Programmable Logic Device, to control power up/down/reset sequencing. Firmware for the CPLD is included in Barreleye design collateral available at on opencompute.org.

BIOS update methods are available with documentation on <a href="https://github/open-power">https://github/open-power</a>.

CPLD update methods are available below.

# 7.1 Update Complex Programmable Logic Device (CPLD)

- 1. Download and extract CPLD firmware archive, it will contain a \*.jbc (Jam Byte Code) file and a binary "jbi" that can be used to flash the CPLD with the bytecode

- 2. From petitboot or an OS loaded on the host use jbi to update the CPLD:

- a. ./jbi -aprogram barreleye\_v20\_160120.jbc

# 8 BMC

The motherboard uses a BMC for various platform management services and interfaces with hardware, BIOS.

The BMC is a standalone system in parallel to the host. The health status of the host system should not affect the normal operation and network connectivity of the BMC. The BMC cannot share memory with the host system. BMC management connectivity should work independently from the host. If using a shared NIC, there should be no NIC driver dependency for out-of-band (OOB) communication.

# 8.1 Management Network Interface

The BMC support RMII/NCSI port for OOB access. Shared-NIC (host and BMC) uses RMII/NCSI interfaces to pass management traffic on BroadCom BCM5720. BCM5720 has 10/100/1000 MDI interface to RJ45(LAN1). Some Barreleye implementations can also support a BCM5719A for Link Flap Avoidance improvements, but are not presently documented here. A 5719A implementation (including board files) may be added as an addendum to a future version of this specification.

# 8.2 Local Serial Console and Serial-Over-LAN(SOL)

The BMC needs to support two access paths to the serial console:

- 1. A local serial console on debug header, described in section 8.12.2.

- 2. A remote console, available via IPMI Serial-Over-LAN (IPMI-SOL), or Secure Shell (SSH), through the management network.

### 8.3 Graphic and GUI

Graphic and GUI features integrated in BMC (ASPEED AST2400) chip.

# 8.4 Remote Power Control and Power Policy

BMC firmware to support remote system power on/off/cycle and warm reboot through the In-Band or Out-of-Band IPMI, ReST, or SSH commands.

BMC firmware to support power on policy to be last-state, always-on and always-off. The default setting is Last-State. The change of power policy should be supported by IPMI, ReST, or SSH command and take effect without a BMC firmware cold reset or a system reboot.

It should take less than 3 seconds from AC on, for the BMC to process the power button signal and to power the system for POST. A long waiting period for the BMC firmware to get ready before allowing a system POST start is NOT allowed.

# 8.5 Power and System Identification LED

The motherboard must combine the Power LED and the System Identification LED into a single blue LED at the front side.

There are 4 states of Power/system identification LED depending on system power state, and chassis identify status.

Open Compute Project • Barreleye G1 Specification, Chassis, Motherboard, IO Board

Power off, Chassis identify off: LED consistently off

Power off, Chassis identify on: LED on for 0.1sec, off for 0.9sec, and loop

Power on, Chassis identify off: LED consistently on

Power on, Chassis identify on: LED on for 0.9sec, off for 0.1sec, and loop

Power LED on is defined by the readiness of all power rails

Blinking the Power LED blinking is used as a system identifier. The on time is different during power on and power off.

### 8.6 BMC Heartbeat LED

LED always Light: AUX PW OK

LED Blink: BMC ACTIVE(FW Ready)

### 8.7 Power and Thermal Monitoring and Power Limiting

BMC firmware supports platform power monitoring. Power limiting for processor, memory, and platform is required. Access to this function must be available through In-Band and Out-of-Band.

BMC FW supports thermal monitoring, including processor, memory, chipset, and Inlet/outlet air temperatures.

### 8.8 Sensors

This portion of the specification is still in development. See production files and BoM available alongside this specification for current implementation.

# 8.9 System Event Log (SEL)

This portion of the specification is still in development. See production files and BoM available alongside this specification for current implementation.

# 8.10 Fan Speed Control in BMC

BMC I2C connect to HW monitor1/2 to control FAN PWN and read FAN tach. Blue & Red LEDs show FAN status, and these 2 LEDs are controlled by BMC.

### 8.11 BMC Firmware

Barreleye can support a variety of BMC firmware solutions, including OpenBMC. OpenBMC is available primarily through two GitHub repositories:

- 1. The Facebook / OpenBMC repository: https://github.com/facebook/openbmc

- 2. The OpenBMC / OpenBMC repository: https://github.com/openbmc/openbmc

- a. This repository includes most OpenPOWER & Barreleye-specific contributions.

- b. Specific drivers for OpenPOWER machines were contributed here: <a href="https://github.com/openbmc/openbmc/tree/master/meta-openbmc-machines/meta-openpower">https://github.com/openbmc/openbmc/openbmc/tree/master/meta-openbmc-machines/meta-openpower</a>

OpenBMC source code is available under its own license scheme.

# 8.12 BMC Firmware Update Methods

# 8.12.1 Physical Method

Replace BMC ROM with the updated one. The following figure shows the location of BMC ROM socket on IO board.

# 8.12.2 Host Operating System Method

- 1. Log in Linux OS

- 2. Copy the package into disk

- 3. Execute socflashtool.sh in folder \SOCFlash\Linux

When BMC is finished updating, the system will be shut down and BMC reset and Beep LED(amber) will be lighted. After Beep the LED turns off, the BMC is ready and can be power on again, by pushing power button

### 8.12.3 Direct-to-BMC-Over-Network-Interface Method

- 1. Connect to BMC via LAN (ssh connection)

- 2. Update settings:

- preserve\_network\_settings = Preserve network settings, only needed if updating uboot

- restore\_application\_defaults = update read-only file system

- update\_kernel\_and\_apps\_only = update kernel and initramfs

- clear\_persistent\_files = Erase persistent files

- 3. Set settings:

```

curl -k -H "Content-Type: application/json" -X PUT -d "{\"data\": 1}"

```

https://bmc/org/openbmc/control/flash/bmc/attr/<setting>

4. Update from a TFTP server:

```

curl -k -H "Content-Type: application/json" -X POST -d

"{\"data\": "<TFTP server IP address>","<filename>"}"

https://bmc/org/openbmc/control/flash/bmc/action/updateViaTftp

```

# 8.13 BMC Update BIOS

- 1. Transfer a copy of the BIOS image to flash into the /tmp directory of OpenBMC

- 2. Use the "pflash" utility to erase and program the BIOS PNOR

- a. pflash -E -p /tmp/barreleye\_0.2.0.pnor

# 9 Thermal Design Requirements

Thermal design can support 35degC ambient with two 190W Power8 in 1.25OU sled under one fan fail condition. Please refer to Barreleye Thermal Spec for more details.

# 10 Motherboard Power system

### 10.1 Input Voltage

The motherboard can accept and operate normally at an input voltage tolerance range between 10.8V and

13.2V. The motherboard's main power under-voltage protection level is 9.5V (Typ.).

### 10.2 Hot Swap Controller (HSC) Circuit

In order to have better control of the 12.5VDC power input to motherboard.

The motherboard include three hot swap controllers, two for main power and one for stand-by power. The hot swap controller provides:

- Inrush current control when the motherboard is inserted and the server is powered on.

- Current limiting protection for short circuits.

- PMBUS interface to enable the BMC to report server input power.

#### 10.3 CPU Voltage Regulator (VR)

#### 7.3.1 CPU Maximum Power

The motherboard shall be designed to handle a processor with a maximum TDP of 190W CPU.

### 7.3.2 CPU VRM Efficiency

The minimum efficiency for the CPU VRM efficiency is 82% over the 30% to 90% load range and 84% over the 50% to 70% load range for TDP power of CPU, measured from the 12.5V input to the VRM output.

### 7.3.3 CPU Core VR Configuration

The guaranteed rewrite count of NVRAM should be equal to 8.

### 7.4 Memory Buffer Voltage Regulator

#### 7.4.1 DIMM Power Rails

The motherboard design should have DIMM Power Rails for DDR3.

### 7.4.2 DIMM VR Configuration

The guaranteed rewrite count of NVRAM should be equal to 8.

### 7.5 Voltage Regulator Module Design Guideline

All regulators in the system response to an over-current event must be verified. A typical over-current set point is 25% or more above the maximum load current.

#### 7.6 Hard Drive Power

### 7.7 System VRM Efficiency

High-efficiency VRMs for all other voltage regulators over 20W and under 5W not defined in this specification. All other voltage regulation modules shall be 82% efficiency over the 30% to 90% load range.

#### 7.8 Power On

The motherboard should be set to restore the last power state during AC on/off. This means when the AC cycles on/off, the motherboard should power on automatically without someone pressing the power button. When the motherboard is powered off on purpose, it should be kept off through AC on/off.

#### **7.9 APSS**

Use for current monitoring of all 240VA, and connect to CPU through SPI interface. On Chip Controller(OCC) of CPU communicates with APSS and calculates the total power consumption of system, then determines if the system needs to do the power capping. APSS also connects to BMC through I2C interface, so BMC can know the system load current as well.

# 8 I/O System

# **8.1Impact Board to Board Connector**

The Impact board to board connectors are connected between MB and I/O board. There are 3 Impact connectors, refer to the attachment for more details.

### **8.2DIMM Connector**

The DIMM connector is SMT type and support DDR3 DIMM. DIMM connectors must also include lubricant/sealant applied by the connector manufacturer which can remain intact after soldering and other manufacturing processes. The sealant is required to displace any voids in the connector gold plating.

#### 8.3 PCIe Slot Connector/Riser Card

The mother board support 3 PCIE cards, but use non-standard PCIE connectors on mother board, need the corresponding riser cards to support standard PCIE cards. Can support 1 x 16 Gen3 FH/FL and 2 x8 Gen3 LP/HL.

See below for the figures of 3 riser cards.

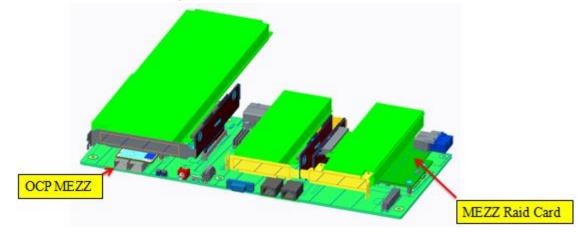

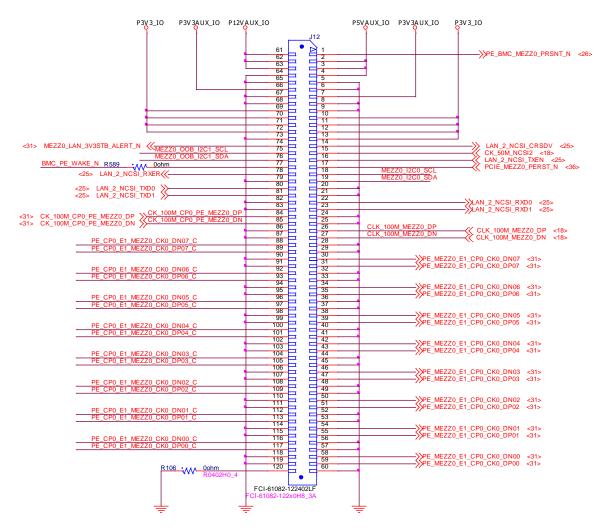

#### 8.40CP PCI-E Mezzanine Card

Two OCP mezzanine connectors (support PCIE Gen3) are placed on the IO board to support 1 x8 OCP mez connector with front Panel access and 1 x8 mez connector for internal slot to support Raid-on-chip with battery backup or SuperCap.

1 x8 OCP mez connector with front Panel access supports standard OCP form factor card. Another 1 x8 OCP mez connector for internal slot loosely follows OCP mezzanine specifications, which is only for RAID function and built LSI 3108 on board.

#### OCP MEZ connector

| OCP MEZ Connector Signal Definitions |     |                                                                               |  |  |  |

|--------------------------------------|-----|-------------------------------------------------------------------------------|--|--|--|

| Signal                               | I/O | Definition                                                                    |  |  |  |

| PE_BMC_MEZZ0_PRSNT_N                 | 0   | OCP MEZ Connector present pin,<br>connect to pin 120 on MEZ card<br>with 0ohm |  |  |  |

| LAN_2_NCSI_RXER                      | 1   |                                                                               |  |  |  |

| LAN_2_NCSI_RXD[0:1]                  | 1   | NC-SI for OOB management                                                      |  |  |  |

|                                 |     | ı                                                |

|---------------------------------|-----|--------------------------------------------------|

| LAN_2_NCSI_CRSDV                | I   |                                                  |

| LAN_2_NCSI_TXEN                 | 0   |                                                  |

| LAN_2_NCSI_TXD[0:1]             | 0   |                                                  |

| LAN_2_NCSI_TXEN                 | 0   |                                                  |

| CK_50M_NCSI2                    | 1   | NC-SI 50M input clock                            |

| MEZZ0_I2C0_SCL                  | I   | PCIe I2C Clock for Mez slot/EEPROM;              |

| MEZZ0_I2C0_SDA                  | I/O | PCIe I2C Data for Mez slot/EEPROM;               |

| MEZZO_LAN_3V3STB_ALERT_N        | 0   | I2C Alert for OOB management                     |

| MEZZ0_OOB_I2C1_SCL              | I   | I2C Clock for OOB management                     |

| MEZZ0_OOB_I2C1_SDA              | I/O | I2C Data for OOB management                      |

| BMC_PE_WAKE_N                   | 1   | PCIe wake up signal                              |

| CK_100M_CP0_PE_MEZZ0_DP/N       | I   | 1 <sup>st</sup> MB clock output for PCIe devices |

| CLK_100M_MEZZ0_DP/N             | I   | 2 <sup>nd</sup> MB clock output for PCIe devices |

| PE_CP0_E1_MEZZ0_CK0_DP/N[00:07] | I   | PCIe Gen3 from CPU to OCP MEZ                    |

| PE_MEZZ0_E1_CP0_CK0_DP/N[00:07] | 0   | PCIe Gen3 from OCP MEZ to CPU                    |

| P3V3_IO                         | 0   | 3.3V input power                                 |

| Ground                          | I/O | Ground pins                                      |

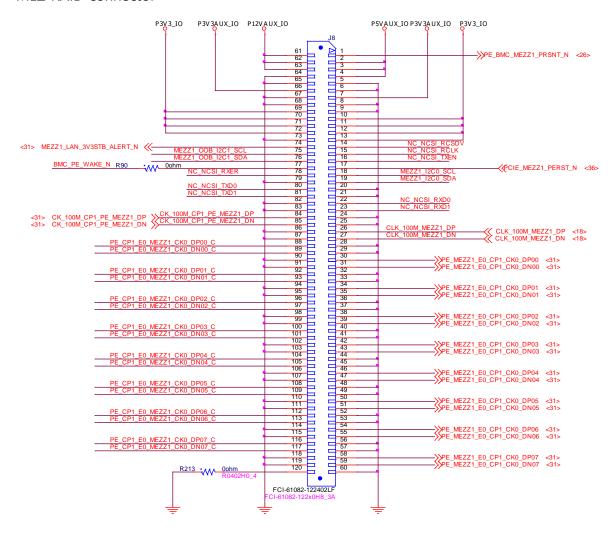

#### MEZ RAID connector

| MEZ RAID Connector Signal Definitions |     |                                                                               |  |  |  |

|---------------------------------------|-----|-------------------------------------------------------------------------------|--|--|--|

| Signal                                | I/O | Definition                                                                    |  |  |  |

| PE_BMC_MEZZ1_PRSNT_N                  | 0   | OCP MEZ Connector present pin,<br>connect to pin 120 on MEZ card<br>with 0ohm |  |  |  |

| MEZZ1_I2C0_SCL                        | 1   | PCIe I2C Clock for Mez slot/EEPROM;                                           |  |  |  |

| MEZZ1_I2C0_SDA                        | I/O | PCIe I2C Data for Mez slot/EEPROM;                                            |  |  |  |

| MEZZ1_LAN_3V3STB_ALERT_N        | 0   | I2C Alert for OOB management                     |

|---------------------------------|-----|--------------------------------------------------|

| MEZZ1_OOB_I2C1_SCL              | I   | I2C Clock for OOB management                     |

| MEZZ1_OOB_I2C1_SDA              | I/O | I2C Data for OOB management                      |

| BMC_PE_WAKE_N                   | I   | PCIe wake up signal                              |

| CK_100M_CP1_PE_MEZZ1_DP/N       | I   | 1 <sup>st</sup> MB clock output for PCIe devices |

| CLK_100M_MEZZ1_DP/N             | I   | 2 <sup>nd</sup> MB clock output for PCIe devices |

| PE_CP1_E0_MEZZ1_CK0_DP/N[00:07] | 1   | PCIe Gen3 from CPU to MEZ RAID                   |

| PE_MEZZ1_E0_CP1_CK0_DP/N[00:07] | 0   | PCIe Gen3 from MEZ RAID to CPU                   |

| P3V3_IO                         | 0   | 3.3V input power                                 |

| Ground                          | I/O | Ground pins                                      |

# 8.5 Network

Support two RJ-45 10/100/1000 LAN ports. NIC Indicators are shown below.

| LAN LED Behavior                     |                                                                                     |

|--------------------------------------|-------------------------------------------------------------------------------------|

| Indicator                            | Indicator Code                                                                      |

| Link and activity indicators are off | The NIC is not connected to the network                                             |

| Link indicator is green              | The NIC is connected to a valid network at its maximum port speed (1Gbps or 10Gbps) |

| Link indicator is amber              | The NIC is connected to a valid network at less than its maximum port speed         |

| Activity indicator is green blinking | Network data is being sent or received                                              |

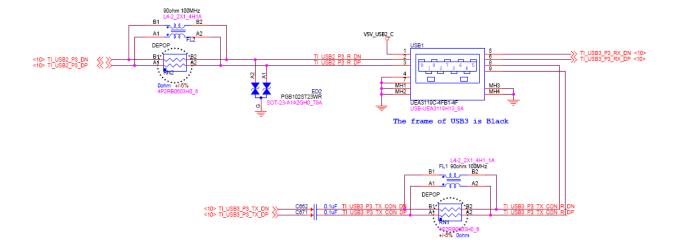

#### **8.6USB**

Support one USB3.0 connector put on front side for user used

USB 3.0 Circuit: USB1 is USB3.0 connector, can support USB3.0 device.

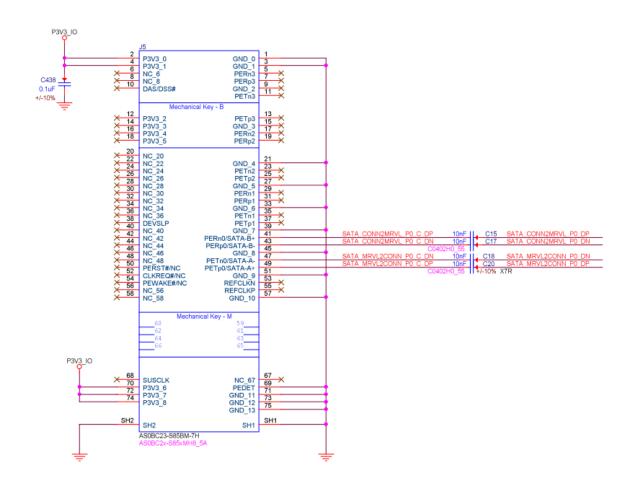

# **8.7SATA**

Support one M.2 connector on I/O board to support M.2 SATA device.

| M.2 Connector Signal Definitions |     |                                                    |  |

|----------------------------------|-----|----------------------------------------------------|--|

| Signal                           | I/O | Definition                                         |  |

| SATA_MRVL2CONN_P0_C_DP/N         | I   | SATA signals from SATA controller to M.2 connector |  |

| SATA_CONN2MRVL_P0_C_DP/N | 0   | SATA signals from M.2<br>connector to SATA<br>controller |

|--------------------------|-----|----------------------------------------------------------|

| P3V3_IO                  | 0   | 3.3V input power                                         |

| Ground                   | I/O | Ground pins                                              |

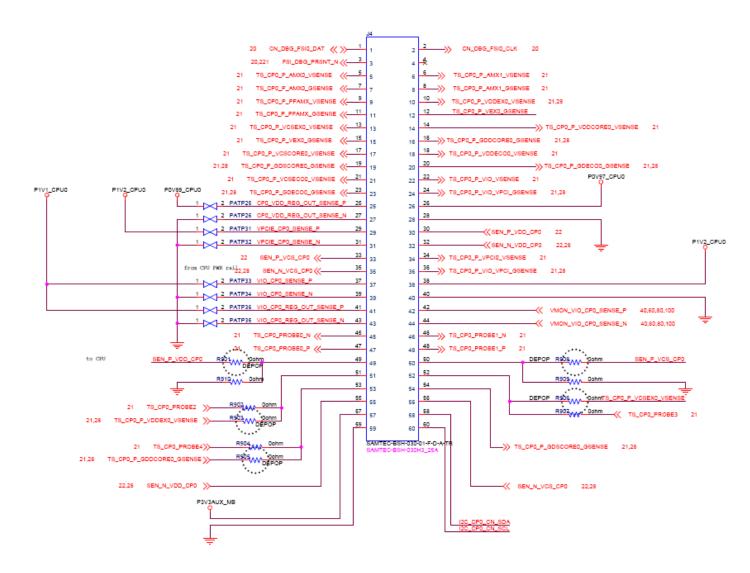

### 8.8 Debug Header

There's a debug header (J4 Connector), the function is CPU status monitoring and some Power sensor.

#### J4 Connector

|         | Open Compute Project • Barreleye G1 Specification, Chassis, Motherboard, IO Board                                                                           |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

|         |                                                                                                                                                             |

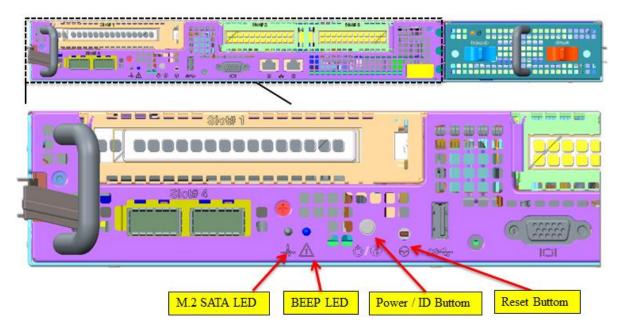

| 8.9Sv   | vitches and LEDs                                                                                                                                            |

|         | The motherboard shall include a power switch, a reset switch, a power LED(combine ID LED), an M.2 SATA HDD activity LED and a beep error LED on front side. |

| 8.9.1   | Switches                                                                                                                                                    |

|         | Two switches put on front-side, one is POWER button and another is RESET button.                                                                            |

| http:// | opencompute.org 53                                                                                                                                          |

When the motherboard is powered off, the end user must push the Power / ID button to power on the system.

The RESET button is designed to generate a platform reset to reset BMC and TPM module.

# 8.9.2 Power, M.2 SATA HDD & BEEP LEDs

The label describes the functionality of Power, M.2 SATA HDD & BEEP LED.

| Front I/O LED           | Front I/O LED Behavior |                                                                                                                                                                              |                                                                                                                                                                                                                                                                         |  |  |

|-------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| LED Type                | LED Color              | Function                                                                                                                                                                     | LED Pattern                                                                                                                                                                                                                                                             |  |  |

| Power/ System<br>ID LED | Blue                   | Power LED on is defined by the readiness of all power rails. Blinking the Power LED blinking is used as a system identifier                                                  | Power off, Chassis identify off:  LED consistently off  Power off, Chassis identify on:  LED on for 0.1sec, off for 0.9sec, and loop  Power on, Chassis identify off:  LED consistently on  Power on, Chassis identify on:  LED on for 0.9sec, off for 0.1sec, and loop |  |  |

| BEEP LED                | Yellow                 | This LED indicates the BMC status. When<br>the LED becomes off, BMC is ready and<br>will power on the system automatically                                                   | BMC code initialing:  LED consistently on  BMC ready:  LED consistently off                                                                                                                                                                                             |  |  |

| M.2 SATA LED            | Green                  | SATA controller detected M.2 SATA HDD,<br>but M.2 SATA hard drive no activity  M.2 SATA hard drive activity. This LED<br>illuminates when M.2 SATA hard drive is<br>activity | Always light Blinking                                                                                                                                                                                                                                                   |  |  |

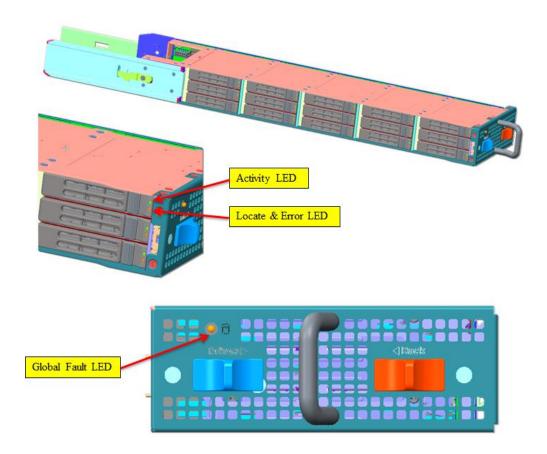

# 8.9.3 HDD Carrier & Tray LEDs

Controlled by expander FW.

| HDD Carrier    | and Tray LED    | Behavior     |                                                                         |                                              |                     |           |                       |

|----------------|-----------------|--------------|-------------------------------------------------------------------------|----------------------------------------------|---------------------|-----------|-----------------------|

| Location       | LED<br>Type     | LED<br>Color | Function                                                                |                                              |                     |           | LED Pattern           |

|                | Locate<br>LED   | Green        | Condition/Event                                                         | Priority<br>(Highest = 0x0<br>Lowest = 0x11) | Error LE            | D Pattern | Locate LED patters    |

|                | 223             |              | INDENT                                                                  | 0x00                                         | OFF                 |           | ON 125ms<br>OFF 125ms |

|                | F               |              | FAULT                                                                   | 0x01                                         | ON                  |           | OFF                   |

| HDD<br>Carrier | Error<br>LED    | Amber        | RR_ABORT                                                                | 0x02                                         | ON 125n<br>OFF 125n |           | OFF                   |

| Carrier        | LLD             |              | REBUILD_REMAP                                                           | 0x03                                         | OFF                 |           | ON 500ms<br>OFF 500ms |

|                | Activity<br>LED | Green        | HOT_SPARE                                                               | 0x04                                         | ON 500m<br>OFF 500m |           | OFF                   |

|                |                 |              | NO_COND                                                                 | 0x05                                         | OFF                 |           | OFF                   |

|                | LLD             |              | DO_NOT_REMOVE                                                           | 0x06                                         | OFF                 |           | OFF                   |

| HDD            | Global<br>Fault | Amber        | "link" down erro<br>HDD drives – W<br>"FAULT", "PRD_F<br>or "HOT_SPARE" | hen HDDs oc                                  | cur                 |           | Always light          |

| Tray           | LED             |              | "link" down erro                                                        |                                              | ne RoC              |           | ON 500ms              |

|                |                 |              | & SEB                                                                   |                                              |                     |           | OFF 500mS             |

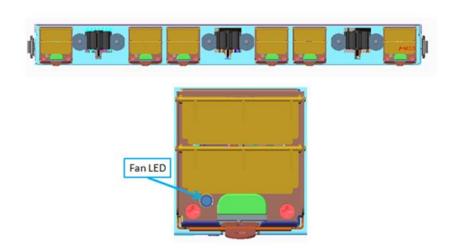

#### 8.10 Fan Connector & LEDs

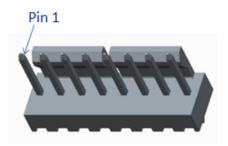

#### 8.10.1 Fan Connector

The motherboard has six fan connectors, and support one fan fail functionality.

The fan connector pin definitions as below, support a dual rotor fan that shares a PWM control signal but has separate tachometer signals. And support two LED to show FAN status.

| Fan | Fan Connector Signal Definitions |                                |  |  |  |  |

|-----|----------------------------------|--------------------------------|--|--|--|--|

| Pin | Wire                             | Definition                     |  |  |  |  |

| 1   | White Wire                       | LED Power, Connect to 3.3V AUX |  |  |  |  |

| 2   | Blue Wire                        | Blue LED -                     |  |  |  |  |

| 3   | Red Wire                         | Red LED -                      |  |  |  |  |

| 4   | Blue Wire                        | Fan Tach of Front Fan          |  |  |  |  |

|     | White Wire                       | PWM of Front FAN               |  |  |  |  |

| 5   | Green Wire                       | PWM of Rear FAN                |  |  |  |  |

| 6   | Yellow Wire                      | Fan Tach of Rear Fan           |  |  |  |  |

|     | Red Wire                         | Main Power of Front Fan,       |  |  |  |  |

| 7   | Orange Wire                      | Connect to 12V                 |  |  |  |  |

|   |            | Main Power of Rear Fan, Connect<br>to 12V |

|---|------------|-------------------------------------------|

|   | Black Wire | GND of Front Fan                          |

| 8 | Brown Wire | GND of Rear Fan                           |

### 8.10.2 Fan LEDs

| Fan LED Behavior |                      |                 |                           |  |  |  |  |

|------------------|----------------------|-----------------|---------------------------|--|--|--|--|

| LED<br>Color     | Function             | LED<br>Pattern  | Comment                   |  |  |  |  |

| Blue             | Fan normal operation | Always<br>light | Bi-color LED and          |  |  |  |  |

| Red              | Fan fault            | Always<br>light | integrated Fan<br>modules |  |  |  |  |

#### 8.11 UART Connector

### 8.11.1 System UART

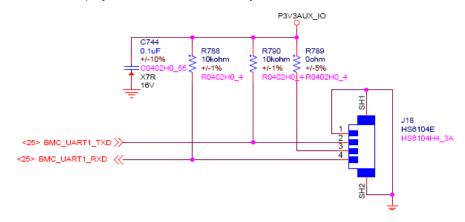

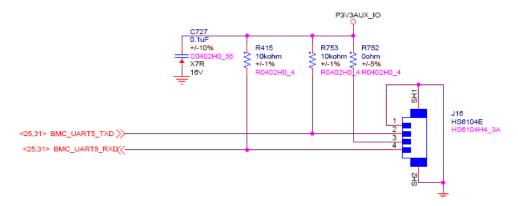

There is a system UART connector J18, which can be redirected to be controlled by LPC bus as physical UARTs of host system.

### 8.11.2 BMC Debug UART

There is a debug UART connector J16 only for BMC console, which is only for BMC designer debug used.

# 9 Mechanical

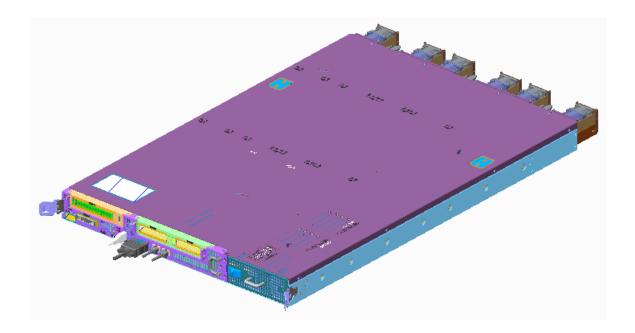

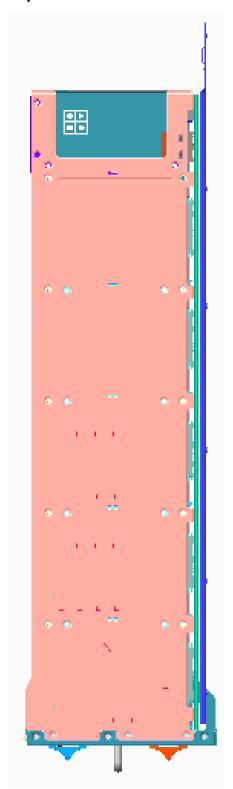

# 9.1Sled

The 1.25OU sled has the dimensions, 537x897.1x56.8mm.

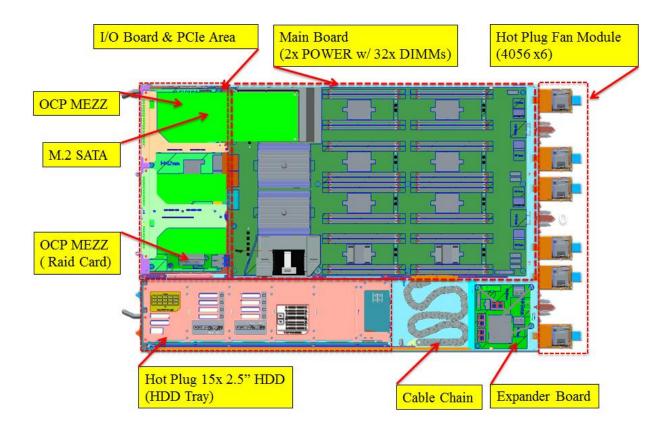

# 9.2Top View

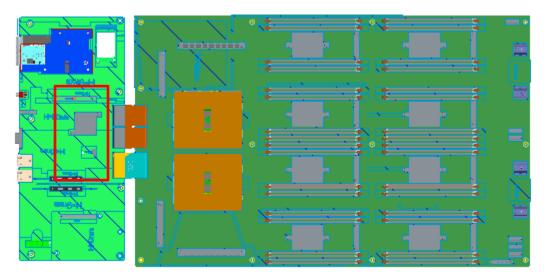

Barreleye supports hot-pluggable 2.5" HDD drives and Fan modules. There are 4 main boards in the system.

They are Main board, I/O board, Expander board and HDD BP.

#### 9.3 Front View

Barreleye supports two x8 LP/HL Gen 3, one x16 FH/FL Gen3 cards and one OCP MEZ Raid Card. The I/O connectors are located on the front. There is one HDD Tray on the right which contains 15pcs Hot-Pluggable 2.5" HDD drives.

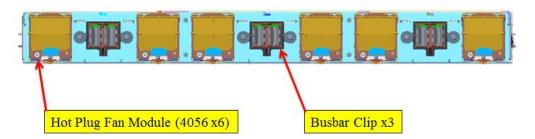

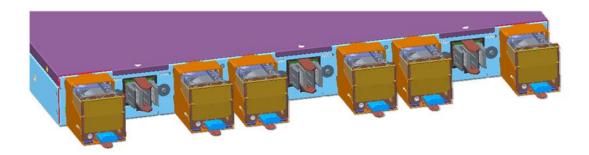

# 9.4Rear View

There are three standard OCP Bus bar clips and 6 Hot-pluggable Fan Modules on the rear wall.

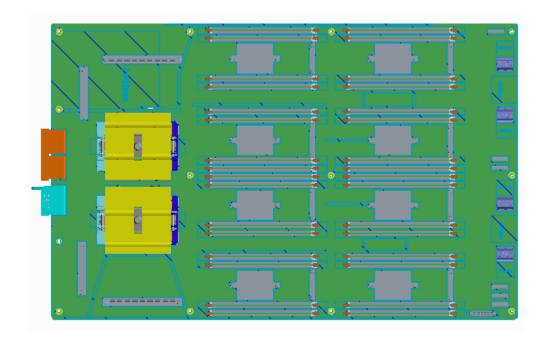

### 9.5 MB

The dimensions of Main board are 600x380mm. It supports two Power CPUs and 32 DIMMs.

# 9.6I/O Board

The dimensions of I/O board are 367.5x160mm. It connects to the main board through the BTB connectors.

# 9.7 Power Expander Board

The dimensions of Power Expander board are 130x120mm. It conducts the SAS signal and Power to I/O board and HDD BP through the cables.

### 9.8BPx15

The dimensions of HDD BP are 485.5x50mm.

# 9.9 Hard Drive Tray

The dimension of Hard Drive Tray is 573.8mm (L) x 146.1mm (W) x 53.6mm (H).

# 9.9.1 Top View

### 9.9.2 Front View

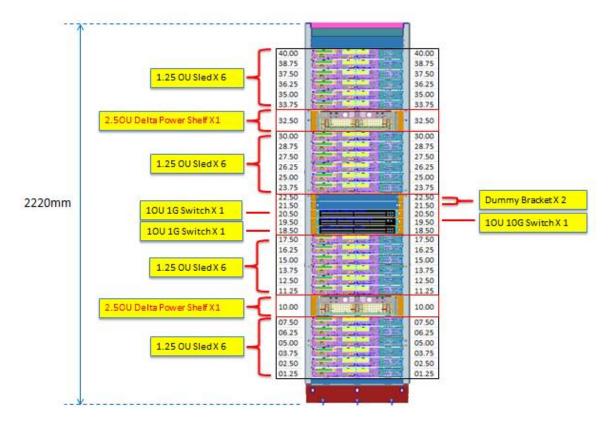

### 9.10 Rack

Barreleye Rack is one standard OCP rack. The configuration shows below. The Switch zone is in the middle.

One Powershelf to support 12 sleds is on the top and another Powershelf with 12 Sleds on the bottom.

#### 9.11 Rack Knife

In order to accommodate the 1.25OU sled into this standard OCP rack, except the standard Support Bracket, we have one special Support Bracket which has 12mm gap from the standard one. These two kinds of brackets are assembled on the rack alternately.

# 10. Lunch Box

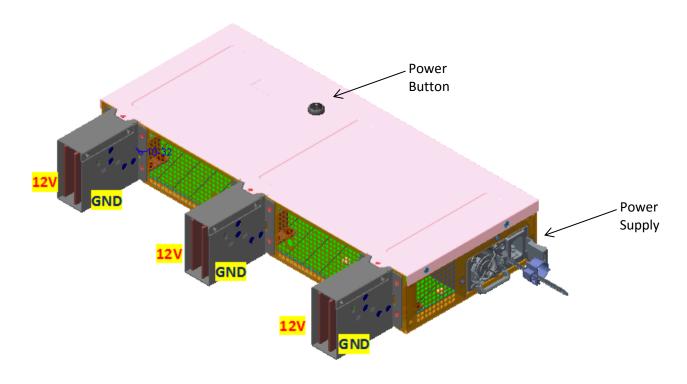

#### 10.1 Lunch Box Feature

Lunch box is a power fixture which supports OCP 1U or 2U sled to power on without Open Rack.

# **10.1.1 Top View**

# **10.2 Power Supply Specification**

The power supply used in Lunch Box is Chicony R1K6A008L.

### 10.2.1 Power Supply Overview

| Form Factor                               |                                        | Custom"1U 86.3(W) x 197.6(D) x 39.3(H)" |                       |  |

|-------------------------------------------|----------------------------------------|-----------------------------------------|-----------------------|--|

| Power Factor Correction                   | n (PFC)                                | Active                                  |                       |  |

| PSU Type                                  |                                        | Server                                  |                       |  |

|                                           |                                        | IEC 61000-4-5 : Common                  | n mode 2.0KV          |  |

| EMC Classification (Sur                   | rge Immunity)                          | Differential mode 1.0KV                 |                       |  |

|                                           |                                        | phases 0, 90, 180, 270 deg.             |                       |  |

|                                           |                                        | Class A                                 |                       |  |

| FCC Classification (Con                   | iducted and Radiated)                  | Class A                                 |                       |  |

| FCC Classification (Con<br>Output Voltage | ducted and Radiated)  Regulation Range | Class A  Minimum Load                   | Maximum Load          |  |

| `                                         | · · · · · · · · · · · · · · · · · · ·  |                                         | Maximum Load<br>133 A |  |

### AC Input Voltage Range

|                                                 | Minimum                                                   | Nominal   | Maximum    |  |

|-------------------------------------------------|-----------------------------------------------------------|-----------|------------|--|

| Input Voltage(High line)                        | 180 V                                                     | 200V~240V | 264 V      |  |

| Frequency                                       | 47 Hz                                                     | 50/60 Hz  | 63 Hz      |  |

| Vin(turn-on)                                    | 170 V                                                     |           | 180 V      |  |

| Vin(turn-off)                                   | 160 V                                                     |           | 175 V      |  |

| Current (Iin)                                   |                                                           |           | 10A@200Vac |  |

| Input Power                                     |                                                           |           | 1850W      |  |

|                                                 | wer supply unit will                                      |           |            |  |

| Vin_OVP Behavior                                | shutdown and latch off, this latch shall be cleared by an |           |            |  |

|                                                 | AC cycling.                                               |           |            |  |

| If input current over 13.5A the power supply un |                                                           |           |            |  |

| Iin_OCP Behavior                                | shutdown and latch off, this latch shall be cleared by an |           |            |  |

|                                                 | AC cycling.                                               |           |            |  |

# 11. Regulatory & Safety Requirements

Barreleye should conform to FCC Part 15, UL, CE, and other similar standards for EMI, Regulatory, and Safety requirements. The design files included in this contribution support common standards in the US, UK, EU, Hong Kong, and Australia.