# Glacier Point V2 Card Design Specification

V0.1

#### **Author:**

Hao Shen, Hardware Engineer, Facebook

Pavan Shetty, Hardware Engineer, Facebook

Chenyu Xu, Mechanical engineer, Facebook

Jarrod Clow, Thermal Engineer, Facebook

Yueming Li, Thermal Engineer, Facebook

Ben Wei, Software Engineer, Facebook

#### **Open Compute Project • Glacier Point V2 Card Design Specification**

# **Copyrights and Trademarks**

Intel® is a trademark of Intel Corporation in the U.S. and/or other countries.

Xeon® is a trademark of Intel Corporation in the U.S. and/or other countries.

Texas Instruments<sup>™</sup> is a trademark of Texas Instruments Incorporated.

# 1 Scope

This specification describes the hardware design details of the Glacier Point Version 2 (GPv2) card. GPv2 is a carrier card designed for accelerator application in Facebook's Yosemite V2 server system.

## 2 Contents

| Co | pyrights | and Trademarks                                     | 2  |  |  |  |

|----|----------|----------------------------------------------------|----|--|--|--|

| 1  | Scope    |                                                    |    |  |  |  |

| 2  | Contents |                                                    |    |  |  |  |

| 3  | Overview |                                                    |    |  |  |  |

| 4  | License  | 3                                                  | 8  |  |  |  |

| 5  | Mecha    | Mechanical Design                                  |    |  |  |  |

|    | 5.1      | Mechanical Outline                                 | 9  |  |  |  |

|    | 5.2      | PCIe Edge Connector                                | 14 |  |  |  |

|    | 5.3      | Platform Design                                    | 14 |  |  |  |

| 6  | Therm    | al Design                                          | 14 |  |  |  |

|    | 6.1      | Data Center Environmental Conditions               | 14 |  |  |  |

|    | 6.2      | Server Operational Conditions                      | 14 |  |  |  |

|    | 6.3      | M.2 Cooling Solution                               | 15 |  |  |  |

|    | 6.4      | Temperature and Power Sensors                      | 16 |  |  |  |

|    | 6.5      | Carrier Card Air Baffle:                           | 16 |  |  |  |

| 7  | Electri  | cal Design                                         | 17 |  |  |  |

|    | 7.1      | Primary X16 Edge Connector Pinout                  | 17 |  |  |  |

|    | 7.2      | Extension X16 Edge Connector B                     | 20 |  |  |  |

|    | 7.3      | Pinout Definitions                                 | 22 |  |  |  |

|    | 7.4      | GPv2 Riser Card Mezzanine Connector Pin Definition | 27 |  |  |  |

|    | 7.5      | M.2 Module Pin Definition                          | 32 |  |  |  |

|    | 7.6      | Dual M.2 Module Support                            | 35 |  |  |  |

|    | 7.7      | PCIe                                               | 36 |  |  |  |

|    | 7.8      | I <sup>2</sup> C                                   | 38 |  |  |  |

|    | 7.9      | Serial port                                        | 39 |  |  |  |

|    | 7.10     | JTAG Port                                          | 40 |  |  |  |

|    | 7.11     | Slot ID                                            | 40 |  |  |  |

## Open Compute Project • Glacier Point V2 Card Design Specification

|    | 7.12                | Pin Header                              | 41 |  |

|----|---------------------|-----------------------------------------|----|--|

| 8  | Power.              |                                         | 41 |  |

|    | 8.1                 | Input                                   | 41 |  |

|    | 8.2                 | Input Capacitance                       | 42 |  |

|    | 8.3                 | Glacier Point V2 power capacity         | 42 |  |

|    | 8.4                 | Power sequence and standby power        | 42 |  |

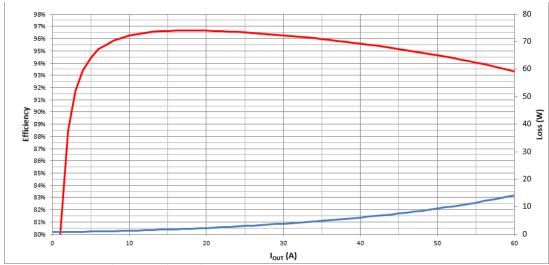

|    | 8.5                 | VR specifications                       | 42 |  |

|    | 8.6                 | Power telemtry and power capping        | 43 |  |

| 9  | Functio             | n                                       | 44 |  |

|    | 9.1                 | Accelerator Carrier card                | 44 |  |

|    | 9.2                 | Debug Interface                         | 44 |  |

|    | 9.3                 | Storage                                 | 44 |  |

|    | 9.4                 | EEPROM                                  | 45 |  |

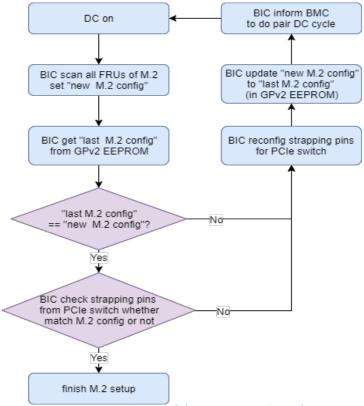

|    | 9.5                 | Module type enumeration                 | 45 |  |

|    | 9.6                 | Glacier Point V2 Management             | 46 |  |

|    | 9.7                 | LEDs                                    | 61 |  |

| 10 | Environ             | mental Requirements                     | 61 |  |

|    | 10.1                | Vibration and Shock (Harsha to revisit) | 62 |  |

| 11 | Prescril            | oed Materials                           | 63 |  |

|    | 11.1                | Disallowed Components                   | 63 |  |

|    | 11.2                | Capacitors and Inductors                | 63 |  |

|    | 11.3                | Component De-rating                     | 63 |  |

| 12 | Labels and Markings |                                         |    |  |

| 13 | Revision History6   |                                         |    |  |

#### 3 Overview

This document describes a card named Glacier Point V2 that is plugged in the Yosemite V2 platform. The Yosemite V2 Platform is a next generation multi-node server platform that hosts four Open Compute Platform (OCP) compliant One Socket (1S) server cards, or two sets of 1S server card and device card pairs in a sled that can be plugged into an OCP vCubby chassis, which is a new 4OU form factor design to easily service and accommodate thermal challenges with higher power 1S servers and device cards.

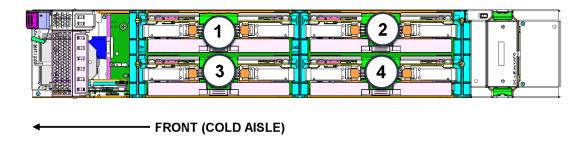

Glacier Point V2 card is one type of the device card that will pair with 1S server card to support accelerator and storage application. it is located on slot 1 and 3 in Yosemite V2 cubby and pair with Twin Lake CPU card which is located on slot 2 and 4. Slot 1 and 2 will form a subsystem; slot 3 and 4 will form another subsystem.

Figure 3-1 Yosemite V2 Cubby top view

The Glacier Point V2 implements primary and extension x16 PCle edge connectors which is the same as the 1S server specification. The primary x16 PCle edge connector supports:

- PCIe Gen3 ports x8

- A USB 2.0 port

- A Universal Asynchronous Receiver/Transmitter (UART) port

- An I<sup>2</sup>C bus for server management

- A System Management Bus (SMBus) as the sideband of the integrated network controller

- Power and Ground Pins

The extension x16 PCIe edge connector supports:

- PCle Gen3 ports x16

- Power and Ground Pins

The Glacier Point V2 supports up to 12x M.2 22110 module or up to 6x Dual M.2 modules. M.2 module form factor is defined in PCIe M.2 specification. That will support standard SSD and accelerator modules. Dual M.2 form factor is defined by Facebook. It can be simply treated as the combination of two M.2 form factor with 2mm pitch in between. Dual M.2 form factor provides more surface area and power which is a good extension of M.2 for applications that need bigger ASIC and higher power consumption.

Both M.2 form factor and Dual M.2 form factor has been customized to better support accelerator application. Please refer to M.2 and Dual M.2 accelerator hardware specification for details.

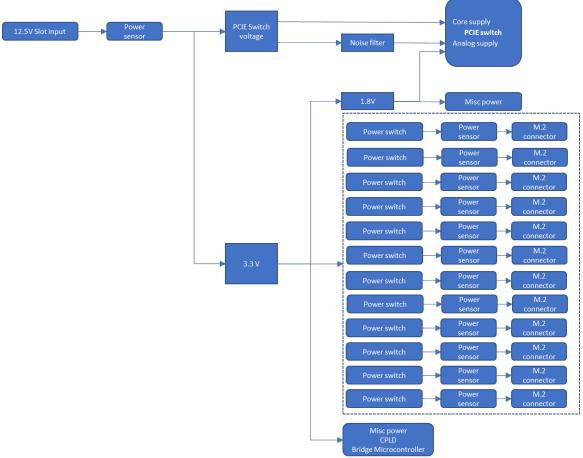

The Glacier Point V2 receives 12.5V from the platform with a maximum current load of 7.7A from the primary edge connector and an additional 7.7A from the extension edge connector. The platform, however, defines and controls the maximum power used by the Glacier Point V2. The Glacier Point V2 uses the INA230 power sensor at the power input to measure the total card power consumption of the whole server with +/-1% accuracy. The power data measured by this sensor can be used by the platform for power management purposes. When the power consumption has exceeded the power limit, the Bridge IC will generate a throttle event to force the all the modules on GPv2 board to throttle to the lowest power state. That throttle capability is defined in accelerator modules only. Storage modules do not support that capability.

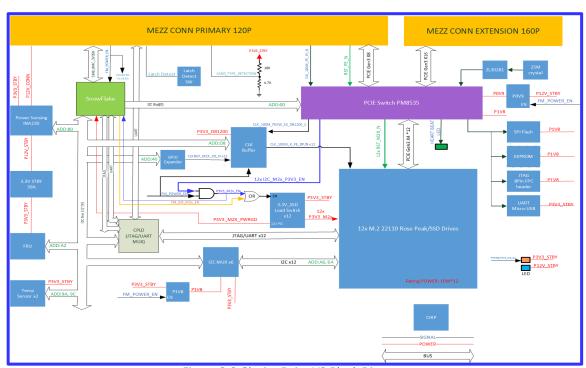

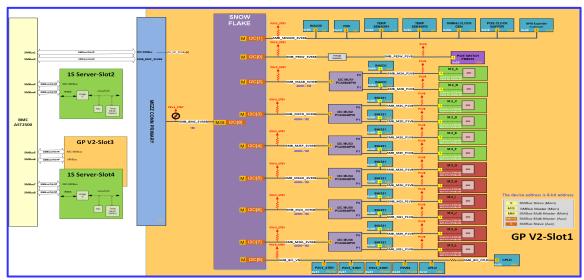

Figure 3-2 Glacier Point V2 Block Diagram

A Bridge IC (Texas Instrument's Tiva microcontroller, show as SnowFlake in Figure 3-2) is used as the management controller on the GPv2 card as the bridge between the BMC and the M.2 modules. The Bridge IC (BIC) manages the M.2 modules on behalf of the BMC. To maximize the communication bandwidth between the BMC and the Bridge IC, a dedicated point-to-point I<sup>2</sup>C bus shall be used.

A PCIE Fanout switch (Microchip PM8535) is used to expand 24 PCIE Gen3 lanes to 48 PCIE Gen3 lanes to support up to 12x M.2 modules. The PCIE switch also have the DPC feature that will help to support the failure recovery of end point device.

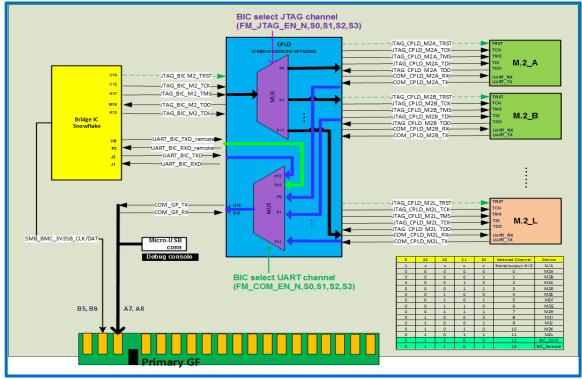

Glacier Point V2's Field Replaceable Unit (FRU) EEPOM and thermal sensors are connected to the Bridge IC's I<sup>2</sup>C buses. Each M.2 module's I2C buses are connected to bridge IC though multiple I2C muxes. We have defined additional debug interface (UART/JTAG) for each M.2 module. Those debug interfaces are connected to the BIC with a CPLD served as a switch in between. Overall, through the interface between BIC, BMC can access the Glacier Point V2's thermal sensors, FRU, M.2 Module's sideband interface and debug interface with standard IPMI commands.

PCIE switch firmware, boot ROM of Bridge IC and other firmwares (CPLD and VRs) are programmable from out-of-band connectivity by the Bridge IC and BMC.

#### 4 License

#### © 2019 Facebook.

As of July 26, 2016, the following persons or entities have made this Specification available under the Open Compute Project Hardware License (Permissive) Version 1.0 (OCPHL-P), which is available at <a href="http://www.opencompute.org/.../spec-submission-process/">http://www.opencompute.org/.../spec-submission-process/</a>.

Facebook, Inc.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The Specification implementer and user assume the entire risk as to implementing or otherwise using the Specification. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE."

## 5 Mechanical Design

#### 5.1 Mechanical Outline

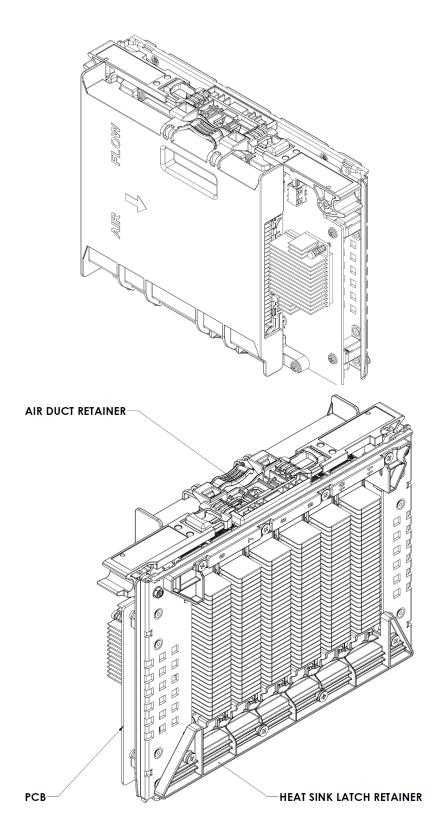

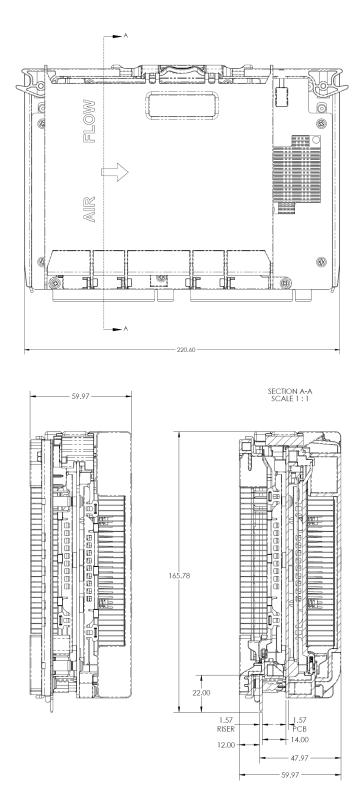

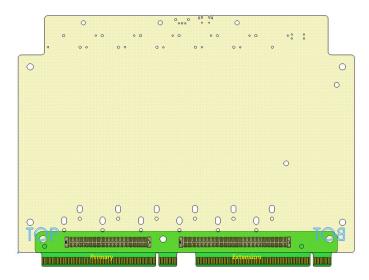

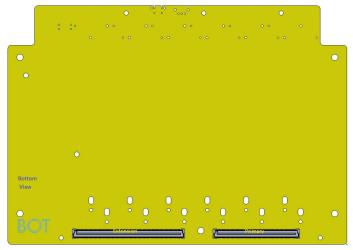

The Glacier Point V2 card uses a riser card adapter with dual PCIe edge connector which is connected to the M.2 PCB by mezzanine connectors. Spacers are used to control the distance between PCBs.

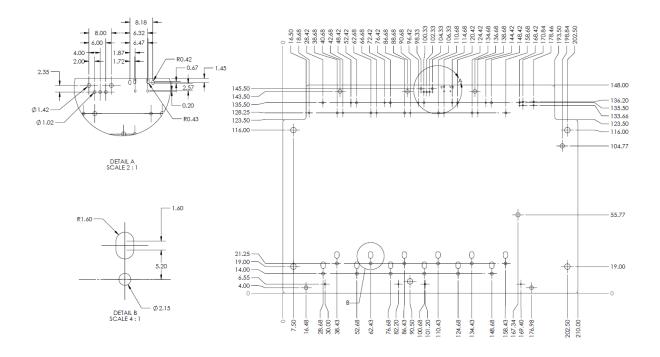

The overall dimensions of the general card are 210 x 148mm (excluding the riser). See Figure 5-1 for the specification drawing including keep-out zones and component restrictions.

Figure 5-1 Glacier Point V2 PCB Mechanical Drawing

The PCB is mounted to a sheet metal carrier which includes flanges on each perpendicular edge that engage the card guides in the chassis. There are no card guide keep-outs on the PCB edge since all available space is needed for traces and components. The card guide engages the sheet metal flanges instead of the PCB itself.

The carrier assembly includes 2x ejectors which are used for card injection/ejection into the PCle connectors. These ejectors rotate horizontally before being allowed to swing open, and they include finger access cutouts. One ejector claw engages a limit switch, which allows the BMC to detect if the ejector has been opened. The air duct rotates to open/close, one end fixed as the pivot point, the other end snaps into the retainer as a spring latch.

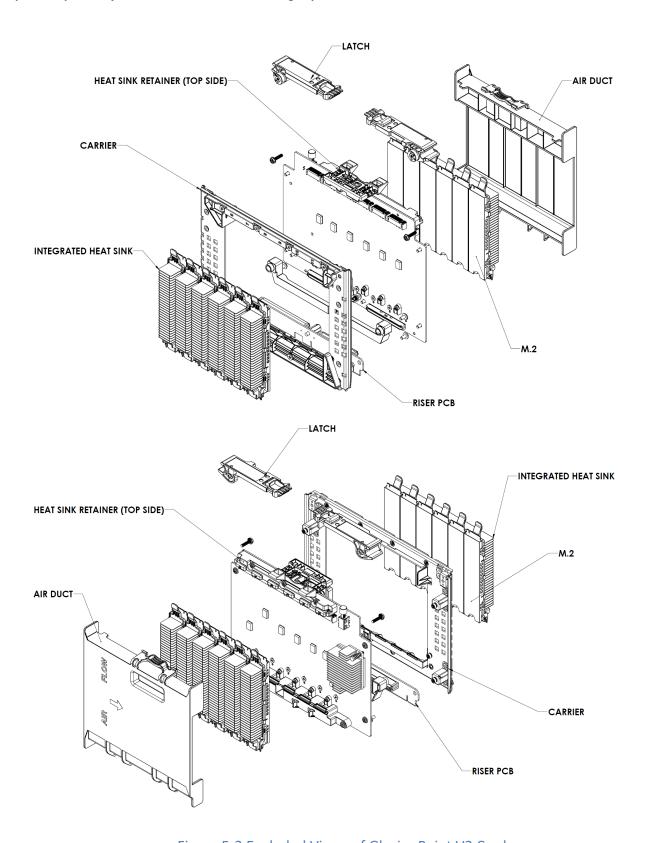

Figure 5-2 Glacier Point V2 Card Mechanical Overview

Figure 5-3 Exploded Views of Glacier Point V2 Card

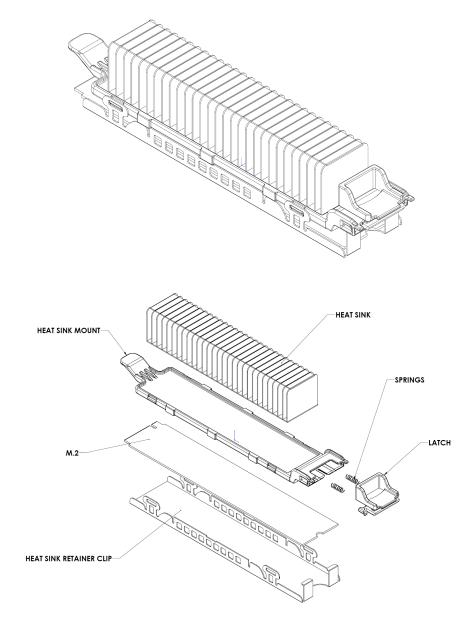

An integrated heat sink was designed for M.2 modules. The M.2 PCBA plus the heat sink forms a whole FRU to replace separate thermal pad plus heatsink design in GPv1 system. This design greatly improved thermal performance and serviceability.

Figure 5-4 Integrated Heat Sink M.2 Module Assembly

Figure 5-5 Glacier Point V2 Card Dimensions

The thickness of the PCB shall be 1.57±10% mm.

#### **5.2** PCIe Edge Connector

The key dimensions, edge chamfer, pad layout (including a shorter pad for PRSNT# signal), placement, and dimensions of the card edge connector match the PCI Express Card electromechanical specification.

The GND planes underneath the pads for the card's edge connector must be recessed according to the PCI Express Card electromechanical specification to improve signal integrity.

#### 5.3 Platform Design

Platform design details are not discussed in this specification.

## 6 Thermal Design

#### 6.1 Data Center Environmental Conditions

This section outlines Facebook data center operational conditions.

#### **6.1.1** Location of Data Center/Altitude

Maximum altitude is 6,000 ft above sea level. Any variation of air properties or environmental difference due to the high altitude needs to be deliberated into the thermal design.

#### 6.1.2 Cold-Aisle Temperature

Data centers generally maintain cold aisle temperatures between 18°C and 30°C (65°F to 85°F). The mean temperature in the cold aisle is usually 25°C with 3°C standard deviation. The cold aisle temperature in a data center may fluctuate minutely depending to the outside air temperature. Every component must be cooled and must maintain a temperature below its maximum specification temperature in the cold aisle.

#### 6.1.3 Cold-Aisle Pressurization

Data centers generally maintain cold aisle pressure between 0 inches H2O and 0.005 inches H2O. The thermal solution of the system should consider the worst operational pressurization possible, which generally is 0 inches H2O and 0.005 inches H2O with a single fan (or rotor) failure.

#### **6.1.4** Relative Humidity

Data centers usually maintains a relative humidity between 20% and 90%.

#### **6.2 Server Operational Conditions**

#### 6.2.1 System Volumetric Flow

The unit of airflow (or volumetric flow) used for this spec is cubic feet per minute (CFM). The CFM can be used to determine the thermal expenditure or to calculate the

approximate Delta T of the system. The thermal expenditure is quantified by the metric CFM/W, which is calculated by the following formula:

Thermal Expenditure =

$$\frac{\text{System airflow}}{\text{Total system power consumption, including fans}}$$

[CFM/W]

The required airflow is 0.115 airflow per watt in the system level at sea level. The desired airflow per watt is 0.1 or lower up to 35°C (113°F) ambient temperature at sea level.

#### 6.2.2 Thermal Margin

The thermal margin is the difference between the maximum theoretical safe temperature and the actual temperature. The board design operates at an inlet temperature of 35°C (95°F) outside of the system with a minimum 5% thermal margin for every component on the card.

#### 6.2.3 Upper Critical Threshold

The upper critical threshold (UCT) setting should allow the detection of abnormal thermal behaviors in the system. The UCT values for the sensors that are not used in Fan Speed Control (FSC) should use a 15% thermal margin from the worst experiment data. The UCT values for the sensors used in FSC, except for CPU, inlet, and outlet sensors, should use a 20% thermal margin from the worst experiment data.

#### 6.2.4 Thermal Testing

Thermal testing must be performed at a low inlet temperature 15°C (59°F) and up to 35°C (95°F) inlet temperature to guarantee the design is free of thermal defect and has high temperature reliability.

#### 6.3 M.2 Cooling Solution

Each card must support up to 12 M.2 or 6 dual M.2. Each M.2 or dual M.2 must have a thermal solution that capable of maintaining all components within their thermal spec with desired thermal margin. The thermal design must be thermally optimized design at the lowest cost. Passive cooling is required with a TIM (Thermal Interface Material) and heat sink. Integrated heat sink solution is desired for improved thermal efficiency and serviceability.

#### 6.3.1 M.2 and Dual M.2 connectors

All M.2s and dual M.2s should use 6.7mm height connectors to allow for airflow for top side and bottom side components.

#### 6.3.2 TIM Requirements

The TIM must be used between top side components and heatsink, and between bottom side components and heatsink retainer clip to fill the gap. The TIM should be soft and

compliant transferring low or no pressure between interfaces. The TIM must have a thermal conductivity of 3W/m-K or higher. A desired TIM bond-line thickness should be less or equal than 0.5mm for components with high power density.

#### 6.3.3 Heat Sink Requirements

Each M.2 or dual M.2 must have a heatsink that is integrated to the M.2 PCB board. The heatsink must be designed to help maintain temperatures of all major components on the M.2 or dual M.2 with desired thermal margin.

#### **6.4 Temperature and Power Sensors**

Each card must provide following sensors:

- Temperature sensors for M.2, Dual M.2, PCIe switch and ambient temperature.

- Power sensors for the SOC and the whole card

- Voltage sensors for all voltage rails

- One inlet ambient temperature sensor and one outlet ambient temperature sensor

The BMC on the platform must be able to read all these sensors via the Bridge IC. Additionally, over-temperature thresholds must be configurable and an alert mechanism must be provided to enable thermal shutdown and/or an increase in airflow. The sensors are accurate to +/-2°C and desired to be within 2% tolerance across whole operation temperature range. The goal sensor accuracy is +/-1°C.

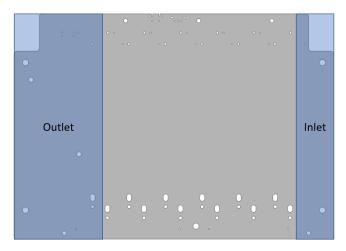

Two ambient temperature sensors are placed along the edges of the card on the B-side (the side without PCle switch). Figure 6-1 depicts the desired areas for ambient temperature sensor placement.

Figure 6-1 Ambient Temperature Sensor Placement Location (Circled Areas in Blue)

#### 6.5 Carrier Card Air Baffle:

The card level air baffle must be designed to help maintain temperatures of all major components on the carrier card by reducing bypass air and increasing airflow through key

components. The air baffle must be easy to service with the goal of requiring no tooling to remove. The air baffle must not have a large adverse effect on system level pressure drop.

## **Electrical Design**

#### 7.1 Primary X16 Edge Connector Pinout

The Glacier Point V2 contains two x16 standard PCIe connector, we defined them as primary and second side. The location of as defined in Figure 7-1 below. The PCIe connects sit on the riser card (green). The carrier card (yellow) has the mezzanine connector to riser card.

Figure 7-1 location of primary and extension connector of GPv2 Card

The definition of Edge Connector is based on Twin lake server card. Differences are the KR, NCSI and NIC SMBus interface are not connected in GPv2 design.

| Table7-1: Glacier Point V2 Primary X16 OCP Edge Connector A Pin-Out  Connector A Default Pin-Out |        |        |                     |  |  |

|--------------------------------------------------------------------------------------------------|--------|--------|---------------------|--|--|

| Pin Name                                                                                         | B Side | A Side | Pin Name            |  |  |

| P12V_CONN                                                                                        | B1     | A1     | FLASHCARD_PRSNT_N   |  |  |

| P12V_CONN                                                                                        | B2     | A2     | P12V_CONN           |  |  |

| P12V_CONN                                                                                        | В3     | A3     | P12V_CONN           |  |  |

| GND                                                                                              | B4     | A4     | GND                 |  |  |

| SMB_BMC_3V3SB_CLK_R                                                                              | B5     | A5     | CARD_TYPE_DETECTION |  |  |

| SMB_BMC_3V3SB_DAT_R                                                                              | В6     | A6     | P3V3_M2_EN_R        |  |  |

| GND                                                                                              | В7     | A7     | COM_GP_TX           |  |  |

| NC                                                                                               | B8     | A8     | COM_GP_RX           |  |  |

| NC                                                                                               | В9     | A9     | LATCH_DETECT        |  |  |

| NC                     | B10 | A10 | NC  |

|------------------------|-----|-----|-----|

| NC                     | B11 | A11 | NC  |

|                        |     |     |     |

| SMB_INA230_ALRT_N      | B12 | A12 | GND |

| GND                    | B13 | A13 | NC  |

| GND                    | B14 | A14 | NC  |

| NC                     | B15 | A15 | GND |

| NC                     | B16 | A16 | GND |

| GND                    | B17 | A17 | NC  |

| GND                    | B18 | A18 | NC  |

| NC                     | B19 | A19 | GND |

| NC                     | B20 | A20 | GND |

| GND                    | B21 | A21 | NC  |

| GND                    | B22 | A22 | NC  |

| NC                     | B23 | A23 | GND |

| NC                     | B24 | A24 | GND |

| GND                    | B25 | A25 | NC  |

| GND                    | B26 | A26 | NC  |

| NC                     | B27 | A27 | GND |

| NC                     | B28 | A28 | GND |

| GND                    | B29 | A29 | NC  |

| GND                    | B30 | A30 | NC  |

| NC                     | B31 | A31 | GND |

| NC                     | B32 | A32 | GND |

| GND                    | B33 | A33 | NC  |

| GND                    | B34 | A34 | NC  |

| CLK_100M_PE_DP         | B35 | A35 | GND |

| CLK_100M_PE_DN         | B36 | A36 | GND |

| GND                    | B37 | A37 | NC  |

| GND                    | B38 | A38 | NC  |

| RST_PE_SLOT1_1_RESET_N | B39 | A39 | GND |

| RST_PE_N_R             | B40 | A40 | GND |

| GND                    | B41 | A41 | NC  |

| GND                    | B42 | A42 | NC  |

| NC                     | B43 | A43 | GND |

| NC                     | B44 | A44 | GND |

| GND                    | B45 | A45 | NC  |

| GND            | B46 | A46 | NC             |

|----------------|-----|-----|----------------|

| NC             | B47 | A47 | GND            |

| NC             | B48 | A48 | GND            |

| GND            | B49 | A49 | P3E_A_TX_DP<0> |

| GND            | B50 | A50 | P3E_A_TX_DN<0> |

| P3E_A_RX_DP<0> | B51 | A51 | GND            |

| P3E_A_RX_DN<0> | B52 | A52 | GND            |

| GND            | B53 | A53 | P3E_A_TX_DP<1> |

| GND            | B54 | A54 | P3E_A_TX_DN<1> |

| P3E_A_RX_DP<1> | B55 | A55 | GND            |

| P3E_A_RX_DN<1> | B56 | A56 | GND            |

| GND            | B57 | A57 | P3E_A_TX_DP<2> |

| GND            | B58 | A58 | P3E_A_TX_DN<2> |

| P3E_A_RX_DP<2> | B59 | A59 | GND            |

| P3E_A_RX_DN<2> | B60 | A60 | GND            |

| GND            | B61 | A61 | P3E_A_TX_DP<3> |

| GND            | B62 | A62 | P3E_A_TX_DN<3> |

| P3E_A_RX_DP<3> | B63 | A63 | GND            |

| P3E_A_RX_DN<3> | B64 | A64 | GND            |

| GND            | B65 | A65 | P3E_B_TX_DP<0> |

| GND            | B66 | A66 | P3E_B_TX_DN<0> |

| P3E_B_RX_DP<0> | B67 | A67 | GND            |

| P3E_B_RX_DP<1> | B68 | A68 | GND            |

| GND            | B69 | A69 | P3E_B_TX_DP<1> |

| GND            | B70 | A70 | P3E_B_TX_DN<1> |

| P3E_B_RX_DN<0> | B71 | A71 | GND            |

| P3E_B_RX_DN<1> | B72 | A72 | GND            |

| GND            | B73 | A73 | P3E_B_TX_DP<2> |

| GND            | B74 | A74 | P3E_B_TX_DN<2> |

| P3E_B_RX_DP<2> | B75 | A75 | GND            |

| P3E_B_RX_DN<2> | B76 | A76 | GND            |

| GND            | B77 | A77 | P3E_B_TX_DP<3> |

| GND            | B78 | A78 | P3E_B_TX_DN<3> |

| P3E_B_RX_DP<3> | B79 | A79 | GND            |

| P3E_B_RX_DN<3> | B80 | A80 | GND            |

| GND            | B81 | A81 | P12V_CONN      |

| GND            | B82 | A82 | P12V_CONN      |

## 7.2 Extension X16 Edge Connector B

The Glacier Point V2 also implements an extension x16 edge connector to bring out additional x16 PCIe lanes. This extension X16 Edge connector is referred as Connector B.

Table 2: Glacier Point V2 Extension X16 OCP Edge Connector B Pin-Out

| Connector B Default Pin-Out |        |        |                     |  |  |

|-----------------------------|--------|--------|---------------------|--|--|

| Pin Name                    | B Side | A Side | Pin Name            |  |  |

| P12V_CONN                   | B1     | A1     | FLASHCARD_B_PRSNT_N |  |  |

| P12V_CONN                   | B2     | A2     | P12V_CONN           |  |  |

| P12V_CONN                   | В3     | А3     | P12V_CONN           |  |  |

| GND                         | B4     | A4     | GND                 |  |  |

| NC                          | B5     | A5     | NC                  |  |  |

| NC                          | В6     | A6     | NC                  |  |  |

| NC                          | В7     | A7     | NC                  |  |  |

| NC                          | B8     | A8     | GND                 |  |  |

| NC                          | В9     | A9     | NC                  |  |  |

| GND                         | B10    | A10    | NC                  |  |  |

| NC                          | B11    | A11    | GND                 |  |  |

|                             |        |        |                     |  |  |

| NC                          | B12    | A12    | GND                 |  |  |

| GND                         | B13    | A13    | RESERVED_USB+       |  |  |

| GND                         | B14    | A14    | RESERVED_USB-       |  |  |

| P3E_F_RX_DP<0>              | B15    | A15    | GND                 |  |  |

| P3E_F_RX_DN<0>              | B16    | A16    | GND                 |  |  |

| GND                         | B17    | A17    | P3E_F_TX_DP<0>      |  |  |

| GND                         | B18    | A18    | P3E_F_TX_DN<0>      |  |  |

| P3E_F_RX_DP<1>              | B19    | A19    | GND                 |  |  |

| P3E_F_RX_DN<1>              | B20    | A20    | GND                 |  |  |

| GND                         | B21    | A21    | P3E_F_TX_DP<1>      |  |  |

| GND                         | B22    | A22    | P3E_F_TX_DN<1>      |  |  |

| P3E_F_RX_DP<2>              | B23    | A23    | GND                 |  |  |

| P3E_F_RX_DN<2>              | B24    | A24    | GND                 |  |  |

| GND                         | B25    | A25    | P3E_F_TX_DP<2>      |  |  |

| GND                         | B26    | A26    | P3E_F_TX_DN<2>      |  |  |

| P3E_F_RX_DP<3>              | B27    | A27    | GND                 |  |  |

| P3E_F_RX_DN<3>              | B28    | A28    | GND                 |  |  |

| GND                         | B29    | A29    | P3E_F_TX_DP<3>      |  |  |

| GND                         | B30    | A30    | P3E_F_TX_DN<3>      |  |  |

| NC                          | B31    | A31    | GND                 |  |  |

| NC             | B32 | A32 | GND            |

|----------------|-----|-----|----------------|

| GND            | B33 | A33 | P3E_C_TX_DP<0> |

| GND            | B34 | A34 | P3E_C_TX_DN<0> |

| P3E_C_RX_DP<0> | B35 | A35 | GND            |

| P3E_C_RX_DN<0> | B36 | A36 | GND            |

| GND            | B37 | A37 | P3E_C_TX_DP<1> |

| GND            | B38 | A38 | P3E_C_TX_DN<1> |

| P3E_C_RX_DP<1> | B39 | A39 | GND            |

| P3E_C_RX_DN<1> | B40 | A40 | GND            |

| GND            | B41 | A41 | P3E_C_TX_DP<2> |

| GND            | B42 | A42 | P3E_C_TX_DN<2> |

| P3E_C_RX_DP<2> | B43 | A43 | GND            |

| P3E_C_RX_DN<2> | B44 | A44 | GND            |

| GND            | B45 | A45 | P3E_C_TX_DP<3> |

| GND            | B46 | A46 | P3E_C_TX_DN<3> |

| P3E_C_RX_DP<3> | B47 | A47 | GND            |

| P3E_C_RX_DN<3> | B48 | A48 | GND            |

| GND            | B49 | A49 | P3E_D_TX_DP<0> |

| GND            | B50 | A50 | P3E_D_TX_DN<0> |

| P3E_D_RX_DP<0> | B51 | A51 | GND            |

| P3E_D_RX_DN<0> | B52 | A52 | GND            |

| GND            | B53 | A53 | P3E_D_TX_DP<1> |

| GND            | B54 | A54 | P3E_D_TX_DN<1> |

| P3E_D_RX_DP<1> | B55 | A55 | GND            |

| P3E_D_RX_DN<1> | B56 | A56 | GND            |

| GND            | B57 | A57 | P3E_D_TX_DP<2> |

| GND            | B58 | A58 | P3E_D_TX_DN<2> |

| P3E_D_RX_DP<2> | B59 | A59 | GND            |

| P3E_D_RX_DN<2> | B60 | A60 | GND            |

| GND            | B61 | A61 | P3E_D_TX_DP<3> |

| GND            | B62 | A62 | P3E_D_TX_DN<3> |

| P3E_D_RX_DP<3> | B63 | A63 | GND            |

| P3E_D_RX_DN<3> | B64 | A64 | GND            |

| GND            | B65 | A65 | P3E_E_TX_DP<0> |

| GND            | B66 | A66 | P3E_E_TX_DN<0> |

| P3E_E_RX_DP<0> | B67 | A67 | GND            |

| P3E_E_RX_DN<0> | B68 | A68 | GND            |

| GND            | B69 | A69 | P3E_E_TX_DP<1> |

| GND            | B70 | A70 | P3E_E_TX_DN<1> |

| P3E_E_RX_DP<1> | B71 | A71 | GND            |

|----------------|-----|-----|----------------|

| P3E_E_RX_DN<1> | B72 | A72 | GND            |

| GND            | B73 | A73 | P3E_E_TX_DP<2> |

| GND            | B74 | A74 | P3E_E_TX_DN<2> |

| P3E_E_RX_DP<2> | B75 | A75 | GND            |

| P3E_E_RX_DN<2> | B76 | A76 | GND            |

| GND            | B77 | A77 | P3E_E_TX_DP<3> |

| GND            | B78 | A78 | P3E_E_TX_DN<3> |

| P3E_E_RX_DP<3> | B79 | A79 | GND            |

| P3E_E_RX_DN<3> | B80 | A80 | GND            |

| GND            | B81 | A81 | P12V_CONN      |

| NC             | B82 | A82 | P12V_CONN      |

## **7.3 Pinout Definitions**

Table 7-3 provides a detailed pin defition. In GPv2 card, the pin definition is very similar

Table 7-3: GPv2 Golden Finger Pin Definition

| Pin                 | Direction    | Required/<br>Configurable | Pin Definition                                                                                                                                                              |

|---------------------|--------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P12V_CONN           | Input        | Required                  | 12VAUX power from platform                                                                                                                                                  |

| SMB_BMC_3V3SB_CLK_R | Input/Output | Required                  | I <sup>2</sup> C clock signal. I <sup>2</sup> C is the primary sideband interface for server management functionality. 3.3VAUX signal. Pull-up is provided on the platform. |

| SMB_BMC_3V3SB_DAT_R | Input/Output | Required                  | I <sup>2</sup> C data signal. I <sup>2</sup> C is the primary sideband interface for server management functionality. 3.3VAUX signal. Pull-up is provided on the platform.  |

| SMB_INA230_ALRT_N   | Output       | Required                  | I <sup>2</sup> C alert signal. Alerts the BMC that an event has occurred that needs to be processed. 3.3VAUX signal. Pullup is provided on the platform.                    |

| FLASHCARD_PRSNT_N   | Output       | Required                  | Present signal. This is pulled low on the card to indicate that a card is installed. 3.3VAUX signal. Pull-up is provided on the platform.                                   |

| FLASHCARD_B_PRSNT_N               | Output | Required | Extension edge connector Present signal. This is pulled low on the card to indicate that a card is installed. 3.3VAUX signal. Pull-up is provided on the platform.                                                                                                                                                                                     |

|-----------------------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COM_GP_TX                         | Output | Required | Serial transmit signal. Data is sent from the 1S Server module to the BMC. 3.3VAUX signal.                                                                                                                                                                                                                                                             |

| COM_GP_RX                         | Input  | Required | Serial receive signal. Data is sent from the BMC to the 1S Server module. 3.3VAUX signal.                                                                                                                                                                                                                                                              |

| CARD_TYPE_DETECTION (GPIO0)       | Output | Required | CARD_TYPE is an output signal to inform platform that if this card is a server or a device. For a server, this pin should be tied to GND through a 10K resistor on the 1S server card.                                                                                                                                                                 |

| P3V3_M2_EN_R<br>(GPIO1)           | Input  | Required | It is an input signal from a 1S server to enable active power on GPv2 side. It is useful when 1S server is going through DC cycling or AC cycling but the server and devices are not in the same power domain. Active high, 3.3VAUX signal.                                                                                                            |

| LATCH_DETECT (GPIO2)              | Output | Required | LATCH_DETECT is an output signal to indicate if the 1S server is fully seated with ejector latch closed and ready for power on. Platform designer can use this signal to control the power to the 1S server and avoid surprise 1S server insertion/removal to/from a hot slot. Active low, 3.3VAUX signal, pull-up should be provided on the platform. |

| RST_PE_N_R                        | Input  | Required | PCIe reset signal. If a PCIe bus is connected, this signal provides the reset signal indicating the card VRs and clocks are stable when driven high to 3.3V.                                                                                                                                                                                           |

| P3E_A_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform.                                                                                                                                                                                     |

| P3E_A_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output | Required | PCle x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.                                                                                                                                                                                      |

| CLK_100M_PE_DP/DN                 | Input  | Required | PCIe reference clock. This signal may or may not be connected on the platform.                                                                                     |

|-----------------------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RST_PE_SLOT1_1_RESET_N            | Output | Required | YV2 UART buffer enable signal. If GPv2 has worked, this signal provides the enable signal for the UART MUX output to YV2 baseboard.                                |

| P3E_B_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

| P3E_B_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| P3E_C_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

| P3E_C_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| P3E_D_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

| P3E_D_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| P3E_E_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

| P3E_E_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| P3E_F_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput       | Required                  | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform.                     |

|-----------------------------------|--------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3E_F_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output       | Required                  | PCle x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.                      |

| RESERVED_USB+/-                   | Input/Output | Required                  | USB 2.0 differential pair.                                                                                                                                                             |

| GND                               | Input        | Required                  | GND from platform                                                                                                                                                                      |

| Pin                               | Direction    | Required/<br>Configurable | Pin Definition                                                                                                                                                                         |

| P12V_CONN                         | Input        | Required                  | 12VAUX power from platform                                                                                                                                                             |

| SMB_BMC_3V3SB_CLK_R               | Input/Output | Required                  | I <sup>2</sup> C clock signal. I <sup>2</sup> C is the primary sideband interface for server management functionality. 3.3VAUX signal. Pull-up is provided on the platform.            |

| SMB_BMC_3V3SB_DAT_R               | Input/Output | Required                  | I <sup>2</sup> C data signal. I <sup>2</sup> C is the primary sideband interface for server management functionality. 3.3VAUX signal. Pull-up is provided on the platform.             |

| SMB_INA230_ALRT_N                 | Output       | Required                  | I <sup>2</sup> C alert signal. Alerts the BMC that an event has occurred that needs to be processed. 3.3VAUX signal. Pullup is provided on the platform.                               |

| FLASHCARD_PRSNT_N                 | Output       | Required                  | Present signal. This is pulled low on the card to indicate that a card is installed. 3.3VAUX signal. Pull-up is provided on the platform.                                              |

| FLASHCARD_B_PRSNT_N               | Output       | Required                  | Extension edge connector Present signal. This is pulled low on the card to indicate that a card is installed. 3.3VAUX signal. Pull-up is provided on the platform.                     |

| COM_GP_TX                         | Output       | Required                  | Serial transmit signal. Data is sent from the 1S Server module to the BMC. 3.3VAUX signal.                                                                                             |

| COM_GP_RX                         | Input        | Required                  | Serial receive signal. Data is sent from the BMC to the 1S Server module. 3.3VAUX signal.                                                                                              |

| CARD_TYPE_DETECTION (GPIO0)       | Output       | Required                  | CARD_TYPE is an output signal to inform platform that if this card is a server or a device. For a server, this pin should be tied to GND through a 10K resistor on the 1S server card. |

| P3V3_M2_EN_R<br>(GPIO1)           | Input  | Required | It is an input signal from a 1S server to enable active power on GPv2 side. It is useful when 1S server is going through DC cycling or AC cycling but the server and devices are not in the same power domain. Active high, 3.3VAUX signal.                                                                                                            |

|-----------------------------------|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LATCH_DETECT<br>(GPIO2)           | Output | Required | LATCH_DETECT is an output signal to indicate if the 1S server is fully seated with ejector latch closed and ready for power on. Platform designer can use this signal to control the power to the 1S server and avoid surprise 1S server insertion/removal to/from a hot slot. Active low, 3.3VAUX signal, pull-up should be provided on the platform. |

| RST_PE_N_R                        | Input  | Required | PCIe reset signal. If a PCIe bus is connected, this signal provides the reset signal indicating the card VRs and clocks are stable when driven high to 3.3V.                                                                                                                                                                                           |

| P3E_A_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform.                                                                                                                                                                                     |

| P3E_A_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.                                                                                                                                                                                      |

| CLK_100M_PE_DP/DN                 | Input  | Required | PCIe reference clock. This signal may or may not be connected on the platform.                                                                                                                                                                                                                                                                         |

| RST_PE_SLOT1_1_RESET_N            | Output | Required | YV2 UART buffer enable signal. If GPv2 has worked, this signal provides the enable signal for the UART MUX output to YV2 baseboard.                                                                                                                                                                                                                    |

| P3E_B_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform.                                                                                                                                                                                     |

| P3E_B_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.                                                                                                                                                                                      |

| P3E_C_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput       | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

|-----------------------------------|--------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P3E_C_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output       | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| P3E_D_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput       | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

| P3E_D_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output       | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| P3E_E_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput       | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

| P3E_E_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output       | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| P3E_F_TX<br>_DP/DN<0>/<1>/<2>/<3> | lutput       | Required | PCIe x4 bus transmit signals. Data is sent from the 1S Server module(Twin Lakes) to the platform(GPv2). These signals may or may not be connected on the platform. |

| P3E_F_RX<br>_DP/DN<0>/<1>/<2>/<3> | Output       | Required | PCIe x4 bus receive signals. Data is sent from the platform(GPv2) to the 1S Server module(Twin Lakes). These signals may or may not be connected on the platform.  |

| RESERVED_USB+/-                   | Input/Output | Required | USB 2.0 differential pair.                                                                                                                                         |

#### 7.4 GPv2 Riser Card Mezzanine Connector Pin Definition

To offset the GPv2 card to the middle for better thermal solution, GPv2 card is assembled with GPv2 riser card. The golder finger is on the GPv2 riser card. GPv2 carrier card is

connected with GPv2 riser card with two mezzanine connectors with 14mm stackup height. The location of two mezzanine connector is listed in the drawing below:

Figure 7-2 Location of mezzanine connector on GPv2 carrier board

Similar to the golden finger idea, we define mezzanine card with primary and extension one. It's pin definition is listed in Table 7-4:

Table 7-4a: GPv2 Carrier Card Mezzanine Connector Pin Definition (Primary)

| Primary-120 pin Mezzanine |     |     |                     |  |  |  |  |

|---------------------------|-----|-----|---------------------|--|--|--|--|

| Signal                    | Pin | Pin | Signal              |  |  |  |  |

| P12V_CONN                 | 2   | 1   | FLASHCARD_PRSNT_N   |  |  |  |  |

| P12V_CONN                 | 4   | 3   | P12V_CONN           |  |  |  |  |

| P12V_CONN                 | 6   | 5   | P12V_CONN           |  |  |  |  |

| P12V_CONN                 | 8   | 7   | P12V_CONN           |  |  |  |  |

| P12V_CONN                 | 10  | 9   | P12V_CONN           |  |  |  |  |

| P12V_CONN                 | 12  | 11  | P12V_CONN           |  |  |  |  |

| P12V_CONN                 | 14  | 13  | P12V_CONN           |  |  |  |  |

| NC                        | 16  | 15  | P12V_CONN           |  |  |  |  |

| NC                        | 18  | 17  | NC                  |  |  |  |  |

| NC                        | 20  | 19  | NC                  |  |  |  |  |

| GND                       | 22  | 21  | NC                  |  |  |  |  |

| GND                       | 24  | 23  | GND                 |  |  |  |  |

| GND                       | 26  | 25  | GND                 |  |  |  |  |

| SMB_BMC_3V3SB_CLK         | 28  | 27  | GND                 |  |  |  |  |

| SMB_BMC_3V3SB_DAT         | 30  | 29  | GND                 |  |  |  |  |

| SMB_INA230_ALRT_N         | 32  | 31  | GND                 |  |  |  |  |

| RST_PE_N                  | 34  | 33  | CARD_TYPE_DETECTION |  |  |  |  |

| GND                       | 36  | 35  | COM_GP_TX           |  |  |  |  |

| GND                       | 38  | 37  | COM_GP_RX           |  |  |  |  |

| SMB_M2_CLK          | 40  | 39  | GND               |

|---------------------|-----|-----|-------------------|

| SMB_M2_DAT          | 42  | 41  | GND               |

| GND                 | 44  | 43  | SMB_M2_ALERT_N    |

| GND                 | 46  | 45  | NC                |

| CLK_100M_PE_DP      | 48  | 47  | GND               |

| CLK_100M_PE_DN      | 50  | 49  | GND               |

| GND                 | 52  | 51  | P3V3_M2_EN        |

| GND                 | 54  | 53  | LATCH_DETECT      |

| P3E_2_PESW_RX0_C_DP | 56  | 55  | GND               |

| P3E_2_PESW_RXO_C_DN | 58  | 57  | GND               |

| GND                 | 60  | 59  | P3E_2_PESW_TX0_DP |

| GND                 | 62  | 61  | P3E_2_PESW_TX0_DN |

| P3E_2_PESW_RX1_C_DP | 64  | 63  | GND               |

| P3E_2_PESW_RX1_C_DN | 66  | 65  | GND               |

| GND                 | 68  | 67  | P3E_2_PESW_TX1_DN |

| GND                 | 70  | 69  | P3E_2_PESW_TX1_DP |

| P3E_2_PESW_RX2_C_DP | 72  | 71  | GND               |

| P3E_2_PESW_RX2_C_DN | 74  | 73  | GND               |

| GND                 | 76  | 75  | P3E_2_PESW_TX2_DP |

| GND                 | 78  | 77  | P3E_2_PESW_TX2_DN |

| P3E_2_PESW_RX3_C_DP | 80  | 79  | GND               |

| P3E_2_PESW_RX3_C_DN | 82  | 81  | GND               |

| GND                 | 84  | 83  | P3E_2_PESW_TX3_DP |

| GND                 | 86  | 85  | P3E_2_PESW_TX3_DN |

| P3E_1_PESW_RXO_C_DP | 88  | 87  | GND               |

| P3E_1_PESW_RX0_C_DN | 90  | 89  | GND               |

| GND                 | 92  | 91  | P3E_1_PESW_TXO_DP |

| GND                 | 94  | 93  | P3E_1_PESW_TX0_DN |

| P3E_1_PESW_RX1_C_DP | 96  | 95  | GND               |

| P3E_1_PESW_RX1_C_DN | 98  | 97  | GND               |

| GND                 | 100 | 99  | P3E_1_PESW_TX1_DP |

| GND                 | 102 | 101 | P3E_1_PESW_TX1_DN |

| P3E_1_PESW_RX2_C_DP | 104 | 103 | GND               |

| P3E_1_PESW_RX2_C_DN | 106 | 105 | GND               |

| GND                 | 108 | 107 | P3E_1_PESW_TX2_DP |

| GND                 | 110 | 109 | P3E_1_PESW_TX2_DN |

| P3E_1_PESW_RX3_C_DP | 112 | 111 | GND               |

| P3E_1_PESW_RX3_C_DN | 114 | 113 | GND               |

| GND                 | 116 | 115 | P3E_1_PESW_TX3_DP |

| GND | 118 | 117 | P3E_1_PESW_TX3_DN |

|-----|-----|-----|-------------------|

| NC  | 120 | 119 | GND               |

Table 7-4b: GPv2 Carrier Card Mezzanine Connector Pin Definition (Extension)

| Extension-160 pin Mezzanine  Extension-160 pin Mezzanine |     |     |                     |  |  |  |  |

|----------------------------------------------------------|-----|-----|---------------------|--|--|--|--|

| Signal                                                   | Pin | Pin | Signal              |  |  |  |  |

| P12V_CONN                                                | 2   | 1   | FLASHCARD_B_PRSNT_N |  |  |  |  |

| P12V_CONN                                                | 4   | 3   | P12V_CONN           |  |  |  |  |

| P12V_CONN                                                | 6   | 5   | P12V_CONN           |  |  |  |  |

| NC                                                       | 8   | 7   | P12V_CONN           |  |  |  |  |

| NC                                                       | 10  | 9   | NC                  |  |  |  |  |

| NC                                                       | 12  | 11  | NC                  |  |  |  |  |

| NC                                                       | 14  | 13  | NC                  |  |  |  |  |

| NC                                                       | 16  | 15  | NC                  |  |  |  |  |

| NC                                                       | 18  | 17  | NC                  |  |  |  |  |

| NC                                                       | 20  | 19  | NC                  |  |  |  |  |

| NC                                                       | 22  | 21  | NC                  |  |  |  |  |

| NC                                                       | 24  | 23  | GND                 |  |  |  |  |

| GND                                                      | 26  | 25  | RESERVED_USB+       |  |  |  |  |

| GND                                                      | 28  | 27  | RESERVED_USB-       |  |  |  |  |

| NC                                                       | 30  | 29  | GND                 |  |  |  |  |

| GND                                                      | 32  | 31  | P3E_6_PESW_TX0_DP   |  |  |  |  |

| GND                                                      | 34  | 33  | P3E_6_PESW_TX0_DN   |  |  |  |  |

| P3E_6_PESW_RXO_C_DP                                      | 36  | 35  | GND                 |  |  |  |  |

| P3E_6_PESW_RXO_C_DN                                      | 38  | 37  | GND                 |  |  |  |  |

| GND                                                      | 40  | 39  | P3E_6_PESW_TX1_DP   |  |  |  |  |

| GND                                                      | 42  | 41  | P3E_6_PESW_TX1_DN   |  |  |  |  |

| P3E_6_PESW_RX1_C_DP                                      | 44  | 43  | GND                 |  |  |  |  |

| P3E_6_PESW_RX1_C_DN                                      | 46  | 45  | GND                 |  |  |  |  |

| GND                                                      | 48  | 47  | P3E_6_PESW_TX2_DP   |  |  |  |  |

| GND                                                      | 50  | 49  | P3E_6_PESW_TX2_DN   |  |  |  |  |

| P3E_6_PESW_RX2_C_DP                                      | 52  | 51  | GND                 |  |  |  |  |

| P3E_6_PESW_RX2_C_DN                                      | 54  | 53  | GND                 |  |  |  |  |

| GND                                                      | 56  | 55  | P3E_6_PESW_TX3_DP   |  |  |  |  |

| GND                                                      | 58  | 57  | P3E_6_PESW_TX3_DN   |  |  |  |  |

| P3E_6_PESW_RX3_C_DP                                      | 60  | 59  | GND                 |  |  |  |  |

| P3E_6_PESW_RX3_C_DN                                      | 62  | 61  | GND                 |  |  |  |  |

| GND                                                      | 64  | 63  | P3E_3_PESW_TX0_DP   |  |  |  |  |

| GND                                                      | 66  | 65  | P3E_3_PESW_TX0_DN   |  |  |  |  |

| P3E_3_PESW_RXO_C_DP | 68  | 67  | GND               |

|---------------------|-----|-----|-------------------|

| P3E_3_PESW_RXO_C_DN | 70  | 69  | GND               |

| GND                 | 72  | 71  | P3E_3_PESW_TX1_DP |

| GND                 | 74  | 73  | P3E_3_PESW_TX1_DN |

| P3E_3_PESW_RX1_C_DP | 76  | 75  | GND               |

| P3E_3_PESW_RX1_C_DN | 78  | 77  | GND               |

| GND                 | 80  | 79  | P3E_3_PESW_TX2_DP |

| GND                 | 82  | 81  | P3E_3_PESW_TX2_DN |

| P3E_3_PESW_RX2_C_DP | 84  | 83  | GND               |

| P3E_3_PESW_RX2_C_DN | 86  | 85  | GND               |

| GND                 | 88  | 87  | P3E_3_PESW_TX3_DP |

| GND                 | 90  | 89  | P3E_3_PESW_TX3_DN |

| P3E_3_PESW_RX3_C_DP | 92  | 91  | GND               |

| P3E_3_PESW_RX3_C_DN | 94  | 93  | GND               |

| GND                 | 96  | 95  | P3E_4_PESW_TX0_DP |

| GND                 | 98  | 97  | P3E_4_PESW_TX0_DN |

| P3E_4_PESW_RXO_C_DP | 100 | 99  | GND               |

| P3E_4_PESW_RXO_C_DN | 102 | 101 | GND               |

| GND                 | 104 | 103 | P3E_4_PESW_TX1_DP |

| GND                 | 106 | 105 | P3E_4_PESW_TX1_DN |

| P3E_4_PESW_RX1_C_DP | 108 | 107 | GND               |

| P3E_4_PESW_RX1_C_DN | 110 | 109 | GND               |

| GND                 | 112 | 111 | P3E_4_PESW_TX2_DP |

| GND                 | 114 | 113 | P3E_4_PESW_TX2_DN |

| P3E_4_PESW_RX2_C_DP | 116 | 115 | GND               |

| P3E_4_PESW_RX2_C_DN | 118 | 117 | GND               |

| GND                 | 120 | 119 | P3E_4_PESW_TX3_DP |

| GND                 | 122 | 121 | P3E_4_PESW_TX3_DN |

| P3E_4_PESW_RX3_C_DP | 124 | 123 | GND               |

| P3E_4_PESW_RX3_C_DN | 126 | 125 | GND               |

| GND                 | 128 | 127 | P3E_5_PESW_TX0_DP |

| GND                 | 130 | 129 | P3E_5_PESW_TX0_DN |

| P3E_5_PESW_RXO_C_DP | 132 | 131 | GND               |

| P3E_5_PESW_RXO_C_DN | 134 | 133 | GND               |

| GND                 | 136 | 135 | P3E_5_PESW_TX1_DP |

| GND                 | 138 | 137 | P3E_5_PESW_TX1_DN |

| P3E_5_PESW_RX1_C_DP | 140 | 139 | GND               |

| P3E_5_PESW_RX1_C_DN | 142 | 141 | GND               |

| GND                 | 144 | 143 | P3E_5_PESW_TX2_DP |

| GND                 | 146 | 145 | P3E_5_PESW_TX2_DN |

|---------------------|-----|-----|-------------------|

| P3E_5_PESW_RX2_C_DP | 148 | 147 | GND               |

| P3E_5_PESW_RX2_C_DN | 150 | 149 | GND               |

| GND                 | 152 | 151 | P3E_5_PESW_TX3_DP |

| GND                 | 154 | 153 | P3E_5_PESW_TX3_DN |

| P3E_5_PESW_RX3_C_DP | 156 | 155 | GND               |

| P3E_5_PESW_RX3_C_DN | 158 | 157 | GND               |

| GND                 | 160 | 159 | NC                |

#### 7.5 M.2 Module Pin Definition

As we mentioned in the overview section, GPv2 card is designed to support accelerator applications to offload some specific workload from host CPU. M.2 form factor is suitable to enable high density deployment in system. It also provides the granuity so system design can deploy different kinds of accelerators in one system and it is easy to change. Last but not least, it is a industrial standard form factor with wide adoption in server system.

Of course, M.2 form factors has some restrictions. One is the debug capability which is critical to accelerators. We have defined the extra debug pins on the golder fingers using NC pins in M.2 standard. The details are listed in Table 7-5 and Table 7-6

Table 7-5: M.2 Accelerator Pin Table

| M.2 Module Golden Finger |     |     |        |  |  |  |  |

|--------------------------|-----|-----|--------|--|--|--|--|

| Signal                   | Pin | Pin | Signal |  |  |  |  |

| 3.3V                     | 2   | 1   | GND    |  |  |  |  |

| 3.3V                     | 4   | 3   | GND    |  |  |  |  |

| PWRDIS                   | 6   | 5   | PETn3  |  |  |  |  |

| PLN#                     | 8   | 7   | РЕТр3  |  |  |  |  |

| LED_1#(0)                | 10  | 9   | GND    |  |  |  |  |

| 3.3V                     | 12  | 11  | PERn3  |  |  |  |  |

| 3.3V                     | 14  | 13  | PERp3  |  |  |  |  |

| 3.3V                     | 16  | 15  | GND    |  |  |  |  |

| 3.3V                     | 18  | 17  | PETn2  |  |  |  |  |

| TRST                     | 20  | 19  | PETp2  |  |  |  |  |

| VIO_1V8                  | 22  | 21  | GND    |  |  |  |  |

| TDI                      | 24  | 23  | PERn2  |  |  |  |  |

| TDO                      | 26  | 25  | PERp2  |  |  |  |  |

| ТСК                      | 28  | 27  | GND    |  |  |  |  |

| PLA_S3#                  | 30  | 29  | PETn1  |  |  |  |  |

| GND                      | 32  | 31  | PETp1  |  |  |  |  |

| USB_D+                 | 34    | 33        | GND               |  |

|------------------------|-------|-----------|-------------------|--|

| USB_D-                 | 36    | 35        | PERn1             |  |

| GND                    | 38    | 37        | PERp1             |  |

| SMB CLK (I/O)(0/1.8V)  | 40    | 39        | GND               |  |

| SMB DATA (I/O)(0/1.8V) | 42    | 41        | PETn0             |  |

| ALERT# (O)(0/1.8V)     | 44    | 43        | РЕТр0             |  |

| Reserved_UART_Rx       | 46    | 45        | GND               |  |

| Reserved_UART_Tx       | 48    | 47        | PERn0             |  |

| PERST# (I)(0/3.3V)     | 50    | 49        | PERp0             |  |

| CLKREQ# (I/O)(0/3.3V)  | 52    | 51        | GND               |  |

| PEWAKE#(I/O)(0/3.3V)   | 54    | 53        | REFCLKn           |  |

| Reserved for MFG DATA  | 56    | 55        | REFCLKp           |  |

| Reserved for MFG CLOCK | 58    | 57        | GND               |  |

| ADD IN CARD KEY M      |       |           | ADD IN CARD KEY M |  |

| ADD IN CARD KEY M      |       |           | ADD IN CARD KEY M |  |

| ADD IN CARD KEY M      |       |           | ADD IN CARD KEY M |  |

| ADD IN CARD KEY M      |       |           | ADD IN CARD KEY M |  |

| NC                     | 68    | 67        | TMS               |  |

| 3.3V                   | 70    | 69        | NC                |  |

| 3.3V                   | 72    | 72 71 GND |                   |  |

| 3.3V                   | 74 73 |           | VIO_CFG_GND       |  |

|                        |       | 75        | GND               |  |

Table 7-6 M.2 Accelerator Pin Definition

| Interface | Signal Name  | 1/0 | Description                           | Volta<br>ge | FB Requirement   |

|-----------|--------------|-----|---------------------------------------|-------------|------------------|

| Power     | 3.3V(9 pins) | I   | 3.3V running power source             | 3.3V        | Required         |

| Ground    | GND(15 pins) |     | Ground                                | 0V          | Required         |

|           | VIO_1V8      | 1   | Reserved 1.8V running power           | 1.8V        | NC in module, FB |

|           |              |     | source for future PCI-SIG standard.   |             | platform leave   |

|           |              |     |                                       |             | this pin open.   |

| PCle      | PETp0/PETn0  | 0   | PCIe TX/RX Differential signals       |             | Required         |

|           | PETp1/PETn1  | 0   | defined by the PCIe 3.0/4.0           |             |                  |

|           | PETp2/PETn2  | 0   | specification. The Tx/Rx are defined  |             |                  |

|           | PETp3/PETn3  | 0   | on module perspective.                |             |                  |

|           | PERp0/PERn0  | 1   |                                       |             |                  |

|           | PERp1/PERn1  | 1   |                                       |             |                  |

|           | PERp2/PERn2  | 1   |                                       |             |                  |

|           | PERp3/PERn3  | 1   |                                       |             |                  |

|           | REFCLKp/REFC | 1   | PCIe Reference Clock signals (100     |             | Required         |

|           | LKn          |     | MHz) defined by the PCIe 3.0/4.0      |             |                  |

|           |              |     | specification                         |             |                  |

|           | PERST#       | 1   | PE-Reset is a functional reset to the | 3.3V        | Required         |

|           |              |     | card as defined by the PCI Express    |             |                  |

|           |              |     | CEM Rev3.0                            |             |                  |

|                     | CLKREQ#                | 1/0 | Clock Request is a reference clock request signal as defined by the PCIe Mini CEM specification; Open Drain with pull up on Platform; Active Low; Also used by L1 PM Substates. | 3.3V | Optional. FB platform leave this pin open.         |

|---------------------|------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------------------------|

|                     | PEWAKE#                | I/O | Vendor do not need to support this feature                                                                                                                                      | 3.3V | Optional. FB platform leave this pin open.         |

| Specific<br>Signals | Reserved for MFG DATA  |     | Manufacturing Data line.                                                                                                                                                        |      | Optional. FB platform leave                        |

|                     | Reserved for MFG CLOCK |     | Manufacturing Clock line.                                                                                                                                                       |      | this pin open.                                     |

|                     | LED1# (O)              | 0   | LED pin                                                                                                                                                                         | 3.3V | Optional. FB platform leave this pin open.         |

|                     | ALERT#                 | 0   | Alert notification to master; Open Drain with pull up on Platform; Active Low.                                                                                                  | 1.8V | Required. Refer<br>to Sec 5.3 for<br>more details. |

|                     | SMB_CLK                | I/O | SMBus clock; Open Drain with pull up on Platform, slave on module                                                                                                               | 1.8V | Required                                           |

|                     | SMB_DATA               | I/O | SMBus DATA; Open Drain with pull up on Platform, slave on module                                                                                                                | 1.8V | Required                                           |

| USB                 | USB_D+                 | I/O | USB 2.0 bus reserved for future application.                                                                                                                                    | N/A  | NC in module, FB platform leave this pin open.     |

|                     | USB_D-                 | I/O | USB 2.0 bus reserved for future application, not required here.                                                                                                                 | N/A  | NC in module, FB platform leave this pin open.     |

| UART                | Reserved_UAR<br>T_RX   | I   | UART Receive Data connected to TXD on the Platform.                                                                                                                             | 1.8V | Required. Please refer section 5.3 for details.    |

|                     | Reserved_UAR<br>T_TX   | 0   | UART Transmit Data connected to RXD on the Platform.                                                                                                                            | 1.8V | Required. Please refer section 5.3 for details.    |

| JTAG                | TDI                    | 1   | Refer to JTAG Specification (IEEE                                                                                                                                               | 1.8V | Required. Please                                   |

|                     | TDO                    | 0   | 1149.1), Test Access Port and                                                                                                                                                   | 1.8V | refer section 5.3                                  |

|                     | TCK                    | ı   | Boundary Scan Architecture for                                                                                                                                                  | 1.8V | for details.                                       |

|                     | TMS                    | ı   | definition.                                                                                                                                                                     | 1.8V |                                                    |

|                     | TRST                   | 1   |                                                                                                                                                                                 | 1.8V |                                                    |

| Reserved<br>New IOs | PWRDIS                 | I   | Reserved for power disable pin.<br>High: disable power on module. This<br>pin shall be NC on module.                                                                            | 3.3V | FB platform does not support these features.       |

|                     | PLN#                   | I   | Reserved for Power Loss notification. NC in module.                                                                                                                             | 3.3V |                                                    |

|                     | PLA_S3#                | 0   | Reserved for Power loss Assert. NC in module.                                                                                                                                   | 3.3V |                                                    |

|                     | VIO_CFG_GND            | 0   | Reserved for IO configure pin.<br>Connected to ground in module.                                                                                                                | 0V   |                                                    |

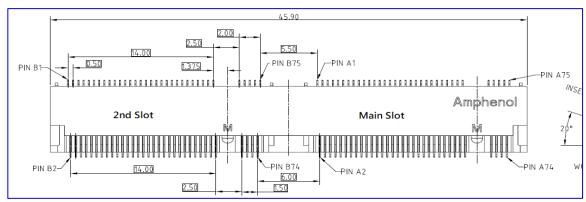

#### 7.6 Dual M.2 Module Support

Still M.2 has pretty tight landing footprint and power restrictions which does not match accelerator application. To mitigate those limitations, we proposed Dual M.2 form factor. Dual M.2 form factor is the combination of two sets of M.2 22110 Socket 3 key M Pin Definition. FB defined this form factor to support more power and bigger ASIC chips for specific work loads. We have defined main slot and second slot in this form factor. the main slot has the full set and the 2<sup>nd</sup> slot just provide additional power and ground pins. In this version each Dual M.2 card shall support 8 PCIE lanes.

Figure 7-5. Dual M.2 Connector Drawing

The Dual-M.2 module need a specified connector to have better pin position control. The drawing of that connector is shown in Figure 7-5. This connector is backward compatible. You can plug in two standard M.2 module in this connector without any problem.

In Dual M.2 module, Main slot provides PCIe lane0-3, power, ground and all the sideband IOs, second slot provides PCIe lane4-7, power and ground only. The details of pin definition is the same as M.2 module. Dual M.2 module support x8 port as default and can fail over to x4 port Main slot if the host does not provide that many lanes. You can find more details about electrical and mechanical defintion of Dual M.2 form factor in Dual M.2 Accelerator Specification.

Table 7-7 Dual M.2 Accelerator Pin Definition

| Dual M.2               |     |     |                   |  |                   |     |     |                   |

|------------------------|-----|-----|-------------------|--|-------------------|-----|-----|-------------------|

| Main Slot (SlotA)      |     |     |                   |  | 2nd Slot (SlotB)  |     |     |                   |

| Signal                 | Pin | Pin | Signal            |  | Signal            | Pin | Pin | Signal            |

| 3.3V                   | A2  | A1  | GND               |  | 3.3V              | B2  | B1  | GND               |

| 3.3V                   | A4  | А3  | GND               |  | 3.3V              | B4  | B3  | GND               |

| PWRDIS                 | A6  | A5  | PETn3             |  | NC                | B6  | B5  | PETn7             |

| PLN#                   | A8  | A7  | PETp3             |  | NC                | B8  | B7  | PETp7             |

| LED_1#(0)              | A10 | A9  | GND               |  | NC                | B10 | B9  | GND               |

| 3.3V                   | A12 | A11 | PERn3             |  | 3.3V              | B12 | B11 | PERn7             |

| 3.3V                   | A14 | A13 | PERp3             |  | 3.3V              | B14 | B13 | PERp7             |

| 3.3V                   | A16 | A15 | GND               |  | 3.3V              | B16 | B15 | GND               |

| 3.3V                   | A18 | A17 | PETn2             |  | 3.3V              | B18 | B17 | PETn6             |

| TRST                   | A20 | A19 | PETp2             |  | NC                | B20 | B19 | PETp6             |

| VIO_1V8                | A22 | A21 | GND               |  | GND               | B22 | B21 | GND               |

| TDI                    | A24 | A23 | PERn2             |  | NC                | B24 | B23 | PERn6             |

| TDO                    | A26 | A25 | PERp2             |  | NC                | B26 | B25 | PERp6             |

| TCK                    | A28 | A27 | GND               |  | GND               | B28 | B27 | GND               |