# Modular Hardware System-Common Redundant Power Supply (M-CRPS) Base Specification

Part of the Datacenter – Modular Hardware Systems (DC-MHS) Rev 1.0 Family

Version 1.00 Release Candidate 3

September 27th, 2022

### M-CRPS Authors/Contributors:

Advanced Micro Devices, Inc.: Paul Artman, Greg Sellman.

**Dell, Inc.:** Jon Lewis, John Jenne, Padmanabh Gharpure, Chris Peterson, Paul Waters, Matthew Dang, Eduardo Escamilla, Rob Bassman, Wayne Cook, Sean O'Donnell, Matthew B. Gilbert, James Utz, Thanh Dang, Daniece Carpenter, William Zuo, Tim Lambert, Jeff Kennedy.

Google LLC: Qiong Wang, Mike Branch, Siamak Tavallaei, Xin Li.

**Hewlett Packard Enterprise Corporation:** Amin Bemat, Mark Rivera, Pranay Mahendra, Arthur Volkmann, David Paquin, Evita Fang, James Yang, Glenn Lesmeister, Gavin Goodson.

**Intel Corporation:** Aurelio Rodriguez-Echevarria, Eric Bokman, Carlos G. Terriquez-Arias, Marco Beltman, Casey Winkel, Jeremy Young, William Susiene, Brian Aspnes, Todd Langley, Dirk Blevins, Javier Lasa.

Meta Platforms, Inc.: Ted Tang, Westhauser Todd.

Microsoft Corporation: Grant Hsu, Priya Raghu.

Note: For questions about this specification please contact Aurelio Rodriguez-Echevarria or Jon Lewis

# Revision history

| Date                                                    | Version      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         | 0.70         | Initial public release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

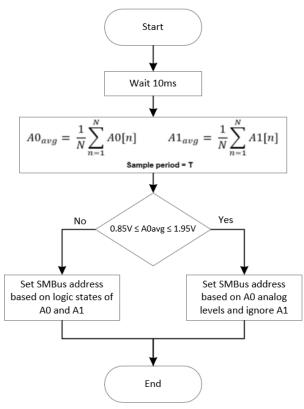

| April 15 <sup>th</sup> 2022  June 24 <sup>th</sup> 2022 | 0.70<br>0.75 | Section 9 Control and Indicator Functions – Fixed typos Section 9.6.1 A0 Input addressing – Updated Table 9-7 A0 input signal characteristics: changed pull-up from $470k\Omega$ to $47k\Omega$ . Section 9.6.1 A0 Input Addressing – Updated Figure 9 6 Flow diagram to detect between logic and analog SMBus addressing: updated decision-making block Section 9.6.1 A0 Input Addressing – Updated Table 9-10: updated resistor values. Section 12.7.1 Physical Layer – Updated Figure 12-16 Section 12.7.1 Physical Layer – Updated Figure 12-17 Section 3 Thermal Requirements – Updated entire section Section 14 Regulatory & Ecology Requirements – Updated entire section Section 2.3 LED Marking and Identification – Updated Table 2-1 LED Characteristics and table notes. Section 5.3.2. Input Voltage Specification – Updated Table 5-12 -48VDC power supply Input voltage range. Section 7.1 Output Power/Currents – Added 54VDC output option in Table 7-1 Section 7.1 Peak Load Protection – Updated Table 7-2 Peak load protection testing conditions Section 7.1 Voltage Regulation – Added 54VDC output option in Table 7-3 Voltage regulation limits Section 7.5 Dynamic Loading – Added 54VDC output option in Table 7-4 Transient Load requirements.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

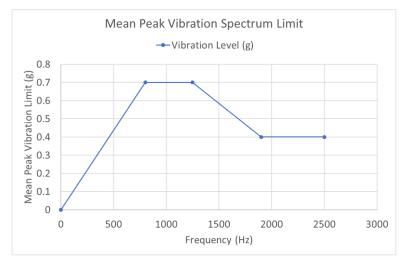

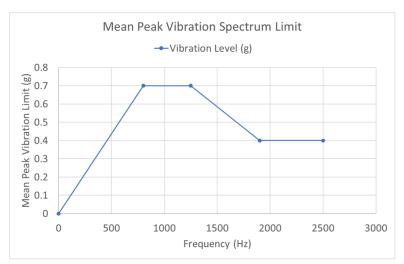

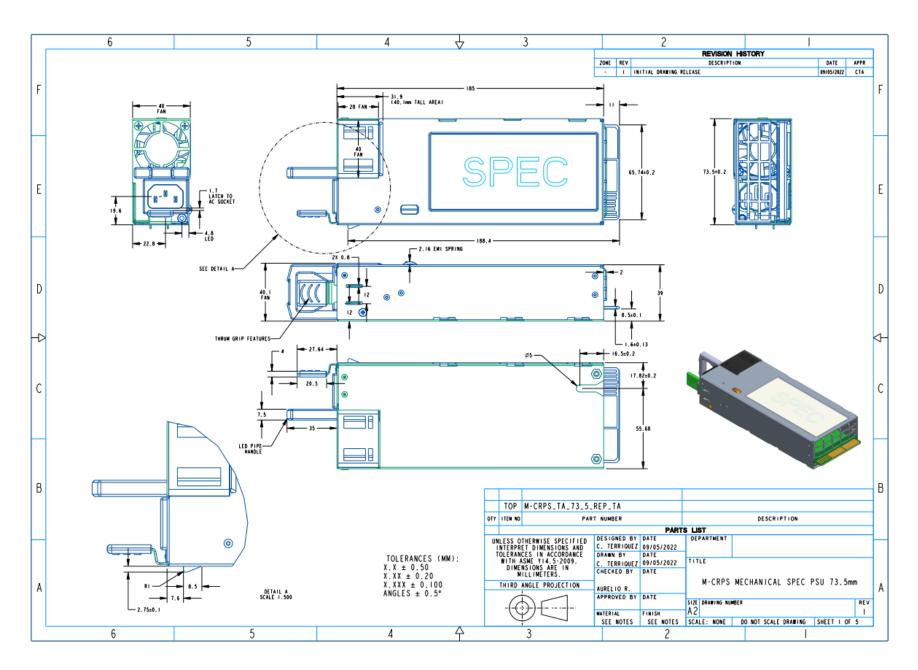

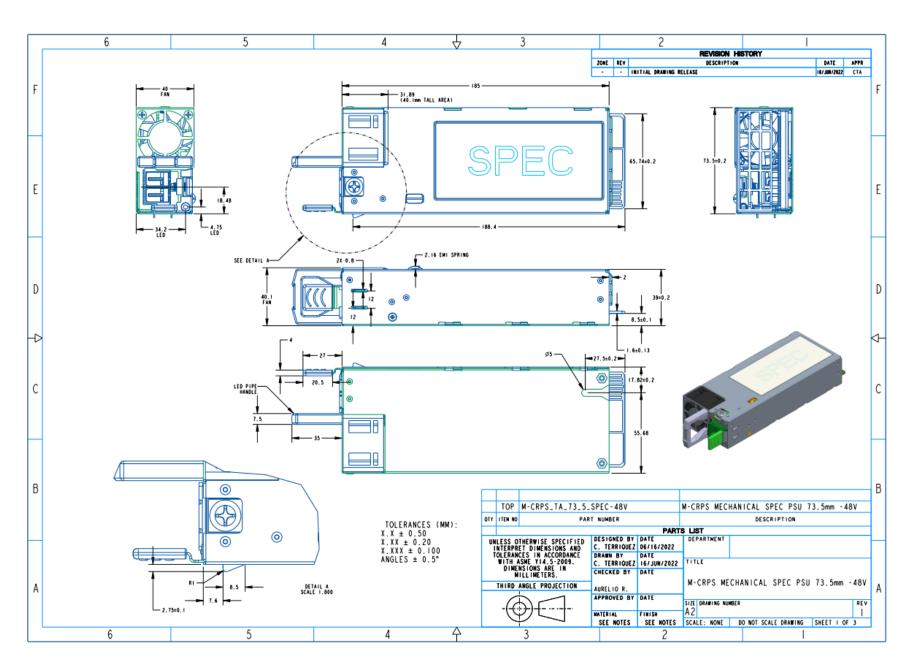

|                                                         |              | 7.6 Capacitive Loading – Added 54VDC output option in Table 7-6 Capacitive loading conditions 7.8 Closed Loop Stability – Updated paragraph Section 8.1.8 Under Voltage Protection - Added subsection Supplemental Material K. 185mm by 73.5mm -48VDC input M-CRPS mechanical drawing – Added drawing. Supplemental Material M, Reference Distorted Waveforms – Added section Section 4.1 Acoustics Requirements – Updated section. Section 4.2.9.1 Continuous Fan Speed Sweep – Updated Figure 4-6 Plot of mean peak vibration spectrum limit. Section 13.1 Component De-Rating – Deleted link.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| August 23 <sup>rd</sup>                                 | 0.90         | Section 2.3 LED Marking and Identification – Updated Table 2-1 LED Characteristics and added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2022                                                    |              | Note 2.  Supplemental Material O Luminosity Measurements – Added section.  Section 3.3 Thermal Sensors – Change temperature sensor accuracy from ±1°C to ±2°C.  Section 2.1.1.2 277VAC/380VDC Input - Updated Figure 2-4 185mm by 73.5mm form factor with 277VAC/380VDC inlet connector.  Section 2.1.1.4 -48VDC Input (Telecom) – Updated Figure 2-6 185mm by 73.5mm form factor with -48VDC input connector.  Section 2.1.2.2 277VAC/380VDC Input – Updated Figure 2-9 185mm by 60mm form factor with 277VAC/380VDC inlet connector.  Section 2.1.2.4 -48VDC Input (Telecom) – Updated Figure 2-10 60mm form factor with -48VDC input connector.  Section 3.1 Temperature and Altitude Conditions – Added note 3 in Table 3-1 Power supply thermal test conditions.  Section 3.1 Temperature and Altitude Conditions – Added note 3 in Table 3-1 Power supply thermal test conditions.  Section 9.5 Imon Signal (Output) – In Table 9-5 Imon signal characteristics: Updated signal delay from <100ns to <2us. Updated sensitivity, now two options configurable via config file.  Added notes 2 and 3.  Section 332.6.1 185mm by 73.5mm Form Factor – Updated Table 2-3 73.5mm in width PSU pinout definition to reflect 54V output option and added note 6.  Section 5.2.2 Input Voltage Specification – Updated start up and power off voltages in Table 5-10 +54VDC input voltage specification.  Section 5.2.4 Inrush Current - Updated paragraph.  Section 5.2.8 Input Ripple Voltage - Updated paragraph.  Section 5.3.1 Inlet Connector - Added reference to Figure 2-20 -48VDC inlet connector example (Telecom).  Section 7.4 Voltage Regulation - Updated Table 7-4 Voltage regulation limits, added +54V output specifications, added more clarification to note 2 and added note 3. |

```

Section 7.5 Dynamic Loading - Updated Table 7-5 Transient load requirements.

```

Section 7.6 Capacitive Loading - Updated Table 7-7 Capacitive loading conditions.

Section 8.1.7 Over Voltage Protection (OVP) - Updated Table 8-4 Over Voltage Protection (OVP) Limits.

Section 8.1.8 Under Voltage Protection (UVP) - Updated Table 8-5 Under Voltage Protection (OVP) Limits.

Section 5.1.3 Input Voltage Specification - Added note 2 in Table 5-3 AC Input voltage ranges.

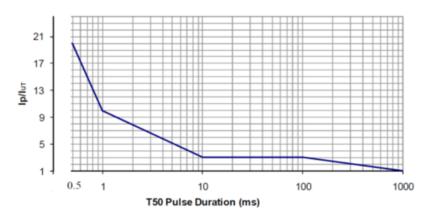

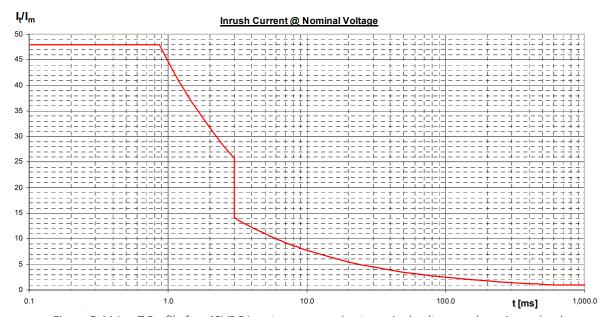

Section 5.1.7 Inrush Current - Updated secondary inrush event current in paragraph.

Section 5.3.7 Reversed Polarity Protection - Updated paragraph.

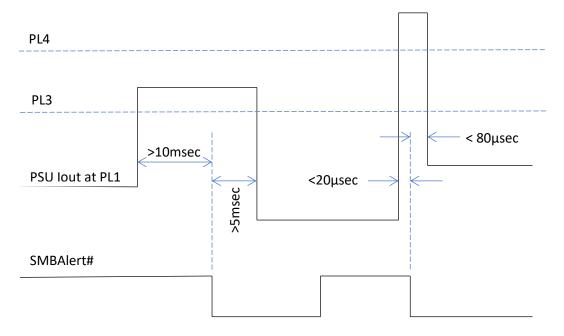

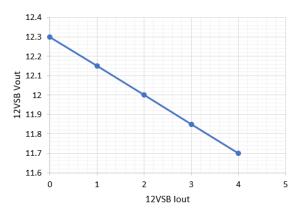

Section 7.3 Auxiliary (Stand-by) Output - Added droop share characteristics and figure.

Section 7.8 Closed Loop Stability - Updated Table 7-8 Phase and gain margin requirements and added note 2.

Section 7.13.7 Concurrent Maintenance - Updated second paragraph.

Section 7.13.9 Current Share Signal Characteristics - Updated Table 7-10 Current Share Signal Characteristics.

Section 7.14 Ripple/Noise - Updated Table 7-11 Ripple and noise.

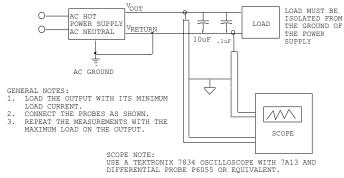

Section 7.14 Ripple/Noise - Added note to Figure 7-6 Differential noise test setup.

Section 7.15 Timing Requirements - Fixed typo in Table 7-12 Timing requirements (VINOK instead of VIONK).

Section 8.1.8 Under Voltage Protection (UVP) - Fixed typo.

Section 8.1.9 Over Temperature Warning (OTW) - Fixed typo in header.

Section 9.1.1 Two-State Signal - Updated Table 9-1 Two-state PSON# signal characteristics (3.3VSB pullup).

Section 9.2 PWOK Signal (Output) - Fixed typo in header (PWOK signal is active high not low). Section 9.2 PWOK Signal (Output) - Updated Table 9-2 PWOK signal characteristics (3.3VSB pullup).

Section 9.3 SMBAlert# Signal (Output) - Updated Table 9-3 SMBAlert# signal characteristics (3.3VSB pullup).

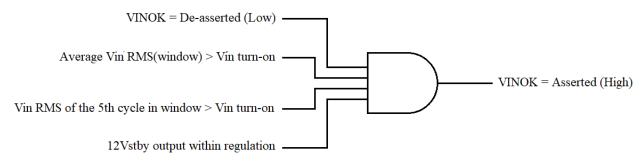

Section 9.4 VINOK Signal (Output) - Updated Table 9-4 VINOK Signal characteristics (3.3VSB pullup).

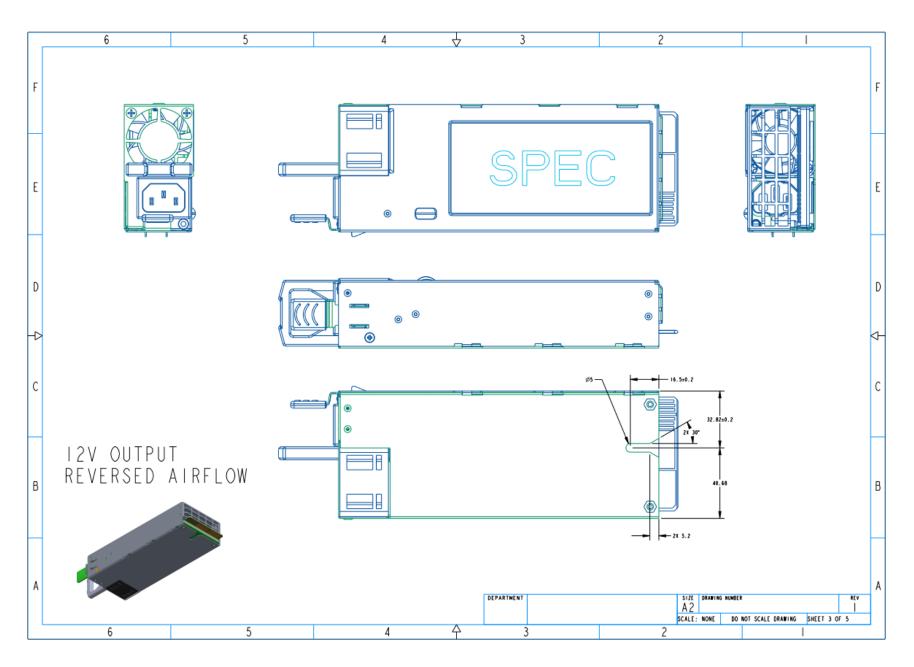

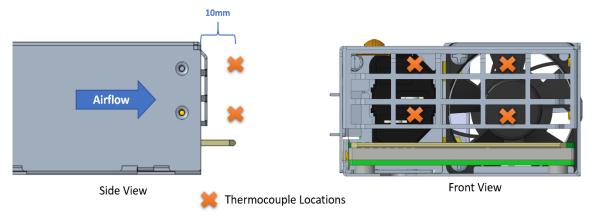

Supplemental Material P. Exhaust Temperature Measurement – Added Figures O-3 and O-4 for temperature measurement in reversed airflow power supplies.

Section 6.1.1.1 240VAC/240VDC and Wide Input Range - Updated efficiency at 100% loading condition from 91% to 92% in Table 6-1 Efficiency requirements for 240VAC/240VDC and wide input range power supplies.

Section 277VAC/380VDC Input – Updated efficiency at 100% loading condition from 91% to 92% in Table 6-2 Efficiency requirements for 277VAC/380VDC power supplies.

Section Data & Sideband Serialization Interface (DSSI) – Updated Figure 12-29 Physical layer and connections for point-to-point communication between Host and Client, Host bias will be updated on a later version.

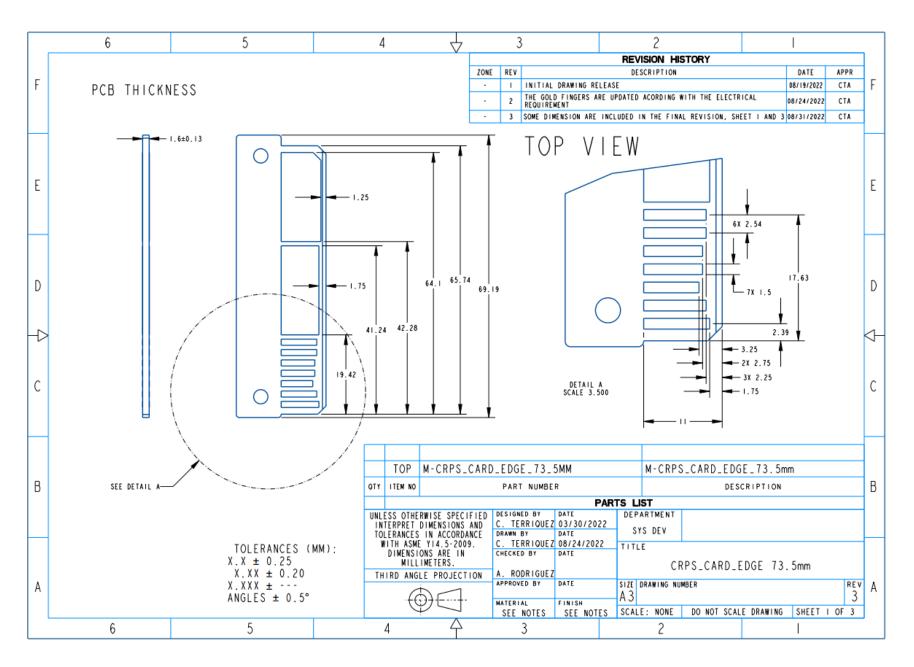

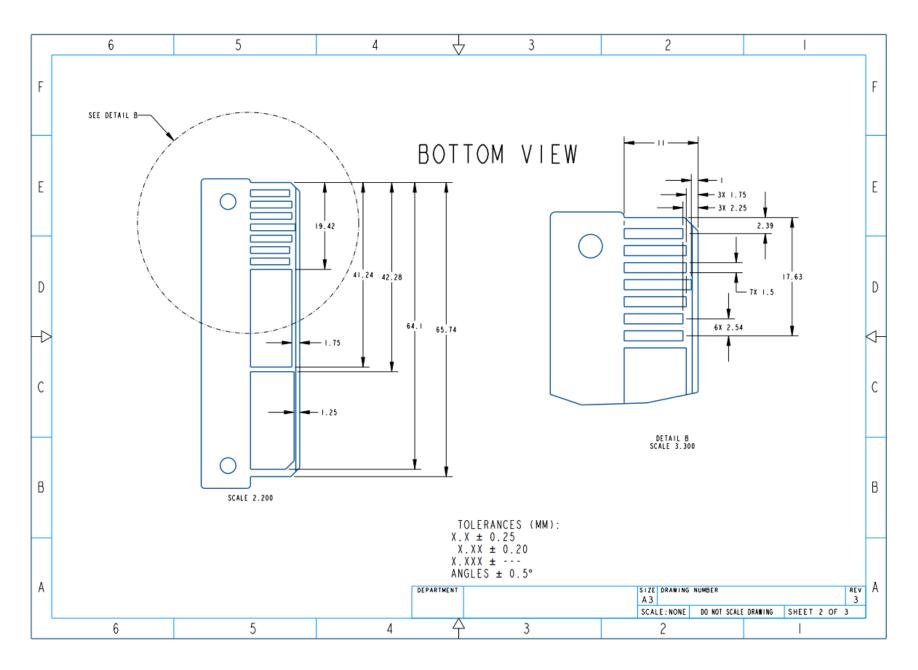

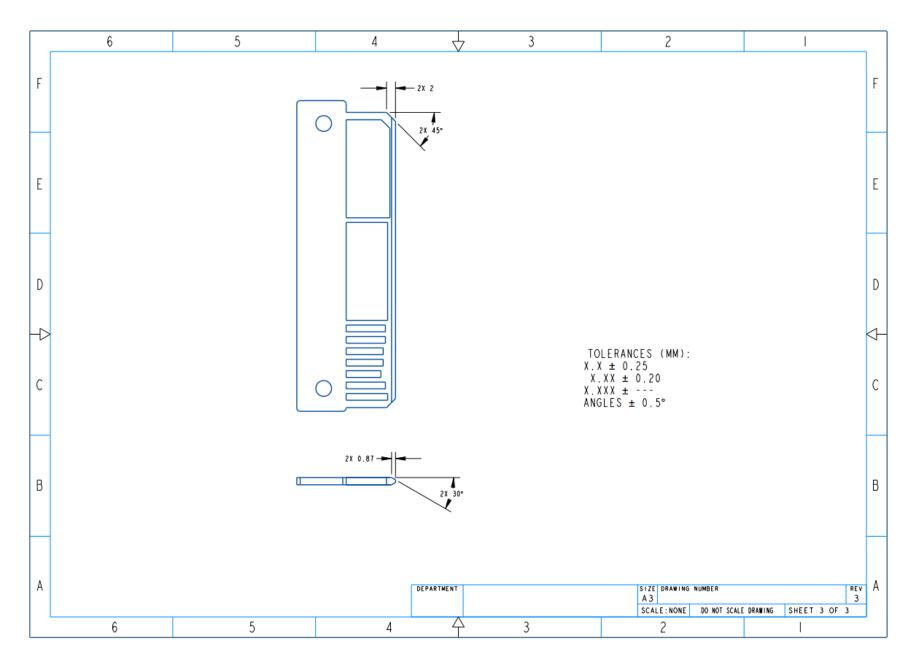

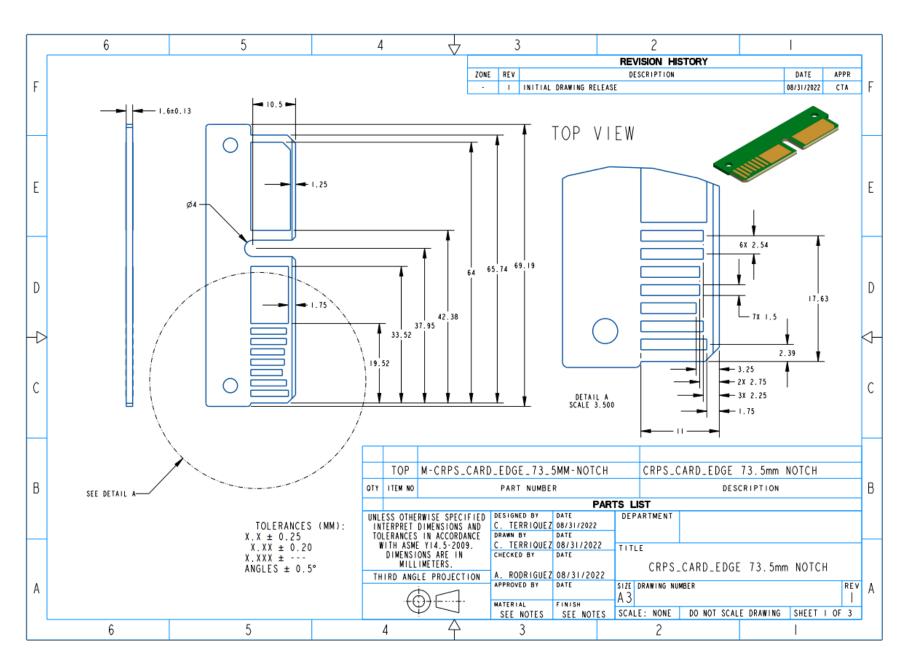

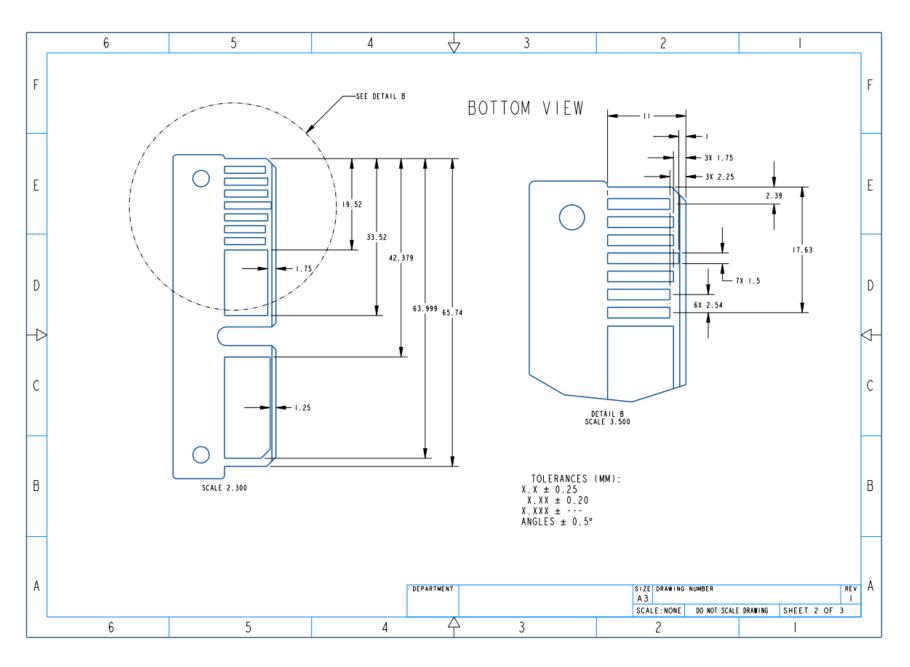

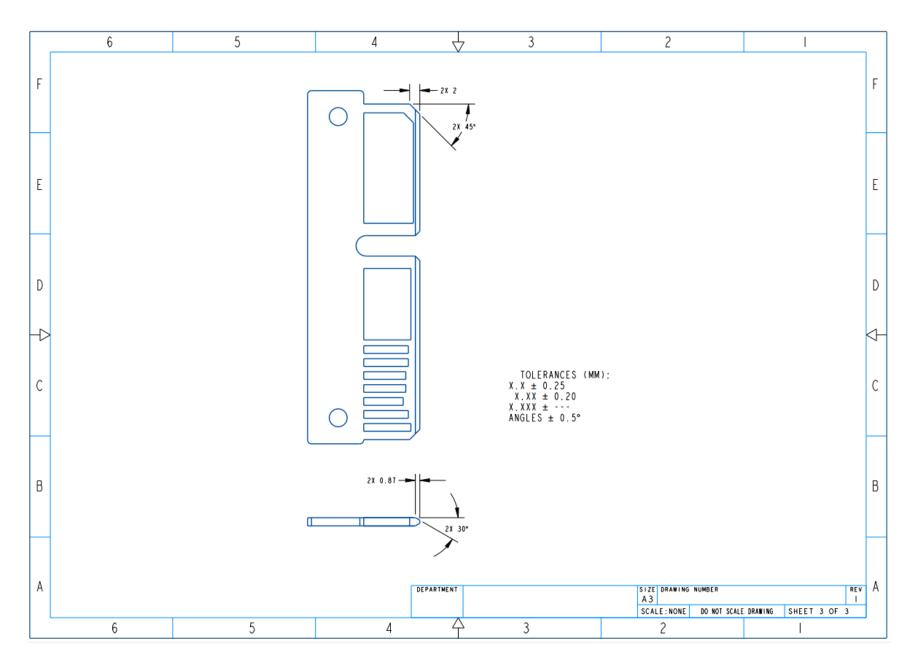

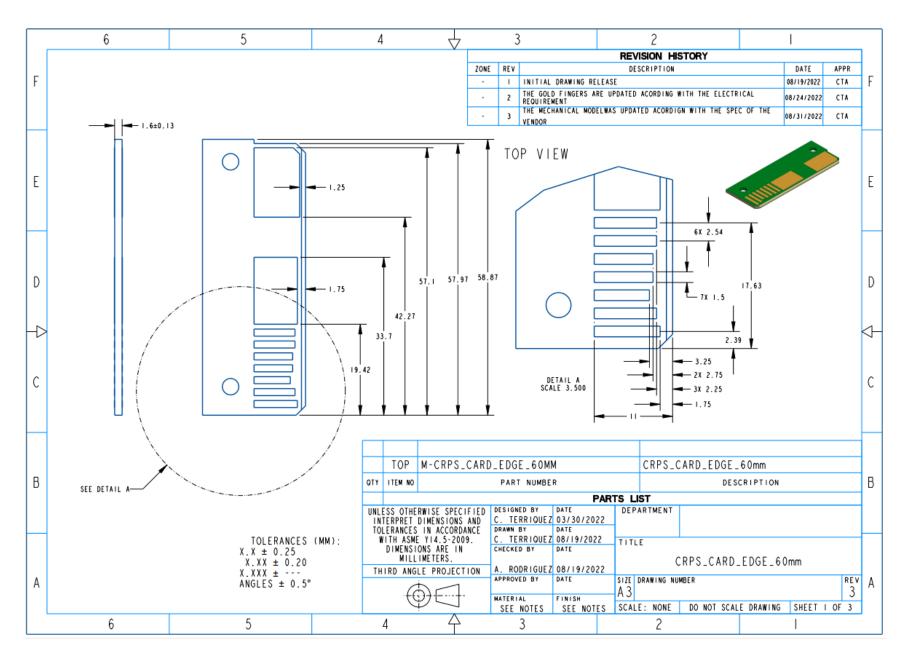

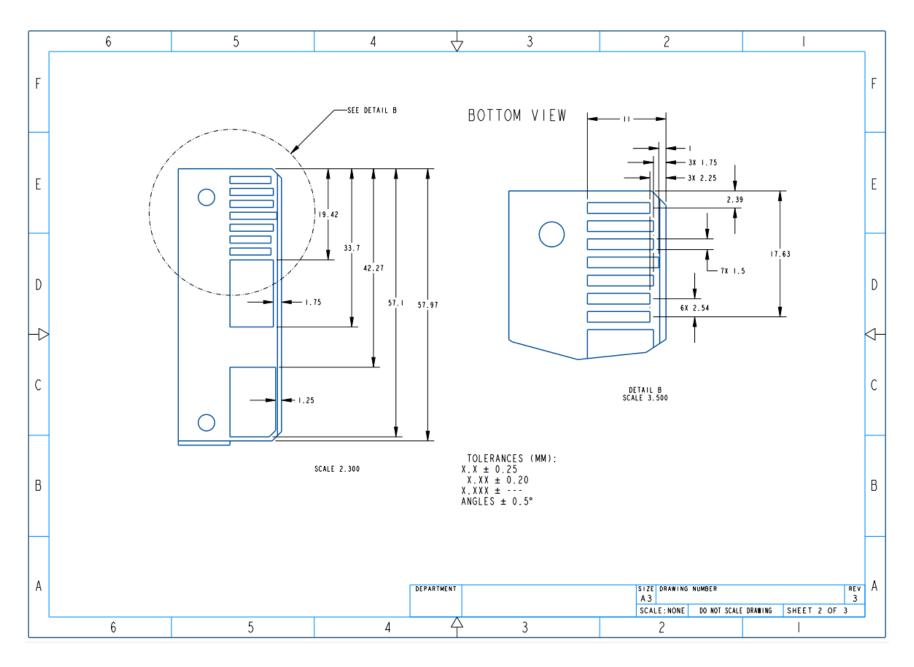

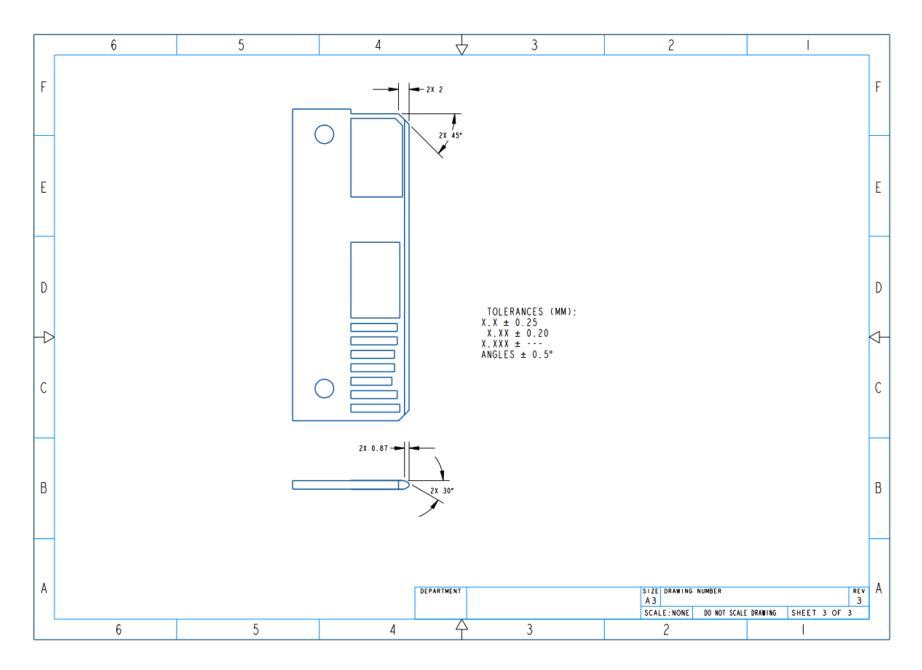

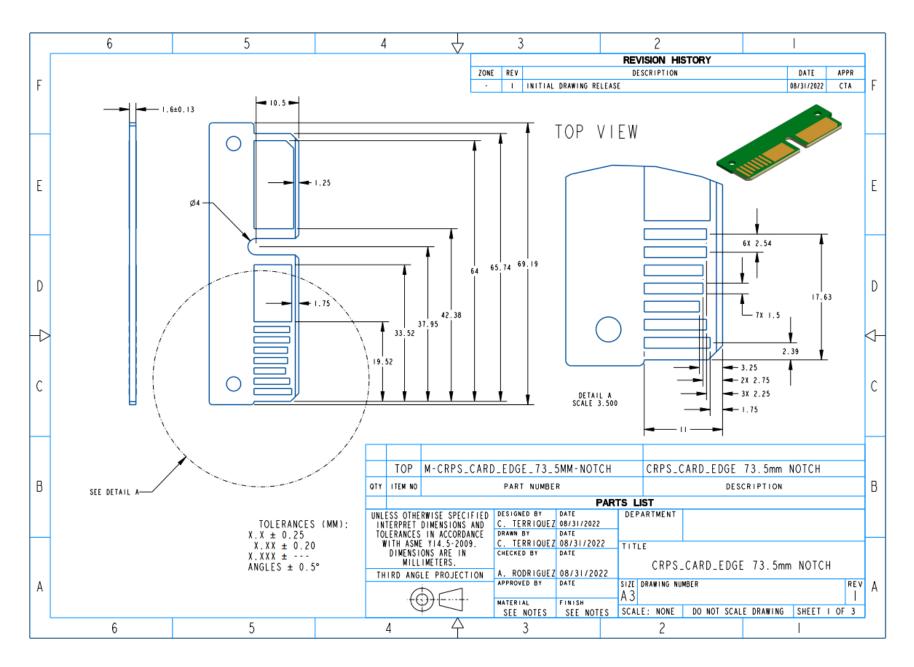

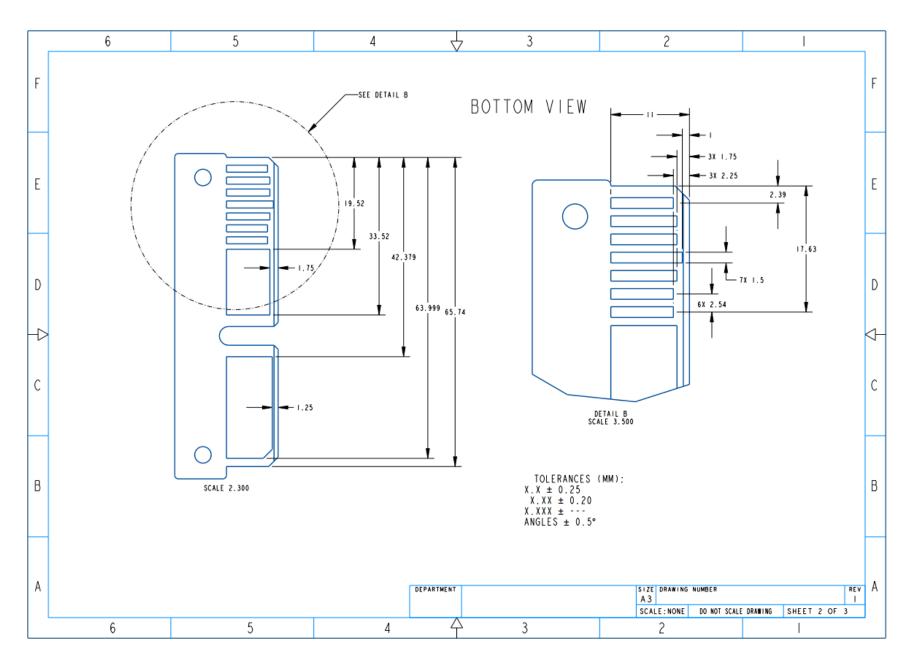

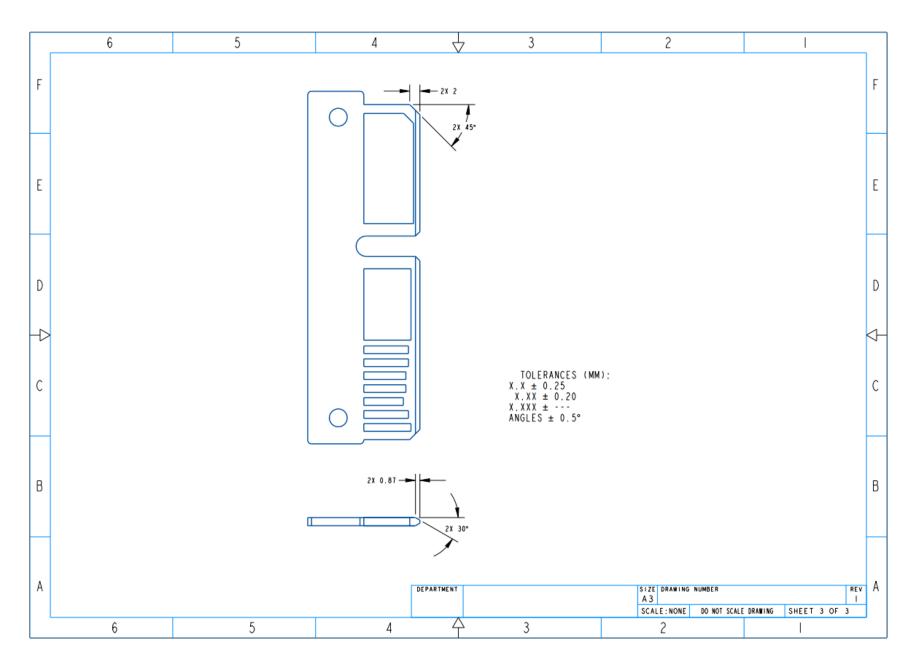

Supplemental Material D. 73.5mm in width M-CRPS card edge mechanical drawing – Updated drawing added chamfer details.

Supplemental Material E. 60mm in width M-CRPS card edge mechanical drawing – Updated drawing added chamfer details.

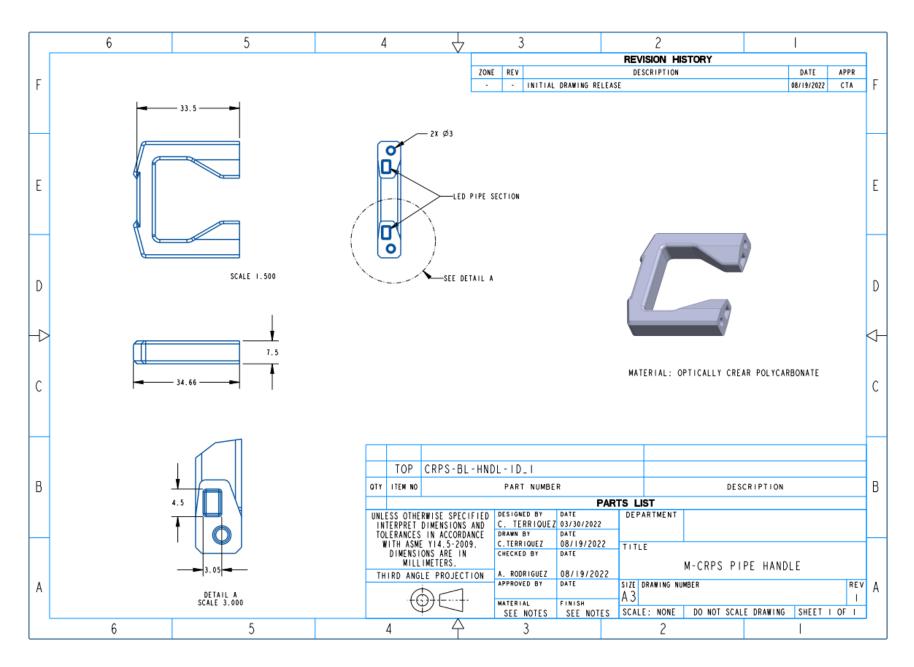

Supplemental Material F. M-CRPS handle mechanical drawing – Updated drawing added handle material.

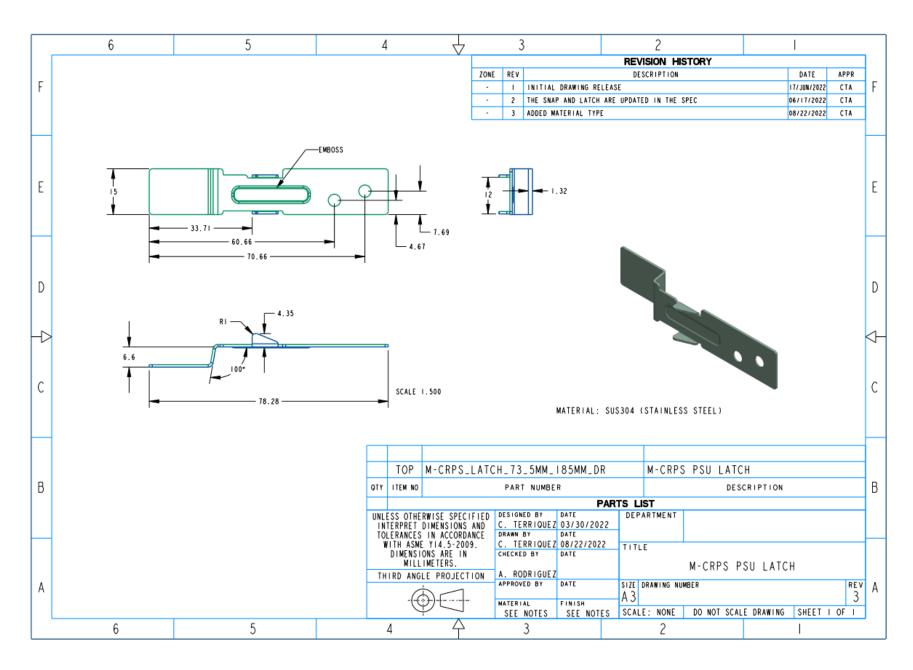

Supplemental Material G. M-CRPS latch mechanical drawing – Updated drawing added radii detail.

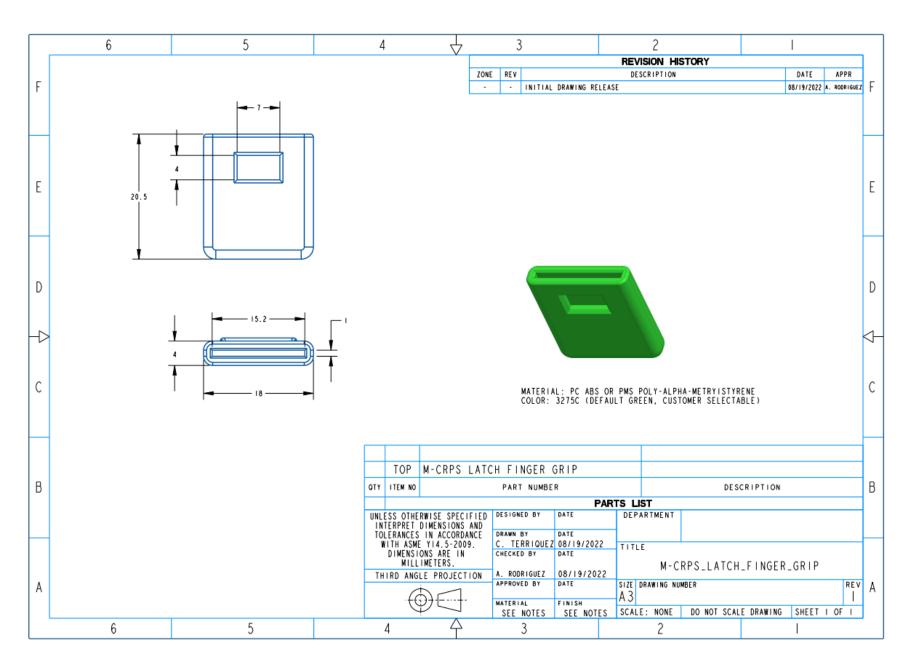

Supplemental Material H. M-CRPS latch plastic grip option 1 (snap-in version) – Updated drawing, added material and default color.

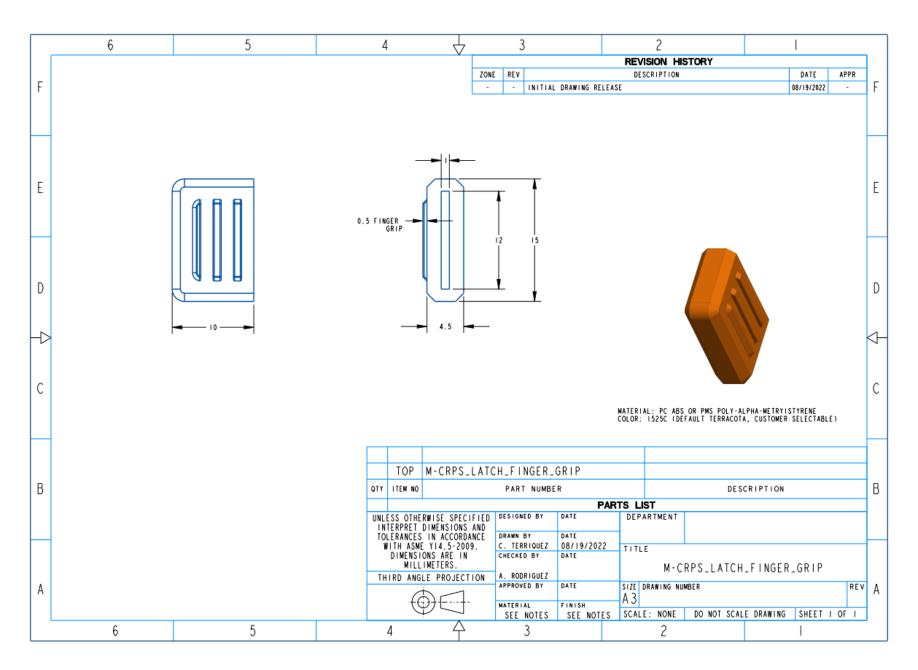

Supplemental Material I. M-CRPS latch plastic grip option 2 (over molded version) – Updated drawing, added material and default color.

Section 2.4.2 277VAC/380VDC Input - Added references for connector vendors and part numbers

Section 2.4.4 -48VDC Input (Telecom) - Added references for connector vendors and part numbers

Section~2.1.1.2~277VAC/380VDC~Input~-~Added~reference~for~connector~vendors~and~part~numbers

Section 2.1.1.4 -48VDC Input (Telecom) - Added reference for connector vendors and part numbers

Section 2.1.2.2 277VAC/380VDC Input - Added reference for connector vendors and part numbers

Section 2.1.2.4 -48VDC Input (Telecom) - Added reference for connector vendors and part numbers

Section 2.6.1 185mm by 73.5mm Form Factor - Updated Table 2-2 185mm/265mm by 73.5mm M-CRPS dimensions and receptacle connector; Added link to connectors information.

|                              |      | ·                                                                                                                                                                                 |

|------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |      | Section 2.6.2 185mm by 60mm Form Factor – Updated Table 2-4 185mm by 60mm M-CRPS                                                                                                  |

|                              |      | dimensions and receptacle connector, Added link to connectors information.                                                                                                        |

|                              |      | Supplemental Material G. M-CRPS latch mechanical drawing - Added latch material.                                                                                                  |

|                              |      | Section 9.7 Remote Sense And Return Sense / PSKILL – Added subsection                                                                                                             |

|                              |      | Section 2.6.1 185mm by 73.5mm Form Factor - Added note 7 in Table 2-3 73.5mm in width PSU                                                                                         |

|                              |      | pinout definition, and updated typo in the title.  Section 2.6.2 185mm by 60mm Form Factor - Added note 3 in Table 2-5 60mm in width PSU                                          |

|                              |      | pinout definition, and updated typo in the title.                                                                                                                                 |

|                              |      | Section 5.1.4 Line Isolation Requirements - Updated paragraph.                                                                                                                    |

|                              |      | Section 14.8.1 Dielectric Strength Testing - Updated paragraph.                                                                                                                   |

|                              |      | Section 5.1.9 Line Transient Specification – Updated note added test at full load                                                                                                 |

| September 26 <sup>th</sup> , | 1.00 | Section 11 FRU Requirements – Updated Table 11-1 Minimum FRU contents and added Table                                                                                             |

| 2022                         | RC2  | 11-2 M-CRPS FRU MultiRecord definition.                                                                                                                                           |

| 2022                         | NOZ  | Section 12.1.47 Summary of PMBus commands – Added command                                                                                                                         |

|                              |      | MFR_SPECIFIC_COMMAND EXT (FEh) in <i>Table 12-23 Summary of PMBus commands</i> .                                                                                                  |

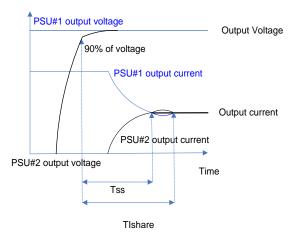

|                              |      | Section 7.13.1 Current Share (Ishare) – Updated settling time in Table 7-9 Additional                                                                                             |

|                              |      | Requirements on current share behavior.                                                                                                                                           |

|                              |      | Section 7.2 Peak Load Protection - Corrected typo in Table 7-2 Peak load protection testing                                                                                       |

|                              |      | conditions, peak load is Rated + 65% total.                                                                                                                                       |

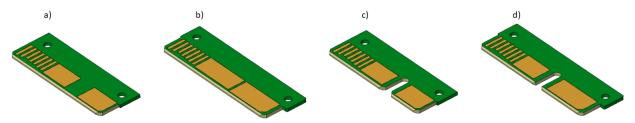

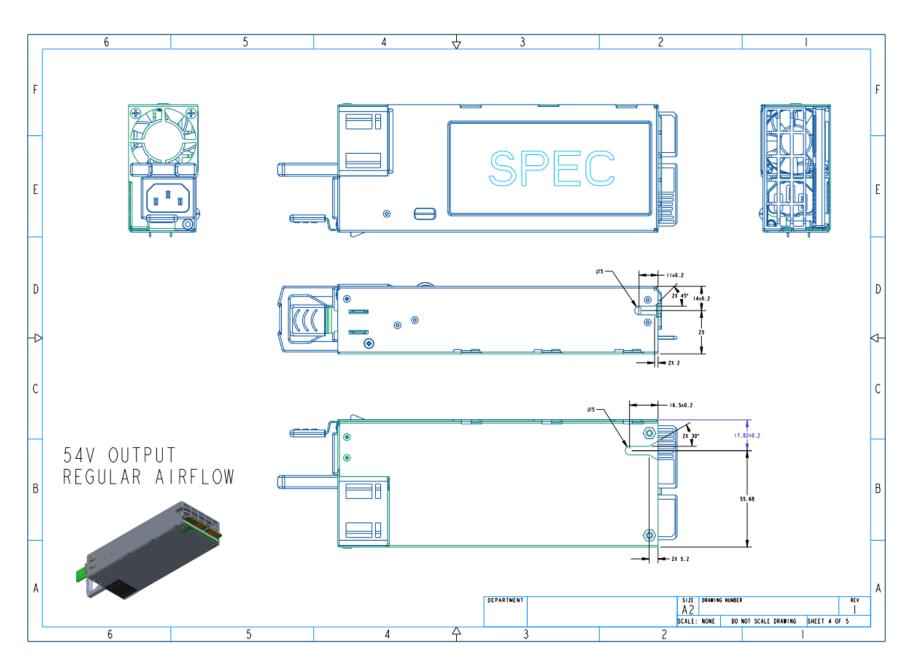

|                              |      | Section 2.6 Output Connector Interface – Updated Table 2-3 73.5mm in width PSU pinout                                                                                             |

|                              |      | definition and added note to reflect the notch in the +54V output M-CRPS.                                                                                                         |

|                              |      | Section 2.6 Output Connector Interface – Updated Table 2-5 60mm in width PSU pinout                                                                                               |

|                              |      | definition and added note to reflect the notch in the +54V output M-CRPS.                                                                                                         |

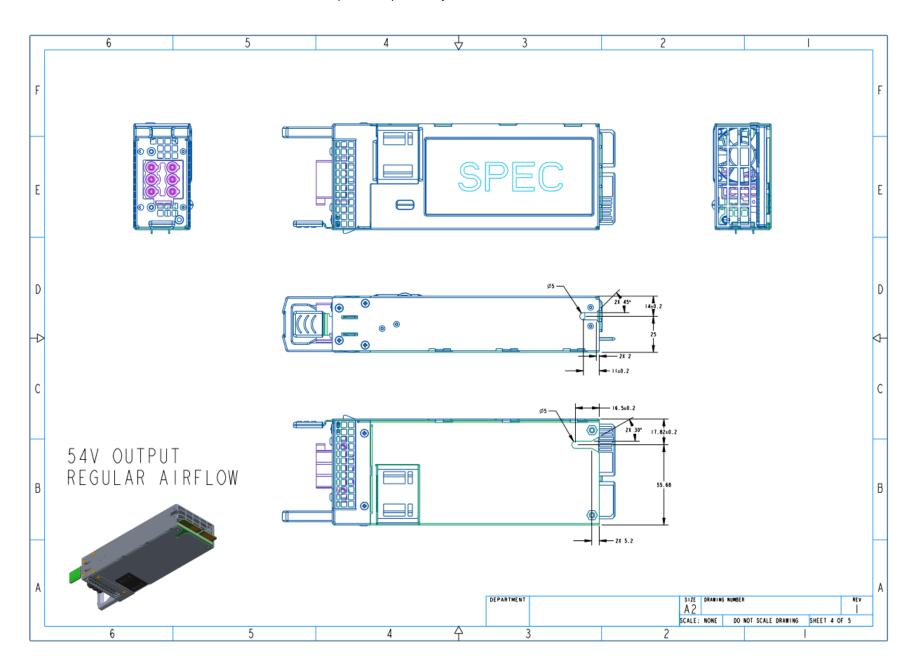

|                              |      | Supplemental Material D. 73.5mm in width M-CRPS card edge mechanical drawing – Added card edge's mechanical drawing with notch for +54V output M-CRPS and updated 12V output card |

|                              |      | edge sinecrianical drawing with hoter for 1547 output M-Ort 5 and dpdated 127 output card edge.                                                                                   |

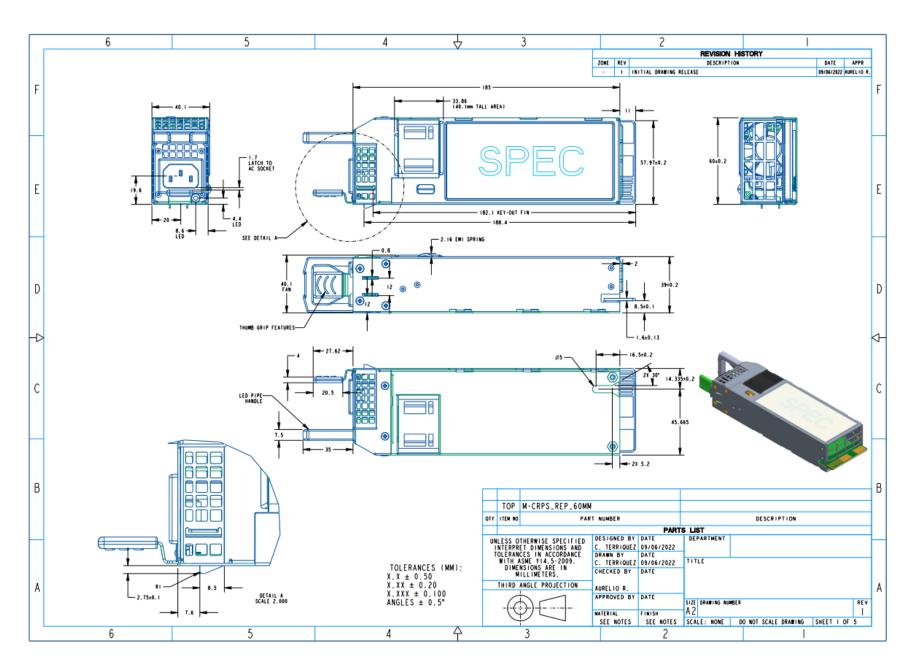

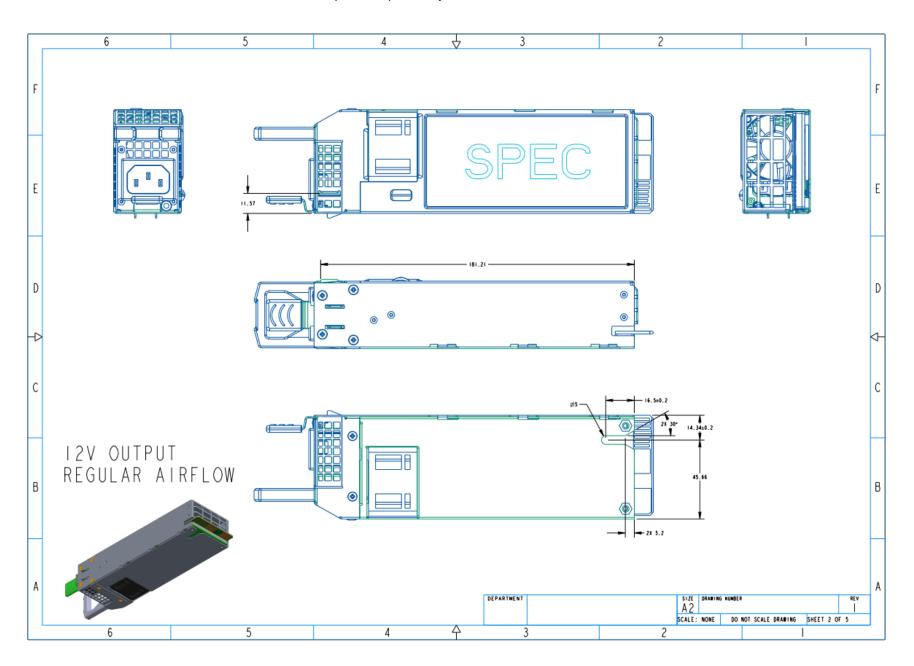

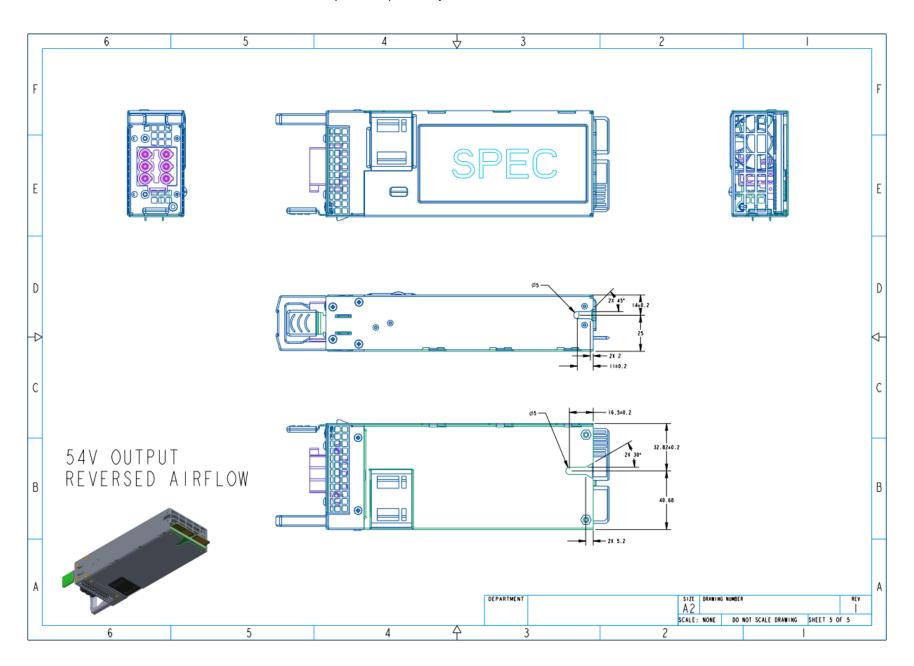

|                              |      | Supplemental Material E. 60mm in width M-CRPS card edge mechanical drawing - Added card                                                                                           |

|                              |      | edge's mechanical drawing with notch for +54V output M-CRPS and updated 12V output card                                                                                           |

|                              |      | edge.                                                                                                                                                                             |

|                              |      | Supplemental Material Q. Additional Requirements on Input Line Transients – Added section.                                                                                        |

|                              |      | Section 7.3 Auxiliary (Stand-by) Output - Added Table 7-3 Output voltage droop characteristics                                                                                    |

|                              |      | and updated caption of Figure 7-2 Typical 12VSB droop share characteristics.                                                                                                      |

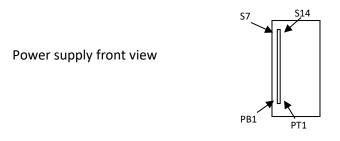

|                              |      | Section 2.6 Output Connector Interface – Updated Figure 2-23 and its caption.                                                                                                     |

|                              |      | Section 2.4.1 240VAC/240VDC Input – Updated Figure 2-16 IEC320-C20 Inlet connector                                                                                                |

|                              |      | example.                                                                                                                                                                          |

|                              |      | Section 8.3 Short Circuit Protection – Added subsection                                                                                                                           |

|                              |      | Section 5.1.1 Power Factor and iTHD - Added option for less than 1400W PSUs iTHD Table 5-2 iTHD requirements.                                                                     |

|                              |      | Section 5.1.8 Inrush Current High Voltage DC Input - Added subsection.                                                                                                            |

|                              |      | Section 5.3 Low Voltage -48VDC Input Requirements (Telecom) - Added Section 5.3.5 Inrush                                                                                          |

|                              |      | Current.                                                                                                                                                                          |

|                              |      | Section 5.3.3 Minimum Input Inductance - Removed last sentence since we already point to the                                                                                      |

|                              |      | supplemental material.                                                                                                                                                            |

|                              |      | Section 7.2 Peak Load Protection - Removed column voltage undershoot in Table 7-2 Peak load                                                                                       |

|                              |      | protection testing conditions.                                                                                                                                                    |

|                              |      | Section 7.4 Voltage Regulation - Updated note 1 of Table 7-4 Voltage regulation limits.                                                                                           |

|                              |      | Section 7.8 Closed Loop Stability - Updated paragraph and Note 2 in Table 7-8 Phase and gain                                                                                      |

|                              |      | margin requirements.                                                                                                                                                              |

|                              |      | Section 7.11 Zero Load Stability- Updated paragraphs.                                                                                                                             |

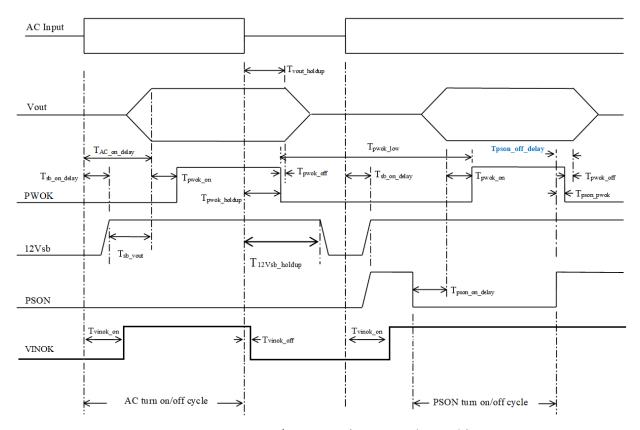

|                              |      | Section 7.16 PWOK Signal Timing Requirements – Updated note in Figure 7-10 Configurable PWOK warning time timing diagram for High voltage power supplies.                         |

|                              |      | Section 14.3 Safety Requirements and Standards - Removed duplicated paragraph i).                                                                                                 |

|                              |      | Section 14.5 Telecommunications DC Mains Powered Power Supplies – Fixed typo in Note 1.                                                                                           |

|                              |      | Section 9.2 PWOK Signal (Output) - Corrected typo in the heading (removed input).                                                                                                 |

|                              |      | Section 8.4 Input Over Current Protection – Added section.                                                                                                                        |

|                              |      | Section 9.1 PSON# Signal (Input) – Updated Figure 9-1 Required PSON# input signal circuit for                                                                                     |

|                              |      | two/three-state operation, for clarification.                                                                                                                                     |

|                              |      | Section 9.2 PWOK Signal (Output) – Updated Figure 9-5 PWOK circuit implementation, for                                                                                            |

|                              |      | clarification.                                                                                                                                                                    |

|                              |      | Section 9.1 PSON# Signal (Input) - Updated heading (removed duplicated "input" word).                                                                                             |

|                              |      | Section 9.3 SMBAlert# Signal (Output) - Updated heading (removed duplicated "output" word).                                                                                       |

|                              |      | Section 9.4 VINOK Signal (Output) - Updated heading (removed duplicated "output" word).                                                                                           |

|                              |      | Section 9.5 Imon Signal (Output) - Updated heading (removed duplicated "output" word).                                                                                            |

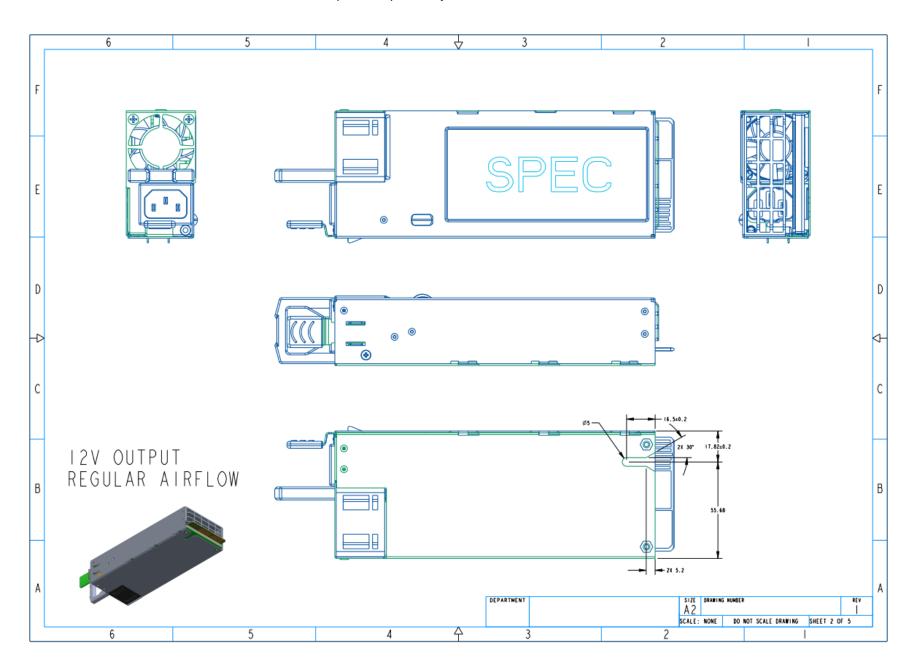

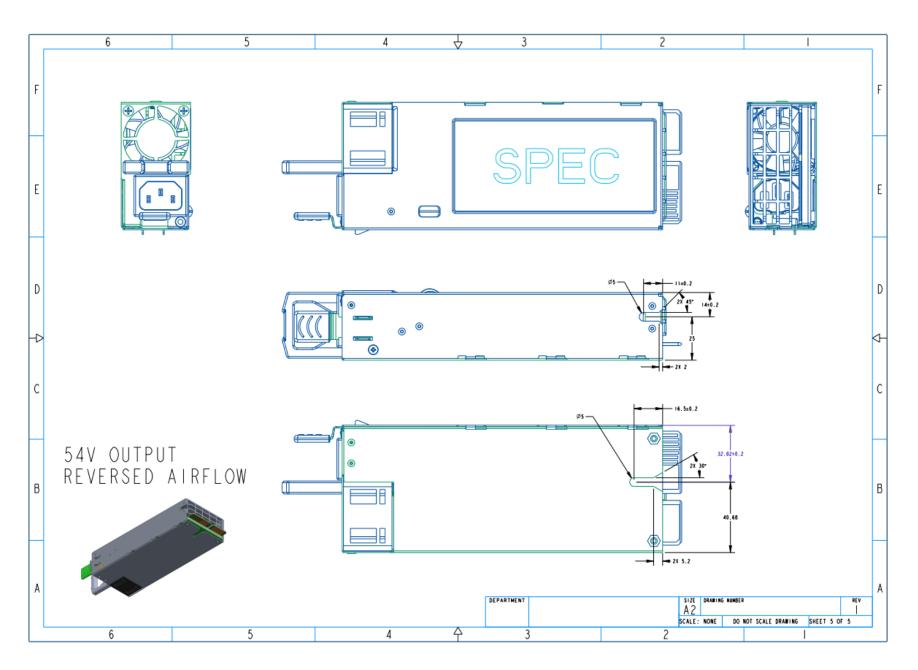

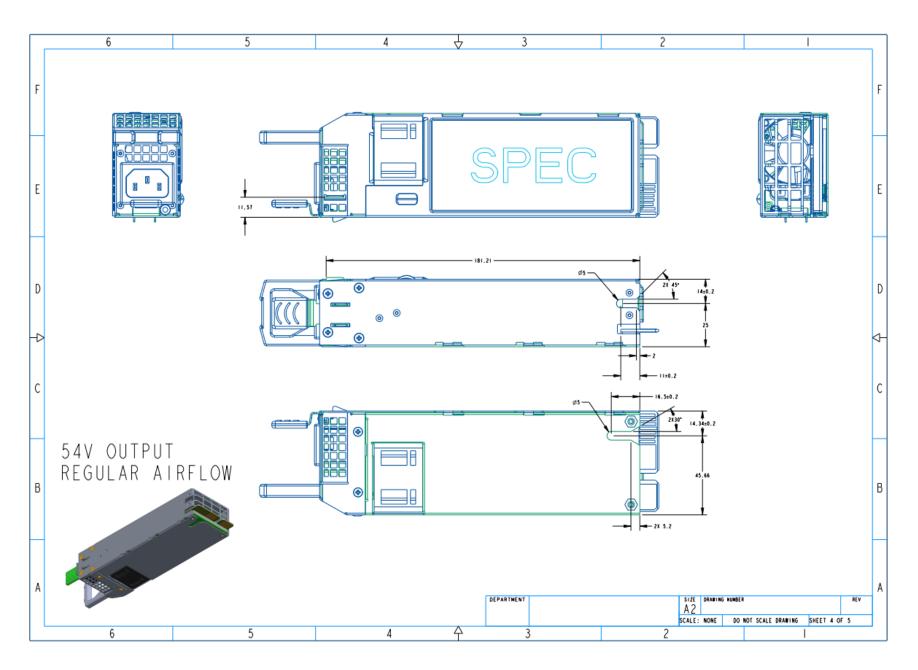

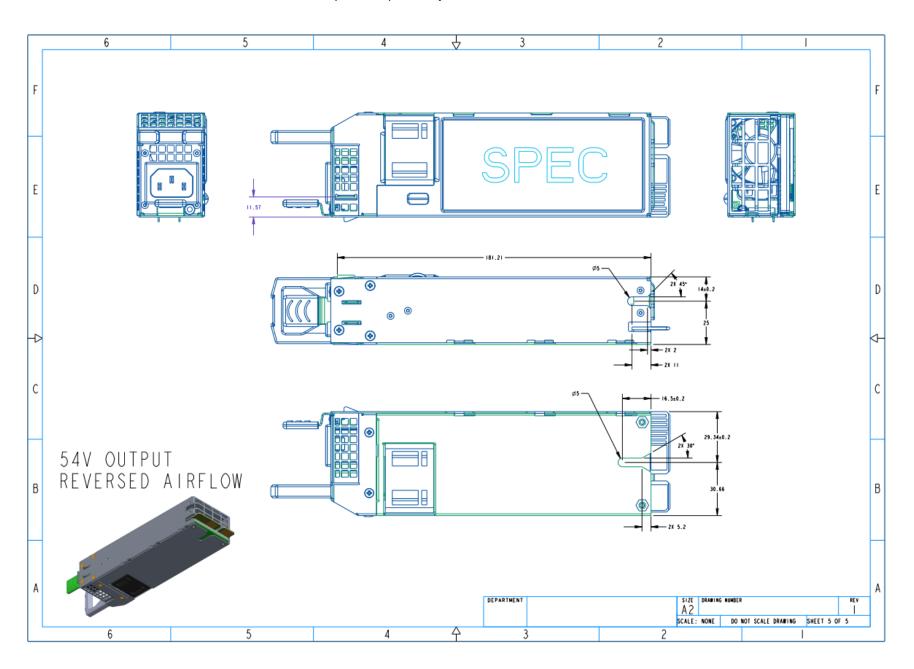

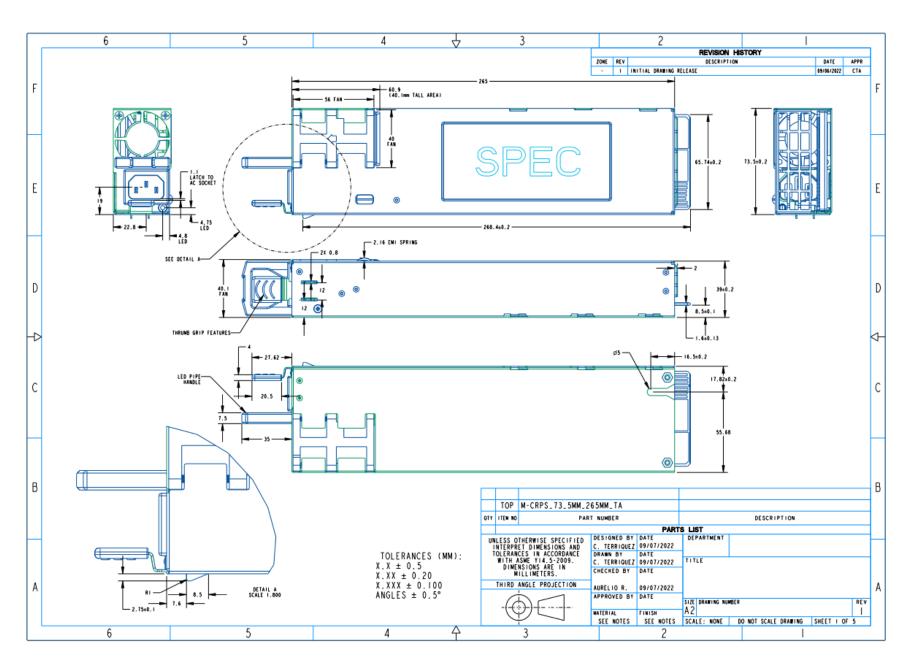

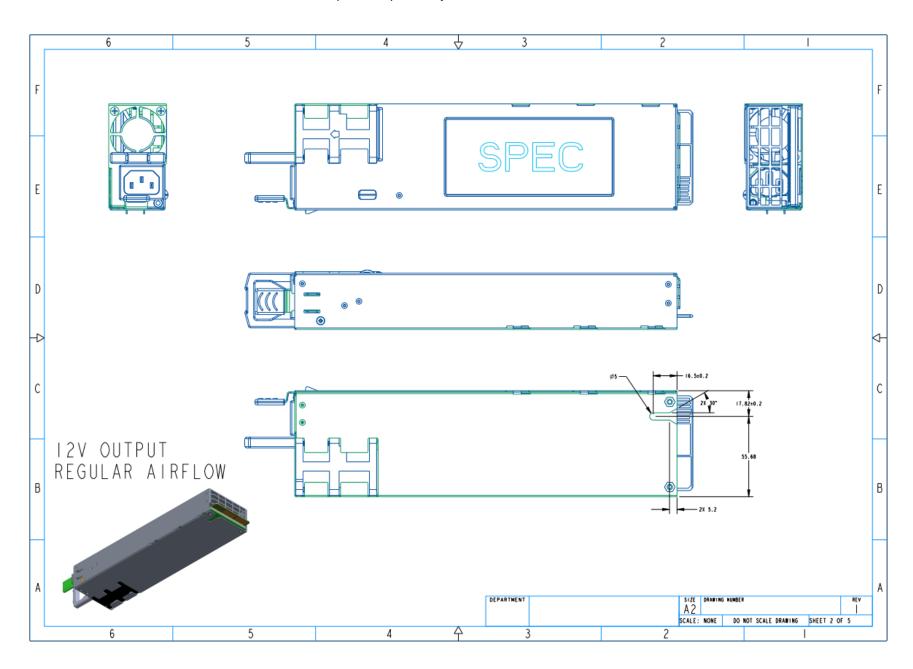

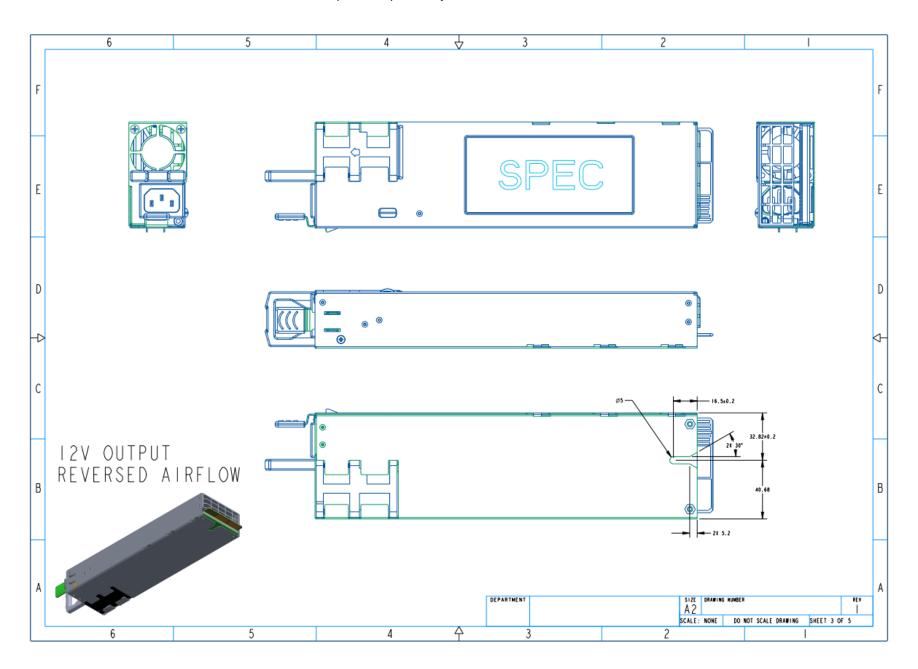

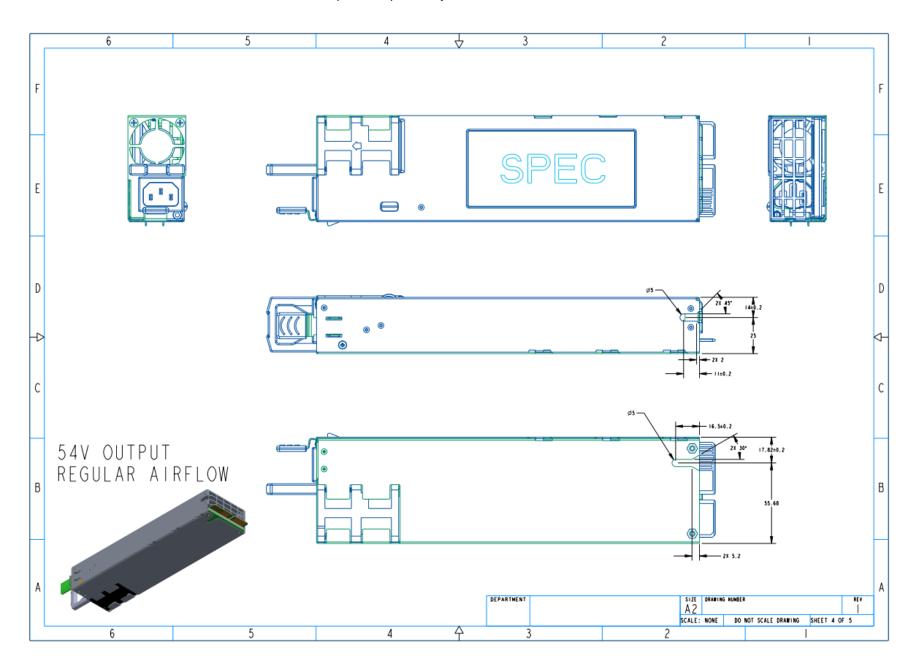

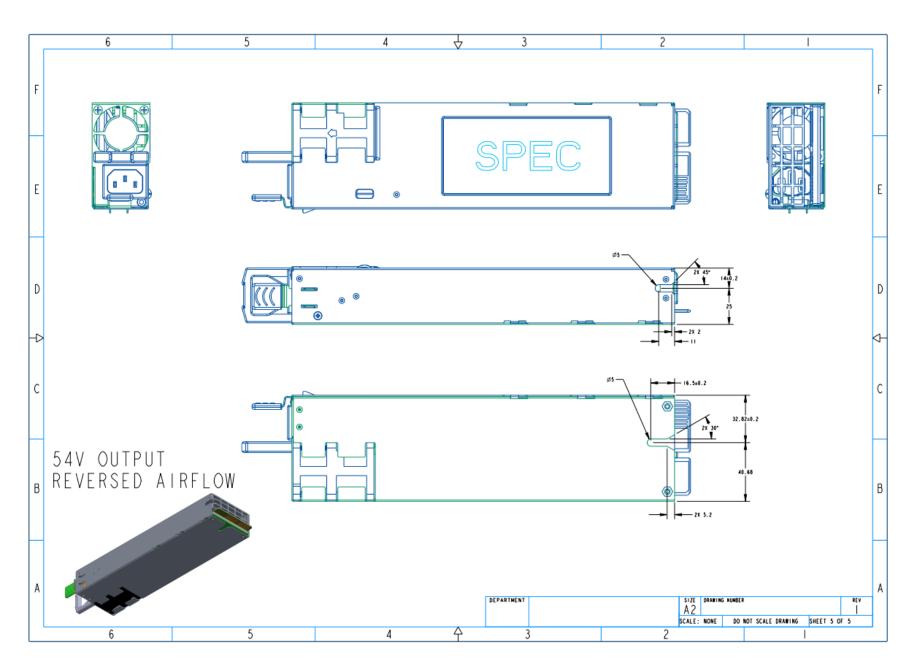

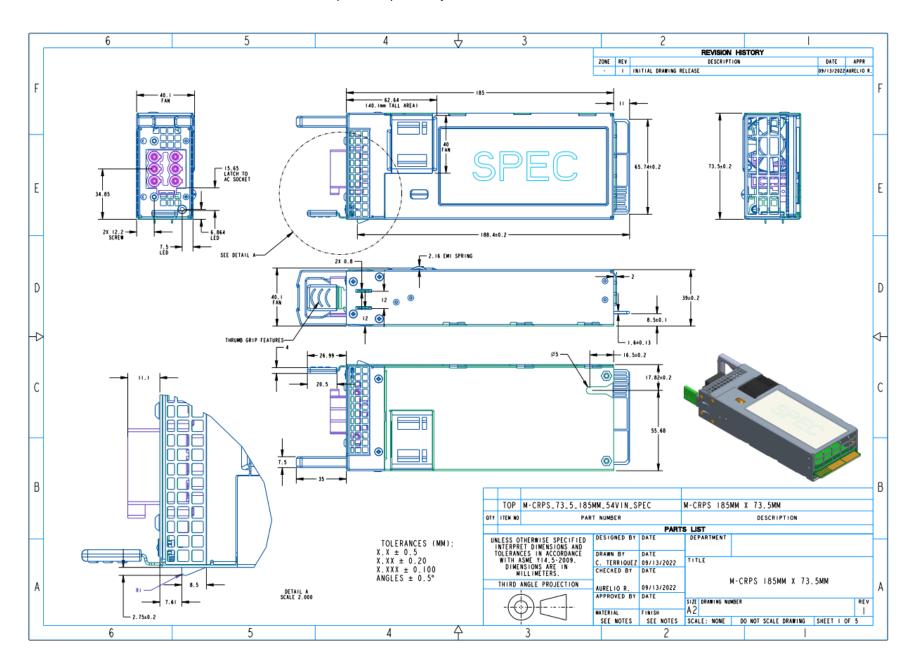

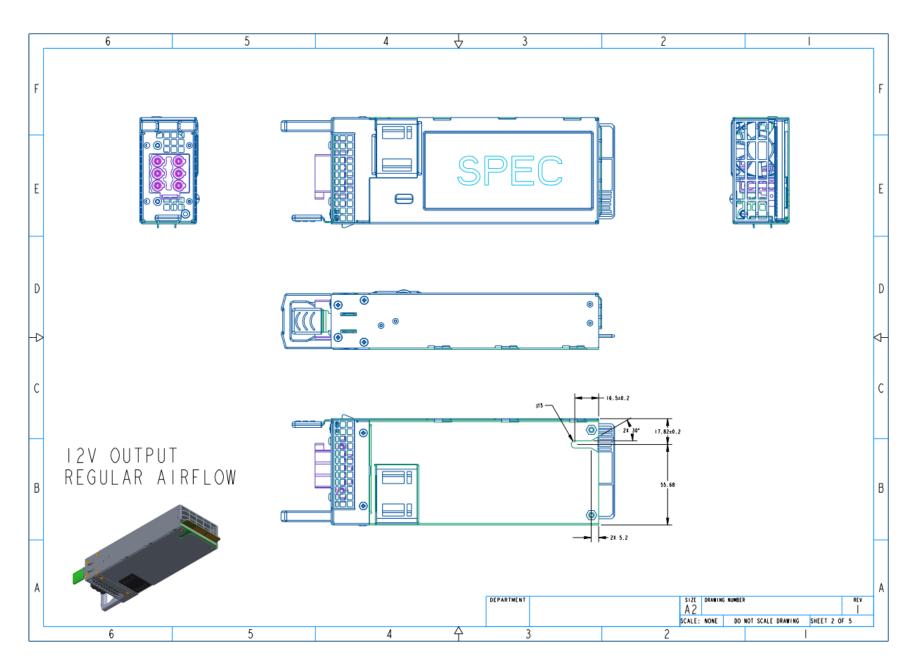

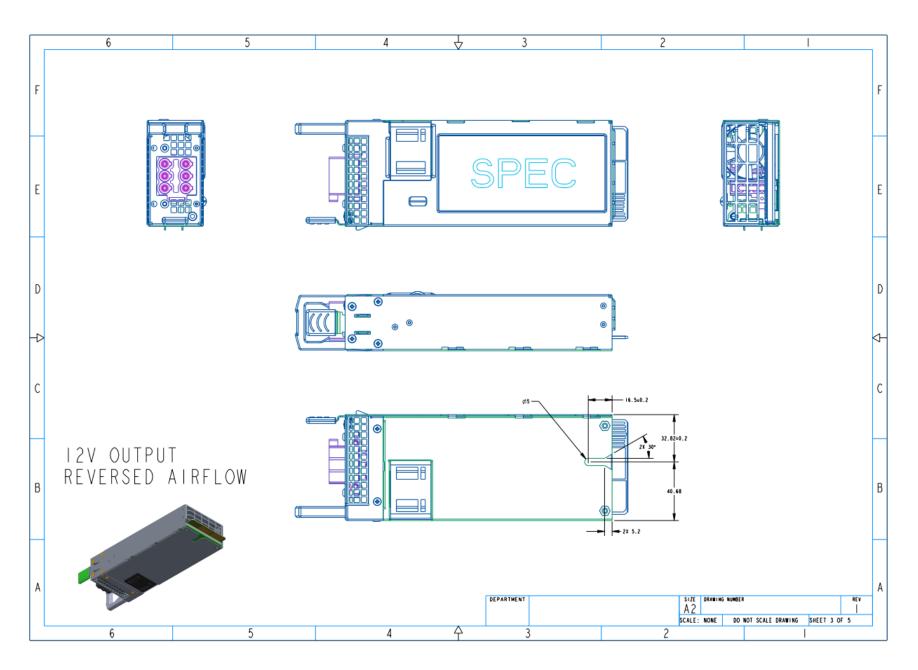

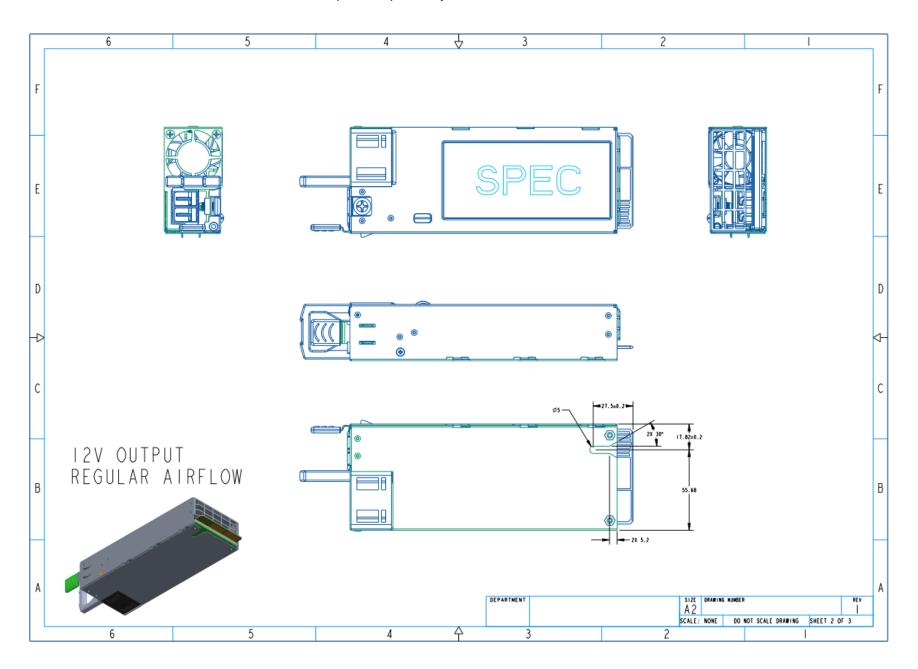

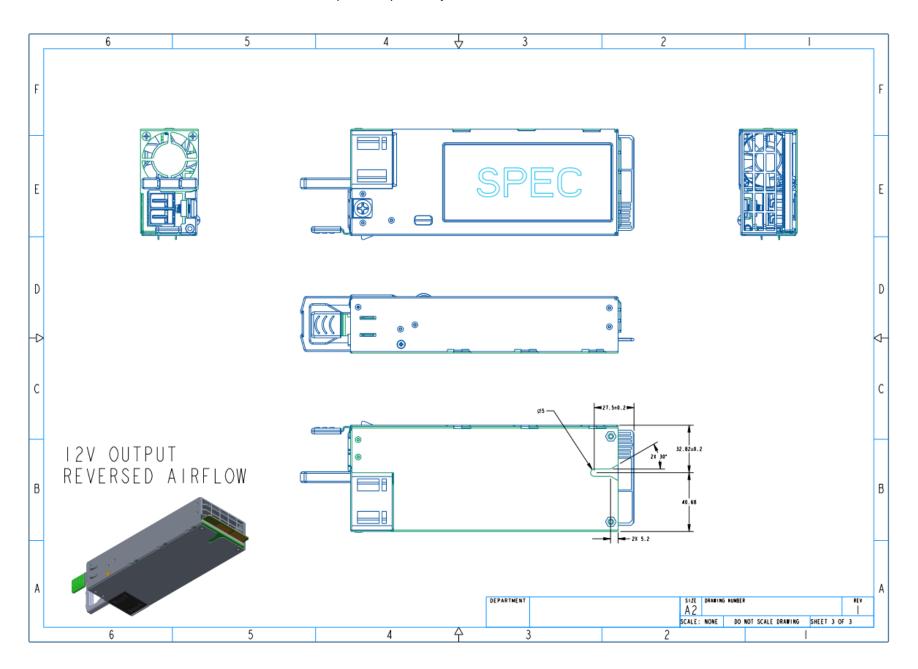

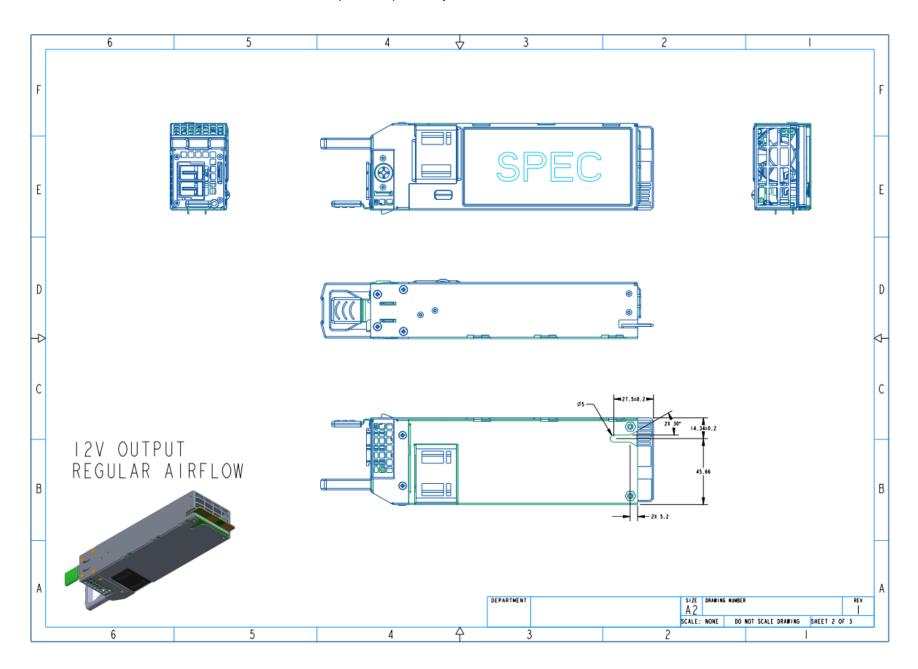

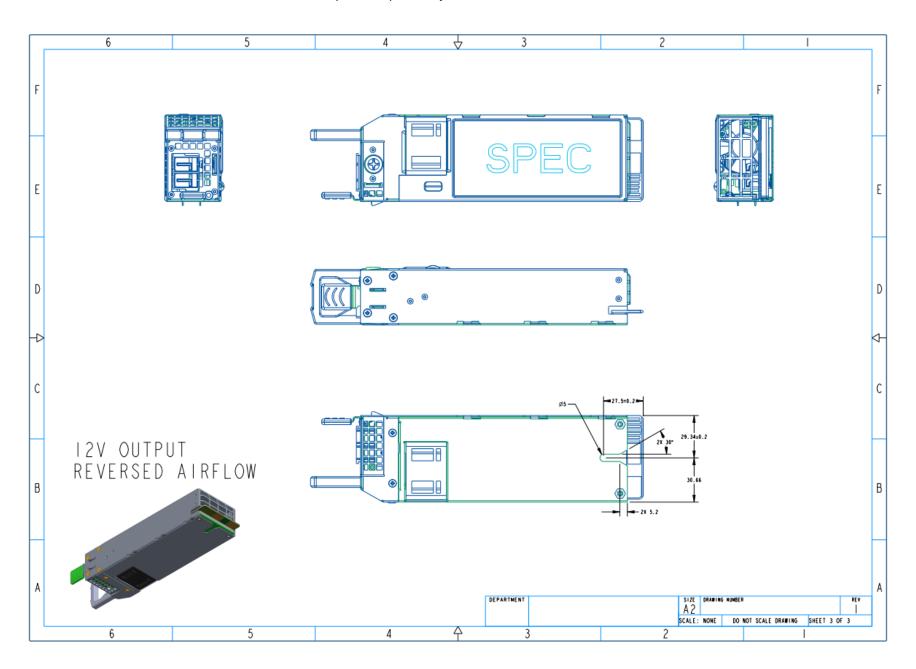

|                              |      | 185mm by 73.5mm M-CRPS mechanical drawing – Updated mechanical drawing to represent                                                                                               |

|                              |      | the different output voltage options (12V or 15V) and regular/reversed airflow                                                                                                    |

```

Section 2.1.1.3 +54VDC Input (Rack Power Input) - Updated paragraph and Figure 2-5 185mm

by 73.5mm form factor with bus bar connector input.

Section 12.1.44 IIN_OC_WARN_LIMIT (5Dh) - Added section.

Section 9.5 Imon Signal (Output) - Added note 4 in Table 9-5 Imon signal characteristics.

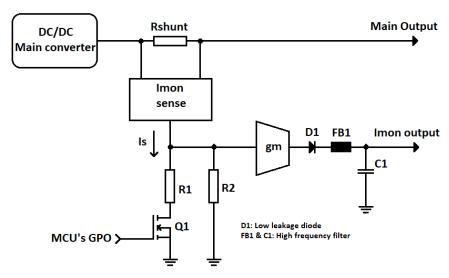

Section 9.5 Imon Signal (Output) - Added Figure 9-6 Imon block diagram concept.

Supplemental Material B 185mm by 60mm M-CRPS mechanical drawing - Added card edge's

mechanical drawing with notch for +54V output M-CRPS and updated 12V output card edge.

Supplemental Material C 265mm by 73.5mm M-CRPS mechanical drawing - Added card edge's

mechanical drawing with notch for +54V output M-CRPS and updated 12V output card edge.

Section 2.4.3 +54VDC Input (Rack Power Input) - Updated Figure 2-9 185mm by 60mm form

factor with 277VAC/380VDC inlet connector.

Section 9.5 Imon Signal (Output) - Updated Figure 9-6 Imon block diagram concept, added high

frequency filter and added Note 2.

Section 8.4 Input Over Current Protection - Table 8-6 Input OCW Averaging window and

hysteresis moved from Section 8.4.1 to Section 8.4.

Section 8.4.1 Input Over Current Warning - AC Input - Added cross reference to Section

12.1.44

Section 5.1.1 Power Factor and iTHD – Added notes 3, 4 & 5 in Table 5-2 iTHD requirements.

Section 5.1.9 Line Transient Specification - Added cross-reference to Supplemental Material Q.

Additional Requirements on Input Line Transients.

Section 12.9 Security - Updated section.

Section 7.16 PWOK Signal Timing Requirements – Updated cross-references and elaborated

return to default value condition.

Section 7.15 Timing Requirements - Updated maximum Tpwok off in Table 7-12 Timing

requirements and added Note 4.

Section 5.1 High Voltage AC/DC Input Requirements - Table 5-1 Power factor requirements

added Current iTHD (120VAC) requirements and added '<' symbols.

Section 7.16 PWOK Signal Timing Requirements - Updated note in Figure 7-10 Configurable

PWOK warning time timing diagram for High voltage power supplies, changed -5% to 11.40V.

Section 7.13.1 Current Share (Ishare) - Updated Ishare signal to 8V = 100% load

Section 9.5 Imon Signal (Output) - Table 9-5 Imon signal characteristics updated compliance

voltage to 3.3V.

Section 12.1.44 IIN_OC_WARN_LIMIT (5Dh) - Added Figure 12-10 Input OCW flowchart.

Section 2.4.3 +54VDC Input (Rack Power Input) - Added Figure 2-19 +54V Input connector

Section 2.4.4 -48VDC Input (Telecom) - Added Figure 2-21 -48V Inlet connector (Telecom)

pinout.

Section 12.7 Data & Sideband Serialization Interface (DSSI) - Updated section to have

compatibility with M-PESTI discovery command and virtual wires command and also a

compatible physical layer.

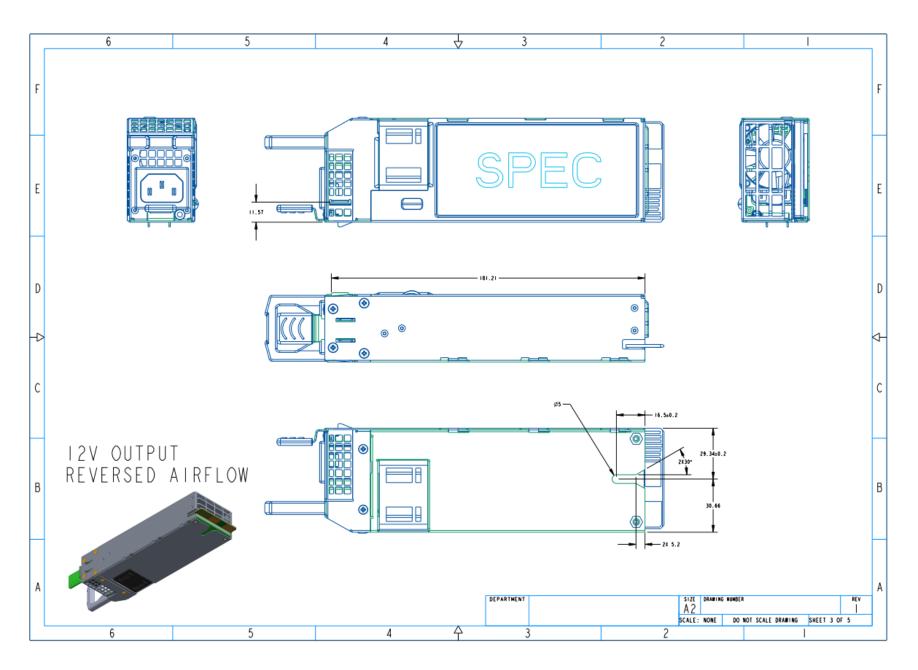

Supplemental Material J. 185mm by 73.5mm +54VDC input M-CRPS mechanical drawing -

Updated mechanical drawing.

Section 2.1.1.3 +54VDC Input (Rack Power Input) - Added note with cross reference to

Supplemental Material J.

Section 2.1.1.4 -48VDC Input (Telecom) - Added note with cross reference to Supplemental

Material K.

Section 12.9 Security - Updated Figure 12-45 Selected SPDM Messages.

Section 12.1.47 Summary of PMBus commands - Added DAh MFR SPDM command in Table

12-23 Summary of PMBus commands.

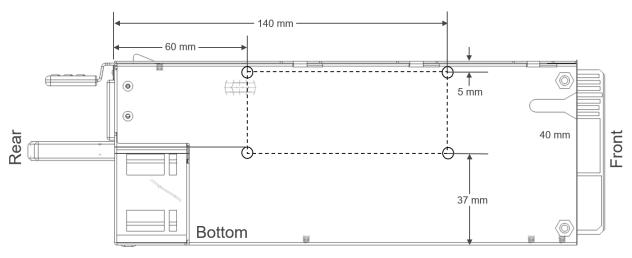

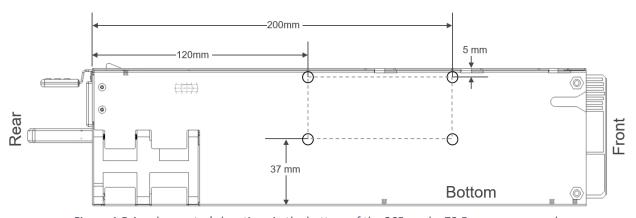

Section 4.2.5 Accelerometer Positions - Updated cross reference to Section 4.

Section 4.2.5 Accelerometer Positions - Updated Figure 4-3 Accelerometer's locations in the

bottom of the 185mm by 73.5mm power supply.

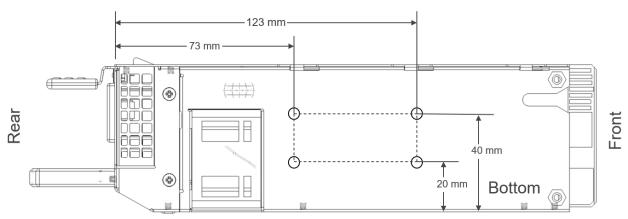

Section 4.2.5 Accelerometer Positions - Updated Figure 4-4 Accelerometer's locations in the

bottom of the 185mm by 60mm power supply.

Section 4.2.5 Accelerometer Positions - Updated Figure 4-5 Accelerometer's locations in the

bottom of the 265mm by 73.5mm power supply.

Section 4.2.9.1 185mm by 60mm Continuous Fan Speed Sweep - Added section.

Section 4.2.9.2 185mm by 73.5mm Continuous Fan Speed Sweep Limit - Added section.

Section 4.2.9.3 265mm by 73.5mm Continuous Fan Speed Sweep Limit - Added section.

Section 2.1.1.3 +54VDC Input (Rack Power Input) - Updated Figure 2-5 185mm by 73.5mm form

factor with bus bar connector input.

Section 12.7 Data & Sideband Serialization Interface (DSSI) - Updated section.

Section 12.8.2 Configuration File Header - Updated polynomial in Note of Table 12-47 Header

Section 12.8.3.1 LED Behavior Configuration Block - Updated Table 12-50 Power supply event

```

table.

|                              | I    | Section 12.9.2.0 Block Box Source on Foult/Marrier Condition Configuration Block                                                                                         |

|------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                              |      | Section 12.8.3.9 Black Box Save on Fault/Warning Condition Configuration Block - Removed                                                                                 |

|                              |      | Section 12.8.3.6 Fans Configuration Block - Added note 2 to Table 12-55 Power supply fans thresholds.                                                                    |

|                              |      | Section 12.8.3.8 Latch on Fault Condition Configuration Block - Updated Table 12-53 Power                                                                                |

|                              |      | supply latch on fault condition configuration block.                                                                                                                     |

|                              |      | Section 12.8.3 Configuration Area Definition - Updated Table 12-48 Configuration block types.                                                                            |

|                              |      | Section 12.8 Configuration File - Added note to Figure 12-40 Main areas of the configuration file.                                                                       |

|                              |      | Section 12.8.3.10 Miscellaneous Configuration Block - Updated section                                                                                                    |

|                              |      | Section 12.8.3.5 Input Configuration Block - Updated note 2 in Table 12-54 Power supply input thresholds.                                                                |

|                              |      | Section 12.8.5 Data Table Area Definition - Updated section.                                                                                                             |

|                              |      | Section 12.5.1 FW Image Mapping - Added Figure 12-25 In-System FW Update Memory Mapping.                                                                                 |

|                              |      | Section 12.5.4 Power Supply Operating Mode During and After Firmware Update - Updated paragraph.                                                                         |

|                              |      | Section 12.5.6 Firmware Update Process - Added Figure 12-27 PSU Boot flow during powering ON.                                                                            |

|                              |      | Section 12.5.7 Power Supply Commands - Updated MFR_MODEL to 24 bytes                                                                                                     |

|                              |      | Section 12.5.7 Power Supply Commands - Updated Table 12-33 PSU FW Image header and                                                                                       |

|                              |      | added notes.                                                                                                                                                             |

|                              |      | Section 12.1.47 Summary of PMBus commands - Added commands D1h, D2h and D3h in Table 12-23 Summary of PMBus commands.                                                    |

|                              |      | Section 2.3 LED Marking and Identification - Deleted note 1.                                                                                                             |

|                              |      | Section 2.1.2.3 +54VDC Input (Rack Power Input) - Updated section                                                                                                        |

|                              |      | Section 5.2.1 Inlet Connector - Updated paragraph                                                                                                                        |

|                              |      | Section 5.2.6 Susceptibility Requirements - Updated paragraph                                                                                                            |

|                              |      | Section 7.13.1 Current Share (Ishare) - Added note 2 in Table 7-9 Additional Requirements on                                                                             |

|                              |      | current share behavior.                                                                                                                                                  |

|                              |      | Section 12.1.44 IIN_OC_WARN_LIMIT (5Dh) - Updated Note 8.b and 9.a.  Section 9.6.1 A0 Input Addressing - Added note 2 in Figure 9-7 Flow diagram to detect between       |

|                              |      | logic and analog SMBus addressing.                                                                                                                                       |

|                              |      | Section 12.5.7 Power Supply Commands - Updated length of MFR_FW_REVISION command to 5 bytes.                                                                             |

|                              |      | Section 13.1 Component De-Rating - Removed ESD TBDs, added Transistor, GaAs, GaN, PHEMT (GaN) type in Table 13-1 Component de-rating guidelines.                         |

|                              |      | Supplemental Material J. 185mm by 73.5mm +54VDC input M-CRPS mechanical drawing – Updated mechanical drawing (latch).                                                    |

|                              |      | Supplemental Material K. 185mm by 73.5mm -48VDC input M-CRPS mechanical drawing – Updated mechanical drawings, added airflow direction options.                          |

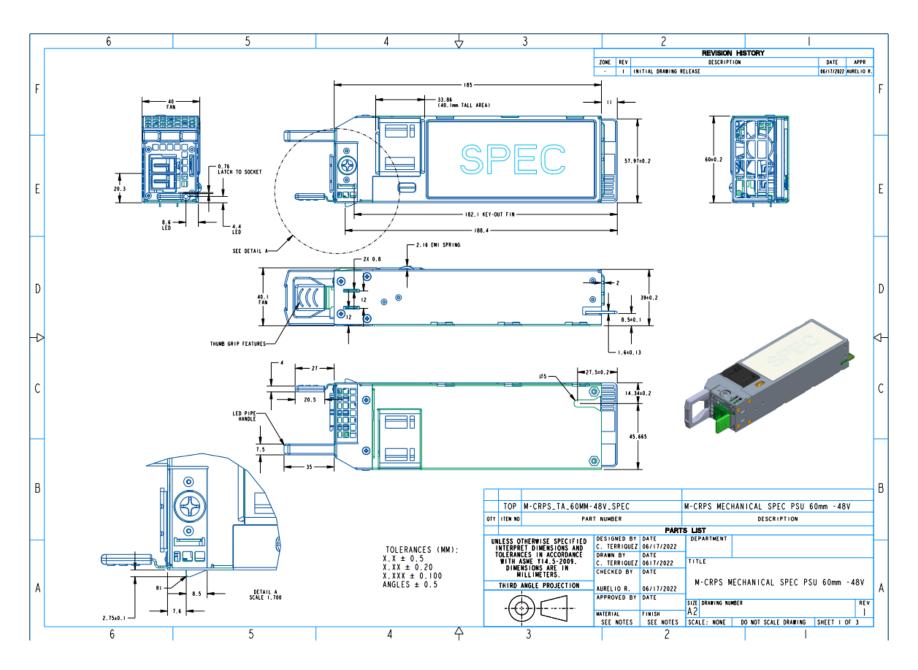

|                              |      | Supplemental Material L. 185mm by 60mm -48VDC input M-CRPS mechanical drawing – Added mechanical drawing and shifting the rest of the Supplemental Material subsections. |

|                              |      | Section 12.1.47 Summary of PMBus commands – Added MFR_LINE_STATUS (E0h) and MFR_SYSTEM_LED_CNTL (E1h) commands to Table 12-23 Summary of PMBus commands.                 |

|                              |      | Section 12.8.3.1 LED Behavior Configuration Block – Updated Table 12-49 LED descriptor.                                                                                  |

|                              |      | Section 12.1.46 MFR_SYSTEM_LED_CNTL (E1h) – Added subsection.                                                                                                            |

|                              |      | Section 12.1.44 IIN_OC_WARN_LIMIT (5Dh) - Updated Note 8.b and 9.a.                                                                                                      |

|                              |      | Section 12.8.3.1 LED Behavior Configuration Block – Added mismatched event in Table 12-50                                                                                |

|                              |      | Power supply event table.                                                                                                                                                |

|                              |      | Section 12.1.45 MFR_LINE_STATUS (E0h) – Added section. Section Acknowledgements – Updated section.                                                                       |

|                              |      | Section III DC-MHS Family of Specifications – Added section.                                                                                                             |

|                              |      | Section 7.3 Auxiliary (Stand-by) Output - Added notes 1 and 2.                                                                                                           |

|                              |      | Formatted the entire document to have everything within the document margins.                                                                                            |

| September 27 <sup>th</sup> , | 1.00 | Removed Appendix A and B.                                                                                                                                                |

| 2022                         | RC3  | Fixed typos                                                                                                                                                              |

|                              |      |                                                                                                                                                                          |

|                              | I.   | l                                                                                                                                                                        |

## Table of Contents

| I.  | Li   | cense           |                                              | 19 |

|-----|------|-----------------|----------------------------------------------|----|

|     | Ope  | n Web           | Foundation (OWF) CLA                         | 19 |

|     | Ackr | nowledg         | gements                                      | 20 |

| 11. | Sc   | cope            |                                              | 20 |

| Ш   |      | DC-MH           | dS Family of Specifications                  | 20 |

| 1   | 0    | verview         | /                                            | 21 |

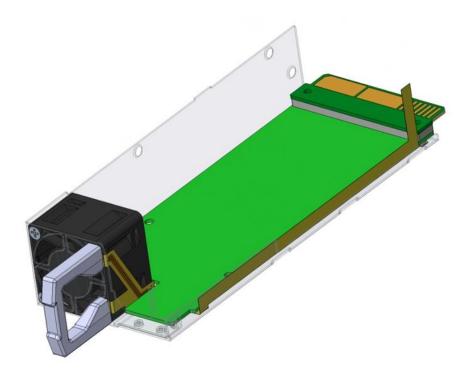

| 2   | M    | 1echanio        | cal Overview                                 | 21 |

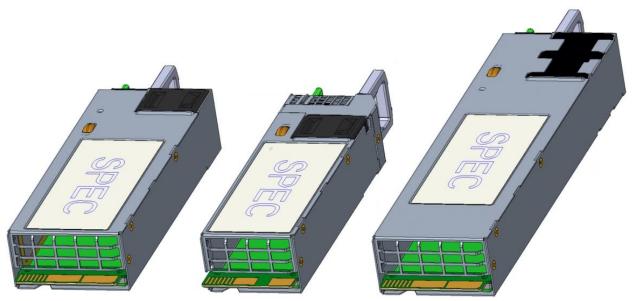

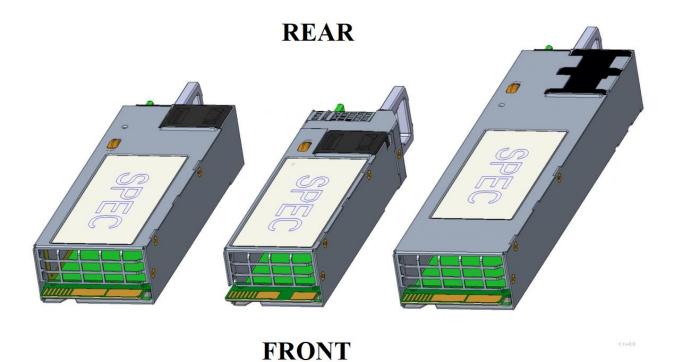

|     | 2.1  | Forn            | n Factor Outline                             | 22 |

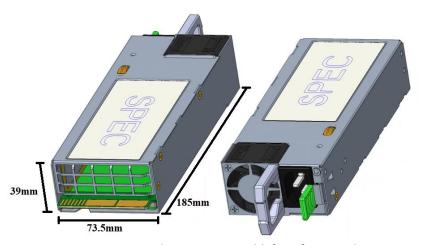

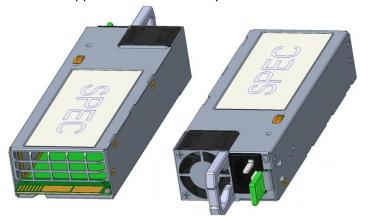

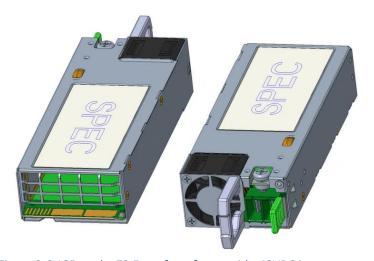

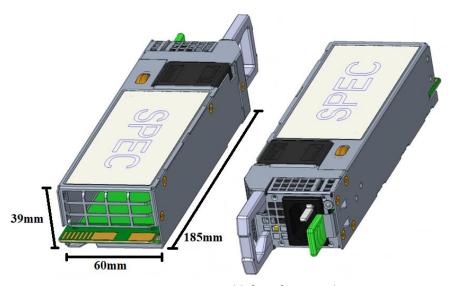

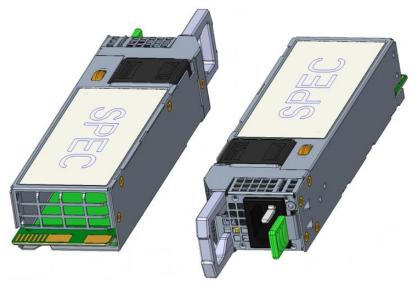

|     | 2.   | .1.1            | 185mm by 73.5mm Form Factor                  | 22 |

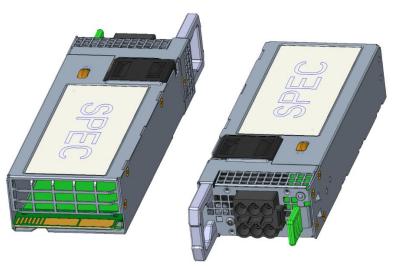

|     | 2.   | .1.2            | 185mm by 60mm Form Factor                    | 24 |

|     | 2.2  | Han             | dle and Retention Latch                      | 26 |

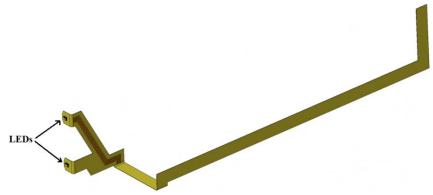

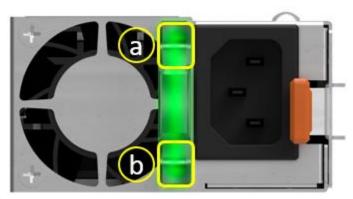

|     | 2.3  | LED             | Marking and Identification                   | 27 |

|     | 2.4  | Inlet           | Connector                                    | 29 |

|     | 2.   | .4.1            | 240VAC/240VDC Input                          | 29 |

|     | 2.   | .4.2            | 277VAC/380VDC Input                          | 29 |

|     | 2.   | .4.3            | +54VDC Input (Rack Power Input)              | 30 |

|     | 2.   | .4.4            | -48VDC Input (Telecom)                       | 31 |

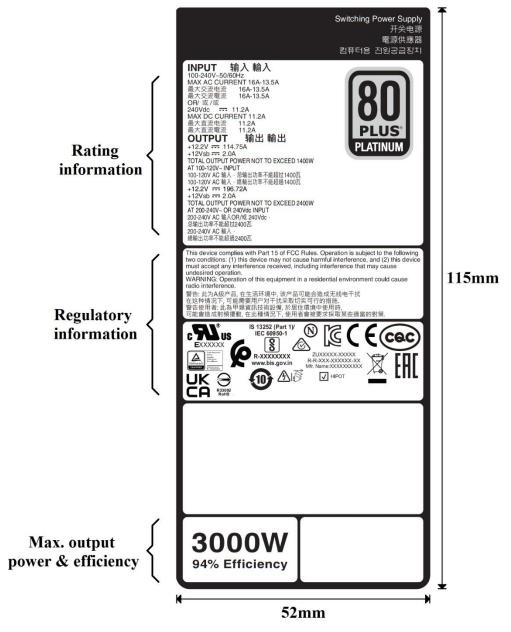

|     | 2.5  | Labe            | el Outline and Artwork                       | 31 |

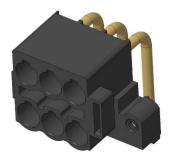

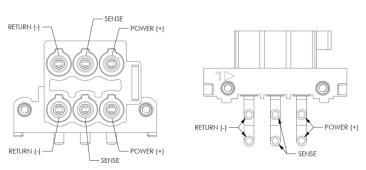

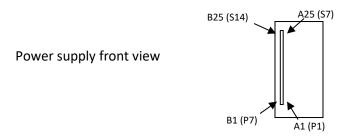

|     | 2.6  | Out             | out Connector Interface                      | 32 |

|     | 2.   | .6.1            | 185mm by 73.5mm Form Factor                  | 33 |

|     | 2.   | .6.2            | 185mm by 60mm Form Factor                    | 34 |

| 3   | Tł   | hermal          | Requirements                                 | 36 |

|     | 3.1  | Tem             | perature and Altitude Conditions             | 36 |

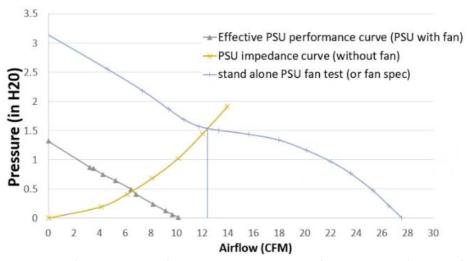

|     | 3.2  | Pow             | er Supply Fan                                | 37 |

|     | 3.3  | Thermal Sensors |                                              | 37 |

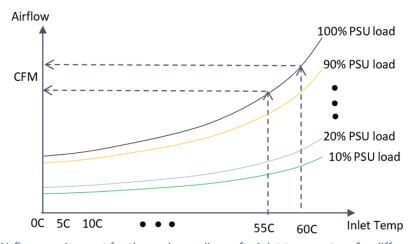

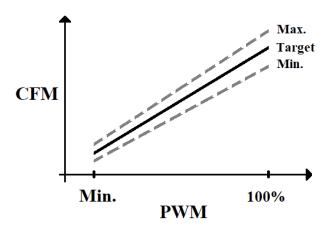

|     | 3.4  | Fan             | Speed Control                                | 37 |

|     | 3.   | .4.1            | Fan Speed Control Algorithm                  | 37 |

|     | 3.   | .4.2            | Fan Fault                                    | 38 |

|     | 3.   | .4.3            | System Fan Speed Override                    | 38 |

|     | 3.5  | Add             | itional Thermal and Airflow Characterization | 39 |

| 4   | A    | coustics        | and Vibration Requirements                   | 42 |

|     | 4.1  | Aco             | ustic Requirements                           | 42 |

|   | 4.1.1     | General, Laboratory, and Sampling Requirements     | 43 |

|---|-----------|----------------------------------------------------|----|

|   | 4.1.2     | Test Environment                                   | 43 |

|   | 4.1.3     | Instrumentation                                    | 43 |

|   | 4.1.4     | Installation and Operation of the Power Supply     | 44 |

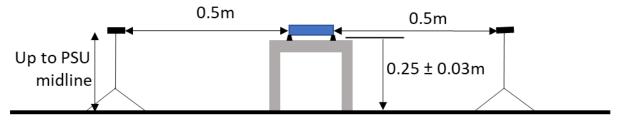

|   | 4.1.5     | Microphone Positions                               | 44 |

|   | 4.1.6     | Measurement of Acoustical Data                     | 45 |

|   | 4.1.7     | Operating Modes                                    | 45 |

|   | 4.1.8     | Calculation of Acoustical Values by Operating Mode | 48 |

|   | 4.1.9     | Acoustical Requirements                            | 49 |

|   | 4.1.10    | Reporting Requirements                             | 53 |

| 4 | I.2 Vibr  | ration Requirements                                | 54 |

|   | 4.2.1     | General, Laboratory, and Requirements              | 54 |

|   | 4.2.2     | Test Environment                                   | 55 |

|   | 4.2.3     | Instrumentation                                    | 55 |

|   | 4.2.4     | Installation and Operation of the Power Supply     | 55 |

|   | 4.2.5     | Accelerometer Positions                            | 55 |

|   | 4.2.6     | Measurement of Acoustical Data                     | 56 |

|   | 4.2.7     | Operating Modes                                    | 57 |

|   | 4.2.8     | Calculation of Vibration Values to Report          | 57 |

|   | 4.2.9     | Vibration Requirements                             | 57 |

|   | 4.2.10    | Reporting Requirements                             | 59 |

| 5 | Electrica | l Input Requirements                               | 60 |

| 5 | 5.1 High  | n Voltage AC/DC Input Requirements                 | 60 |

|   | 5.1.1     | Power Factor and iTHD                              | 60 |

|   | 5.1.2     | Inlet Connector                                    | 60 |

|   | 5.1.3     | Input Voltage Specification                        | 60 |

|   | 5.1.4     | Line Isolation Requirements                        | 62 |

|   | 5.1.5     | Line Dropout/Holdup                                | 62 |

|   | 5.1.6     | Line Fuse                                          | 63 |

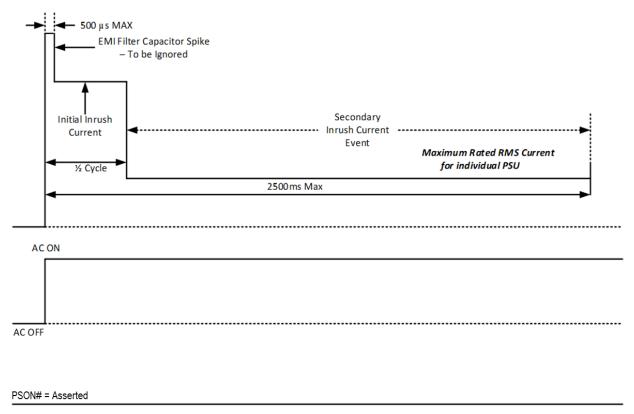

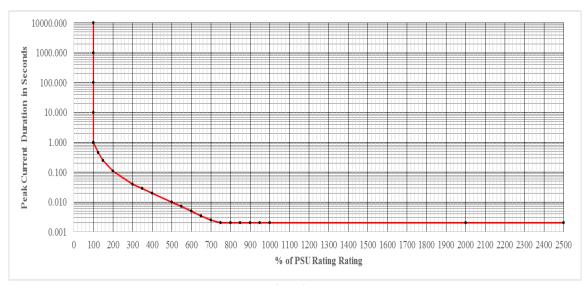

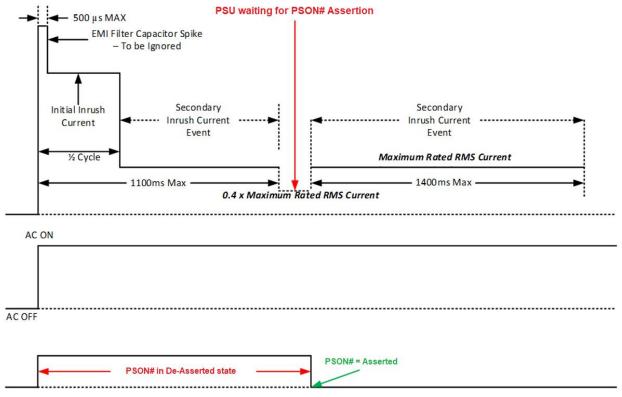

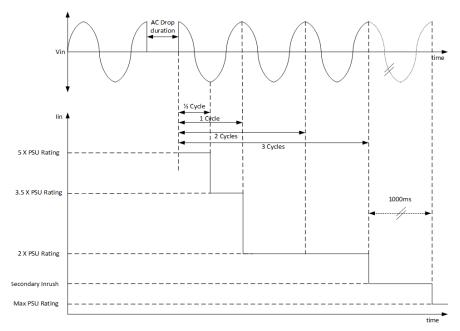

|   | 5.1.7     | Inrush Current                                     | 63 |

|   | 5.1.8     | Inrush Current High Voltage DC Input               | 66 |

|   | 5.1.9     | Line Transient Specification                       | 67 |

|   | 5.1.10    | Susceptibility Requirements                        | 68 |

| !   | 5.1.11     | Electrostatic Discharge Susceptibility               | 68 |

|-----|------------|------------------------------------------------------|----|

| !   | 5.1.12     | Fast Transient/Burst                                 | 69 |

| !   | 5.1.13     | Radiated Immunity                                    | 69 |

| !   | 5.1.14     | Surge Immunity                                       | 69 |

| !   | 5.1.15     | Voltage Interruptions                                | 69 |

| !   | 5.1.16     | Power Recovery                                       | 69 |

| !   | 5.1.17     | Minimum Input Inductance                             | 70 |

| 5.2 | . Low      | Voltage +54VDC Input Requirements (Rack Power Input) | 70 |

| !   | 5.2.1      | Inlet Connector                                      | 70 |

| į   | 5.2.2      | Input Voltage Specification                          | 70 |

| !   | 5.2.3      | Fuse                                                 | 71 |

| !   | 5.2.4      | Inrush Current                                       | 71 |

| !   | 5.2.5      | Transients Requirements                              | 71 |

| !   | 5.2.6      | Susceptibility Requirements                          | 71 |

| !   | 5.2.7      | Input Dropout/Holdup                                 | 71 |

| !   | 5.2.8      | Input Ripple Voltage                                 | 72 |

| !   | 5.2.9      | Isolation Requirements                               | 72 |

| 5.3 | S Low      | Voltage -48VDC Input Requirements (Telecom)          | 72 |

| !   | 5.3.1      | Inlet Connector                                      | 72 |

|     | 5.3.2      | Input Voltage Specification                          | 72 |

| !   | 5.3.3      | Minimum Input Inductance                             | 72 |

| !   | 5.3.4      | Input Impedance                                      | 73 |

| !   | 5.3.5      | Inrush Current                                       | 73 |

| į   | 5.3.6      | Fuse                                                 | 74 |

| !   | 5.3.7      | Reversed Polarity Protection                         | 74 |

| į   | 5.3.8      | Input dv/dt                                          | 74 |

| !   | 5.3.9      | Input Ripple Voltage                                 | 75 |

| !   | 5.3.10     | Input Reflected Ripple Current                       | 75 |

| !   | 5.3.11     | Surge Immunity                                       | 75 |

| !   | 5.3.12     | Inrush Current                                       | 75 |

| I   | Efficiency | <i>,</i>                                             | 76 |

| (   | 6.1.1      | High Voltage AC/DC Input Power Supplies              | 76 |

| (   | 6.1.2      | Low Voltage DC Input Power Supplies                  | 77 |

| 7 | Out  | put R | equirements                                                 | 77  |

|---|------|-------|-------------------------------------------------------------|-----|

|   | 7.1  | Out   | put Power/Currents                                          | 77  |

|   | 7.2  | Pea   | k Load Protection                                           | 78  |

|   | 7.3  | Aux   | iliary (Stand-by) Output                                    | 79  |

|   | 7.4  | Volt  | age Regulation                                              | 79  |

|   | 7.5  | Dyn   | amic Loading                                                | 80  |

|   | 7.6  | Cap   | acitive Loading                                             | 81  |

|   | 7.7  | Gro   | unding                                                      | 81  |

|   | 7.8  | Clos  | ed Loop Stability                                           | 81  |

|   | 7.9  | Resi  | dual Voltage Immunity in Standby Mode                       | 82  |

|   | 7.10 | Soft  | Starting                                                    | 82  |

|   | 7.11 | Zero  | Load Stability                                              | 82  |

|   | 7.12 | Hot   | Swap                                                        | 82  |

|   | 7.13 | Ford  | ed Load Sharing                                             | 83  |

|   | 7.13 | 3.1   | Current Share (Ishare)                                      | 83  |

|   | 7.13 | 3.2   | Main Output Voltage Regulation Droop                        | 85  |

|   | 7.13 | 3.3   | Current Sharing Load Step Response                          | 85  |

|   | 7.13 | 3.4   | Current Share with Margining                                | 85  |

|   | 7.13 | 3.5   | Current Share Activation                                    | 85  |

|   | 7.13 | 3.6   | Ishare Disconnect Circuitry                                 | 86  |

|   | 7.13 | 3.7   | Concurrent Maintenance                                      |     |

|   | 7.13 | 8.8   | Maximum Power Rating with Parallel PSUs                     | 86  |

|   | 7.13 | 3.9   | Current Share Signal Characteristics                        | 86  |

|   | 7.14 |       | ole/Noise                                                   |     |

|   | 7.15 |       | ing Requirements                                            |     |

|   | 7.16 |       | OK Signal Timing Requirements                               |     |

| 8 |      |       | n Circuits                                                  |     |

|   | 8.1  |       | n Output                                                    |     |

|   | 8.1. |       | Current sense                                               |     |

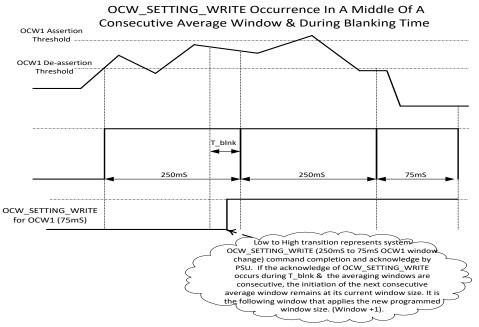

|   | 8.1. |       | Averaging Mechanism                                         |     |

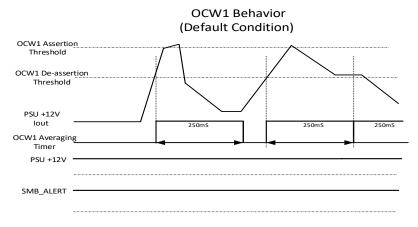

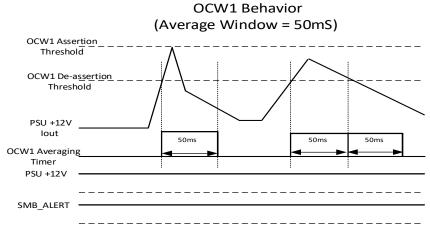

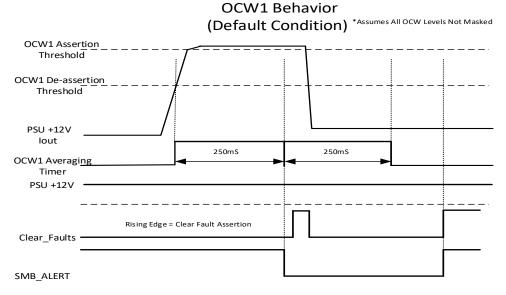

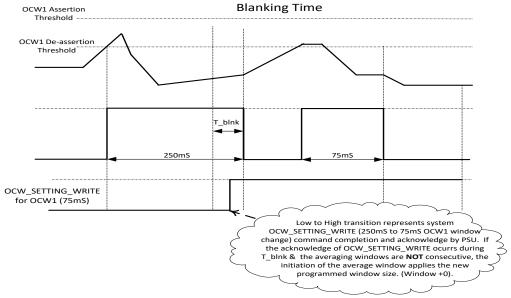

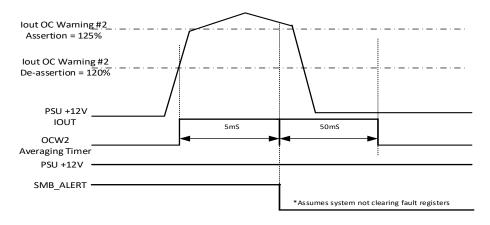

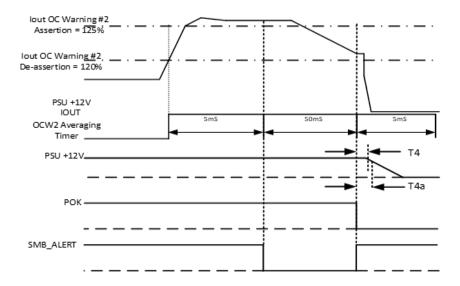

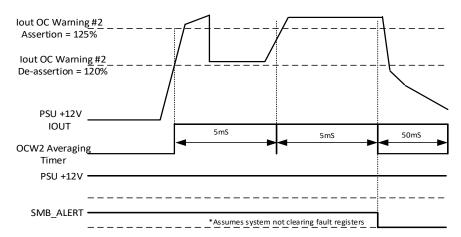

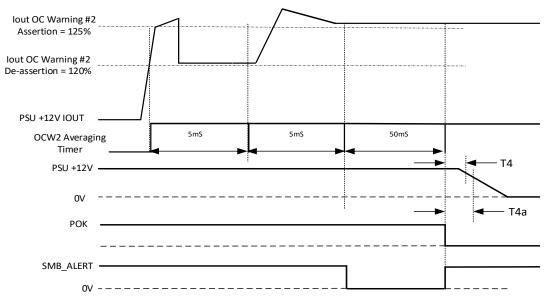

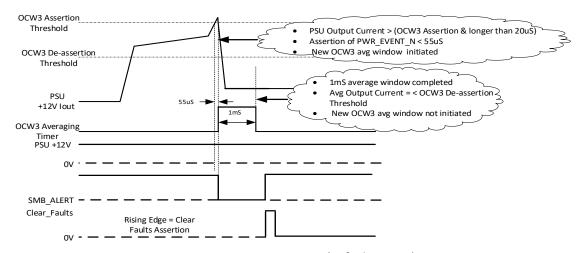

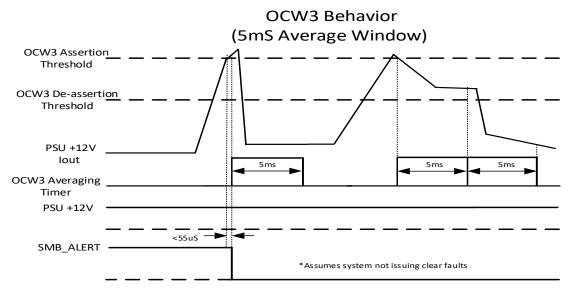

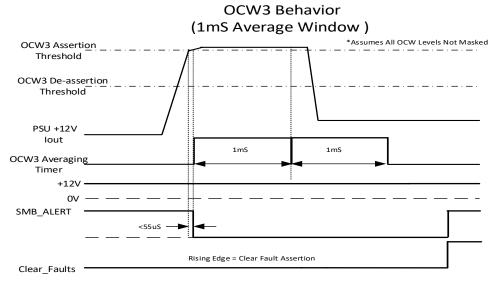

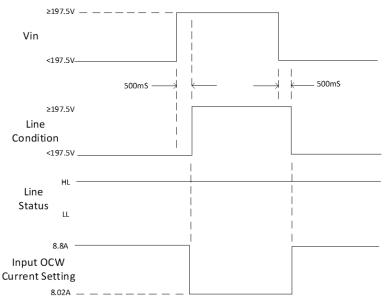

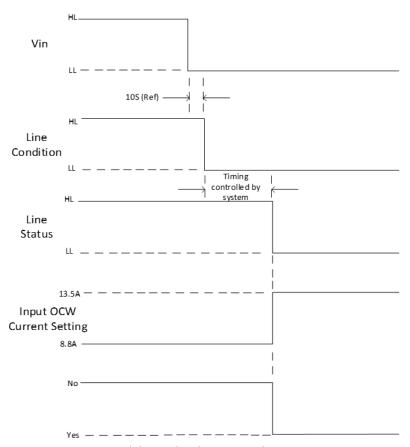

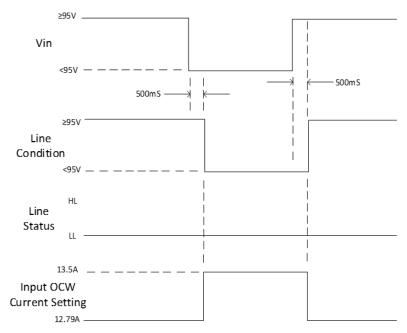

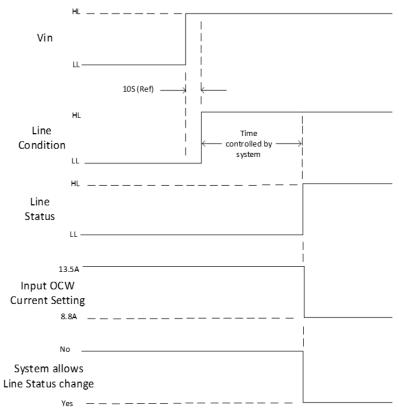

|   | 8.1. |       | Over Current Warning (OCW)                                  |     |

|   | 8.1. | 4     | Over Current Warning Behavioral Timing Diagrams             | 96  |

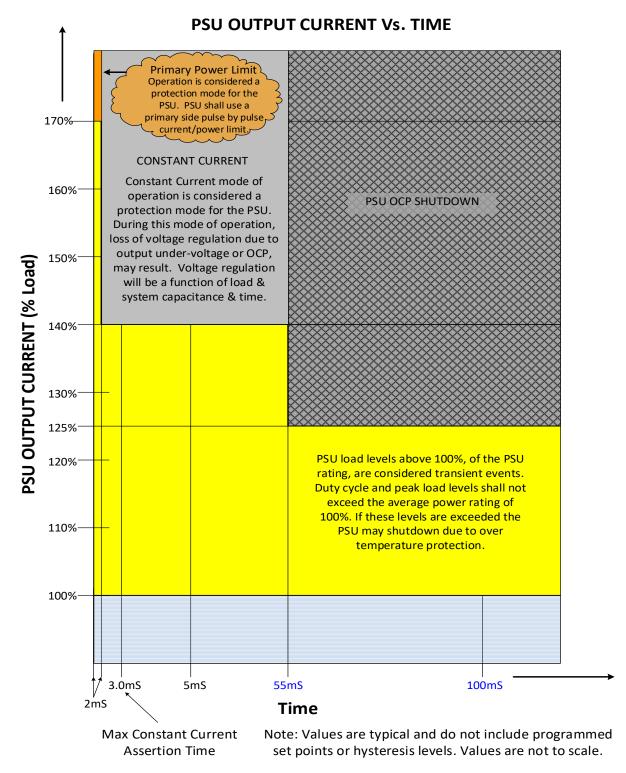

|   | 8.1. | 5     | Over Current Protection & Over Power Protection (OCP & OPP) | 103 |

|    | 8.1.6 |         | Fast Output Current Sensing for Fast Over Current Warning | 107 |

|----|-------|---------|-----------------------------------------------------------|-----|

|    | 8.1.  | .7      | Over Voltage Protection (OVP)                             | 108 |

|    | 8.1.  | .8      | Under Voltage Protection (UVP)                            | 108 |

|    | 8.1.9 |         | Over Temperature Warning (OTW)                            | 108 |

|    | 8.1.  | .10     | Over Temperature Protection (OTP)                         | 108 |

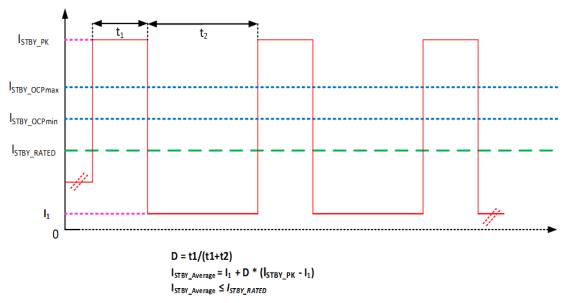

|    | 8.2   | Aux     | iliary (Stand-by) Output                                  | 109 |

|    | 8.2.  | .1      | Over Current Protection Behavior                          | 109 |

|    | 8.3   | Sho     | rt Circuit Protection                                     | 110 |

|    | 8.4   | Inpu    | t Over Current Protection                                 | 110 |

|    | 8.4.  | .1      | Input Over Current Warning – AC Input                     | 110 |

|    | 8.4.  | .2      | Input Over Current Warning – DC Input                     | 111 |

| 9  | Cor   | ntrol a | nd Indicator Functions                                    | 111 |

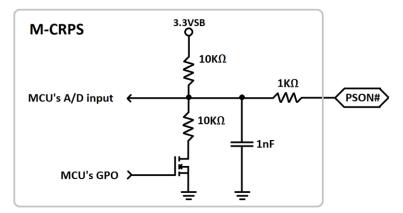

|    | 9.1   | PSO     | N# Signal (Input)                                         | 111 |

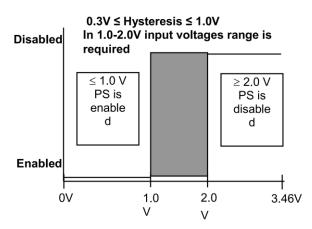

|    | 9.1.  | .1      | Two-State Signal                                          | 111 |

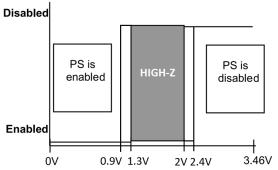

|    | 9.1.  | .2      | Three-State Signal                                        | 112 |

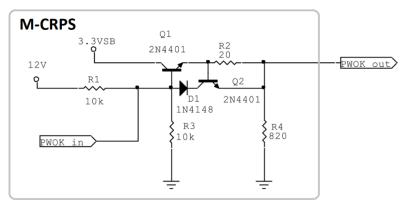

|    | 9.2   | PW      | OK Signal (Output)                                        | 113 |

|    | 9.3   | SME     | 3Alert# Signal (Output)                                   | 114 |

|    | 9.4   | VIN     | OK Signal (Output)                                        | 114 |

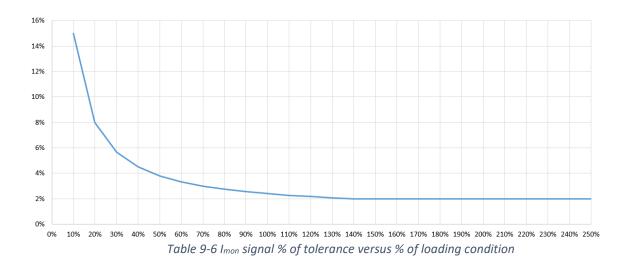

|    | 9.5   | Imo     | n Signal (Output)                                         | 115 |

|    | 9.6   | A0 a    | and A1 Signals (Inputs)                                   | 117 |

|    | 9.6.  | .1      | A0 Input Addressing                                       | 117 |

|    | 9.6.  | .2      | A1 as Data & Sideband Serialization Interface (DSSI)      | 119 |

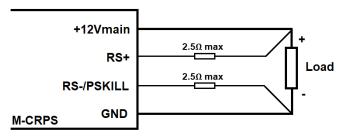

|    | 9.7   | Rem     | note Sense And Return Sense / PSKILL                      | 119 |

| 1( | ) E   | nviro   | nmental Requirements                                      | 119 |

|    | 10.1  | Tem     | perature                                                  | 119 |

|    | 10.2  | Hun     | nidity                                                    | 120 |

|    | 10.3  | Altit   | ude                                                       | 120 |

|    | 10.4  | Med     | chanical Shock                                            | 120 |

|    | 10.5  | Ran     | dom Vibration                                             | 120 |

|    | 10.6  | The     | rmal Shock (Shipping)                                     | 120 |

| 1: | 1 F   | RU R    | equirements                                               | 120 |

|    | 11.1  | FRU     | Data                                                      | 120 |

|    | 11.2  | Dev     | ice Protocol                                              | 120 |

|    | 11.2.1  | Data Format                                                     | 121 |

|----|---------|-----------------------------------------------------------------|-----|

|    | 11.2.2  | Write Protection                                                | 122 |

| 12 | Firmw   | are Requirements                                                | 122 |

| 1  | 2.1 PM  | 3us                                                             | 122 |

|    | 12.1.1  | Related Documents                                               | 122 |

|    | 12.1.2  | Addressing                                                      | 122 |

|    | 12.1.3  | Hardware                                                        | 123 |

|    | 12.1.4  | PMBus Power Sourcing                                            | 123 |

|    | 12.1.5  | Pull Ups                                                        | 123 |

|    | 12.1.6  | Data Speed                                                      | 123 |

|    | 12.1.7  | Bus Errors                                                      | 124 |

|    | 12.1.8  | Additional SMBus hardware requirements                          | 124 |

|    | 12.1.9  | Writing to the power supply                                     | 124 |

|    | 12.1.10 | PAGE                                                            | 124 |

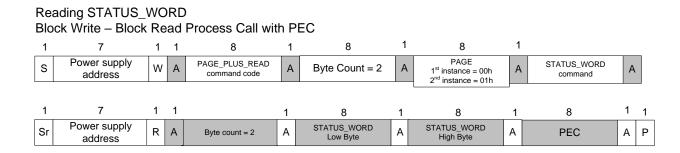

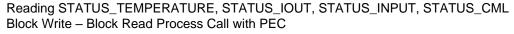

|    | 12.1.11 | PAGE_PLUS_WRITE and PAGE_PLUS_READ (05h/06h)                    | 124 |

|    | 12.1.12 | Sensors                                                         | 125 |

|    | 12.1.13 | Sensor Functionality in Different PSU States and Configurations | 126 |

|    | 12.1.14 | READ_PIN (97h)                                                  | 126 |

|    | 12.1.15 | READ_IOUT (8Ch)                                                 | 127 |

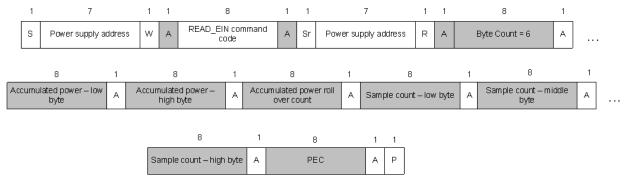

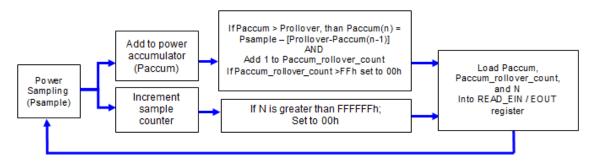

|    | 12.1.16 | READ_EIN (86h)                                                  | 127 |

|    | 12.1.17 | READ_EOUT (87h)                                                 | 128 |

|    | 12.1.18 | READ_EIN & READ_EOUT Formats                                    | 128 |

|    | 12.1.19 | COEFFICIENT (30h)                                               | 130 |

|    | 12.1.20 | Status Commands                                                 | 130 |

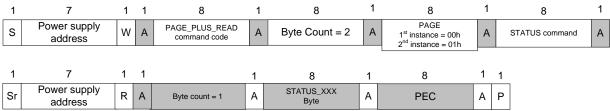

|    | 12.1.21 | Resetting Status Bits                                           | 131 |

|    | 12.1.22 | Default Limits for Warning and Faults                           | 132 |

|    | 12.1.23 | Resetting to Default Limits                                     | 132 |

|    | 12.1.24 | Faults and Error Checking                                       | 132 |

|    | 12.1.25 | Packet Error Checking                                           | 132 |

|    | 12.1.26 | Capability and Inventory Reporting                              | 132 |

|    | 12.1.27 | SMBAlert# Signal                                                | 133 |

|    | 12.1.28 | SMBAlert# Operation in Standby Mode                             | 134 |

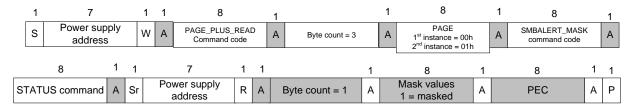

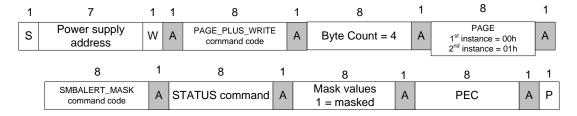

|    | 12.1.29 | SMBALERT_MASK (1Bh)                                             | 134 |

| 12.  | 1.30 | Alert Response Address (ARA)                                               | 134 |

|------|------|----------------------------------------------------------------------------|-----|

| 12.  | 1.31 | Setting and Resetting the SMBAlert# Signal                                 | 134 |

| 12.  | 1.32 | Fan Speed Control                                                          | 135 |

| 12.  | 1.33 | FAN_CONFIG_1_2 (3Ah)                                                       | 135 |

| 12.  | 1.34 | FAN_COMMAND_1 (3Bh)                                                        | 135 |

| 12.  | 1.35 | READ_FAN_SPEED_1 (90h)                                                     | 135 |

| 12.  | 1.36 | PSU Commands Supported For Testing Purposes                                | 135 |

| 12.  | 1.37 | OT_WARN_LIMIT (51h)                                                        | 135 |

| 12.  | 1.38 | IOUT_OC_WARN_LIMIT(4Ah)                                                    | 136 |

| 12.  | 1.39 | Modification to 10.2.6 and 10.3 of PMBus Part II revision 1.2              | 136 |

| 12.  | 1.40 | PMBUS_REVISION                                                             | 136 |

| 12.  | 1.41 | Continuous Assertion After Clearing If Condition Is Still Present          | 136 |

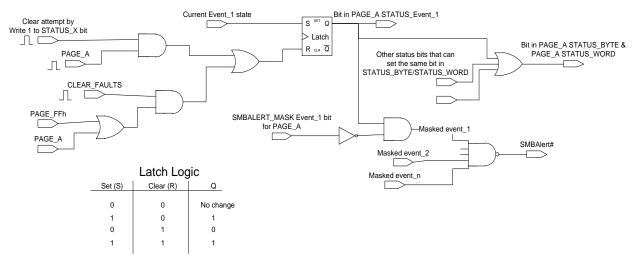

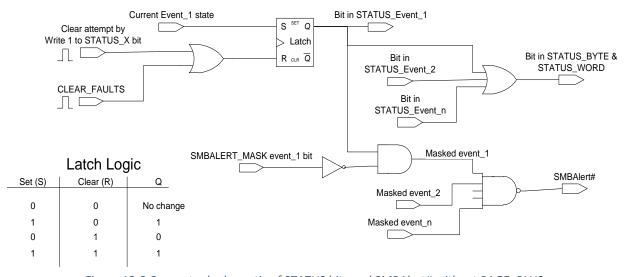

| 12.  | 1.42 | Conceptual View of How Status Bits and SMBAlert# Work                      | 136 |

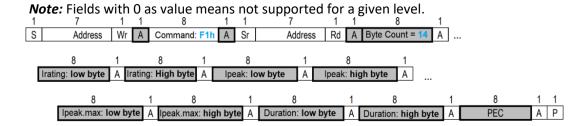

| 12.  | 1.43 | MFR_MAX_IOUT_CAPABILITY (F1h)                                              | 137 |

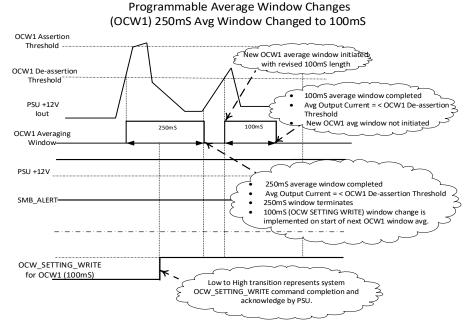

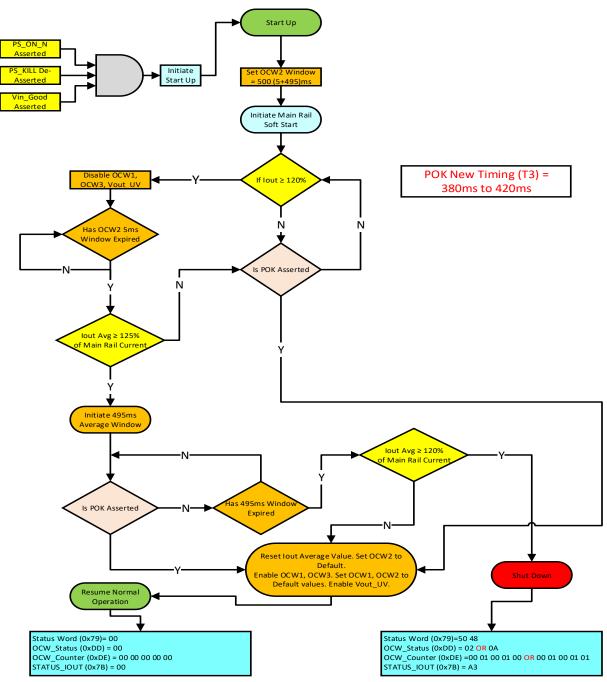

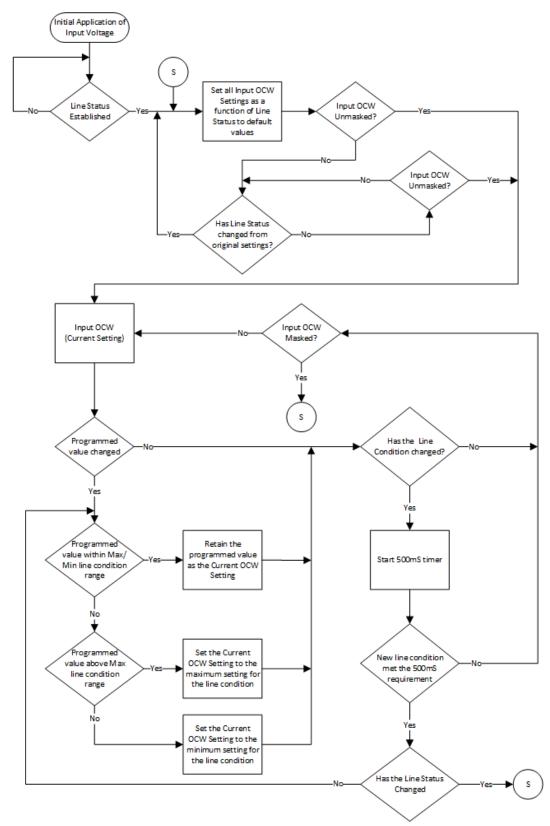

| 12.  | 1.44 | IIN_OC_WARN_LIMIT (5Dh)                                                    | 138 |

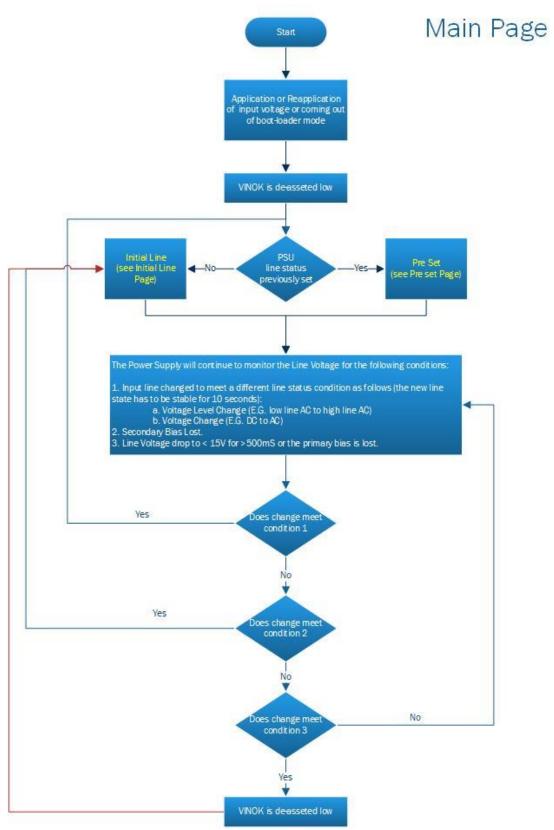

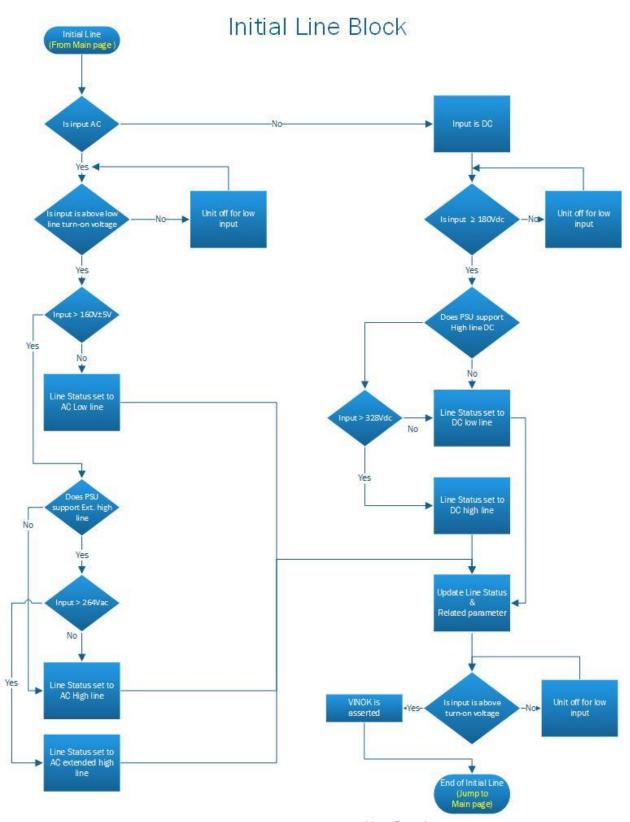

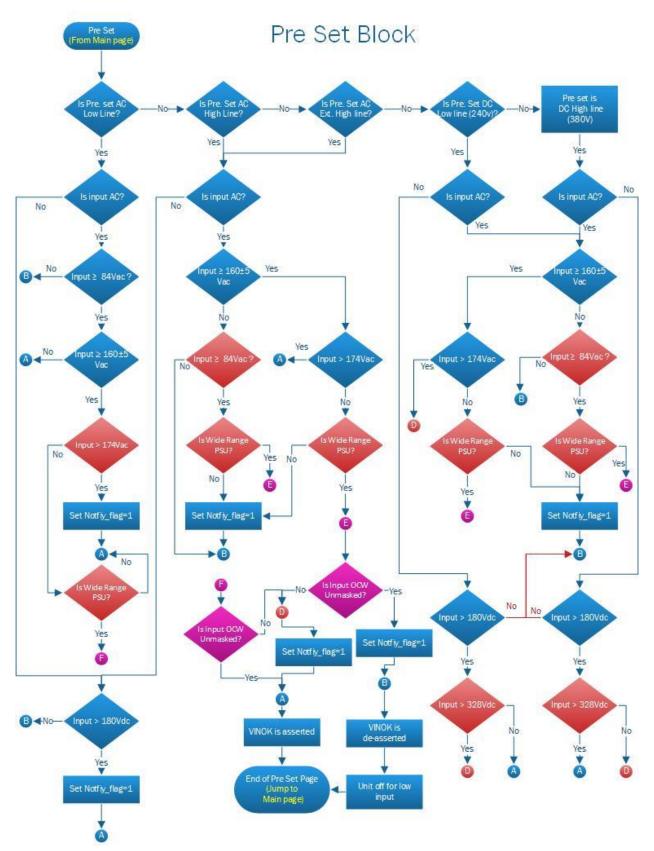

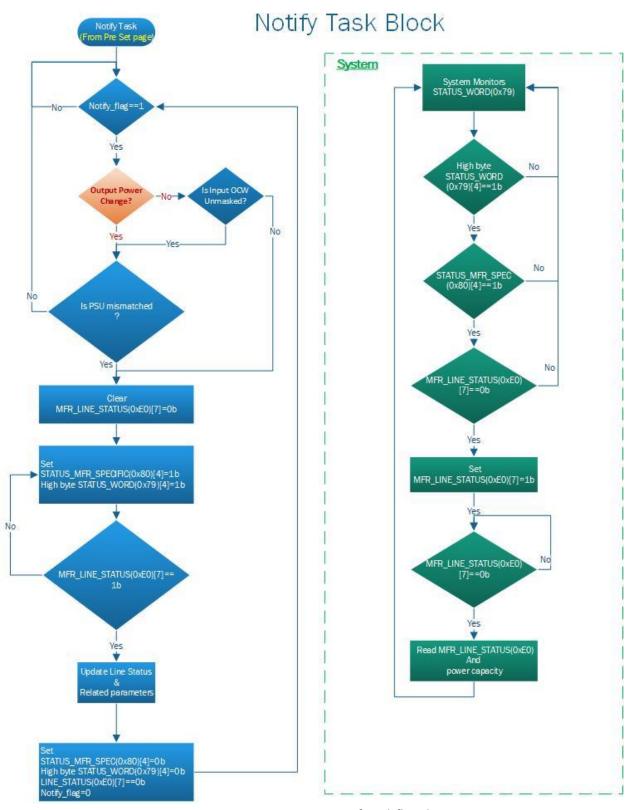

| 12.  | 1.45 | MFR_LINE_STATUS (E0h)                                                      | 144 |

| 12.  | 1.46 | MFR_SYSTEM_LED_CNTL (E1h)                                                  | 153 |

| 12.  | 1.47 | Summary of PMBus commands                                                  | 154 |

| 12.2 | The  | rmal Closed Loop System Throttling (Thermal CLST)                          | 159 |

| 12.3 | Sma  | rt Ride-Through (SmaRT)                                                    | 159 |

| 12.4 | Colo | l Redundancy                                                               | 159 |

| 12.  | 4.1  | Overview                                                                   | 160 |

| 12.  | 4.2  | Cold Standby Power Supply Operating State                                  | 161 |

| 12.  | 4.3  | Powering on Cold Standby Supplies to Maintain Best Efficiency              | 162 |

| 12.  | 4.4  | Powering on Cold Standby Supplies During a Fault or Over Current Condition | 162 |

| 12.  | 4.5  | Cold Redundancy SMBus Commands                                             | 162 |

| 12.  | 4.6  | Cold Redundant Signals                                                     | 163 |

| 12.  | 4.7  | Cold Redundancy Bus (CR_BUS)                                               | 163 |

| 12.  | 4.8  | System BMC Requirements                                                    | 164 |

| 12.  | 4.9  | Power Supply Turn ON Function                                              | 165 |

| 12.5 | In-S | ystem Firmware Upload                                                      | 165 |

| 12.  | 5.1  | FW Image Mapping                                                           | 166 |

| 12.  | 5.2  | Summary of Commands & Capabilities Supported in Bootloader Mode            | 166 |

| 12.5.3   | LED Status                                                   | 167 |

|----------|--------------------------------------------------------------|-----|

| 12.5.4   | Power Supply Operating Mode During and After Firmware Update | 167 |

| 12.5.5   | Firmware Image Header                                        | 167 |

| 12.5.6   | Firmware Update Process                                      | 168 |

| 12.5.7   | Power Supply Commands                                        | 170 |

| 12.6 Bla | ack Box                                                      | 172 |

| 12.6.1   | When is Data Saved to the Black Box?                         | 172 |

| 12.6.2   | Black Box Events                                             | 172 |

| 12.6.3   | Black Box Process                                            | 172 |

| 12.6.4   | Commands                                                     | 173 |

| 12.6.5   | Hardware Requirements                                        | 176 |

| 12.7 Da  | ta & Sideband Serialization Interface (DSSI)                 | 176 |

| 12.7.1   | Physical Layer                                               | 176 |

| 12.7.2   | Default configuration                                        | 177 |

| 12.7.3   | Electrical Characteristics                                   | 178 |

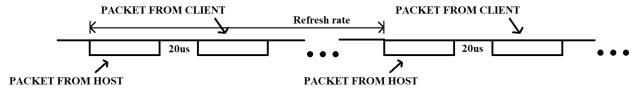

| 12.7.4   | DSSI Protocol Phases                                         | 178 |

| 12.7.5   | Interface Initialization                                     | 179 |

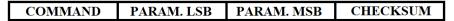

| 12.7.6   | Protocol                                                     | 181 |

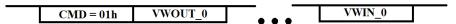

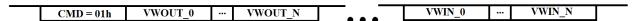

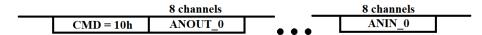

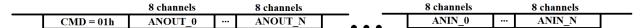

| 12.7.7   | Command Set                                                  | 182 |

| 12.7.8   | Profiles                                                     | 184 |

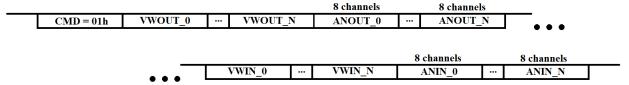

| 12.8 Co  | nfiguration File                                             | 185 |

| 12.8.1   | Overview                                                     | 185 |

| 12.8.2   | Configuration File Header                                    | 187 |

| 12.8.3   | Configuration Area Definition                                | 188 |

| 12.8.4   | Embedded Code Area Definition                                | 193 |

| 12.8.5   | Data Table Area Definition                                   | 194 |

| 12.8.6   | Configuration File Creation                                  | 194 |

| 12.9 Se  | curity                                                       | 194 |

| 12.9.1   | Measurement                                                  | 196 |

| 12.9.2   | Firmware Attestation                                         | 196 |

| 12.9.3   | Device Authentication                                        | 196 |

| 12.9.4   | Code Protection                                              | 196 |

| 13 Relia | bility                                                       | 196 |

|    | 13.1  | Com   | nponent De-Rating                              | 196 |

|----|-------|-------|------------------------------------------------|-----|

|    | 13.2  | Life  | Requirement                                    | 205 |

|    | 13.3  | Mea   | antime Between Failures (MTBF)                 | 206 |

|    | 13.4  | Relia | ability Demonstration Test                     | 206 |

|    | 13.5  | Fan   | Reliability Qualification                      | 206 |

|    | 13.6  | Sold  | ler Assembly Qualification                     | 208 |

|    | 13.7  | Wor   | st Case Electrical Parts Tolerance Analysis    | 209 |

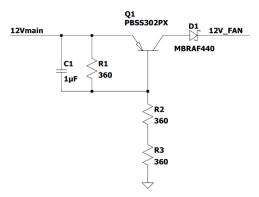

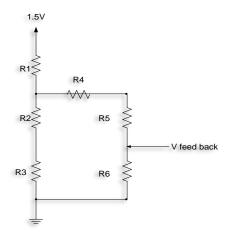

|    | 13.7  | .1    | Circuit Schematic Example                      | 209 |

|    | 13.7  | .2    | Collect Component Datasheets                   | 210 |

|    | 13.7  | .3    | Quantify Component Sources of Variation        | 210 |

|    | 13.7  | .4    | Circuit Transfer Function Determination        | 211 |

|    | 13.7  | .5    | Non-Conforming Circuit                         | 212 |

|    | 13.8  | Stre  | ss Life Test (STRIFE)                          | 213 |

|    | 13.9  | Relia | ability Validation                             | 213 |

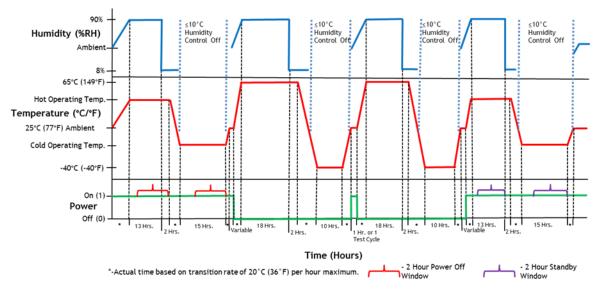

|    | 13.10 | Te    | emperature Humidity                            | 214 |

|    | 13.11 | M     | lechanical Life                                | 214 |

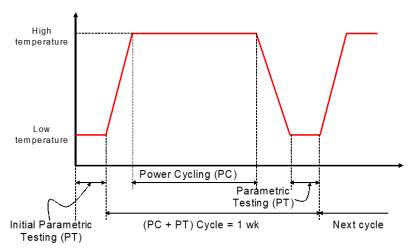

|    | 13.12 | P     | ower Cycling                                   | 214 |

|    | 13.13 | SI    | nock and Vibration                             | 215 |

| 14 | l Re  | egula | tory & Ecology Requirements                    | 216 |

|    | 14.1  | Scop  | oe                                             | 216 |

|    | 14.2  | EMC   | Requirements and Standards                     | 216 |

|    | 14.3  | Safe  | ty Requirements and Standards                  | 216 |

|    | 14.4  | Fire  | and Electrical Enclosure                       | 217 |

|    | 14.4  | .1    | Safeguard Robustness                           | 217 |

|    | 14.5  | Tele  | communications DC Mains Powered Power Supplies | 218 |

|    | 14.6  | Com   | nponents                                       | 218 |

|    | 14.6  | .1    | Flammability requirements                      | 218 |

|    | 14.6  | 5.2   | Capacitors                                     | 219 |

|    | 14.7  | Тур   | e Testing                                      | 222 |

|    | 14.7  | .1    | General                                        | 222 |

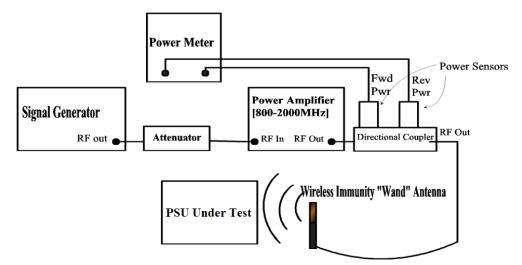

|    | 14.7  | .2    | Wireless GSM Test                              | 222 |

|    | 14.8  | Prod  | duction (Routine) Testing                      | 225 |

|    | 14.8  | .1    | Dielectric Strength Testing                    | 225 |

| 14.8.2 Ground Continuity Testing                                             | 226 |

|------------------------------------------------------------------------------|-----|

| 14.9 Energy Efficiency Requirements and Standards                            | 226 |

| 14.10 Environmental Requirements and Standards                               | 228 |

| 14.11 Applicable RoHS Exemptions                                             | 230 |

| 14.12 Sustainable Materials                                                  | 230 |

| 14.13 EPEAT                                                                  | 230 |

| 14.14 Design for Recyclability                                               | 231 |

| 14.15 Expectation of the Supplier                                            | 232 |

| 14.15.1 Change Notification                                                  | 232 |

| 14.15.2 Required Documentation                                               | 232 |

| 14.15.3 Regulatory Model Designation                                         | 232 |

| 14.16 Compliance Certifications                                              | 233 |

| 15 Quality Assurance                                                         | 235 |

| 15.1 Vendor Responsibility                                                   | 235 |

| 15.1.1 General                                                               | 235 |

| 15.1.2 Scope                                                                 | 235 |

| 15.2 Inspection                                                              | 235 |

| 15.2.1 Responsibility for Inspection/Test                                    | 235 |

| 15.2.2 Inspection and Test Procedure                                         | 236 |

| 15.2.3 Qualification Inspection/Test Procedures                              | 236 |

| 15.2.4 Acceptance Inspection/Test                                            | 236 |

| 15.3 Final Test Data                                                         | 236 |

| 15.4 Rejection and Retest                                                    | 236 |

| 15.5 Corrective Action Program                                               | 236 |

| 15.6 Failure Analysis                                                        | 236 |

| 15.7 Vendor Burn-In                                                          | 236 |

| 15.8 Enhanced Burn-In                                                        | 237 |

| 15.8.1 Preparation for Delivery                                              | 238 |

| Supplemental Material A. 185mm by 73.5mm M-CRPS mechanical drawing           | 239 |

| Supplemental Material B. 185mm by 60mm M-CRPS mechanical drawing             | 245 |

| Supplemental Material C. 265mm by 73.5mm M-CRPS mechanical drawing           | 251 |

| Supplemental Material D. 73.5mm in width M-CRPS card edge mechanical drawing | 258 |

| Supplemental Material F. 60mm in width M-CRPS card edge mechanical drawing   | 265 |

| Supplemental Ma           | aterial F. | M-CRPS handle mechanical drawing                                             | 272      |

|---------------------------|------------|------------------------------------------------------------------------------|----------|

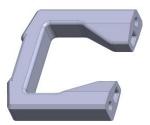

| Supplemental Ma           | aterial G. | M-CRPS latch mechanical drawing                                              | 274      |

| Supplemental Ma           | aterial H. | M-CRPS latch plastic grip option 1 (snap-in version)                         | 276      |

| Supplemental Ma           | aterial I. | M-CRPS latch plastic grip option 2 (over molded version)                     | 278      |

| Supplemental Ma           | aterial J. | 185mm by 73.5mm +54VDC input M-CRPS mechanical drawing                       | 280      |

| Supplemental Ma           | aterial K. | 185mm by 73.5mm -48VDC input M-CRPS mechanical drawing                       | 286      |

| Supplemental Ma           | aterial L. | 185mm by 60mm -48VDC input M-CRPS mechanical drawing                         | 290      |

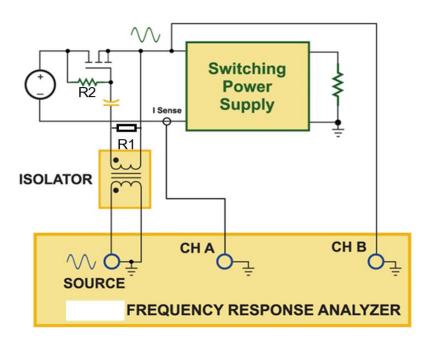

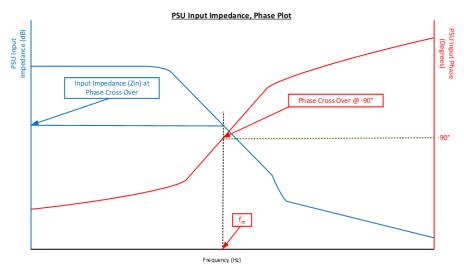

| Supplemental Ma           | aterial M. | DC input impedance measurement procedure                                     | 294      |

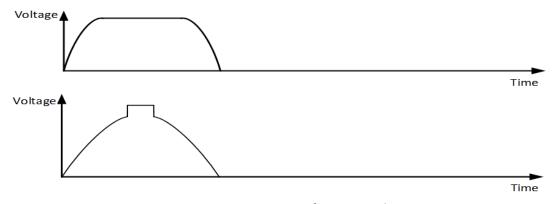

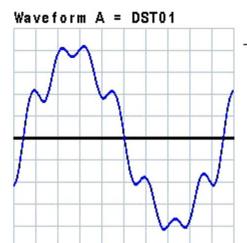

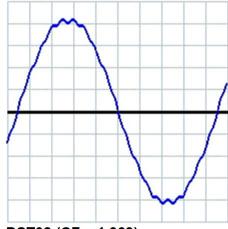

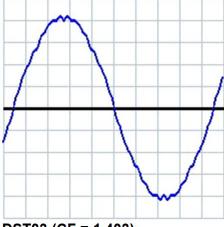

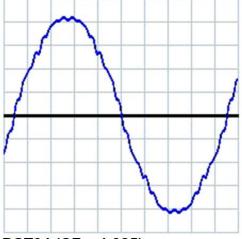

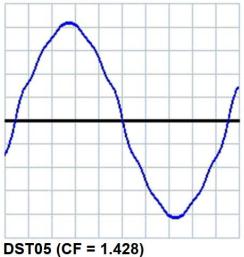

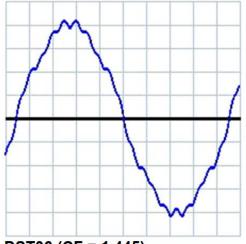

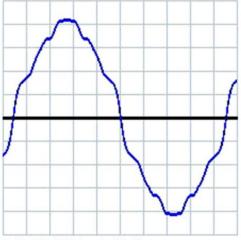

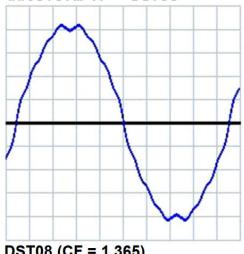

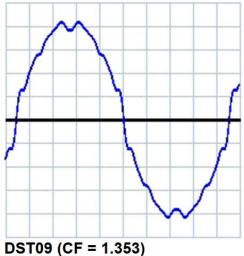

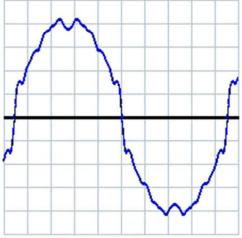

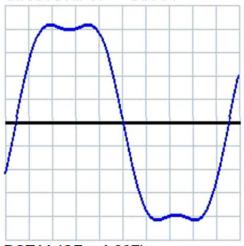

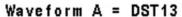

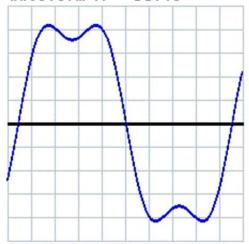

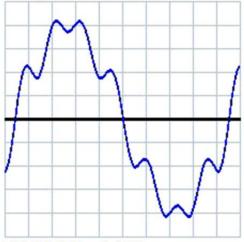

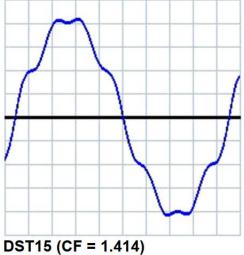

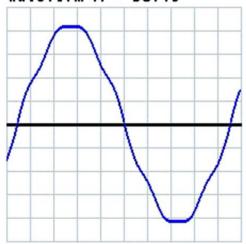

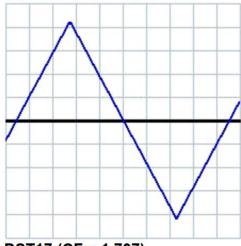

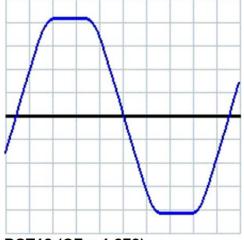

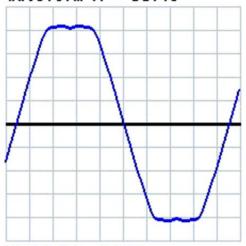

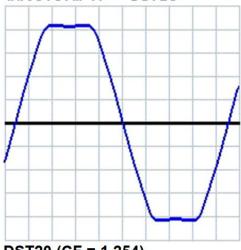

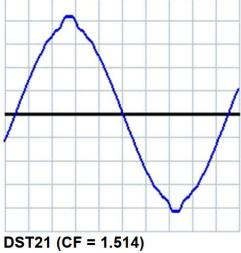

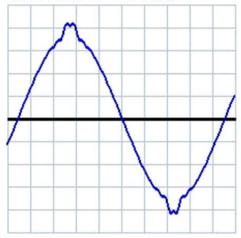

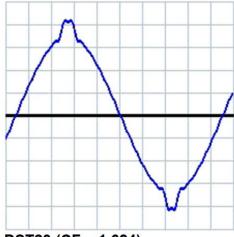

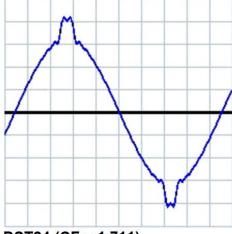

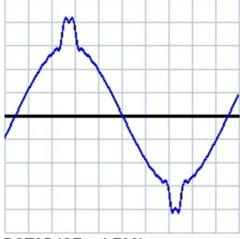

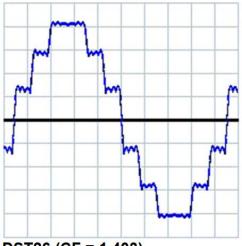

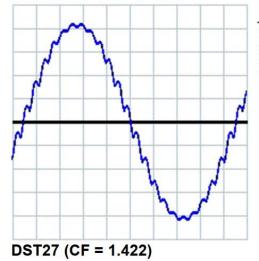

| Supplemental Ma           | aterial N. | Reference Distorted Waveforms                                                | 298      |

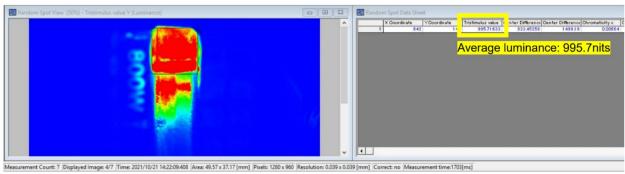

| Supplemental Ma           | aterial O. | Luminosity Measurements                                                      | 309      |

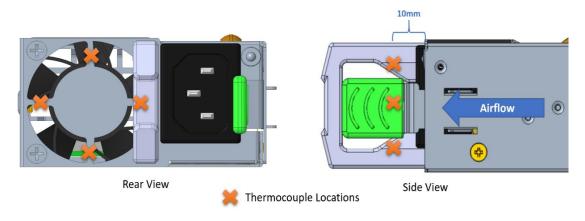

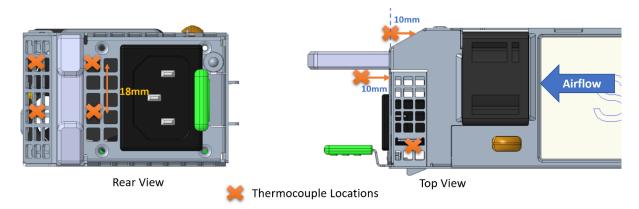

| Supplemental Ma           | aterial P. | Exhaust Temperature Measurement                                              | 311      |

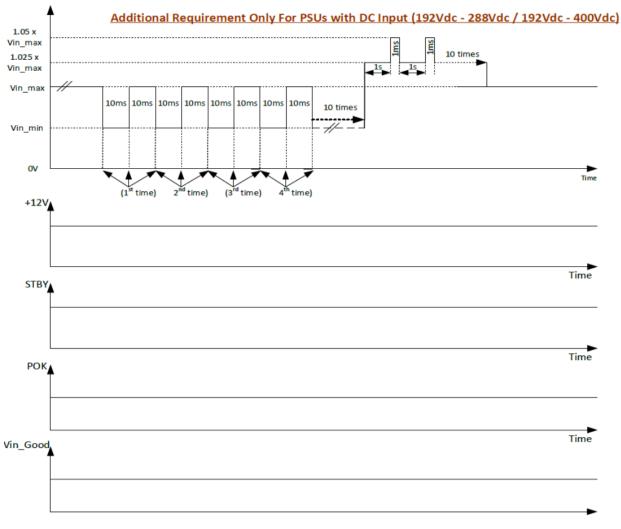

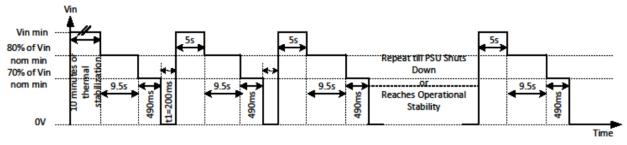

| Supplemental Ma           | aterial Q. | Additional Requirements on Input Line Transients                             | 314      |

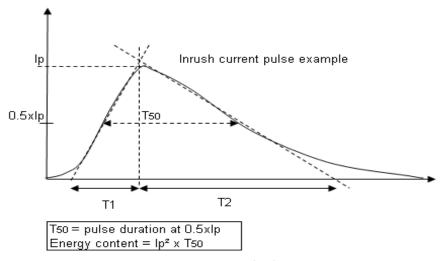

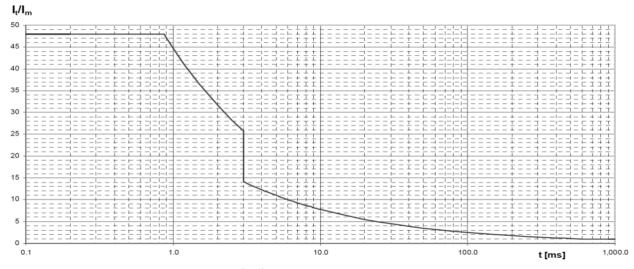

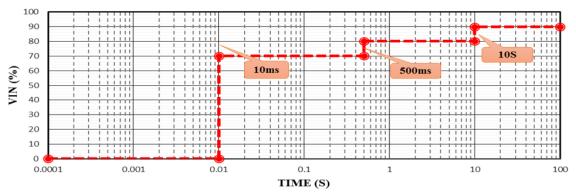

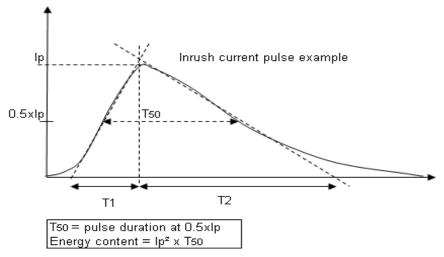

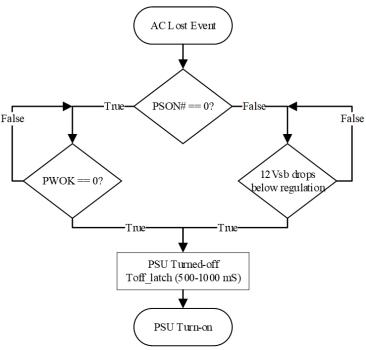

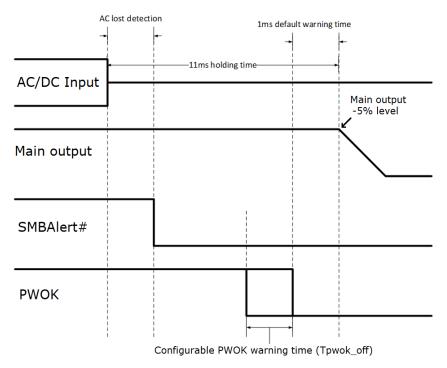

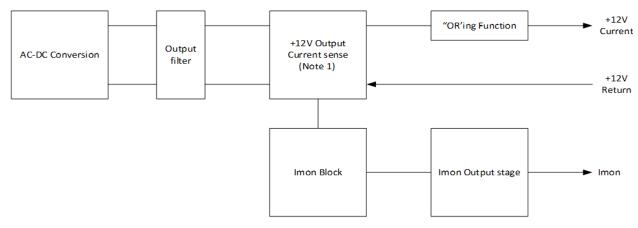

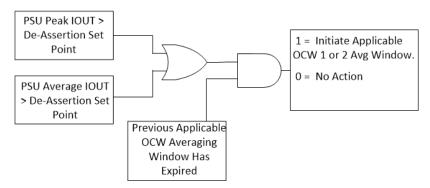

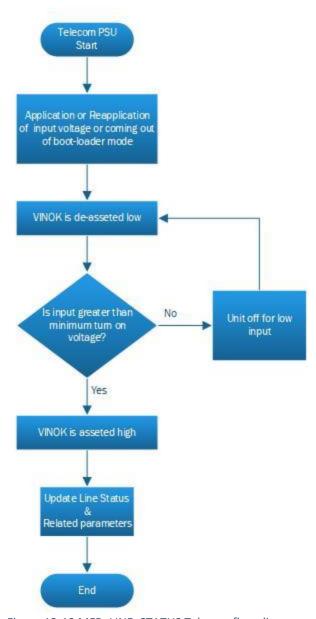

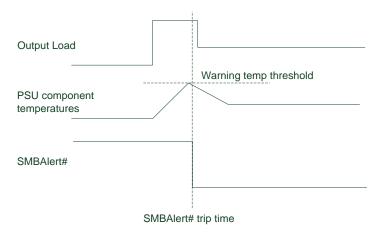

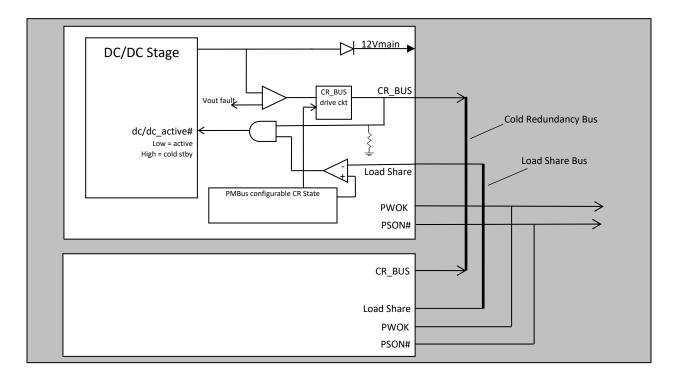

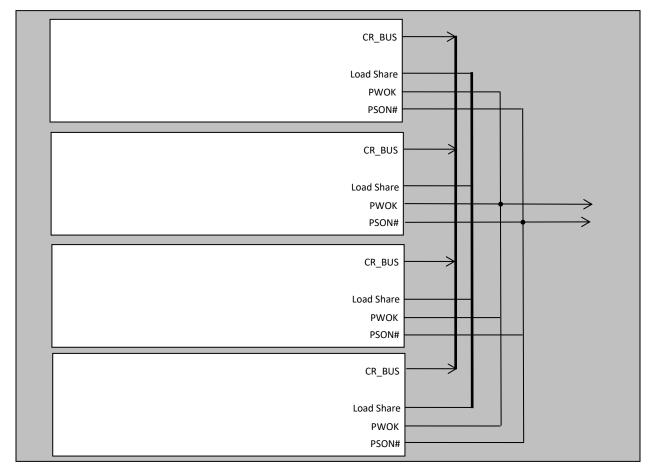

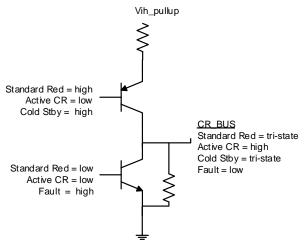

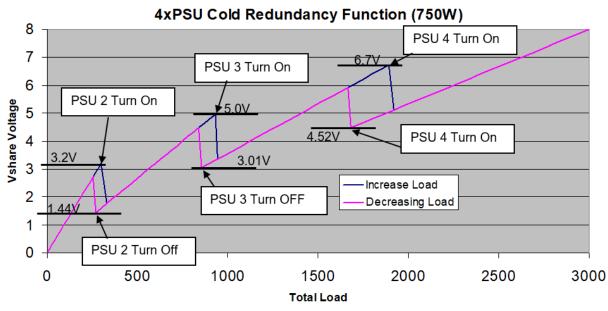

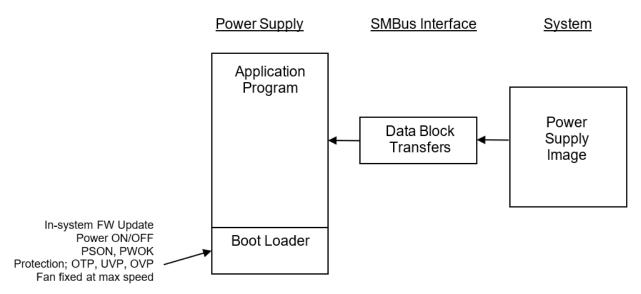

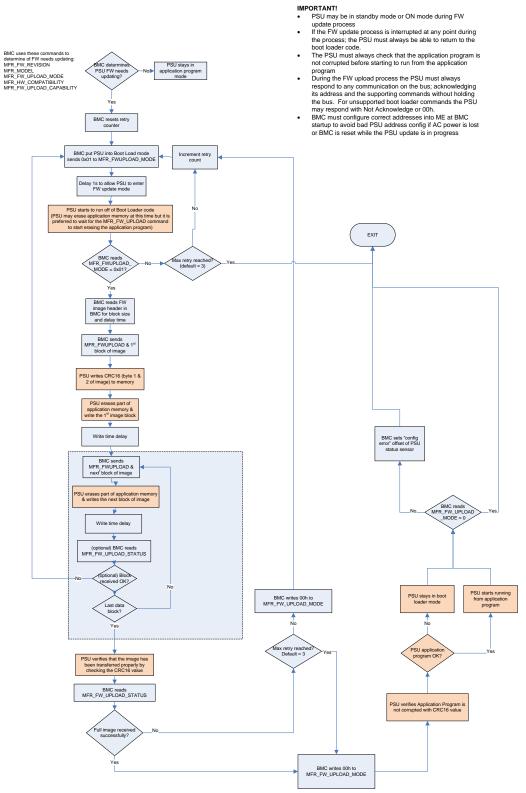

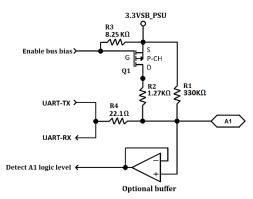

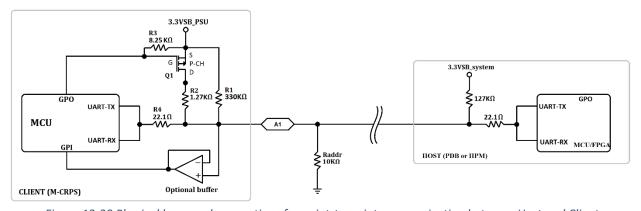

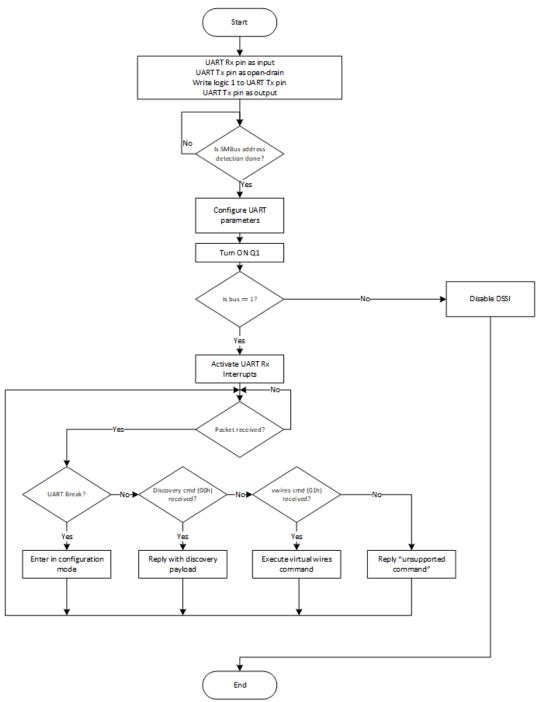

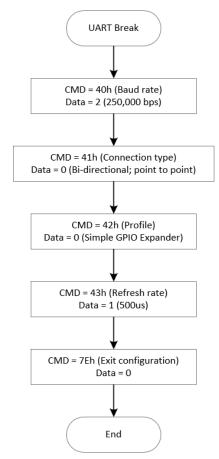

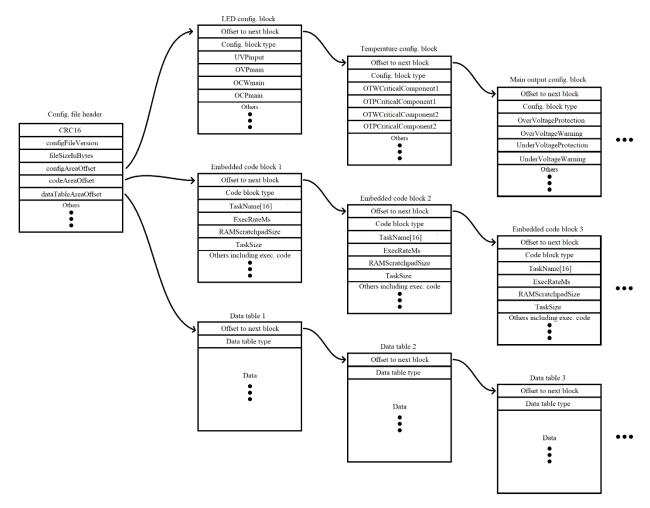

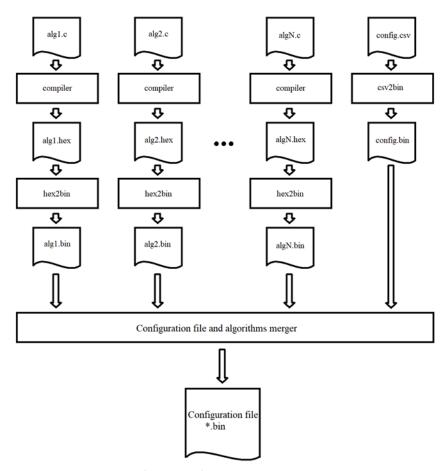

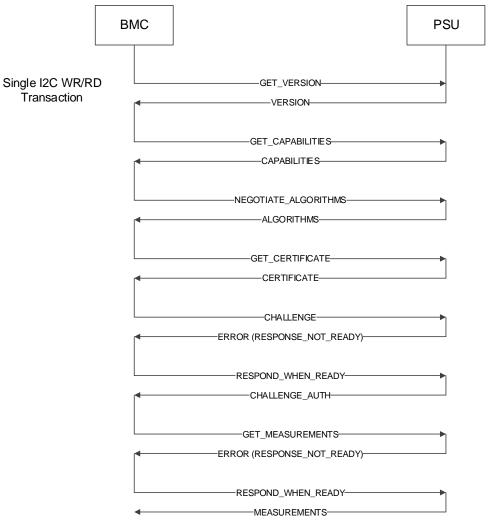

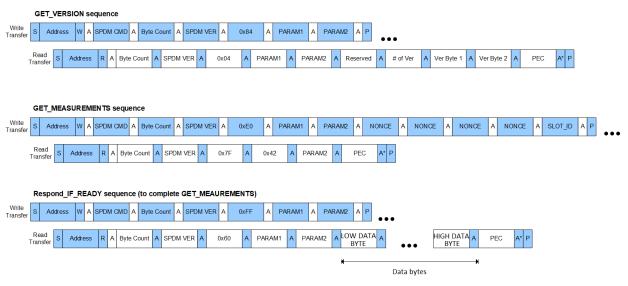

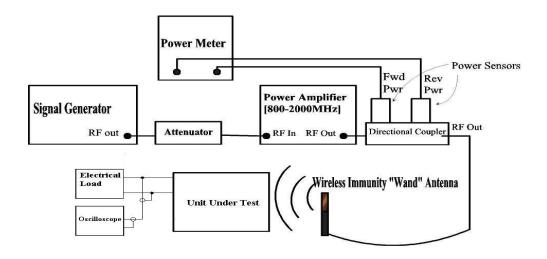

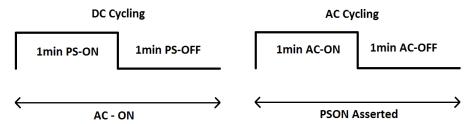

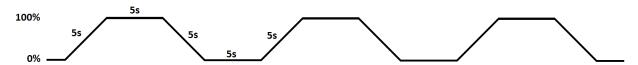

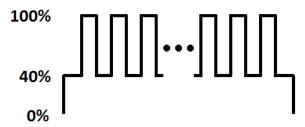

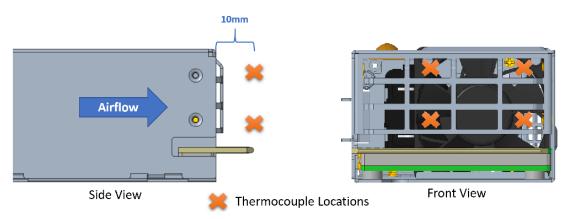

| Appendix A -              | Checklist  | for IC approval of this specification Error! Bookmark not                    | defined. |