# Rev. 1.1

# SwitchX®-2 based 40GbE, 1U Open Ethernet Switch with 36 QSFP+ ports

Author: Shy Zimmerman Rev 1.1

# **Revision History**

| Revision       | Date         | Description of Change                  |  |  |  |

|----------------|--------------|----------------------------------------|--|--|--|

| 1.1 April 2015 |              | Added Section 2.1.1, 2.1.2, 17.1, 17.2 |  |  |  |

| 1.0            | January 2015 | Initial release                        |  |  |  |

# Scope

This document defines the technical specifications for the MSX1710-OCP switch used in the Open Compute Project

# Contents

| Revision History2                     |

|---------------------------------------|

| Scope                                 |

| Contents                              |

| Overview                              |

| License                               |

| 1 Abbreviations                       |

| 2 Mechanical Drawings                 |

| 2.1 Mechanical System Overview        |

| 2.2 Switch Dimensions (in mm)9        |

| 3 System Feature List                 |

| 3.1 Management Board Feature List     |

| 3.2 Switch Board Feature List         |

| 4 Block Diagram                       |

| 5 Ethernet interface                  |

| 5.1 SwitchX-2                         |

| 5.2 Port Mapping                      |

| 6 QSFP Interface                      |

| 6.1.1 Port over Current Protection    |

| 6.1.2 Port I <sup>2</sup> C Interface |

| 6.1.3 I <sup>2</sup> C                |

| 7 CPLD                                |

| 7.1 CPLD Features                     |

| 7.2 CPLD Field Upgrade                |

| 8 SPI and Safe BIOS Mechanism         |

| 9   | Ethe                    | ernet                             |  |  |  |  |  |

|-----|-------------------------|-----------------------------------|--|--|--|--|--|

| 10  | RS232 Interface         |                                   |  |  |  |  |  |

| 11  | USE                     | 3                                 |  |  |  |  |  |

| 12  | LPC                     | 28                                |  |  |  |  |  |

| 13  | SAT                     | A29                               |  |  |  |  |  |

| 14  | PCI                     | ə                                 |  |  |  |  |  |

| 15  | Pow                     | ver                               |  |  |  |  |  |

| 15. | 1                       | Power Consumption                 |  |  |  |  |  |

| 15. | 2                       | Power Monitoring and Distribution |  |  |  |  |  |

| 16  | FRL                     | Js                                |  |  |  |  |  |

| 16. | 1                       | Power Supply Units                |  |  |  |  |  |

| 16. | 2                       | Fan Units                         |  |  |  |  |  |

| 16. | 3                       | FRU Control                       |  |  |  |  |  |

| 17  | Res                     | et                                |  |  |  |  |  |

| 18  | Tem                     | perature Monitor                  |  |  |  |  |  |

| 19  | Cloc                    | ks                                |  |  |  |  |  |

| 19. | 1                       | Switch Board Clocks               |  |  |  |  |  |

| 19. | 9.2 MGMT Board Clocks45 |                                   |  |  |  |  |  |

| 20  | 20 LEDs                 |                                   |  |  |  |  |  |

| 21  | 21 JTAG                 |                                   |  |  |  |  |  |

| 21. | 1                       | Testing I <sup>2</sup> C GPIO     |  |  |  |  |  |

| 22  | 22 Compliancy           |                                   |  |  |  |  |  |

# Overview

The MSX1710-OCP Ethernet system provides the highest performing fabric solution by delivering high bandwidth and low latency to Enterprise Data Centers (EDC), High-Performance Computing (HPC) and Embedded environments.

The SX1710 Ethernet system switch family delivers up to 2.88Tb/s of non-blocking throughput to HPCs, high frequency trading and EDCs, with ultra-low-latency. It has 36 40GbE ports, that when connected to Mellanox NICs with Mellanox cables and adapters, give you the optimal end-to-end solution for Ethernet Data-Centers.

# License

As of May 25, 2015, the following persons or entities have made this Specification available under the Open Compute Project Hardware License (Copyleft) Version 1.0 (OCPHL-R), which is available at <a href="http://www.opencompute.org/community/get-involved/spec-submission-process/">http://www.opencompute.org/community/get-involved/spec-submission-process/</a>

Mellanox, Inc.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# **Semiconductor Devices Licenses**

All semiconductor devices that may be referred to in this specification, or required to manufacture products described in this specification, will be considered referenced only, and no intellectual property rights embodied in or covering such semiconductor devices shall be licensed as a result of this specification or such references.

Notwithstanding anything to the contrary in the CLA, the licenses set forth therein do not apply to the intellectual property rights included in or related to the semi without limitation the reference to devices listed below. For clarity, no patent claim that reads on such semiconductor devices will be considered a "Granted Claim" under the applicable Contributor License Agreement for this specification.

| Manufacturer | Description                                                                |

|--------------|----------------------------------------------------------------------------|

| Mellanox     | SwitchX-2, 36 Port 40GbE Switch IC<br>MT51136A2-CLCR-B                     |

| Lattice      | CPLD 4320LUT 3.3V<br>LCMXO2-4000HC-4BG332CCA2                              |

| Intel        | C QM77 EXPRESS CHIPSET<br>BD82QM77-SLJ8A                                   |

| Intel        | IC CPU 1047UE 2M 1.40GHZ<br>AV8063801116300-SR10E                          |

| Intel        | IC GIGABIT ETHERNET CONTROLLER 82583<br>WG82583V-SLGVD                     |

| Windbond     | MEMORY FLASH SPI SERIAL 32MBIT 4KBYTEX1024 W25Q32FVSSIGT                   |

| Windbond     | MEMORY FLASH SPI SERIAL 64MBIT 4KBYTEX2048 W25Q64FVSSIGT                   |

| Windbond     | SUPER IO LPC INTERFACE WITH UART<br>NCT5577D                               |

| Intel        | LHA5 "LEWISVILLE" GIGABIT ETHERNET LAN CONTROLLER HURON<br>WG82579LM-SLHA6 |

| INNODISK     | MODULE MSATA SSD 16GB MLC 070<br>DEMSR-16GD07SC2DC-92                      |

| APACER       | MODULE SO-DIMM DDR3 ECC 4GB 1600MBS 800MHZ SDRAM 204PIN<br>78.B2GCS.AT00C  |

### 1 Abbreviations

ToR – Top of Rack Switch

MNG – Management

SWB – Switch Board

FRU – Field Replaceable Unit

PWR - Power

- HS High Speed

- SE Single Ended

OCP - Open Compute Project

WD – Watch Dog

# 2 Mechanical Drawings

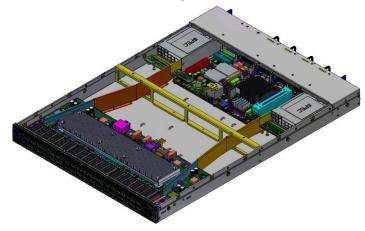

# 2.1 Mechanical System Overview

Figure 1 - Mechanical System Overview

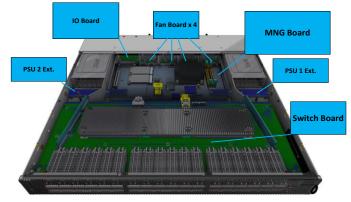

Figure 2 – Main Components

| PCB Function | PCB Layer # | Dimensions  |

|--------------|-------------|-------------|

| Switch Board | 18          | 413 x 186   |

| MNG Board    | 16          | 250 x 134   |

| IO Board     | 4           | 51 x 80.7   |

| FAN Board    | 2           | 40.2 x 18.7 |

| PSU Extender | 4           | 127 x 25    |

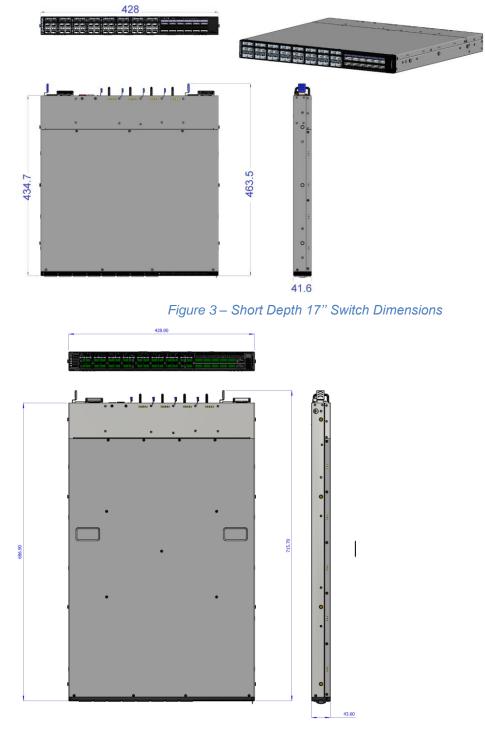

# 2.2 Switch Dimensions (in mm)

Figure 4 – Long Depth 27" Switch Dimensions

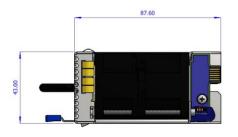

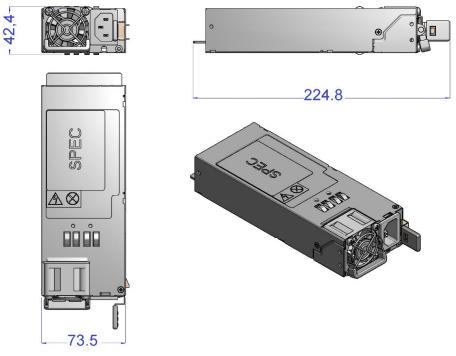

# Fan Unit Dimensions (in mm)

Figure 5: Fan Unit Dimensions

# 2.2.2Power Supply Dimensions (in mm)

# 3 System Feature List

The SX1710 system supports the following features:

#### Managed and Unmanaged Systems

- 1 + 1 redundant 460W AC/DC hot swappable power supplies

- 3 + 1 redundant dual fan units (supports IN/OUT Airflow)

- External I<sup>2</sup>C connector (shard with RS232 connector in managed systems)

- Reset Push button on front & back panel (only FRU PB side will be assembled)

- Front/back panel indication LEDs

- FRU EEPROM on:

- All FRUs

- MNG Board

- Switch board

- JTAG support in fully assembled system

#### Managed Systems Only

- 2 x 10/100/1000BASE-T RJ-45 Ethernet external ports

- 1 x USB external connector

- RS-232 external connector

- 4X PCIE up to Gen2 interface between MNG and switch board

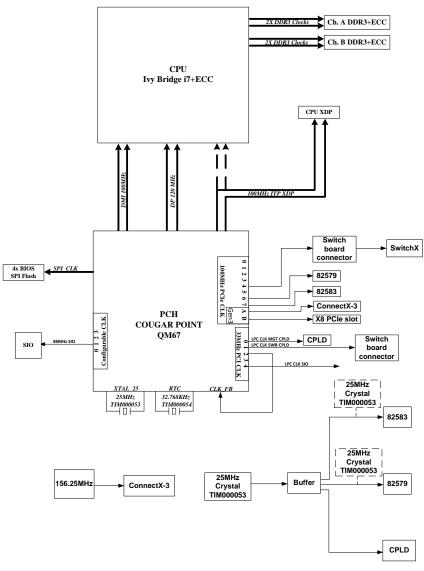

# 3.1 Management Board Feature List

#### Managed Systems Only

- CPU: Intel Ivy Bridge (1047UE in the basic version)

- Chipset: Intel QM77 (Panther Point)

- X8 PCIe GEN3 from CPU to PCIe slot connector\*\* (not supported in the basic version)

- Up to two 1333MTs, 8GB (Each), DDR3, ECC SO-DIMM modules (1X4G in the basic version)

- Supports up to 2 mSATA 4/8/16/64GB SLC or MLC SSD modules (1X16G MLC in the basic version)

- 2 SPI flash memory chips, 64Mb each, for BIOS code

- 2 additional SPI flash chips, 64Mb each, for BIOS FU fail safe support

- BIOS field upgrade

- Real Time clock 24H-SuperCap (optional battery)

- Assembly option for Connect-X3 as bridge between the CPU and SwitchX-2 (not supported in the basic version)

- Super cap for SSD surprise power off (not supported in the basic version)

- No internal graphic core

\*\*Gen3 is supported only with i5 or i7 CPU

#### Managed and Unmanaged Systems

- CPLD with field upgrade and Fail Safe capabilities

- Fan control

- AC/DC power supplies control

### **3.2 Switch Board Feature List**

- Supports 36 SR4\LR4\ACC\DAC QSFP ports up to 56Gbps

- Based on Mellanox SwitchX-2

- 2 SPI flash chips 32Mbit, for SwitchX-2 image

- 2 CPLDs with field upgrade and fail safe capabilities

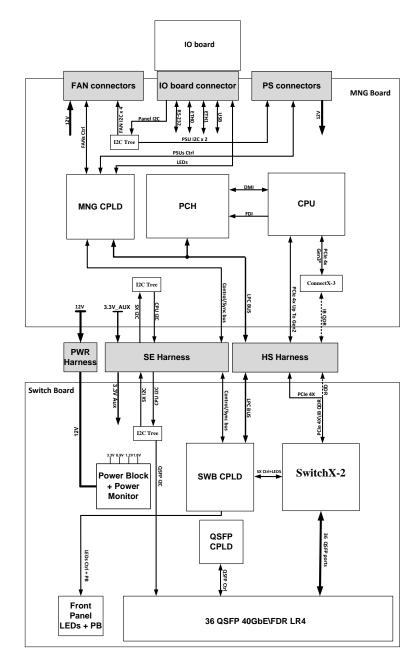

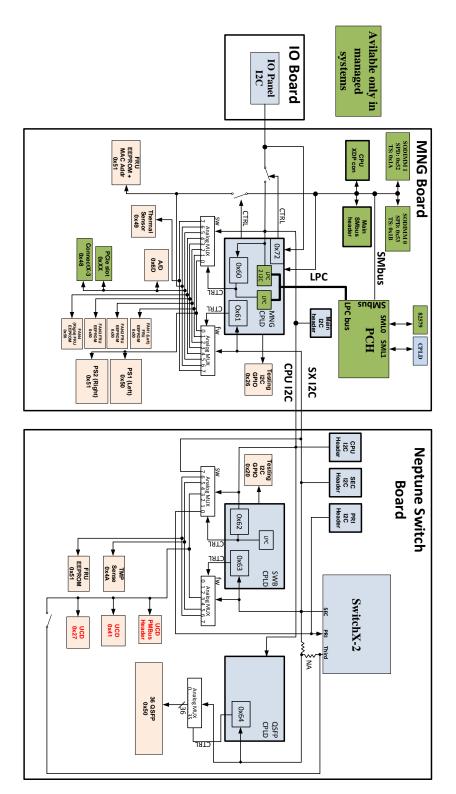

# 4 Block Diagram

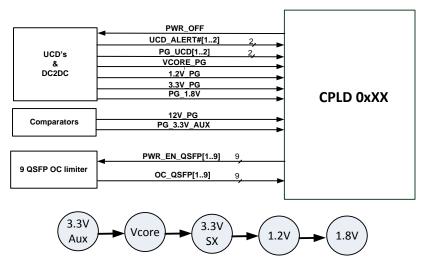

SX1710 is a SwitchX-2 based system with 36 QSFP ports (40GbE). The SwitchX-2 firmware image is stored in 2 SPI flash modules. All QSFP I/Os are controlled by CPLD on the switch board. SwitchX-2 is connected to the CPU via a 4-lane PCIe bus (in managed systems). Most of the control signals on the MGMT board and switch board are controlled by on board CPLD.

Figure 7: System Block Diagram

### 5 Ethernet interface

# 5.1 SwitchX-2

SwitchX-2 is Mellanox's fifth generation switch device, supporting Mellanox's Virtual Protocol Interconnect® (VPI) technology, and enabling converged and virtualized I/O over Ethernet. SwitchX-2 provides 144 network SerDes that can be configured in various combinations of network ports, running multiple standards at several speed options, such as 10, 20, 40 GbE (1X/2X/4X lanes) and 10, 20, 40 Gb/s (1X/4X lanes).

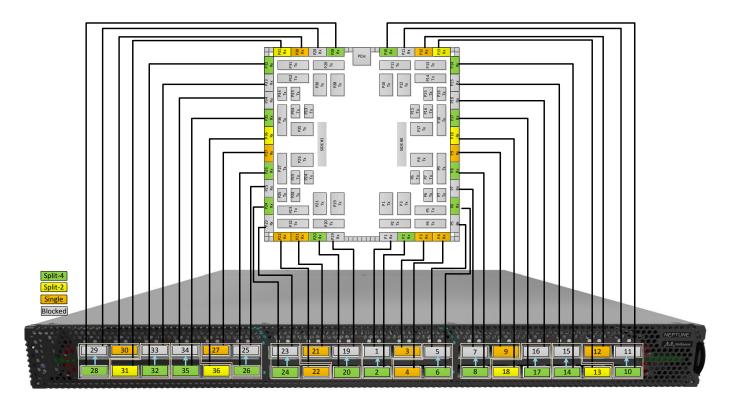

### 5.2 Port Mapping

The SX1710 switch system includes 36 ports of 40GbE that are reaching towards the panel from the SwitchX-2. The switch supports up to 64 different MACs in different combinations, enabled by the use of split cables.

<u>Figure 8</u> shows the split options marked in different colors, while each split-4 (green) port is blocking the port above it (gray ports). <u>Figure 8</u> also shows the general fan-out of the high speed signals on the SX1710 board.

Figure 8: Ports Mapping

| Panel Port | HW Port | Panel Port | HW Port |

|------------|---------|------------|---------|

| 1          | 29      | 19         | 1       |

| 2          | 28      | 20         | 2       |

| 3          | 30      | 21         | 3       |

| 4          | 31      | 22         | 4       |

| 5          | 33      | 23         | 5       |

| 6          | 32      | 24         | 6       |

| 7          | 34      | 25         | 7       |

| 8          | 35      | 26         | 8       |

| 9          | 27      | 27         | 9       |

| 10         | 36      | 28         | 18      |

| 11         | 25      | 29         | 16      |

| 12         | 26      | 30         | 17      |

| 13         | 23      | 31         | 15      |

| 14         | 24      | 32         | 14      |

| 15         | 21      | 33         | 12      |

| 16         | 22      | 34         | 13      |

| 17         | 19      | 35         | 11      |

| 18         | 20      | 36         | 10      |

#### Table 2 specifies the SX1710 4X port mapping.

Table 2: SX1710 Port Mapping

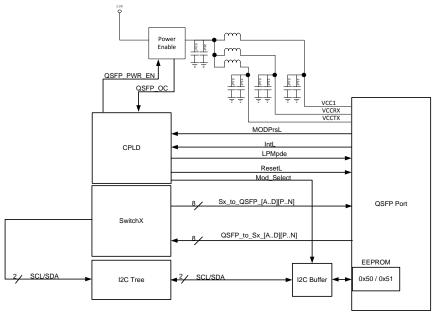

### 6 **QSFP** Interface

The SX1710 system has 36 ports of QSFP connectors. Each QSFP connector supports the following:

| Signal Name | Description                                                                             | Туре                                                                             |

|-------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| TD+/TD-     | High Speed Transmission pairs (x4)                                                      | CML from SwitchX-2 to connector                                                  |

| RD+/RD-     | High Speed Receive pairs (x4)                                                           | CML from connector to SwitchX-2                                                  |

| SCL/SDA     | I <sup>2</sup> C slave interface<br>address 0x50                                        | Open Drain from SwitchX-2 to<br>connector                                        |

| ModSel      | Module select for I <sup>2</sup> C communication to prevent bus conflicts               | In module: short to GND<br>MOD_SEL register in CPLD selects<br>between the ports |

| ResetL      | Module reset use to reset all user module settings to their default state               | LVTTL from CPLD to connector                                                     |

| IntL        | Used to indicate the host for a fault or critical status                                | OC from Connector to CPLD                                                        |

| ModPrsL     | Module present                                                                          | Shorted to GND in module                                                         |

| LPMod       | When the module is in a low power<br>mode it has a maximum power<br>consumption of 1.5W | This signal is floating in the board                                             |

#### Table 3: QSFP Interface

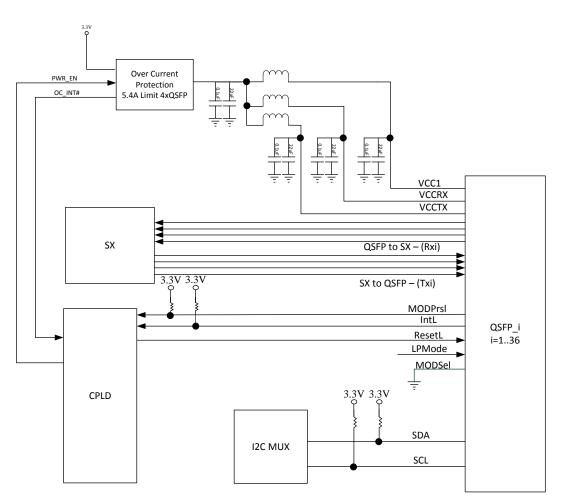

A single QSFP interface in the MSX1410-OCP board is presented in the figure below.

Figure 9 : QSFP Interface

### **6.1.1 Port over Current Protection**

The power for all 4 QSFP modules is controlled by a 5.4 Amperes current, limited power distribution switch. All of these power limiting switches are controlled by QSFP\_PWR\_EN[1..9] signals (default enabled), originated from the CPLD.

When the output load exceeds the current limit threshold, the power switch limits the current to a safe level. In addition, the QSFP\_OVER\_CURRENT[1..9] signals are asserted low, in order to notify of the condition to the CPU interrupt registers and to the SwitchX-2 interrupt register. Figure 10 describes a single QSFP interface in the SX1710 board.

Figure 10: Port over Current Protection

### 6.1.2Port I<sup>2</sup>C Interface

CPLD controls the I<sup>2</sup>C switch and connected to SwitchX-2 secondary I<sup>2</sup>C bus. 60 different I<sup>2</sup>C buses are connected from I<sup>2</sup>C switch to the 60 MSX1410-OCP ports. MOD\_SEL register selects which I<sup>2</sup>C bus will be open- each time only one bus can be open.

The main reason for using this CPLD buffering method is that all the QSFP modules have the same address (0x50). By separating the buses in the CPLD, Switch-X2 can select a specific module to communicate with. Another reason for selecting a different bus for each port is to isolate problematic modules from the others. This way, if a specific port is corrupted, it does not affect the other ports.

# 6.1.3I<sup>2</sup>C

- The SX1710 I<sup>2</sup>C tree contains 4 masters:

- 1. SW (LPC to I<sup>2</sup>C module)

- 2. FW (SwitchX-2)

- 3. External connector for testing/FAE

- 4. BIOS (SMbus)

- The PCH does not support I<sup>2</sup>C. Therefore, an LPC to I<sup>2</sup>C module was implemented in the MGMT CPLD.

- I<sup>2</sup>C switching is done by external analog MUX devices. These devices are controlled by I<sup>2</sup>C/LPC registers inside the CPLD.

- FW general I<sup>2</sup>C switching is controlled via 0x61 and 0x63 by writing the channel number into the relevant register. FW ports' I<sup>2</sup>C switching is controlled via 0x64 by writing "1" to the relevant "ModSel" bit. There is one "ModSel" bit per port and only one can be "1".

- SW I<sup>2</sup>C switching is controlled via LPC through dedicated registers in the SW reg. map

- The SW master and the connector master share the same MUX and the same head of tree.

- The I<sup>2</sup>C connector is not connected directly to the head of the SW tree. When connection between the connector and the head of the tree is required, it must be opened via the 0X80 device inside the CPLD.

- When connection between the connector and the head of the tree is enabled, the SW I<sup>2</sup>C connection to the head of the tree is disabled.

- In case of collision between masters, the following hierarchy will be implemented (decreasing order):

- 1. Connector

- 2. SW I<sup>2</sup>C register

- 3. SW LPC register

- 4. FW

- The I<sup>2</sup>C and the RS232 share the same RJ45 connector on the I/O board.

- CPLD I<sup>2</sup>C slave modules 0x61, 0x63 and 0x64 are "Two Byte Address" modules. The rest of the CPLD modules are "One Byte Address modules".

- Sequential read and write modes are supported by all CPLD I<sup>2</sup>C modules.

Figure 11: I<sup>2</sup>C Tree

# 7 CPLD

Three CPLD devices on the SX1710 provide monitoring and controlling capabilities:

- MGMT CPLD (CPLD1): located on the MGMT board, controls most of the board's SE signals, fans, PS, power sequence, most of the SW registers, a few FW registers, SW interrupt, FW interrupt, reset, I<sup>2</sup>C switching, safe BIOS etc.

- Switch board MGMT CPLD (CPLD2): located on the switch board, responsible for all board peripheries such as LEDs, reset logic, power monitor, I<sup>2</sup>C switching, SW registers, FW registers etc.

- 3. QSFP CPLD (CPLD3): located on the switch board, controls and monitors the QSFP ports this CPLD is mainly controlled by the SwitchX-2. LPC is not connected to this CPLD and therefore, it cannot contain SW registers.

The CPLD codes contain various modules for board control. One of the main modules is the R/W registers for SW and FW control. The registers list with their functionality is presented in the register map documents.

For CPLD registers that are controlled via SW (CPU controlled via LPC), please refer to SX1710 CPLD SW registers map document.

For CPLD registers that are controlled via FW (SwitchX controlled via I<sup>2</sup>C), please refer to SX1710 CPLD FW registers map document.

CPLD 1 and 2 are connected via a 3-signal sync serial bus. The CPLDs are syncing data using this bus, which was implemented in order to reduce signals connectivity between the two CPLDs. Instead of connecting signal per bit, the bits are synced via a serial bus.

All CPLDs are powered by the auxiliary power; therefore, they still function during main 12V rail shutdown.

# 7.1 CPLD Features

- Lattice XO2 CABGA332 device

- 4320 Logic elements

- 271 I/Os in four banks

- 96K bit UFM user flash memory

- 332-Pin FineLine BGA

- Field upgrade with Fail-Safe mechanism using SPI flash memory

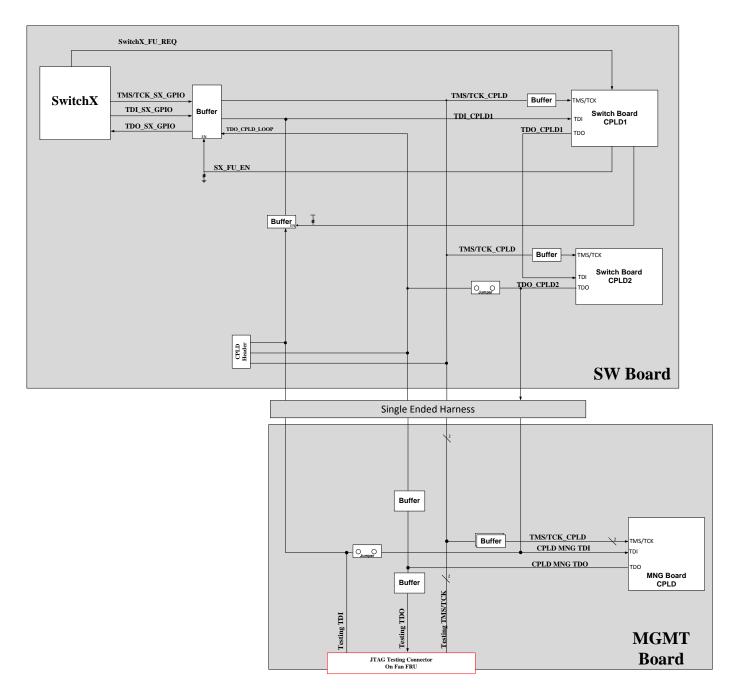

# 7.2 CPLD Field Upgrade

All three CPLD devices can be field upgraded through SX JTAG emulation. Fail Safe feature is supported in case of field upgrade failure for all CPLDs.

Figure 12: CPLD Field Upgrade and JTAG

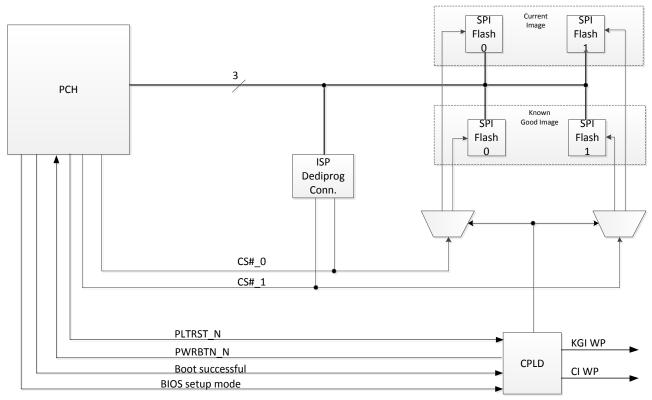

### 8 SPI and Safe BIOS Mechanism

NOTE: This section is relevant to managed systems only.

The Serial Peripheral Interface on the chipset supports two 64MB flash devices (each), storing a Unified BIOS Code.

The MGMT board has two pairs of SPI flash chips: one serves as the default pair, and the other serves as the safe BIOS pair.

The following figure describes the BIOS SPI interface.

Figure 13: Safe BIOS Mechanism

The system includes two SPI Flash pairs:

- Known Good Image (KGI) pair

- Current Image (CI) pair

Both of these pairs are loaded with identical images at the factory. The factory programmed images are the KGI images, which are not intended for update. The KGI provides an image to allow recovery of the system at any point.

The system always selects the CI as the default boot device after power up. This selection is made by the CPLD.

Safe BIOS events flow:

- 1. Initial boot: the default is CI.

- 2. When PLTRST\_N is asserted (logic low) and then de-asserted, a timer starts inside the CPLD (this timer's value can vary based upon boot time of the system).

- 3. The CPLD then waits for "Boot Successful" bit driven by the BIOS.

- 4. If "Boot Successful" is high before the timer runs out, everything functions properly normal boot. If not, the mechanism starts working:

- 5. CPLD selects the KGI pair.

- 6. Then PWRBTN\_N is asserted for 6 seconds, then de-asserted for 5 seconds, asserted for 1 second and then released. This will power cycle the platform (PCH and CPU).

- 7. The system then boots from KGI.

- 8. After a successful boot, the CPLD selects the CI again

- 9. At this point, it is possible to recover the CI using the BIOS FU mechanism.

Note that the CPU has no indication of which image it was uploaded from. Therefore, on every boot, the SW should check a special bit in CPLD (via LPC) that tells which image was uploaded.

In addition to the BOOT\_SUCCESS signals, two other signals are connected from the PCH to the CPLD:

- i. BIOS\_SETUP\_MODE Asserted high by the PCH, in case the user entered the setup menu. As long as this signal is high, the CPLD counter for boot success is paused.

- ii. BIOS\_STARTED Asserted high by the PCH once the BIOS load is started.

BOOT\_SUCCESS and BIOS\_STARTED are used for status LED control.

### 9 Ethernet

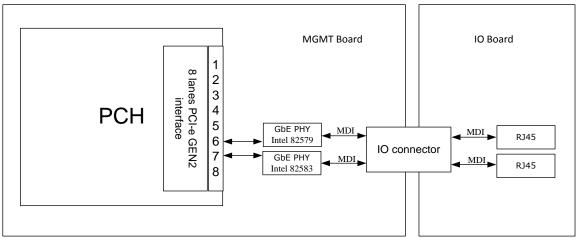

NOTE: This section is relevant to managed systems only.

The MNG board provides two Ethernet MDI 10/100/1000MB/s port to the I/O board. One port is connected through internal PCH MAC and Intel 82579 PHY (port 1). The other port is connected through Intel 82583 MAC/PHY (port 2).

These two MDI ports are routed to two RJ45 ports on the I/O board.

The following figure describes the Ethernet interface.

Figure 14: SX1710 Ethernet Interface

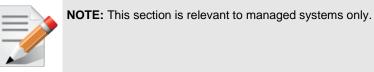

### 10 RS232 Interface

An 8-pin RJ-45 connector is located on the I\O board and provides CLI connectivity (RS-232) to the CPU. The I<sup>2</sup>C and the RS232 share the same RJ45 connector.

The following figure describes the RS-232 interface.

Figure 15: RS-232 Interface

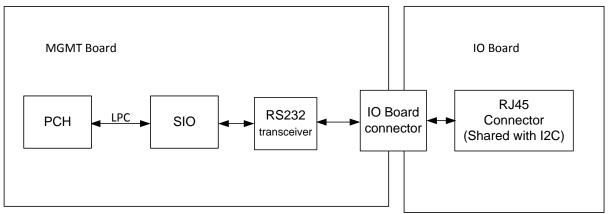

# 11 USB

NOTE: This section is relevant to managed systems only.

The system has one external USB 2.0 Host interface for general use. The USB port can supply 500mA @ 5V and has internal current limiter with fault signal.

Figure 16 describes the USB interface.

Figure 16: USB Interface

# 12 LPC

**NOTE:** This section is relevant to managed systems only.

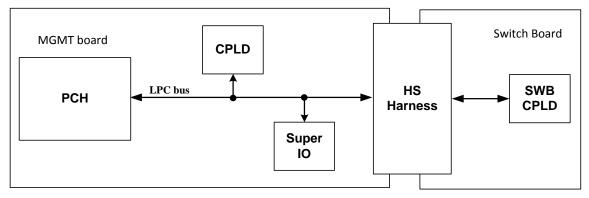

The PCH implements an LPC interface, as described in the Low Pin Count Interface Specification, Revision 1.1. The LPC interface from the PCH is shown in Figure 17.

Figure 17: LPC Interface

# 13 SATA

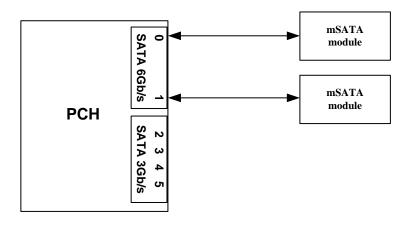

NOTE: This section is relevant to managed systems only.

Up to two mSATA SSD (Solid State Drive) modules are supported by the system. Each one of them supports 4-64GB SLC or MLC. By default, only one 16GB MLC module is assembled on slot 0.

On power down sequence, both of the SSD modules are powered by a super capacitor, in order to perform a graceful shutdown. The super capacitors provide power to the SSD modules, while the rest of the board parts are already shut down.

Figure 18 describes the SATA interface.

Figure 18: SATA Interface

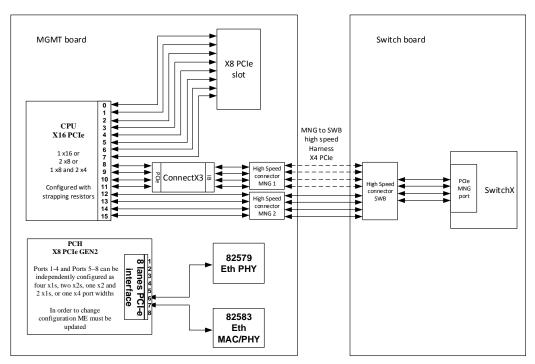

### 14 PCle

NOTE: This section is relevant to managed systems only.

The SX1710 contains 4 PCIe interfaces:

- 1. 1X from PCH to 82579

- 2. 1X from PCH to 82583

- 3. 8X (gen 2 for Celeron/i3, Gen3 for i5/i7) from CPU to 8X slot

- 4. Connection between the MGMT board and the switch board:

Direct 4X (gen 2 for Celeron/i3, Gen3 for i5/i7) connection between the CPU and SwitchX. The gen is also depended in SwitchX capabilities, currently only Gen1 is supported by SwitchX.

Figure 19 describes the PCIe interface.

Figure 19: PCIe Interface

### 15 Power

# **15.1Power Consumption**

# 15.1.1 Switch Board Max Power Consumption

| Configuration                    | 3.3_SX<br>(3.3V)[W] | 1.8_SX<br>(1.8V) [W] | 1.2_SX<br>(1.2V) [W] | VCORE_SX<br>(0.9V) [W] | Total 12v<br>Including<br>DC/DC<br>Efficiency |

|----------------------------------|---------------------|----------------------|----------------------|------------------------|-----------------------------------------------|

| 36 Copper<br>(0W per port)       | 5.9                 | 9.5                  | 20.6                 | 41.2                   | 85.8                                          |

| 36 SR4<br>(3.5W per port)        | 77.9                | 9.5                  | 20.6                 | 41.2                   | 165.8                                         |

| 36 LR4<br>(2W per port)          | 131.9               | 9.5                  | 20.6                 | 41.2                   | 225.8                                         |

| 36 Active cables (1.5W per port) | 59.9                | 9.5                  | 20.6                 | 41.2                   | 145.8                                         |

Table 4: Switch Board Max Power Consumption

# 15.1.2 MGMT Board Power Consumption

|                                                                                                                                                                                       | Current (Amp) | Power[Watt] Tota |         |           |         |           |          |       |       | Total pow er |       |       |         |           |       |       |             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|---------|-----------|---------|-----------|----------|-------|-------|--------------|-------|-------|---------|-----------|-------|-------|-------------|

| voltage                                                                                                                                                                               | voltage       | 0.90             | 1.23    | 1.05      | 1.05    | 1.35      | 0.675    | 0.85  | 5.00  | 3.30         | 1.90  | 1.05  | 1.80    | 0.90      | 1.20  | 1.80  | consumption |

| Device                                                                                                                                                                                | Qty.          | CPU Core         | CPU GFX | CPU VCCIO | PCH Vtt | Vddq DDR3 | Vtt DDR3 | VCCSA | 5V    | 3.3V         | 1.9V  | 1.05  | CPU PLL | ADIR Core | ADIR  | ADIR  | per part    |

| CPU                                                                                                                                                                                   | 1             | 47.700           | 0.000   | 8.925     | 0.000   | 6.750     | 0.000    | 5.400 | 0.000 | 0.000        | 0.000 | 0.000 | 2.160   | 0.000     | 0.000 | 0.000 | 35.000      |

| PCH                                                                                                                                                                                   | 1             | 0.000            | 0.000   | 0.000     | 6.152   | 0.225     | 0.000    | 0.000 | 0.010 | 0.878        | 0.000 | 0.000 | 0.004   | 0.000     | 0.000 | 0.000 | 4.000       |

| 82583                                                                                                                                                                                 | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.017        | 0.505 | 0.205 | 0.000   | 0.000     | 0.000 | 0.000 | 0.727       |

| 82579                                                                                                                                                                                 | 1             | 0.000            | 0.000   | 0.000     | 0.320   | 0.000     | 0.000    | 0.000 | 0.000 | 0.310        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.630       |

| CPLD                                                                                                                                                                                  | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.330        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.330       |

| SODIMM                                                                                                                                                                                | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 4.050     | 0.506    | 0.000 | 0.000 | 0.017        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 4.573       |

| mSATA                                                                                                                                                                                 | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.990        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.990       |

| ConnectX-3                                                                                                                                                                            | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.957        | 0.000 | 0.000 | 0.000   | 2.124     | 1.032 | 0.504 | 4.617       |

| PCle slot                                                                                                                                                                             | 0             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.000        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.000       |

| USB                                                                                                                                                                                   | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 2.500 | 0.000        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 2.500       |

| CRT                                                                                                                                                                                   | 0             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.000        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.000       |

| SPI flash                                                                                                                                                                             | 2             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.132        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.132       |

| SIO                                                                                                                                                                                   | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.132        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.132       |

| OSC                                                                                                                                                                                   | 4             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.264        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.264       |

| LEDs                                                                                                                                                                                  | 15            | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.594        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.594       |

| 3.3->1.9V                                                                                                                                                                             |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| (Integrated in                                                                                                                                                                        |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| 82583)                                                                                                                                                                                | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.878        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.878       |

| 3.3->1.05V                                                                                                                                                                            |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| (Integrated in 82583)                                                                                                                                                                 | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.644        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.644       |

| 3.3-> 1.8V CPU                                                                                                                                                                        | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 3.967        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 3.967       |

| 3.3V-> 1.8 ADIR                                                                                                                                                                       | 1             | 0.000            | 0.000   | 0.000     | 0.000   | 0.000     | 0.000    | 0.000 | 0.000 | 0.924        | 0.000 | 0.000 | 0.000   | 0.000     | 0.000 | 0.000 | 0.924       |

|                                                                                                                                                                                       | Total         | 47.70            | 0.00    | 8.93      | 6.47    | 11.03     | 0.51     | 5.40  | 2.51  | 11.03        | 0.51  | 0.20  | 2.16    | 2.12      | 1.03  | 0.50  |             |

|                                                                                                                                                                                       |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

|                                                                                                                                                                                       | Power[W]      |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| 12V (including                                                                                                                                                                        |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| 90%                                                                                                                                                                                   |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| efficiency)                                                                                                                                                                           | 51.66         |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| 12V_AUX                                                                                                                                                                               |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| (including 90%                                                                                                                                                                        |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| efficiency)                                                                                                                                                                           | 12.26         |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| 12V PCle slot                                                                                                                                                                         | 0.00          |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| Total                                                                                                                                                                                 | 63.91         |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

|                                                                                                                                                                                       |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

|                                                                                                                                                                                       | CPU power [W] |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| t> 2sec                                                                                                                                                                               | 35            |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| 10ms <t<2s< td=""><td>45</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<2s<> | 45            |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| t<10mS                                                                                                                                                                                | 45            |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

| 10110                                                                                                                                                                                 |               |                  |         |           |         |           |          |       |       |              |       |       |         |           |       |       |             |

Table 5: MGMT Board Power Consumption

# 15.1.3 System Power Consumption

| Part         | Power               | Current | Comments  |

|--------------|---------------------|---------|-----------|

| Fans         | 92.2                | 7.7     |           |

| MNG Board    | 51.7                | 4.3     |           |

| SWB          | 225.8 (with 36 LR4) | 18.8    |           |

| 12V Total    | 369.6               | 30.8    | From 460W |

| 12V AUX MNG  | 12.3                | 1.0     |           |

| 12V AUX SWB  | 3.5                 | 0.3     |           |

| 12 AUX Total | 15.7                | 1.3     | From 24W  |

Table 6: System Max Power Consumption

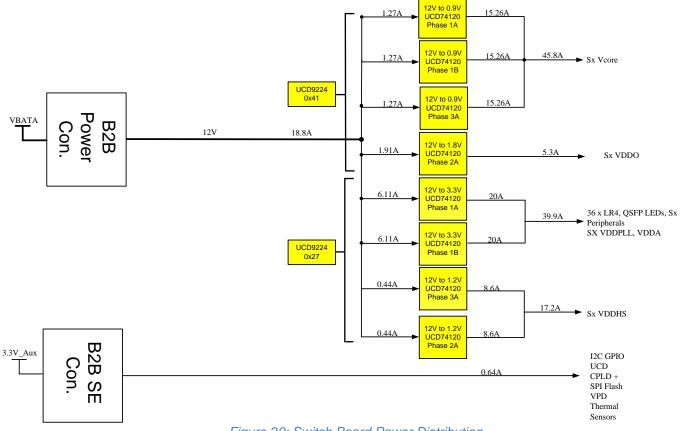

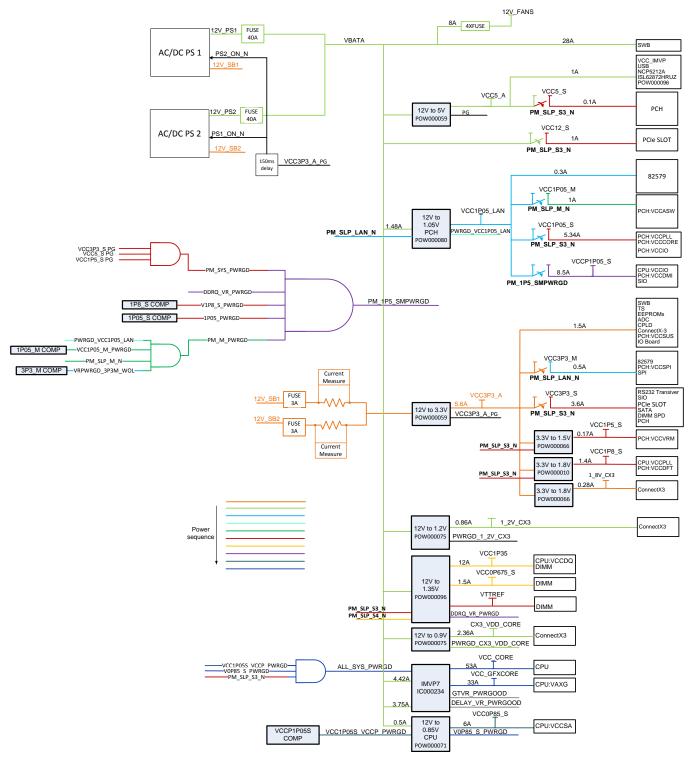

# **15.2Power Monitoring and Distribution**

# **15.2.1** Switch Board Power Monitoring and Distribution

Figure 21: Switch Board Power Monitor and Power Sequence

# 15.2.2 MGMT Board Power Monitoring and Distribution

### 15.2.3 System and MGMT Board Voltages and Currents Sensing

Certain voltages and currents in the system can be read by SW/FW via an 8-channel I<sup>2</sup>C analog to digital converter. Voltage/current inputs to the A2D channels 2-7 are MUXed by 1:2 MUX. Therefore, two values can be read per channel. The MUX select signal is derived by the CPLD and can be controlled by SW and FW. The main 12V voltages and currents can be read directly from the AC/DC PS.

The following table describes the voltage rail in each channel and the expected reading.

| A/D Channel | MUX Select<br>Signal | Monitored Voltage/Current               |                                   | "B" Parameter        |  |                    |

|-------------|----------------------|-----------------------------------------|-----------------------------------|----------------------|--|--------------------|

| 0           | NA                   | DDR3 VTT 0.675V<br>(VCC0P675_S)         |                                   | 0.008 (See note 2)   |  |                    |

|             |                      | Rail Level                              | [VID0,VID1]                       |                      |  |                    |

|             | NA                   | 0.675                                   | [1,1]                             |                      |  |                    |

| 1           | VCC0P85_S            | 0.725                                   | [1,0]                             | 0.008 (See note 2)   |  |                    |

|             | (See Note 1)         | 0.8                                     | [0,1]                             |                      |  |                    |

|             |                      | 0.9                                     | [0,0]                             |                      |  |                    |

| 2           | 0                    | 12V_AUX1 (12V                           | SB1 current)                      | 0.008 (See note 2)   |  |                    |

| 2           | 1                    | 12V_AUX2 (12VSB2 current)               |                                   | 0.008 (See note 2)   |  |                    |

| 3           | 0                    | 3.3V (VCC3P3_/                          | 4)                                | 0.016 (See note 2,3) |  |                    |

| 3           | 1                    | 5V (VCC5_A)                             |                                   | 0.024 (See note 2,3) |  |                    |

| 4           | 0                    | CPU 1.8V (VCC1P8_S)                     |                                   | 0.008 (See note 2)   |  |                    |

| 4           | 1                    | CX3 1.2V (1_2V                          | _CX3)                             | 0.008 (See note 2)   |  |                    |

| 5           | 0                    | CPU/PCH 1.05V<br>(VCC1P05_LAN)          |                                   |                      |  | 0.008 (See note 2) |

|             | 1                    | CPU 1.5V (VCC <sup>2</sup>              | 1P5_S)                            | 0.008 (See note 2)   |  |                    |

| 6           | 0                    | CPU 1.05V (VCC                          | CPU 1.05V (VCCP1P05_S) 0.008 (See |                      |  |                    |

| U           | 1                    | CX3 1.8V (1_8V_CX3)                     |                                   | 0.008 (See note 2)   |  |                    |

| 7           | 0                    | DDR3 1.35V (VCC1P35) 0.008 (See note 2) |                                   | 0.008 (See note 2)   |  |                    |

| 1           | 1                    | CX3 0.9V (CX3_                          | VDD_CORE)                         | 0.008 (See note 2)   |  |                    |

The acceptable range for each rail is +-10% from nominal value.

Table 7: A/D Channels

Notes:

- This rail has 4 valid values controlled by the CPU, using 2 lines which are connected to the voltage regulator - VCCSA\_SEL[0:1]. In order to allow the testing of all 4 levels in JTAG tests, these two controls are routed through the CPLD (CPLD\_VCCSA\_SEL[0:1]).

- 2. The B parameter is used to calculate the real voltage/current from I<sup>2</sup>C reading, using the following formula: V=B\*R, where V is the real voltage and R is the I<sup>2</sup>C reading.

- 3. This voltage is divided by voltage divider before it is sampled; therefore its B parameter contains the divider value as well.

## 16 FRUs

### **16.1Power Supply Units**

The system contains 2 power supplies – AC version (DPS-460KBJ\_REV.03) with the following features:

- Input voltage: 100 to 240 VAC

- Frequency: 50 to 60 Hz

- Efficiency: 89 to 91% at 220V

Table 8 describes the power supply connector pinout.

| Pin #  | Description          | Pin #  | Description        |

|--------|----------------------|--------|--------------------|

| A1~9   | GND                  | B1~9   | GND                |

| A10~18 | +12V                 | B10~18 | +12V               |

| A19    | PMBus SDA            | B19    | A0 (SMBus Address) |

| A20    | PMBus SCL            | B20    | N/A                |

| A21    | PSON                 | B21    | 12VSB              |

| A22    | SMBAlert#            | B22    | Smart)on           |

| A23    | Return Sense         | B23    | 12VLS              |

| A24    | +12V Remote<br>Sense | B24    | No Connect         |

| A25    | PWOK                 | B25    | N/A                |

Table 8: Power Supply Connector Pinout

#### 16.2Fan Units

The fan FRU is Delta Module P/N FA121A04-D40. <u>Table 9</u> describes the fan unit connector pinout. Figure 18 is a mechanical drawing of the unit.

| Pin # | Description | Pin # | Description |

|-------|-------------|-------|-------------|

| 1     | 12V         | 9     | 12V         |

| 2     | 12V         | 10    | 12V         |

| 3     | Fan PWM     | 11    | FAN TACH    |

| 4     | Fan PWM     | 12    | FAN TACH    |

| 5     | GND         | 13    | GND         |

| 6     | GND         | 14    | GND         |

| 7     | FAN Present | 15    | I2C SCL     |

| 8     | 3.3V        | 16    | I2C SDA     |

Table 9: Fan Unit Connector Pinout

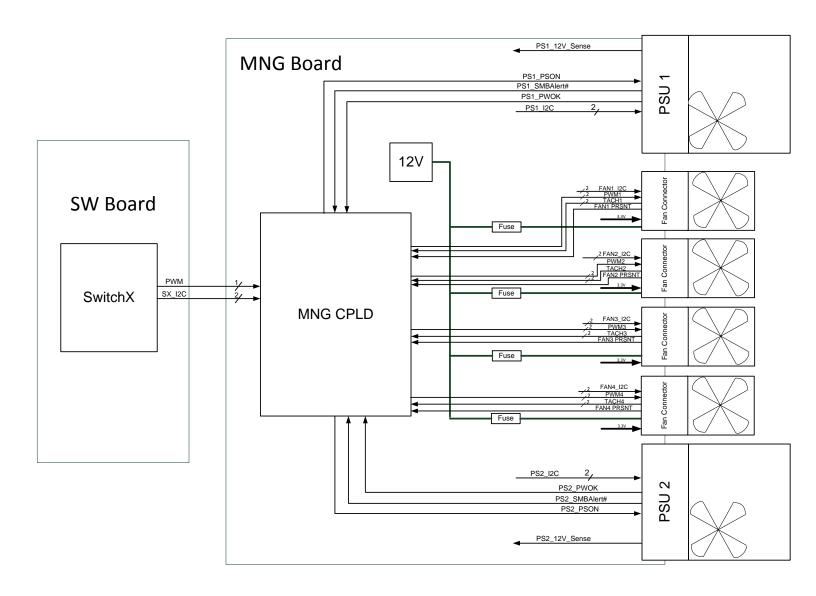

### 16.3FRU Control

The following figure describes the SX1710 FRU control.

Figure 23: SX1710 FRU Control

# 16.3.1 Fan Control

The MGMT CPLD includes a fan controller that is controlled by the SwitchX FW. The fans' speed is controlled by 8 PWM signals from the MGMT CPLD to the fans, and they are monitored by 8 Tacho signals from the fans towards the CPLD.

PWM:

• One PWM output signal from SX is connected to the MGMT CPLD. This signal is reflected to all 8 fans by default.

Tacho:

• 8 Tacho RO registers are available via FW I<sup>2</sup>C (part of the FW register map)

Fan present signal can be monitored by SW and FW via FW and SW registers maps.

Inside the FRU the I<sup>2</sup>C is connected only to one EEPROM. FW and SW can access the fans I<sup>2</sup>C buses. For more info regarding the I<sup>2</sup>C connection to the fans FRUs, see I<sup>2</sup>C chapter.

### 16.3.2 PS Control

The PS is controlled via PMbus and a few signals. SW and FW can access the PMbus. For more information regarding the I<sup>2</sup>C connection to the PS, see  $\underline{I^2C}$ .

PS fans can be controlled via the PMbus. As default, PS fans are controlled automatically by the PS. PS fans speed can be increased by FW/SW, but never reduced.

All other PS control signals can be controlled (for PS inputs) and monitored (for PS outputs) via FW and SW register maps.

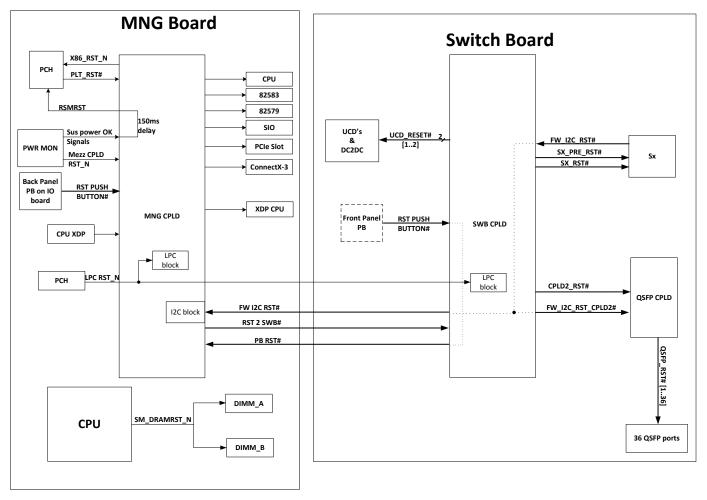

# 17 Reset

The following table specifies the reset scenarios in the SX1710 system:

| #  | Cause                                      | Source         | Target                                                                                            | Description                                                                                                                                                                                                                                                                                       |

|----|--------------------------------------------|----------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | Power monitor<br>circuit indication        | CPLD           | Entire board.                                                                                     | Power monitor circuit monitors that the local voltages are in the range of $\pm 10\%$ of the nominal value.                                                                                                                                                                                       |

| 2. | External push<br>button Short<br>assertion | Push<br>Button | Entire board.                                                                                     | User reset from panel.<br>Assertion of more than ½ sec<br>and less than 12sec.                                                                                                                                                                                                                    |

| 3. | External push<br>button Long<br>assertion  | Push<br>Button | Entire board.                                                                                     | User reset from panel.<br>Restores CPU factory defaults.<br>Assertion of more than 12sec.<br>Supported only on managed<br>systems.                                                                                                                                                                |

| 4. | SW RST                                     | SW             | Entire board.<br>The SW has the ability to<br>reset specific components<br>via its registers map. | SW request RST.<br>Supported only on managed<br>systems.                                                                                                                                                                                                                                          |

| 5. | FW RST                                     | FW             | Entire board.<br>The FW has the ability to<br>reset specific components<br>via its registers map. | FW request RST                                                                                                                                                                                                                                                                                    |

| 6. | WD expired                                 | CPLD           | Entire board.<br>WD is disabled as default.                                                       | WD mechanism is<br>implemented in the CPLD<br>device. The CPU periodically<br>writes counter value via LPC to<br>4 WD registers in the SW<br>board 0xXX CPLD – if the<br>CPLD does not recognize a<br>counter value, change board<br>reset is initiated.<br>Supported only on managed<br>systems. |

| 7. | I <sup>2</sup> C Reset<br>request          | FW             | FW I <sup>2</sup> C tree                                                                          | FW request from CPLD to<br>reset the internal I <sup>2</sup> C switches.<br>Asserted by dedicated GPIO<br>from SwitchX.                                                                                                                                                                           |

Table 10: SX1710 Reset Matrix

Figure 24: SX1710 Reset Mechanism

#### **18 Temperature Monitor**

The following temperature sensors can be read by SW or FW, or both:

- Two external sensors provide temperature sensing:

- In front of the fan FRUs: sense the ambient temperature when fans are pushing air into the system (Air In system)

- In front of the front panel: sense the ambient temperature when fans are sucking air from the system (Air Out system)

- SwitchX-2 has an internal temperature sensing diode. The temperature sensed by the diode is processed, and according to it, two signals may be asserted: Over Thermal Warning and Over Thermal Shutdown. The temperature above / below which these signals are activated /deactivated is controlled by firmware via the INI file, and it must be within the operational temperature range of the device.

- The CPU has an internal sensor that can be monitored only by SW. The CPU can reduce its power (the performance might be reduced as well) in order to prevent from reaching the maximum Tj value.

- The PCH has an internal sensor that can be monitored only by SW.

- Each SODIMM has on module thermal sensor that can be monitored only by SW.

#### 19 Clocks

# **19.1Switch Board Clocks**

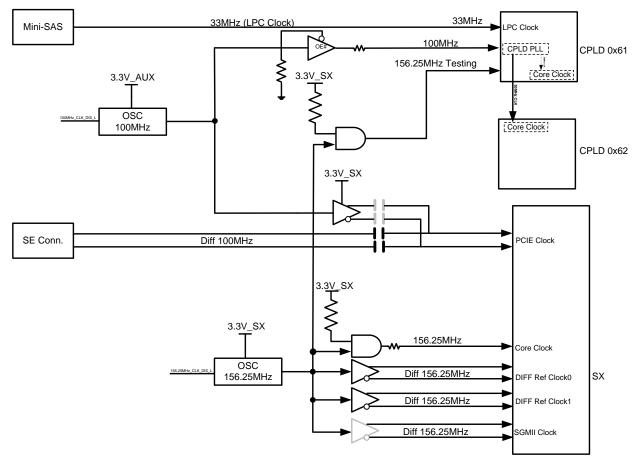

Figure 25 describes the switch board clock distribution.

Figure 25: Switch Board Clock Distribution

#### **19.2MGMT Board Clocks**

Most of the MGMT board clocks are generated from two crystals and distributed by the PCH. In addition, one 25MHz oscillator is buffered and distributed to the ETH PHYs and to the CPLD. The ConnectX3 156.25MHz is generated by additional oscillator.

The ConnectX3 and the PCIe slot are connected to GEN3 supported clocks (PCIe clocks A and B). The rest of the PCIe components are connected to GEN2 clocks. In case a GEN3 connection with the switch board is required, a GEN 3 clock source on the switch board will be needed.

Figure 26 describes the clock distribution in the MGMT board.

Figure 26: MGMT Board Clock Distribution

#### 20 LEDs

The following table describes the SX1710 indication LEDs.

| LED                 | Qty.      | Color                    | Description                                                                                                            |                    | Originator                                                                                                | Driver               | Location                               |

|---------------------|-----------|--------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------|----------------------|----------------------------------------|

| Status<br>LED       | 1         | Red/<br>Green/<br>Yellow | Off – No power<br>Solid Red – Fault<br>Solid Green – Normal operation<br>Blinking Green – Boot<br>Solid Yellow – Error |                    | CPU via<br>LPC I/F<br>towards<br>MNG Board<br>CPLD or<br>SW Board<br>0xXX CPLD<br>or MNG<br>Board<br>CPLD | MNG<br>Board<br>CPLD | On Ports<br>Side and<br>on IO<br>Board |

| General<br>Fans LED | 1         | Red/<br>Green            | Off – No power<br>Green – All fans operating<br>Red – Fan failure                                                      |                    | MNG Board<br>CPLD                                                                                         | SW<br>Board<br>CPLD  | On Ports<br>Side                       |

| Fans 1-4<br>LEDs    | 4         | Red/<br>Green            |                                                                                                                        |                    | MNG Board<br>CPLD                                                                                         | MNG<br>Board<br>CPLD | IO Board                               |

| UID LED             | 1         | Blue                     | Static – The operator has a<br>this LED to identify this mo<br>Blinking – The Operator is<br>to replace this module    | dule.              | CPU via<br>LPC I/F<br>toward SW<br>Board<br>CPLD                                                          | SW<br>Board<br>CPLD  | Ports Side<br>LED<br>Board             |

| Bad Port indication | 1         | Green /<br>Yellow        | Blinking yellow – Bad port                                                                                             | indication         | SwitchX-2                                                                                                 | SW<br>Board<br>CPLD  | Ports Side<br>LED<br>Board             |

| PSU LED             | 1         | Green/<br>Red            | Green – Both PSU OK<br>Red –PSU is Faulty                                                                              |                    | MNG Board<br>CPLD<br>according<br>to PSU<br>indications                                                   | SW<br>Board<br>CPLD  | Ports Side<br>LED<br>Board             |

| PSU LED             | 1 per     | Green /                  | Output ON and OK                                                                                                       | GREEN              | PS                                                                                                        | PS                   | PS FRU                                 |

|                     | PS<br>FRU | Amber                    | No AC power to all power supplies                                                                                      | OFF                |                                                                                                           |                      |                                        |

|                     |           |                          | AC present / Only<br>12VSB on (PS off) or PS<br>in Smart on state                                                      | 1Hz Blink<br>GREEN |                                                                                                           |                      |                                        |

|                     |           |                          | AC cord unplugged or<br>AC power lost; with a<br>second power supply in<br>parallel still with AC input                |                    |                                                                                                           |                      |                                        |

| power.                                                                                                                                 |                    |  |

|----------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Power supply warning<br>events where the power<br>supply continues to<br>operate; high temp, high<br>power, high current, slow<br>fan. | 1Hz Blink<br>Amber |  |

| Power supply critical<br>event causing a<br>shutdown;<br>failure, OCP, OVP, Fan<br>Fail                                                | AMBER              |  |

| Power Supply FW<br>updating                                                                                                            | 2Hz Blink<br>GREEN |  |

Table 11: SX1710 LEDs

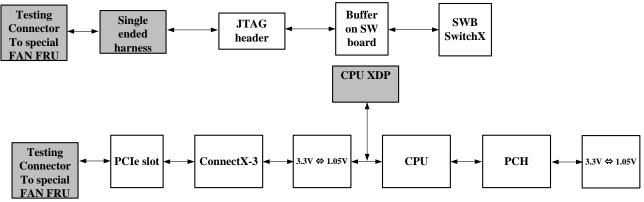

#### 21 JTAG

The system's MGMT board has standalone JTAG support; in addition, the system allows JTAG support via a special fan FRU, while the top cover is assembled.

In order to connect to the MGMT JTAG chain, a special extension card is required (no on-board connectors).

For lab CPLD burning, a few jumpers might have to be assembled, depending on the board and on the system structure. For CPLD JTAG chain, please refer t o<u>CPLD</u>.

The SwitchX chain and the MGMT board chain are described in the following figure.

Figure 27: MGMT Board and Switch Board JTAF Chains

# 21.1Testing I<sup>2</sup>C GPIO

Each of the two boards has a dedicated I<sup>2</sup>C GPIOs for testing. This GPIO is for use only during JTAG tests. The CPLD emulates I<sup>2</sup>C (using JTAG) to control this GPIO.

The GPIO allows control on critical signals during the JTAG test.

In addition, the I<sup>2</sup>C GPIO on the MGMT board is connected to the "Safe BIOS" mechanism. This will allow switching between the 2 sets of SPI flash (Know Good Image and Current Image) without the need of a jumper during the burning process.

## 22 Compliancy

- Shock & Vibration: ETSI EN 300 019-2-2: 1999-09

- Humidity operating: 5% 95% non-condensing

- Operating temperature 0C-45C

- Safety:

- US/Canada: cTUVus

- EU: IEC60950

- International: CB

- CCC

- EMC (Emissions):

- USA: FCC, Class A

- Canada: ICES, Class A

- EU: EN55022, Class A

- EU: EN55024, Class A

- EU: EN61000-3-2, Class A

- EU: EN61000-3-3, Class A

- Japan: VCCI, Class A

- Environmental

- EU: IEC 60068-2-64: Random Vibration

- EU: IEC 60068-2-29: Shocks Type I /II

- EU: IEC 60068-2-32: Fall Test

- Acoustics:

- ISO 7779

- ETS 300 753