# Project Olympus Hyperscale GPU Accelerator (HGX-1) Specification

Author: Siamak Tavallaei, Principal Architect, Microsoft

# **Revision History**

| Date      | Description |

|-----------|-------------|

| 11/1/2017 | Version 1.0 |

####

© 2017 Microsoft Corporation.

As of November 1, 2017, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at <u>http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0</u>

Microsoft Corporation.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at <u>Project Olympus</u> <u>License Agreements</u>, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

CONTRIBUTORS AND LICENSORS OF THIS SPECIFICATION MAY HAVE MENTIONED CERTAIN TECHNOLOGIES THAT ARE MERELY REFERENCED WITHIN THIS SPECIFICATION AND NOT LICENSED UNDER THE OWF CLA OR OWFA. THE FOLLOWING IS A LIST OF MERELY REFERENCED TECHNOLOGY: INTELLIGENT PLATFORM MANAGEMENT INTERFACE (IPMI), I<sup>2</sup>C TRADEMARK OF PHILLIPS SEMICONDUCTOR. IMPLEMENTATION OF THESE TECHNOLOGIES MAY BE SUBJECT TO THEIR OWN LEGAL TERMS.

# Contents

| 1  | Project Olympus Specifications List1 |                            |                                                      |     |  |

|----|--------------------------------------|----------------------------|------------------------------------------------------|-----|--|

| 2  | Ove                                  | Overview                   |                                                      |     |  |

| 3  | Bac                                  | Background2                |                                                      |     |  |

| 4  | Arcł                                 | Architectural Requirements |                                                      |     |  |

| 5  | High                                 | n-leve                     | l Specification                                      | 6   |  |

| 6  | Med                                  | chanic                     | al Features                                          | 10  |  |

| 7  | Pow                                  | ver                        |                                                      | 15  |  |

| ;  | 7.1                                  | Pow                        | er Adapter Module (PAM)                              | 16  |  |

| 8  | Coo                                  | ling                       |                                                      | 18  |  |

| 9  | Acce                                 | elerat                     | ors and Compute Elements                             | 18  |  |

| 10 | PCle                                 | e Swite                    | ch Fabric                                            | 18  |  |

| 11 | Inte                                 | rconn                      | ects                                                 | 19  |  |

| Ĺ  | 1.1                                  | Inter                      | r-Chassis PCIe Cables                                | 19  |  |

| Ĺ  | 1.2                                  | Rise                       | r Boards                                             | 20  |  |

| Ĺ  | 1.3                                  | Host                       | Presence Detection                                   | 26  |  |

| Ĺ  | 1.4                                  | Conr                       | necting to External Chassis                          | 27  |  |

| Ĺ  | 1.5                                  | Pow                        | er Sequencing and PCIe Port Enable Control           | 27  |  |

| Ĺ  | 1.6                                  | PCIe                       | , NVLINK, and PCIe Fabric Manager Network Topologies | 28  |  |

| Ĺ  | 1.7                                  | Mez.                       | zanine Variants                                      | 31  |  |

| 12 | Mar                                  | nagem                      | nent Subsystems                                      | 32  |  |

| Ĺ  | 2.1                                  | Fabr                       | ic Manager (FM)                                      | 32  |  |

| Ĺ  | 2.2                                  | In-Cl                      | hassis Head Node                                     | 34  |  |

| i  | 2.3                                  | вмс                        | C (Baseboard Management Controller)                  | 35  |  |

|    | 12.3                                 | 8.1                        | DRAM                                                 | .36 |  |

|    | 12.3                                 | 3.2                        | BMC Boot Flash                                       | 36  |  |

|    | 12.3                                 | 3.3                        | BIOS Flash                                           | 37  |  |

|    | 12.3                                 | 3.4                        | 1GbE PHY                                             | 37  |  |

| Ĺ  | .2.4                                 | Ther                       | mal Monitoring                                       | 37  |  |

| Ĺ  | 2.5                                  | I²C                        |                                                      | 37  |  |

| Ĺ  | 2.6                                  | UAR                        | Т                                                    | 37  |  |

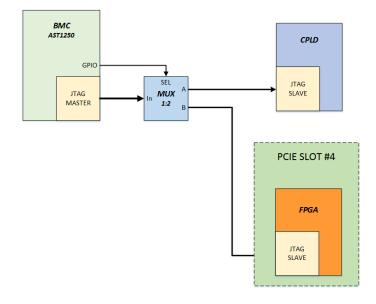

| Ĺ  | 2.7                                  | JTAG                       | G Master                                             | 37  |  |

####

| 12.8    | Volt   | age Regulators                     | 38 |

|---------|--------|------------------------------------|----|

| 12.9    | FRU    | ID PROM                            | 38 |

| 12.10   | Т      | emperature Sensors                 | 39 |

| 12.11   | Н      | ot Swap Controllers                | 39 |

| 12.12   | LI     | EDs                                | 39 |

| 12.1    | 2.1    | UID LED                            |    |

| 12.1    | 2.2    | Power Status LED                   | 40 |

| 12.1    | 2.3    | Attention LED                      |    |

| 12.13   | Fo     | an Control                         | 40 |

| 12.14   | P      | ower Management                    | 40 |

| 12.1    | 4.1    | Rack Management                    | 43 |

| 12.1    | 4.2    | PSU Management                     | 43 |

| 12.1    | 4.3    | Hot Swap Controller                | 43 |

| 12.1    | 4.4    | Power Capping (optional)           |    |

| 12.1    | 4.5    | Overcurrent Protection             | 43 |

| 12.1    | 4.6    | Service Requirements               |    |

| 13 Upp  | er Ba  | seboard (UBB) Interfaces           | 44 |

| 13.1    | Dua    | l-device Card (e.g., FPGA) Support | 44 |

| 13.1    | .1     | OCuLink x8 Connector               | 45 |

| 13.2    | PCIe   | x16 Connectors                     | 47 |

| 13.3    | Fan    | Control Connector                  | 49 |

| 13.4    | Coni   | nector Quality                     | 50 |

| 14 Regu | ulatio | ns and Certifications              | 50 |

| 14.1    | Envi   | ronmental                          | 50 |

| 14.2    | Safe   | ty                                 | 51 |

| 14.3    | ,      | ability                            |    |

| 14.3    | Kella  | 10111Ly                            | 51 |

| 14.4    | FCC    | Certification                      | 51 |

# **Table of Figures**

| Figure 1 4U HGX-1                                                                              | 10   |

|------------------------------------------------------------------------------------------------|------|

| Figure 2 Eight SXM2 Modules                                                                    | 10   |

| Figure 3 Top-view and Side-view of HGX-1 with SXM2 Modules                                     | 11   |

| Figure 4 UBB with eight SXM2 Modules                                                           | 11   |

| Figure 5 UBB Component Placement                                                               | 12   |

| Figure 6 HGX-1 with eight double-width PCIe Cards                                              | 12   |

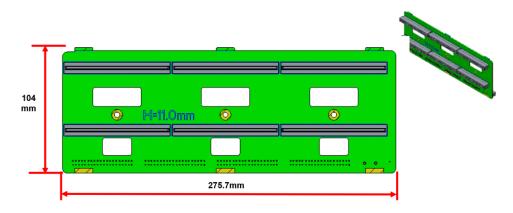

| Figure 7 Eight MEZZ1x16 mezzanines support eight x16 PCIe Cards on UBB                         | 13   |

| Figure 8 MEZZ1x16                                                                              | 13   |

| Figure 9 MEZZ1x16 Mechanical Dimensions                                                        | 13   |

| Figure 10 MEZZ1x16 Connector Placement                                                         | 13   |

| Figure 11 UBB Tray with PCIe Card and SXM2 options                                             | 14   |

| Figure 12 Front and Rear Views of the HGX-1                                                    | 14   |

| Figure 13 Front Door completes the Faraday Cage                                                | 15   |

| Figure 14 Six 1600W Power Supplies in the rear of the HGX-1 (PSU dimensions: 86mm x 40mm x 197 | 'mm) |

|                                                                                                | 15   |

| Figure 15 Power Adapter Module (PAM)                                                           | 16   |

| Figure 16 An inside view of PAM                                                                | 16   |

| Figure 17 Power Adapter Module Block Diagram                                                   | 16   |

| Figure 18 PAM RJ45 pinout (interface to Project Olympus Rack Manager)                          | 17   |

| Figure 19 PAM interface pinout for interfacing to Project Olympus Blade's FCI (PMDU) connector | 17   |

| Figure 20 Twelve N+2 redundant Fans                                                            | 18   |

| Figure 21 Various PCB (Modules) and External PCIe Cabling                                      | 19   |

| Figure 22 PCIe Riser for x8 PCIe Slots (x8 PCIe Cable + Misc. sideband signals)                | 20   |

| Figure 23 PCIe Riser for x16 PCIe Slots (x16 PCIe Cable + Misc. sideband signals)              | 20   |

| Figure 24 UBB x16 PCIe Connector Pinout                                                        | 21   |

| Figure 25 Pinout of the TE Sliver Connector of the single x16 Riser (RISERx16)                 | 22   |

| Figure 26 Pinout of the connector for the single x8 PCIe Riser (RISERx8)                       | 23   |

| Figure 27 Connector pinout for Port A of the dual-x8 Riser (RISERx16 Port A)                   | 24   |

| Figure 28 Connector pinout for Port B of the dual-x8 Riser (RISERx16 Port B)                   | 25   |

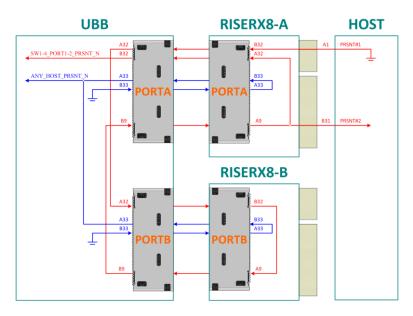

| Figure 29 Host and Cable Presence Detect (Riser x8 A & B)                                      | 26   |

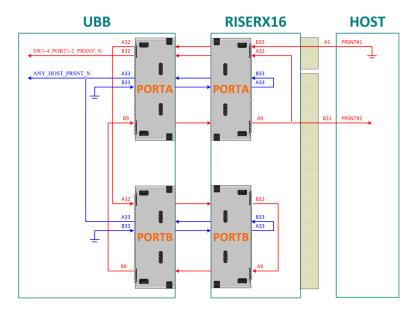

| Figure 30 Host and Cable Presence Detect (Riser x16)                                           | 26   |

| Figure 31 External PCIe Links                                                                  | 27   |

| Figure 32 PCIe, NVLINK, and PCIe Fabric Management Topologies (not all NVLINK connections are  |      |

| shown)                                                                                         | 28   |

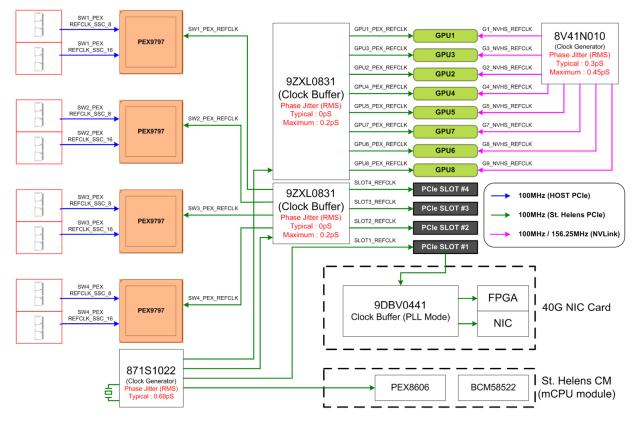

| Figure 33 PCIe Clock Distribution Map                                                          | 29   |

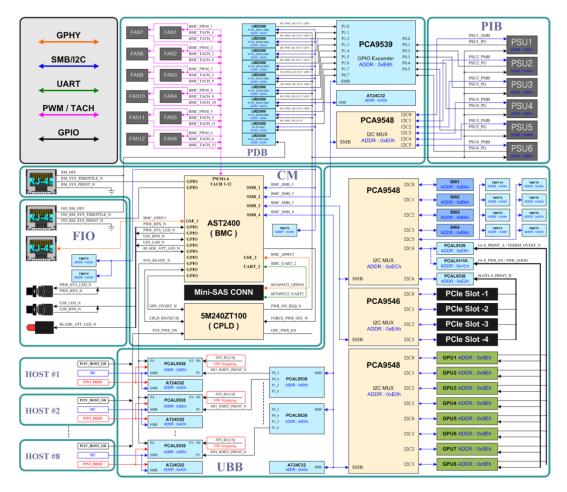

| Figure 34 Chassis Management (CM) Module Block Diagram                                         | 30   |

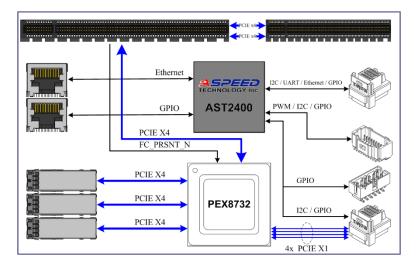

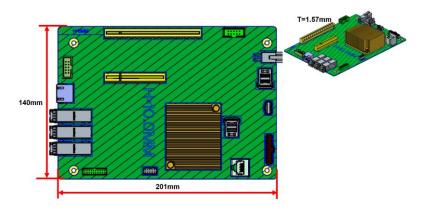

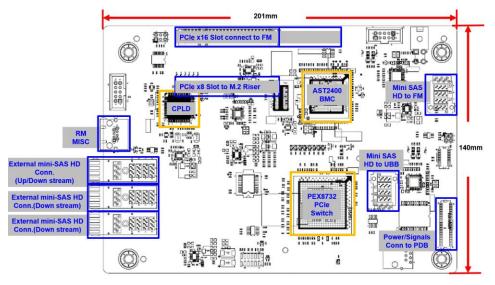

| Figure 35 Chassis Management (CM) Board                                                        | 30   |

| Figure 36 MEZZ2x16                                                                             | 31   |

#### **Open Compute Project • Project Olympus HGX-1 Hyperscale GPU Accelerator Specification**

| Figure 37 MEZZ4x16                                                                  | 31 |

|-------------------------------------------------------------------------------------|----|

| Figure 38 HGX-1 with 4x16 + 32x4 PCIe Slots                                         | 31 |

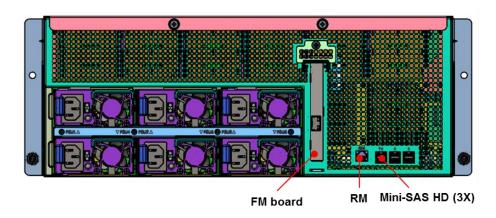

| Figure 39 Fabric Management Network                                                 | 32 |

| Figure 40 Fabric Manager Controller (FM) block Diagram                              | 33 |

| Figure 41 Fabric Manager Board                                                      | 33 |

| Figure 42 FM and CM at the rear of the HGX-1                                        | 34 |

| Figure 43. Chassis Manager Block Diagram                                            | 35 |

| Figure 44 BMC Control Signals and I <sup>2</sup> C Topology Diagram                 | 36 |

| Figure 45. JTAG Programming                                                         | 38 |

| Figure 46. Power Management Block Diagram                                           | 41 |

| Figure 47 Power Interface Board (PIB)                                               | 41 |

| Figure 48 Power Distribution Board (PDB)                                            | 42 |

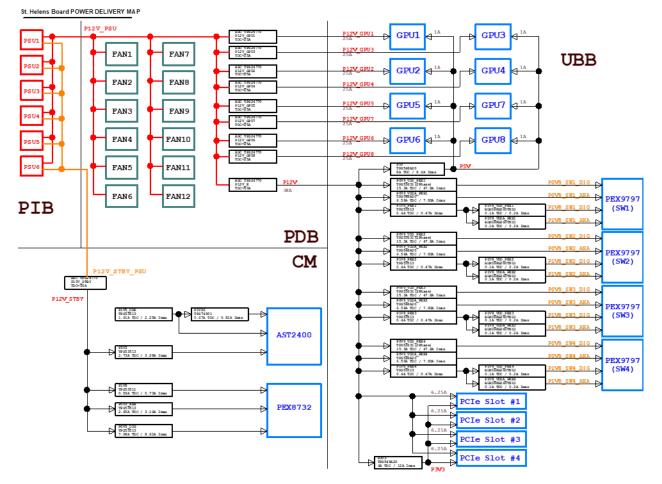

| Figure 49 Power Distribution Diagram                                                | 42 |

| Figure 50 Supporting a dual-device PCIe Card via a x16 Riser and a x8 OCuLink Cable | 45 |

| Figure 51 Dual-device PCIe Riser                                                    | 45 |

| Figure 52. OCuLink x8 Pin Numbering                                                 | 46 |

# **Table of Tables**

| Table 1. List of Specifications             | 1  |

|---------------------------------------------|----|

| Table 2 High-level Mechanical Specification | 6  |

| Table 3 High-level Specification            | 8  |

| Table 4. LEDs                               |    |

| Table 5. Power Status LED Description       | 40 |

| Table 6. Attention LED Description          | 40 |

| Table 7. OCuLink x8 Connector Pinout        | 45 |

| Table 8. PCIe x16 connector pinout          | 47 |

| Table 9. Fan Control Signals                | 49 |

| Table 10. Environmental Requirement         | 50 |

# **1 Project Olympus Specifications List**

*Project Olympus* base specification defines a modular architecture with clear internal and external interfaces. These modules include:

#### <u>Hardware</u>

- Rack

- Universal PDU

- Rack Manager

- 1U/2U Server and mechanical Enclosure

- Power Supply (PSU)

- Universal Motherboard

- PCIe Riser Boards

- PCIe and other Cables

- Expansion Modules (for storage etc.)

#### Software/Firmware

- Software RESTful API

- Rack Manager Software/Firmware/Interface

- BMC Firmware

- System Firmware (BIOS/UEFI code)

- ResetAPI Spec

- Software APIs

*Project Olympus* comprises the above Modules to realize a holistic rack architecture. As specification, design, or product, individual Modules are also applicable to Racks, Chassis, Rack Managers, PDUs, PSUs, Blades, and Motherboards from other architectures such as OCP Open Rack, Open Rack 19, Scorpio, 19" EIA Racks, Rack-mount Servers, and Tower Servers.

Table 1 lists Project Olympus system specifications.

#### Table 1. List of Specifications

| Specification title                            | Description                                                                                                            |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Project Olympus HGX-1<br>Specification         | Describes the modules that comprise a flexible PCIe expansion box for Artificial Intelligence Workloads                |

| Project Olympus HGX-1 Mechanical Specification | Describes the mechanical structure for an expansion box which may be cabled to Project Olympus Server or other Servers |

| Project Olympus JBOD Specification             | Describes the modules that comprise a HDD expansion box for Project Olympus Server                                     |

| Project Olympus JBOF Specification             | Describes the modules that comprise an SSD expansion box for Project Olympus Server                                    |

| Project Olympus Server Rack<br>Specification                  | Describes the mechanical rack hardware used in Project<br>Olympus system                            |

|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Project Olympus Server Mechanical Specification               | Describes the mechanical structure for a server which may be used as a Host Node to couple to HGX-1 |

| Project Olympus Universal Server<br>Motherboard Specification | Describes general requirements of the Host server motherboard                                       |

| Project Olympus PSU Specification                             | Describes the custom Power Supply Unit (PSU) used in the Host server                                |

| Project Olympus Universal PMDU<br>Specification               | Describes the Universal Power and Management Distribution<br>Unit (PMDU)                            |

| Project Olympus Rack Manager<br>Specification                 | Describes the Rack Manager used to couple to the Project<br>Olympus Server                          |

| Project Olympus Standalone Rack<br>Manager Specification      | Describes the Standalone Rack Manager used to couple to the HGX-1                                   |

This document is intended for designers and engineers who will build PCIe expansion boxes for Project Olympus systems.

# 2 Overview

This specification focuses on modules that comprise Project Olympus Hyperscale GPU Accelerator (HGX-1) which provides acceleration capabilities for various frameworks and workloads such as HPC, Video Transcoding, Search, and Artificial Intelligence (AI), Deep Neural Networks (DNN) including Training and Inference.

Refer to respective specifications for other elements of the Project Olympus system such as Power Supply Unit (PSU), Standalone Rack Manager (RM), Power and Management Distribution Unit (Universal PDU, Universal PMDU), and Server Rack.

# **3** Background

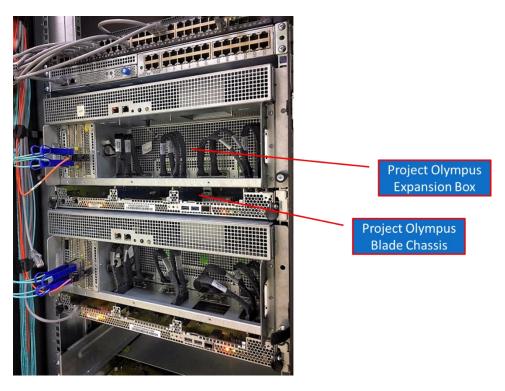

Project Olympus Architecture defines a modular system which includes a Rack, power distribution within the Rack, a Blade Server Chassis, and a Rack Manager.

The Server Chassis consists of a Universal Motherboard, CPU/Memory/Storage, power supply, cooling components, PCIe Risers, and IO interfaces.

Project Olympus Universal Motherboard (MB) provides an efficient CPU/Memory compute node in a 1U Chassis. Project Olympus specification allows for this MB to include single- and multi-socket CPUs and

SoCs of various types to meet different compute needs of cloud-scale datacenters. Mechanical enclosures other than Project Olympus may deploy such Universal Motherboards.

To increase the capabilities of the Server, Project Olympus includes a set of expansion boxes to augment bulk storage (Project Olympus JBOD), high-performing storage (Project Olympus JBOF), and accelerated computing via an HGX-1. These expansion boxes appropriately couple to the Server via PCIe or SAS cables.

At Cloud-scale, the accompanying Project Olympus Hyperscale GPU Accelerator (HGX-1 Expansion Box) described here augments I/O and accelerator capabilities for various frameworks and workloads such as HPC, Artificial Intelligence (AI), Deep Machine Learning (DL), Training, Inference, Graphics, Transcoding, and Search.

The Host Interface and the PCIe Switch Fabric flexibility of Project Olympus HGX-1 provide efficient Host-to-IO binding for single- and multi-CPUs to PCIe device sets of various sizes.

Since its baseline is Project Olympus Server, this expansion box benefits from the streamlined datacenter management required of Cloud-Scale.

# 4 Architectural Requirements

The architecture of Project Olympus Hyperscale Graphics Expansion Chassis (HGX-1) is based on the following tenets:

- 4U Chassis (HGX-1 Expansion Chassis)

- Power: (over 4800W DC available)

- Six highly efficient, 12V Power Supply Units (PSU) conform to MSFT PSU specification

- 1800W and 2000W options

- Two sets of 3-phase balanced power feeds (Primary Feed A and Secondary Feed B)

- Each of A and B inputs feeds three single-phase units

- The power supplies current-share the outputs of each feed

- The power supply sub-system may choose to select feed A, feed B, or both to produce 12V output.

- Cooling: streamlined airflow for efficient cooling of up to 5000W thermal load

- e.g., 12 Fans with N+2 redundant rotors

- Cooling 5000W thermal load with less than 790 CFM of airflow (with the choice of different power supplies, the Expansion Chassis may receive 5kW of sustained power.)

- Management:

- The HGX-1 is a member of the Project Olympus Rack Management on a 1GE Fabric.

- The Expansion Chassis interfaces to a Project Olympus Standalone Rack Manager via an RJ45 connector/cable for sideband signals Presence#, PowerEn#, and Throttle

- PowerEn# controls Chassis and BMC power.

- o AST2500 BMC family

- Uses an RJ45 for 1GE BMC interface (at the rear of the chassis and optionally both at front of the Chassis)

- Based on OpenBMC firmware

- BMC controls Power Supplies, Fans, JTAG, Firmware Updates, etc.

- PCIe Switch Fabric:

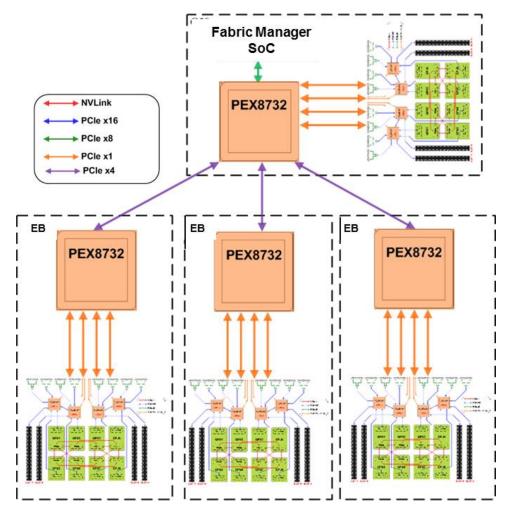

- The HGX-1 interconnects four 96-lane PCIe Switches capable of efficient peer-to-peer traffic, multi-Hosting, and Shared IO.

- Each PCle Switch has one x1 PCle port for Fabric Management.

- Each PCIe Switch provides six x16 Ports:

- 1 x16 Ports used for inter-Switch Link (ISL)

- 3 x 16 Ports connect to three PCIe Devices within HGX-1

- 2 x 16 Ports are available for external connection. (The physical connectors are x8; each x16 Port may bifurcate to two x8 or four x4 Ports.)

- External PCIe Links:

- The HGX-1 provides sixteen x8 PCIe Ports (via eight x16 cable/connectors).

- These PCIe Ports may interconnect to external PCIe Hosts, external HGX-1, PCIe Target Devices, or to internal Switches for better peer-to-peer PCIe traffic for Devices within the HGX-1.

- The pinout of the x8 or x16 Connectors and the circuitry at the end of the of the Cable at the Head Node interface provide Host-presence, Host-power-presence, cable-presence, and correct-seating indications.

- PCIe Fabric Management Network

- PCIe Fabric Manager (FM)

- Internal Head Node:

- The same SoC PCIe Card that performs as a FM may plug into a UBB PCIe Slot and perform as the Head Node for the Expansion box.

- This Head Node couples to the HGX-1 BMC via a cable to control Power Supplies, Fans, etc.

- Interface to an External Head Node(s):

- Project Olympus Server (Head Node) is optimized for front-IO access

- Using one x16 PCIe Link, up to eight Head Nodes may interface HGX-1

- The HGX-1 may link to up to sixteen Hosts or External PCIe Ports using x8 Links (via x8 or x16 Cables)

- Each x8 Link may bifurcate to two x4 Links (at the destination of the x8 Cable).

- Each external Head Node resides underneath an Expansion Chassis and provides x16 PCIe Links to HGX-1. (HGX-1 provides eight x16 PCIe Links.)

- To facilitate cable management, serviceability, and EMI containment, a portion of the front bezel of the HGX-1 is offset from the front plane of the Rack (and that of the Head Node) to allow front-cabling behind the Chassis Door of the HGX-1. This Chassis Door along with the rest of the Chassis forms a Faraday Cage for electromagnetic field containment to reduce EMI.

- Up to four HGX-1 Expansion Chassis may interface via a vertical Chimney behind the Chassis Door(s).

- Head Node:

- $\circ$  An external Head Node such as Project Olympus Server is optimized for front-IO.

- A Head Node may couple to up to four Expansion Chassis. (Each Expansion Chassis may include up to 36 PCIe devices.)

- For various balance of CPU-to-IO ratio, up to sixteen Head Nodes may bind to up to 36 PCIe devices in an HGX-1.

- Upper Baseboard (UBB):

- The Expansion Box consists of a UBB which provides four front-accessible, x16, singlewidth, ¾LFH PCIe Slots.

- Within HGX-1, behind the row of PCIe Slots in the base configuration, there are four PCIe Switches toward the front of the Chassis for ease of interconnection to the Host Node which resides underneath the HGX-1. (no PCIe Re-timer is needed for this configuration.)

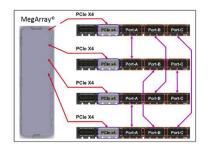

- Using 400-pin MegArray<sup>®</sup> connectors, eight embedded PCIe Devices within the Chassis reside behind the PCIe Switches on UBB.

- Using a second 400-pin MegArray<sup>®</sup> connector and PCB traces, UBB interconnects these 8 embedded PCIe Devices to each other to form a private peer-to-peer network such as nVidia's NVLINK in a hyper-cube + double-ring topology.

- UBB can be flipped around by 180 degrees in a different Chassis so that it may receive PCIe Links from the rear and may present PCIe Cards and Devices with front-accessible connectors.

- Mezzanine:

- Using Mezzanine boards plugged into the MegArray<sup>®</sup> connectors, UBB offers up to eight double-width, 300W, x16 PCIe add-in Cards.

- Several variants of Mezzanine boards provide flexible PCIe Slot or Device configurations.

- MEZZ1x16 includes one x16 PCIe Slot connected to a PCIe Switch for Host Interface.

- MEZZ2x16 includes two x16 PCIe Connectors to provide for two x8 PCIe Slots connected to the Host via the PCIe Switch Fabric. The upper x8 port of the two x16 PCIe connectors are interconnected to form a private Card-to-Card Link.

- MEZZ4x16 includes four x16 PCIe Connectors to provide for four x4 PCIe Slots connected to the Host via the PCIe Switch Fabric. The three upper x4 port of each x16 PCIe connector are interconnected to form a fully-connected, private Card-to-Card network.

- Double-device Cards (e.g., FPGA):

- Via a PCIe Riser board and a x8 OCuLink Cable, one of the PCIe Slots provides the support for an add-in Card implementation with two PCIe Devices.

- One PCIe device receives its PCIe Link via the normal PCIe Slot Connector; while, the other PCIe Device receives its x8 PCIe Link via a x8 OCuLink Cable.

- JTAG Tree:

- The HGX-1 provides a JTAG Tree to program all programable devices such as CPLDs or PCIe Devices/Slots. JTAG signals connected to PCIe Slots are isolated from each other. The BMC is the primary JTAG Root with a 6-bit Device Select.

- I<sup>2</sup>C:

- I<sup>2</sup>C GPIO Device: JTAG Device Select

- Temp Monitors

- Clock Synthesizer Control

- PCIe Slots and Devices

- Power Supplies power monitoring

o GPO for various Reset signals

Panel-mount connector:

- Provisions for 32 x QSFP+ at the IO-plate of the HGX-1 (two Rows of 16 each)

- Panel-mount QSFP+ connectors cable to internal dual-SERDES 50GE or quad-SERDES 100GE Ports.

Internal 100GE Switch in the top U:

- As an alternative, a 48-ported 100GE Switch Board interfaces to the 32 QSFP+ Ports of the HGX-1 IO-Plate in the upper U. Up to 32 internal devices connect to this Switch using internal cables (32 x2, 16 x4, or a mix without over-subscription). With 2:1 oversubscription, 32 internal 100GE ports connect to an External ToR via this Switch.

- Notes:

- Internal 100GE cables are not as thick as the ones for external cabling.

- With smaller bend-radius of internal cables, up to 32 internal PCIe Cards may cable to this Switch using the upper U space above PCIe Cards.

- This Ethernet Switch may be designed so that it does not block the inter-HGX-1 Chimney.

# **5 High-level Specification**

The following sections describe a high-level specification for realizing the architectural goals outlined in the previous section.

Table 2 shows the high-level mechanical specification of Microsoft Project Olympus HGX-1.

#### Table 2 High-level Mechanical Specification

| Feature/ Function                                      | Project Olympus Server HGX-1 Specification                                                             |  |  |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|

| Mechanical Specification                               | Mechanical Specification                                                                               |  |  |

| Form Factor Height                                     | 4U (172mm)                                                                                             |  |  |

| Chassis Dimensions:<br>Width (W) x Length (L)          | 441mm (W) x 947mm (L)                                                                                  |  |  |

| Rack Width                                             | 482.6 mm (19-inch EIA)                                                                                 |  |  |

| Upper Base Board Dimensions –<br>Width (W) x Depth (L) | UBB Dimensions: 425mm (W) x 576mm (L)                                                                  |  |  |

| Total Mass                                             | Less than 45 kg                                                                                        |  |  |

| Power blind mating                                     | 6 x C14 Power Plugs                                                                                    |  |  |

| I/O cards support                                      | Four FHHL x16 Gen3 PCIe Cards<br>Eight SXM2 Modules Or Eight double-width FH¾L PCIe Cards via MEZZ1x16 |  |  |

| Cabling access                                         | Cold aisle cabling for IO and inter-chassis Links<br>Rear-access Power and Management                  |  |  |

| Servicing                                              | Cold aisle servicing PCIe Cards and Accelerators<br>Hot aisle servicing PSUs                           |  |  |

#### **Open Compute Project • Project Olympus HGX-1 Hyperscale GPU Accelerator Specification**

| Power Supply Unit                                | Two 3-pahse feeds:                                                                                                                                                                                                                                          |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  | 6 x 1600W (86mm x 40mm x 197mm)                                                                                                                                                                                                                             |

| SATA devices support                             | N/A                                                                                                                                                                                                                                                         |

| Fans                                             | 12 (N+2) non-hot-swap (60mm x 60mm x 38mm)                                                                                                                                                                                                                  |

| Optional remote heat sink                        | N/A                                                                                                                                                                                                                                                         |

| Front Panel                                      | Four FHHL x 16 PCIe Cards                                                                                                                                                                                                                                   |

|                                                  | RJ45 for 1GE Chassis Management Port                                                                                                                                                                                                                        |

|                                                  | RJ45 for sideband power control and presence                                                                                                                                                                                                                |

| Rear Panel                                       | RJ45 for 1GE Chassis Management Port                                                                                                                                                                                                                        |

|                                                  | RJ45 for sideband power control and presence<br>Three x4 PCIe Ports for Fabric Management                                                                                                                                                                   |

|                                                  | Six C14 Power Plugs                                                                                                                                                                                                                                         |

| Electromagnetic Interference                     |                                                                                                                                                                                                                                                             |

| Electromagnetic Interference<br>(EMI) Mitigation | For EMI containment, EMI shielding, and grounding are considered at the<br>Chassis assembly level. The Chassis supports a top cover that fits within the<br>4U envelope to prevent leakage of electromagnetic fields and airflow                            |

| Grounding and Return                             | The chassis grounding/return is provided to the UBB from the tray assembly through the alignment and mounting holes that secure the UBB to the tray. The UBB is also tied to the PSU ground through the 12 V connector.                                     |

| Environmental                                    | Inlet Temperatures: Operating<br>50°F to 95°F (10°C to 35°C)                                                                                                                                                                                                |

|                                                  | Inlet Temperature: Non-Operating                                                                                                                                                                                                                            |

|                                                  | $-40^{\circ}$ F to $140^{\circ}$ F ( $-40^{\circ}$ C to $60^{\circ}$ C)                                                                                                                                                                                     |

|                                                  | Rate of change less than 36°F (20°C)/hour                                                                                                                                                                                                                   |

|                                                  | Acoustics                                                                                                                                                                                                                                                   |

|                                                  | Less than 7.5 bells at system idle mode                                                                                                                                                                                                                     |

|                                                  | Non-operational vibration<br>Random 1.09Grms, 30 minutes per axis, each of 3 mutually orthogonal axes.                                                                                                                                                      |

|                                                  | Non-operational shock<br>Half sine 20G/11ms, 1 shock per direction of 3 mutually perpendicular axes,<br>total 6 shocks.                                                                                                                                     |

| Regulatory and Safety<br>Requirements            | UL, BSMI                                                                                                                                                                                                                                                    |

| Thermals                                         | The required airflow to maintain thermal integrity shall not be more than 158CFM per kW of consumed power (even with failed fans).                                                                                                                          |

|                                                  | The Expansion Chassis must be able to operate at its maximum power configuration without performance degradation while meeting reliability requirements with two failed fans for an N+2 configuration (12 fans running).                                    |

|                                                  | Failed fan testing should be conducted on all fans with the worst case failed fan locations as the minimum requirement.                                                                                                                                     |

|                                                  | Variable fan speed capability shall be implemented to enable the rack to minimize energy consumption of the air movers and facilities in conditions that permit it. The speed of airflow is based on component temperature requirements within the chassis. |

Table 3 shows a high-level specification of Project Olympus Server and the associated HGX-1.

Table 3 High-level Specification

|                                        | Description                                                                                                                                                                                                                                                                                      |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Feature/ Function                      | Project Olympus Server HGX-1 Specification                                                                                                                                                                                                                                                       |  |  |

| Processors                             |                                                                                                                                                                                                                                                                                                  |  |  |

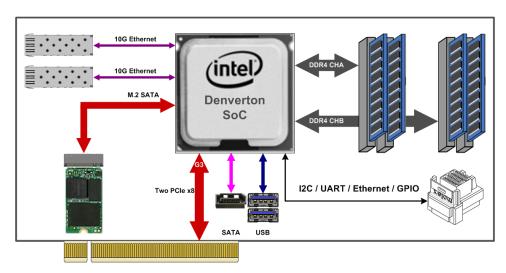

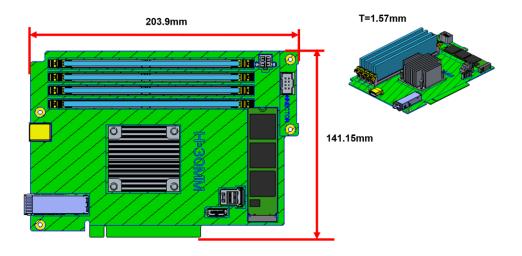

| SoC                                    | Fabric Manager SoC                                                                                                                                                                                                                                                                               |  |  |

| Number of Sockets                      | (1) Optional                                                                                                                                                                                                                                                                                     |  |  |

| I/O Devices/Functions and S            | Slots                                                                                                                                                                                                                                                                                            |  |  |

| PCI Express Connectors                 | Four x16                                                                                                                                                                                                                                                                                         |  |  |

|                                        | Eight x16 using MEZZ1x16                                                                                                                                                                                                                                                                         |  |  |

| SXM2                                   | Eight nVidia SXM2 Modules (Volta 100 + six NVLINKs)                                                                                                                                                                                                                                              |  |  |

| SoC Ethernet interfaces                | One 10GE Fabric Manger                                                                                                                                                                                                                                                                           |  |  |

| System Management                      |                                                                                                                                                                                                                                                                                                  |  |  |

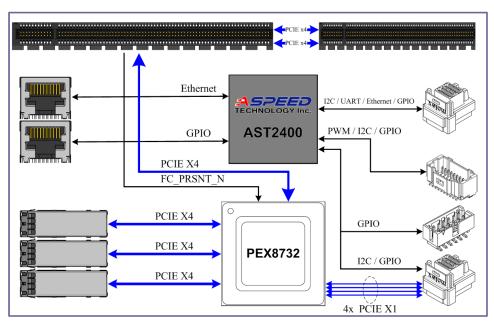

| BMC device                             | ASPEED AST2400 or AST2500 family, on Chassis Management Board                                                                                                                                                                                                                                    |  |  |

| BMC Boot Flash                         | BMC SPI Flash – Minimum 32 MB device                                                                                                                                                                                                                                                             |  |  |

|                                        | (Windbond W25Q256FVFIG)                                                                                                                                                                                                                                                                          |  |  |

| 1 GbE PHY                              | Ethernet Interface – Dedicated BMC 1GE (RJ45) at front-panel and rear-panel.                                                                                                                                                                                                                     |  |  |

| CPU Thermal Monitoring                 | N/A                                                                                                                                                                                                                                                                                              |  |  |

| Telemetry through BMC I <sup>2</sup> C | <ul> <li>The following functions support I<sup>2</sup>C access from the BMC:</li> <li>Local Hot Swap Controllers</li> <li>Power Supplies</li> <li>Key Voltage Regulators (processors and memory)</li> <li>Temperature sensors</li> <li>FRUID PROM</li> </ul>                                     |  |  |

| BMC UART                               | N/A                                                                                                                                                                                                                                                                                              |  |  |

| JTAG Master                            | <ul> <li>The BMC provides JTAG controller for all PCIe Slots and Devices.</li> <li>Debug Header overrides BMC.</li> </ul>                                                                                                                                                                        |  |  |

| Voltage Regulators                     | <ul> <li>Voltage Regulators that support I<sup>2</sup>C or PMBus should be available to the BMC.</li> <li>Clock Circuitry that supports I<sup>2</sup>C should be available to the BMC.</li> </ul>                                                                                                |  |  |

| FRUID PROM                             | <ul> <li>Accessible via local BMC:</li> <li>The system includes a 256Kb serial EEPROM (AT24C256) for storing manufacturing data and the serial number of MAC.</li> <li>Accessible via local External Hosts:</li> <li>One FRUID PROM for each one of the eight External x16 PCIe Links</li> </ul> |  |  |

|                                        | <ul> <li>Up to eight external Hosts may connect to this Expansion Chassis and see the FRUID PROMs.</li> <li>These FRUID PROMs may be programmed the same or as Host-specific configuration</li> </ul>                                                                                            |  |  |

| Temperature sensors                    | <ul> <li>The system supports I<sup>2</sup>C temperature sensors (TMP75) for monitoring the inlet and outlet air temperatures.</li> <li>For accurate temperature reading, care shall be taken to not place these temperature sensors close to component or board heat sources.</li> </ul>         |  |  |

| Hot Swap Controllers                   | <ul> <li>The system includes I<sup>2</sup>C support for nine hot-swap controllers for power monitoring and power capping.</li> <li>All the controllers are located on PDB</li> </ul>                                                                                                             |  |  |

|                                            | Description                                                                                                                                                                                                                                                  |  |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Feature/ Function                          | Project Olympus Server HGX-1 Specification                                                                                                                                                                                                                   |  |

| LEDs                                       | <ul> <li>Each PSU comprises two individual status indications using one LED</li> <li>Green: Output On and OK</li> <li>Amber: Fault</li> </ul>                                                                                                                |  |

| Fan Control                                | The system shall support control of twelve 60 mm fans located on the middle wall<br>of the chassis.<br>Separate six fan zones for six fan modules (two fans per module).<br>Support 12V power, six PWM, and twelve TACH signals for fan control              |  |

| Security                                   |                                                                                                                                                                                                                                                              |  |

| TPM 2.0                                    | N/A                                                                                                                                                                                                                                                          |  |

| FPGA Card Support                          |                                                                                                                                                                                                                                                              |  |

| FPGA Card                                  | The HGX-1 supports a dual-device FHHL x16 PCIe form factor Card for applications such as an FPGA+NIC. Such a Card installs in a x16 Riser in a x16 PCIe Slot. This Riser provides a x8 Link to the Card via Gold Fingers and a x8 Link via an OCuLink cable. |  |

| Power Input and Voltage Re                 | gulators                                                                                                                                                                                                                                                     |  |

| Power Supply Unit interface to Motherboard | The Upper Baseboard isolates power into 9 power zones. Using HSCs, the power distribution board protects each power plane against over-current.                                                                                                              |  |

| Rack Management                            | The Chassis Manager (BMC) communicates with Project Olympus Standalone<br>Rack Manager via an 1GE link (RJ45) and a sideband control link (RJ45) which<br>provides presence, power enable, and throttle functions.                                           |  |

| PSU Management                             | The Chassis Manger manages the six PSUs                                                                                                                                                                                                                      |  |

| Hot Swap Controller                        | The Chassis Manger controls Hot-swap Controllers (HSC) via I <sup>2</sup> C bus.<br>The system shall include I <sup>2</sup> C support for nine hot swap controllers for power monitoring and power capping. All the controllers are located on PDB.          |  |

| Power Capping                              | N/A                                                                                                                                                                                                                                                          |  |

| Overcurrent Protection                     | HSCs are responsible for detecting current levels that indicate catastrophic failure.<br>In such events, the HSC that detects a failure disables 12V rail to the section it<br>monitors (typically by disabling the HSC's input FETs).                       |  |

| M.2 Support                                | The HGX-1 supports PCIe Cards as M.2 Carriers                                                                                                                                                                                                                |  |

| Service Requirements                       |                                                                                                                                                                                                                                                              |  |

| USB Service Port                           | N/A                                                                                                                                                                                                                                                          |  |

| LED visibility                             | The Expansion Box includes the following LEDs: UID LED Power Status LED Attention LED                                                                                                                                                                        |  |

### 6 Mechanical Features

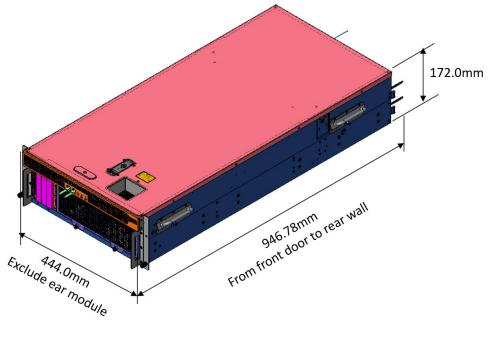

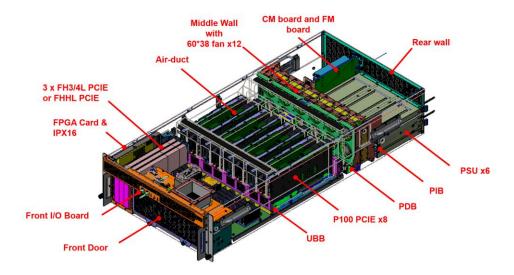

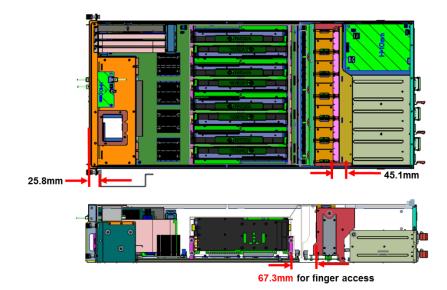

Figure 1 shows the dimensions of a 4U chassis suitable for Project Olympus HGX-1 Expansion Chassis.

Figure 1 4U HGX-1

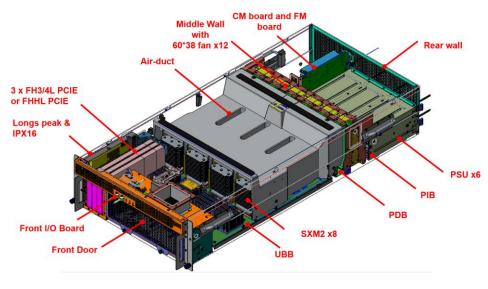

The HGX-1 may house various PCIe-connected Accelerators and IO peripherals. Figure 2 shows an isometric view of the HGX-1 with eight SXM2 Modules such as those for nVidia Volta V100 family of GPGPUs.

Figure 2 Eight SXM2 Modules

Figure 3 Top-view and Side-view of HGX-1 with SXM2 Modules

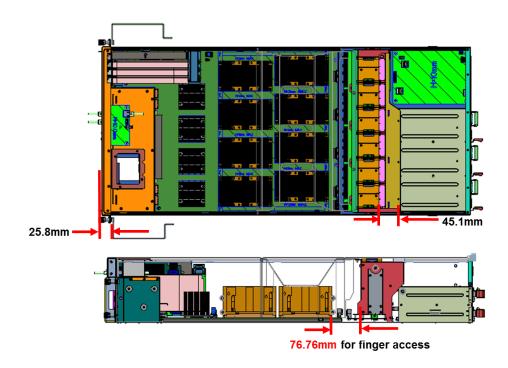

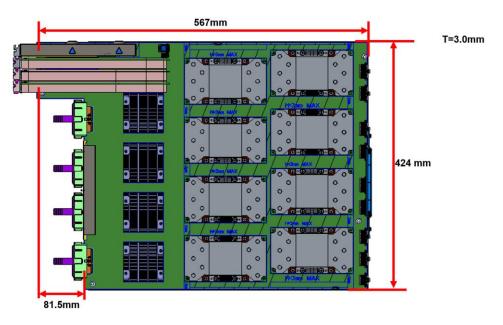

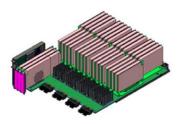

The HGX-1 provides an Upper Baseboard (UBB) with four PCIe Switches to couple to an external Motherboard (MB) via a set of cables. Figure 4 shows the UBB and the placement of eight SXM2 Modules.

Figure 4 UBB with eight SXM2 Modules

Figure 5 shows component placement on UBB such as PCIe Switches, eight pairs of 400-pin Meg-Array<sup>®</sup> Connectors, front-accessible x16 PCIe Slots, and eight x16 external PCIe connectors (four of which are under the PCB).

Figure 5 UBB Component Placement

Figure 6 shows an isometric view of the HGX-1 with eight double-width FH¾L 300W PCIe Cards.

#### Figure 6 HGX-1 with eight double-width PCIe Cards

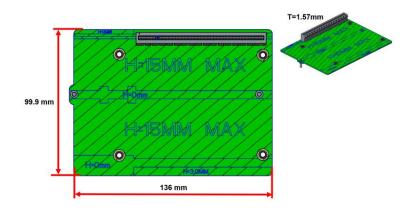

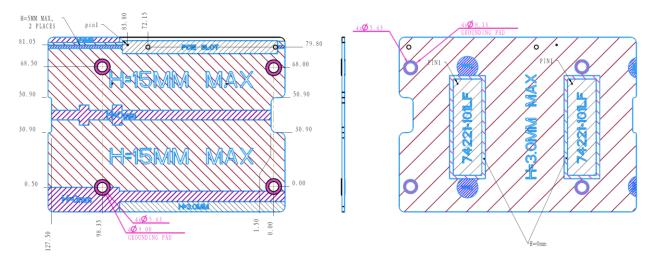

#### Figure 7 Eight MEZZ1x16 mezzanines support eight x16 PCIe Cards on UBB

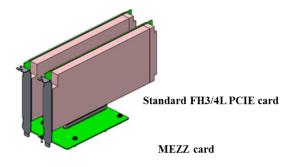

Figure 7 and Figure 8 show MEZZ1x16 which plugs into Meg-Array<sup>®</sup> connectors on UBB and provides eight x16 PCIe Slots.

Figure 8 MEZZ1x16

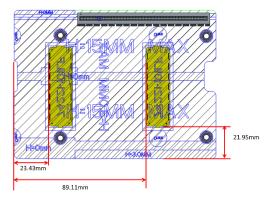

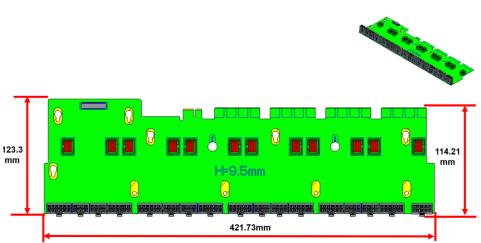

#### Figure 9 MEZZ1x16 Mechanical Dimensions

Figure 10 MEZZ1x16 Connector Placement

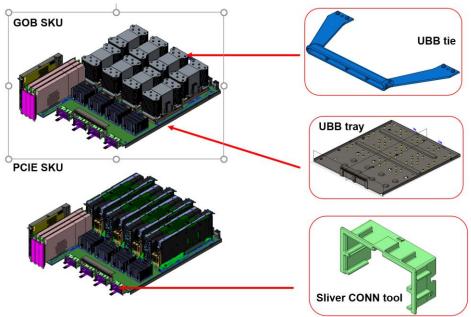

Figure 11 UBB Tray with PCIe Card and SXM2 options

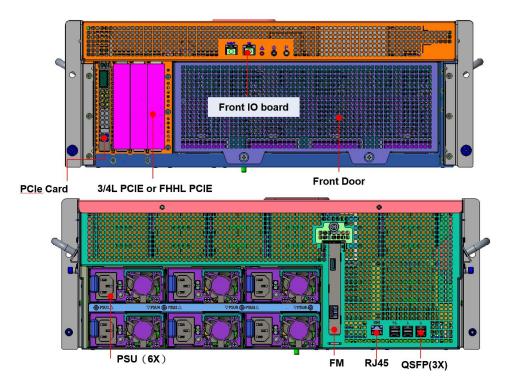

Figure 12 shows the front and rear views of the HGX-1.

Figure 12 Front and Rear Views of the HGX-1

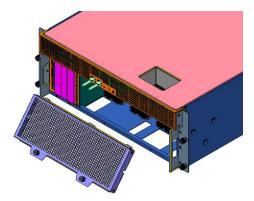

Figure 13 Front Door completes the Faraday Cage

# 7 Power

Consistent with Project Olympus Rack Architecture, Project Olympus HGX-1 provides balanced 3-phase power with two redundant feeds (A and B). The HGX-1 includes 6 Power Supplies in an N+N redundant configuration and provides load-balancing over three phases. (two feeds of 3-phase each.) These Power Supplies provide 1600W each.

Figure 21 shows UBB Power Islands. To enable the e-fuses (via Hot-swap Controller) detect overcurrent, the UBB has several power islands. Separate e-fuses (HSC) monitor and control each power island.

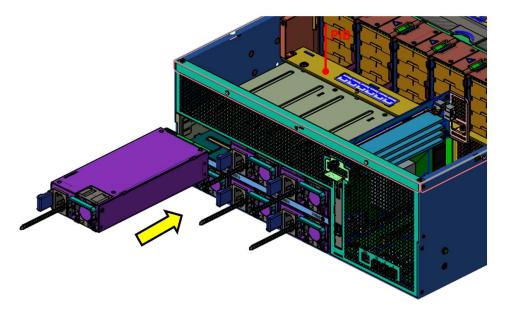

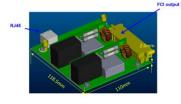

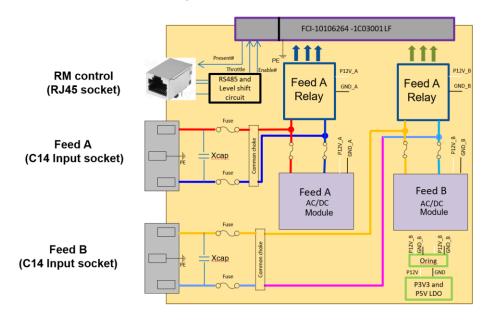

### 7.1 Power Adapter Module (PAM)

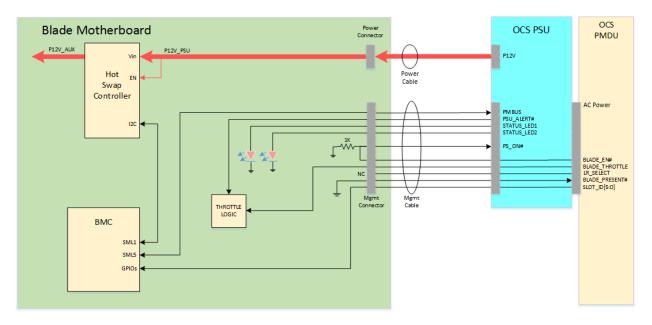

While HGX-1 Expansion Chassis includes six PSUs with C14 power receptacles, it couples to Project Olympus-compatible Server Blades. Project Olympus Rack architecture defines a Power and Management Distribution Unit (PMDU) for power and rack management interfaces.

To enable compatible power cabling, the Power Adapter Module (PAM) shown in Figure 15 through Figure 19 is suitable for interfacing the FCI power connector of a Project Olympus Blade to two C14 power receptacles and one RJ45 connector for power control signals.

Figure 15 Power Adapter Module (PAM)

Figure 16 An inside view of PAM

Figure 17 Power Adapter Module Block Diagram

####

| Pin # | Signal         | I/O | Voltage | Description                 |

|-------|----------------|-----|---------|-----------------------------|

| 1     | RM_THROTTLE+   | 1   | RS485   | Set server to throttle mode |

| 2     | RM_THROTTLE-   | 1   | RS485   | Set server to throttle mode |

| 3     | RM_BOOTSTRAP+  | 1   | RS485   | DEPOP                       |

| 4     | /A             |     |         |                             |

| 5     | BLADE_PRESENT# | 0   | 3.3V    | Indicates Blade is present  |

| 6     | RM_BOOTSTRAP-  | 1   | RS485   | DEPOP                       |

| 7     | GND            |     | 0V      | Ground                      |

| 8     | RM_OFF         | 1   | 5V      |                             |

#### Figure 18 PAM RJ45 pinout (interface to Project Olympus Rack Manager)

| Pin #      | Signal         | I/0 | Voltage | Description          |

|------------|----------------|-----|---------|----------------------|

| P1         | Safety Ground  | -   |         |                      |

| P2         | Not Used       | -   |         |                      |

| P3         | Feed B Neutral | 0   |         |                      |

| P4         | Feed B Phase C | 0   |         |                      |

| P5         | Feed A Neutral | 0   |         |                      |

| P6         | Feed A Phase C | 0   |         |                      |

| P7         | Feed B Neutral | 0   |         |                      |

| P8         | Feed B Phase B | 0   |         |                      |

| P9         | Feed A Neutral | 0   |         |                      |

| P10        | Feed A Phase B | 0   |         |                      |

| P11        | Feed B Neutral | 0   |         |                      |

| P12        | Feed B Phase A | 0   |         |                      |

| P13        | Feed A Neutral | 0   |         |                      |

| P14        | Feed A Phase A | 0   |         |                      |

| A1         | LR_SELECT      | 0   | 3.3V    | DEPOP                |

| A2         | -              |     |         |                      |

| A3         | Analog Return  |     | 0V      |                      |

| B1         | -              |     |         |                      |

| B2         | -              |     |         |                      |

| <b>B</b> 3 | -              |     |         |                      |

| C1         | BLADE_THROTTLE | 0   | 3.3V    | Default Disable(Low) |

| C2         | BLADE_ENABLE#  | 0   | 3.3V    | Default Enable(Low)  |

| C3         | BLADE_PRESENT# | 1   | 3.3V    |                      |

| D1         | -              |     |         |                      |

| D2         | -              |     |         |                      |

| D3         | -              |     |         |                      |

Figure 19 PAM interface pinout for interfacing to Project Olympus Blade's FCI (PMDU) connector

# 8 Cooling

Twelve 60mm Fans provide up to 5000W of cooling for the HGX-1 in an N+2 redundant configuration with less than 790 CFM of airflow to meet airflow specification of no more than 158 CFM per kW.

Figure 20 Twelve N+2 redundant Fans

# **9** Accelerators and Compute Elements

Project Olympus HGX-1 supports various compute accelerator (GPGPUs, FPGAs, ASICs, SoCs) or PCIe peripheral devices. For example, Figure 2 shows a configuration with eight nVidia Pascal P100 GPGPU family in SXM2 form factor suitable for Deep Machine Learning (DL, Training); Figure 6 shows eight accelerators in double-width, 300W PCIe form factor for visualization or HPC; and Figure 38 shows thirty-two 75W accelerators in single-width FHHL PCIe form factor for DL/Inference or Transcoding.

# **10 PCIe Switch Fabric**

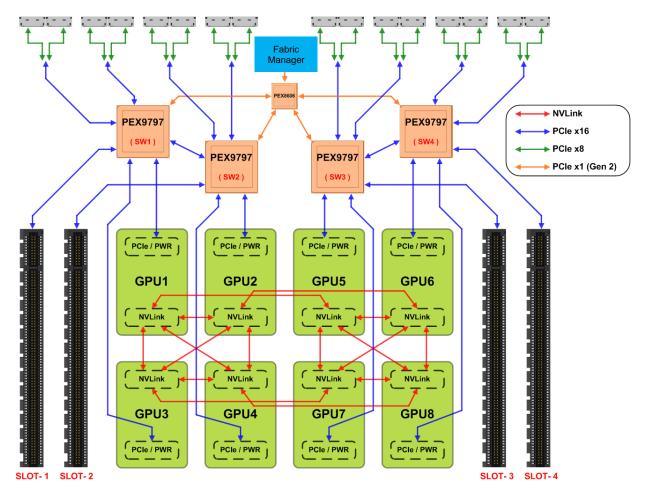

The Upper Baseboard of the HGX-1 implements a PCIe Gen-3 Switch Fabric. The HGX-1 interconnects four 96-lane PCIe Switches (PEX9797 from Broadcom) capable of efficient peer-to-peer traffic, multi-Hosting, and Shared IO. Each PCIe Switch has one x1 PCIe port for Fabric Management. Each PCIe Switch provides six x16 Ports. One x16 Port is dedicated for inter-Switch Link (ISL). Three x16 Ports connect to three PCIe Devices on UBB. Two x16 Ports are available for external connection.

The physical connectors for the external Links are x16 TE Sliver Cable/Connectors. Each x16 Port may bifurcate to two x8 or four x4 Ports. Using x8 cables, the HGX-1 can export up to sixteen x8 PCle Links.

These sixteen PCIe Ports may interconnect to external PCIe Hosts, external HGX-1, PCIe Target Devices, or to internal Switches for better peer-to-peer PCIe traffic for Devices within the HGX-1.

While, this PCIe Switch Fabric is cable of multi-Hosting and Shared IO which require enabling the Fabric Mode and a Fabric Management Controller, the simplest implementation includes PCIe traffic multiplexing between one Host and PCIe end Devices and peer-to-peer traffic between PCIe Devices.

Other configurations include one Host connecting to up to four interconnecting HGX-1 or up to sixteen Hosts to one HGX-1.

### **11Interconnects**

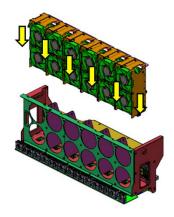

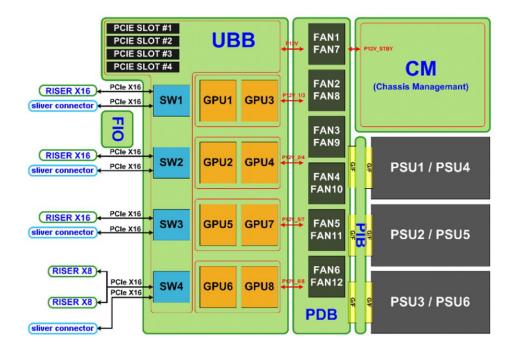

Figure 21 depicts various HGX-1 Modules and PCIe Cabling to an External Chassis.

Figure 21 Various PCB (Modules) and External PCIe Cabling

### **11.1 Inter-Chassis PCIe Cables**

Figure 21 shows eight x16 connectors that are available to connect the HGX-1 PCIe Ports to either external Hosts, to itself for peer-to-peer interconnect, or to other expansion boxes.

The pinout of the x16 connector and the circuitry at the end of the of the Cable at the Head Node interface provide Host-presence, Host-power-presence, cable-presence, and correct-seating indications.

### **11.2 Riser Boards**

Figure 21 showed that HGX-1 provides eight x16 PCIe Links to connect to Project Olympus Server.

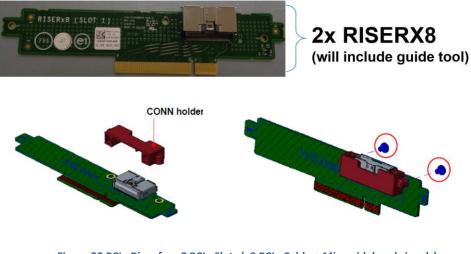

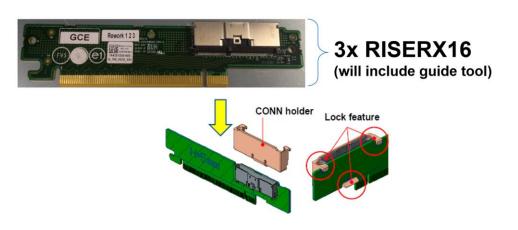

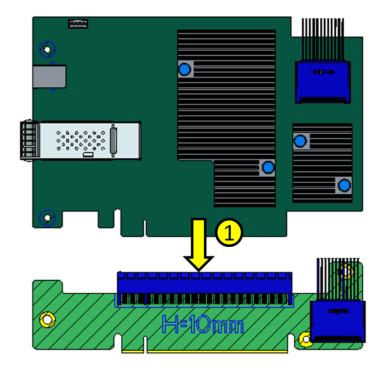

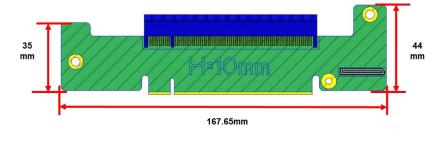

Figure 22 and Figure 23 show various Riser Boards suitable for extracting PCIe Links from standard PCIe Slots. Three x16 and two x8 PCIe Risers plug into Project Olympus Universal Motherboard to provide up to four x16 PCIe Links (plus miscellaneous sideband signals) to the HGX-1.

Figure 22 PCIe Riser for x8 PCIe Slots (x8 PCIe Cable + Misc. sideband signals)

Figure 23 PCIe Riser for x16 PCIe Slots (x16 PCIe Cable + Misc. sideband signals)

Various connector/cable assemblies may accommodate Host Nodes of different capabilities.

HGX-1 Expansion Chassis incorporates TE Sliver connector/cable assemblies for the eight x16 PCIe Ports.

|          | UBB (TE-2294190-3) |             |                                                              |            |                  |            |                                         |  |  |

|----------|--------------------|-------------|--------------------------------------------------------------|------------|------------------|------------|-----------------------------------------|--|--|

|          |                    | A SID       |                                                              | B SIDE     |                  |            |                                         |  |  |

| Pin      | Signal Name        | Direction   | - Description                                                | Pin        | Signal Name      | Direction  | Description                             |  |  |

| 1        | GND                | -           |                                                              | 124        | GND              | -          |                                         |  |  |

| 2        | PRSNT_A_N          | I, PU       | Cable Present Signal on A side                               | 123        | GND              | 0          | Present GND for UBB Cross Link          |  |  |

| 3        | ANY_HOST_PRSNT_N   | I, PU       | Present Signal for Power control                             | 122        | SSC_ISO_EN       | I, PU      | Present Signal for PEX9797 Configation  |  |  |

| 4        | GND<br>PE RST N    | -<br>I , PU | PCIe Reset signal from HOST                                  | 121        | GND<br>PE RST N  | -<br>L, PU | PCIe Reset signal to next stage UBB     |  |  |

| 6        | P12V_HOST_GD       | I, PU       | 12V Power on control form HOST                               | 119        | P12V_HOST_GD     | I, PU      | 12V Power on control to next stage UBB  |  |  |

| 7        | GND                | -           |                                                              | 118        | GND              | -          | 120 Porter on control to next stage obb |  |  |

| 8        | REFCLK+            | I           | PCIe Reference Clock Input                                   | 117        | SMCLK            | I          | SMbus from HOST                         |  |  |

| 9        | REFCLK-            | 1           | P Cie Relefence Clock Input                                  | 116        | SMDAT            | I/O        |                                         |  |  |

| 10       | GND                | -           |                                                              | 115        | GND              | -          |                                         |  |  |

| 11<br>12 | P3V3_HOST<br>GND   | 1           | 3.3V Power input form HOST<br>Present GND for UBB Cross Link | 114<br>113 | NC<br>PRSNT B N  | -<br>I, PU | Cable Dresent Cignal on Disida          |  |  |

| 12       | GND                | 0           | Present GND for OBB Cross Link                               | 113        | GND              | 1, PU<br>- | Cable Present Signal on B side          |  |  |

| 14       | PETp0              | 0           |                                                              | 111        | PERp0            | 1          |                                         |  |  |

| 15       | PETn0              | 0           | PEX9797 PCIe Transmit Path                                   | 110        | PERn0            | 1          | PEX9797 PCIe Receive Path               |  |  |

| 16       | GND                | -           |                                                              | 109        | GND              | -          |                                         |  |  |

| 17       | PETp1              | 0           | PEX9797 PCIe Transmit Path                                   | 108        | PERp1            | I          | PEX9797 PCIe Receive Path               |  |  |

| 18       | PETn1              | 0           |                                                              | 107        | PERn1            | 1          |                                         |  |  |

| 19<br>20 | GND                | - 0         |                                                              | 106        | GND<br>PERp2     | -          |                                         |  |  |

| 20       | PETp2<br>PETn2     | 0           | PEX9797 PCIe Transmit Path                                   | 105<br>104 | PERp2<br>PERn2   | 1          | PEX9797 PCIe Receive Path               |  |  |

| 22       | GND                | -           |                                                              | 104        | GND              | -          |                                         |  |  |

| 23       | PETp3              | 0           |                                                              | 102        | PERp3            | 1          |                                         |  |  |

| 24       | PETn3              | 0           | PEX9797 PCIe Transmit Path                                   | 101        | PERn3            | I          | PEX9797 PCIe Receive Path               |  |  |

| 25       | GND                | -           |                                                              | 100        | GND              | -          |                                         |  |  |

| 26       | PETp4              | 0           | PEX9797 PCIe Transmit Path                                   | 99         | PERp4            | 1          | PEX9797 PCIe Receive Path               |  |  |

| 27       | PETn4              | 0           |                                                              | 98         | PERn4            | 1          |                                         |  |  |

| 28<br>29 | GND                | - 0         |                                                              | 97<br>96   | GND<br>PERp5     | -          |                                         |  |  |

| 30       | PETp5<br>PETn5     | 0           | PEX9797 PCIe Transmit Path                                   | 96         | PERp5<br>PERn5   | 1          | PEX9797 PCIe Receive Path               |  |  |

| 31       | GND                | -           |                                                              | 94         | GND              | -          |                                         |  |  |

| 32       | PETp6              | 0           | PEX9797 PCIe Transmit Path                                   | 93         | PERp6            | 1          | PEX9797 PCIe Receive Path               |  |  |

| 33       | PETn6              | 0           | PEX9797 PCIe Transmit Path                                   | 92         | PERn6            | I          | PEX9797 PCIE Receive Path               |  |  |

| 34       | GND                | -           |                                                              | 91         | GND              | -          |                                         |  |  |

| 35       | PETp7              | 0           | PEX9797 PCIe Transmit Path                                   | 90         | PERp7            | 1          | PEX9797 PCIe Receive Path               |  |  |

| 36<br>37 | PETn7<br>GND       | 0           |                                                              | 89<br>88   | PERn7<br>GND     | -          |                                         |  |  |

| 38       | GND                | _           |                                                              | 87         | GND              | -          |                                         |  |  |

| 39       | PETp8              | 0           |                                                              | 86         | PERp8            | 1          |                                         |  |  |

| 40       | PETn8              | 0           | PEX9797 PCIe Transmit Path                                   | 85         | PERn8            | I          | PEX9797 PCIe Receive Path               |  |  |

| 41       | GND                | -           |                                                              | 84         | GND              | -          |                                         |  |  |

| 42       | PETp9              | 0           | PEX9797 PCIe Transmit Path                                   | 83         | PERp9            | 1          | PEX9797 PCIe Receive Path               |  |  |

| 43       | PETn9              | 0           |                                                              | 82         | PERn9            |            |                                         |  |  |

| 44<br>45 | GND<br>PETp10      | - 0         |                                                              | 81<br>80   | GND<br>PERp10    | -          |                                         |  |  |

| 45       | PETp10<br>PETn10   | 0           | PEX9797 PCIe Transmit Path                                   | 79         | PERpio<br>PERn10 |            | PEX9797 PCIe Receive Path               |  |  |

| 47       | GND                | -           |                                                              | 78         | GND              | -          |                                         |  |  |

| 48       | PETp11             | 0           | PEX9797 PCIe Transmit Path                                   | 77         | PERp11           | I          | PEX9797 PCIe Receive Path               |  |  |

| 49       | PETn11             | 0           | FLAJIJI PCIE Hanshin Path                                    | 76         | PERn11           | I          | F2A9/9/ PCIE Receive Path               |  |  |

| 50       | GND                | -           |                                                              | 75         | GND              | -          |                                         |  |  |

| 51       | PETp12             | 0           | PEX9797 PCIe Transmit Path                                   | 74         | PERp12           | 1          | PEX9797 PCIe Receive Path               |  |  |

| 52<br>53 | PETn12<br>GND      | 0           |                                                              | 73         | PERn12<br>GND    | -          |                                         |  |  |

| 54       | PETp13             | 0           |                                                              | 72         | PERp13           |            |                                         |  |  |

| 55       | PETn13             | 0           | PEX9797 PCIe Transmit Path                                   | 70         | PERn13           |            | PEX9797 PCIe Receive Path               |  |  |

| 56       | GND                | -           |                                                              | 69         | GND              | -          |                                         |  |  |

| 57       | PETp14             | 0           | PEX9797 PCIe Transmit Path                                   | 68         | PERp14           | I          | PEX9797 PCIe Receive Path               |  |  |

| 58       | PETn14             | 0           | . 2.5757 Fele Hanshiel du                                    | 67         | PERn14           | 1          | . 20777 Cle Receive Full                |  |  |

| 59       | GND                | -           |                                                              | 66         | GND              | -          |                                         |  |  |

| 60<br>61 | PETp15<br>PETn15   | 0           | PEX9797 PCIe Transmit Path                                   | 65<br>64   | PERp15<br>PERn15 |            | PEX9797 PCIe Receive Path               |  |  |

| 62       | GND                | -           |                                                              | 63         | GND              | -          |                                         |  |  |

| - V2     | 0110               | I           |                                                              |            | 0170             |            |                                         |  |  |

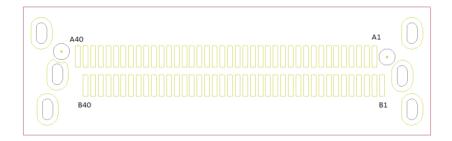

Figure 24 shows the pinout of UBB x16 PCIe Connector.

Figure 24 UBB x16 PCIe Connector Pinout

Figure 25 shows the pinout of the TE Sliver connector for a PCIe Riser board with a single x16 cable connector.

|          | RISERX16 (TE-2294190-3) |           |                               |            |                      |           |                               |  |  |

|----------|-------------------------|-----------|-------------------------------|------------|----------------------|-----------|-------------------------------|--|--|

|          |                         | A SI      | DE                            | B SIDE     |                      |           |                               |  |  |

| Pin      | Signal Name             | Direction | Description                   | Pin        | Signal Name          | Direction | Description                   |  |  |

| 1 2      | GND<br>NC               | -         |                               | 124        | GND<br>PEX_PRSNT_GND | - 0       | Present GND form C2010 to UBB |  |  |

| 3        | PEX_PRSNT_GND           | 0         | Present GND form C2010 to UBB | 123        | PEX PRSNT GND        | 0         | Present GND form C2010 to UBB |  |  |

| 4        | GND                     | -         |                               | 121        | GND                  | -         |                               |  |  |

| 5        | NC                      | -         |                               | 120        | PE_RST_N             | 0         | PCIe Reset signal to UBB      |  |  |

| 6        | NC                      | -         |                               | 119        | P12V_HOST_GD         | 0         | 12V Power on control to UBB   |  |  |