# A Novel, Scalable, Energy Proportional Architecture for 48V to PoL Direct Conversion

Paolo Sandri Product Marketing Director STMicroelectronics

OPEN HARDWARE. OPEN SOFTWARE. OPEN FUTURE.

## Data Center Power Challenges

- Data Center Energy Consumption (US Department of Energy Study)

- US data centers consumed about 70 billion kilowatt-hours of electricity in 2014

- Total US data center energy consumption to grow by 4 percent between now and 2020

- Efficiency improvements played an enormous role in taming the growth rate of the data center industry's ٠ energy consumption.

- If stayed at efficiency levels of 2010, data centers would have consumed close to 40 billion kWh more than • they did in 2014

- Higher Power Needed by Silicon Key Components

- CPU power demand going above 240W

- GPU and Networking ASICs power demand above 350W •

- DDR power increase due to faster memory and higher number of DIMMs •

- More Efficient Data Center and Power Architectures are Needed

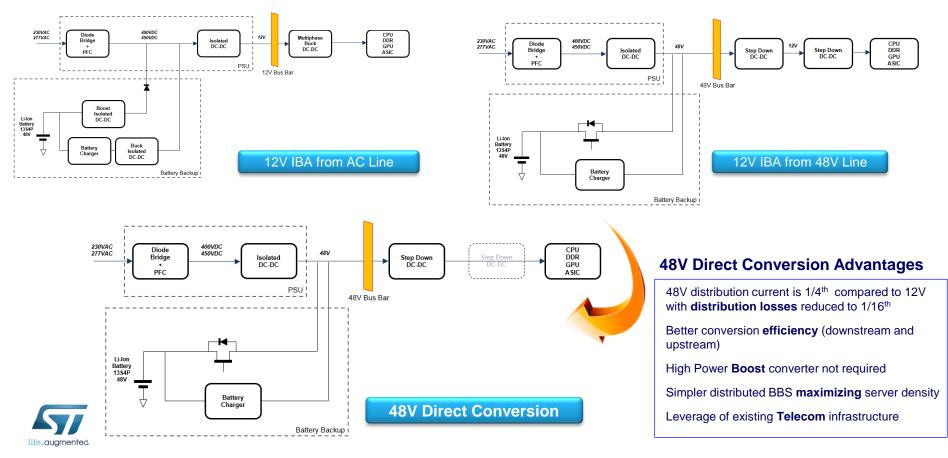

## **Power Distribution Overview**

life.auamented

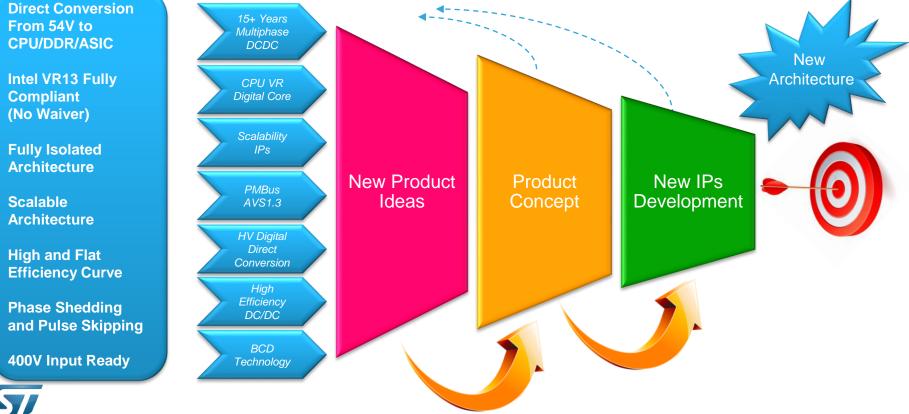

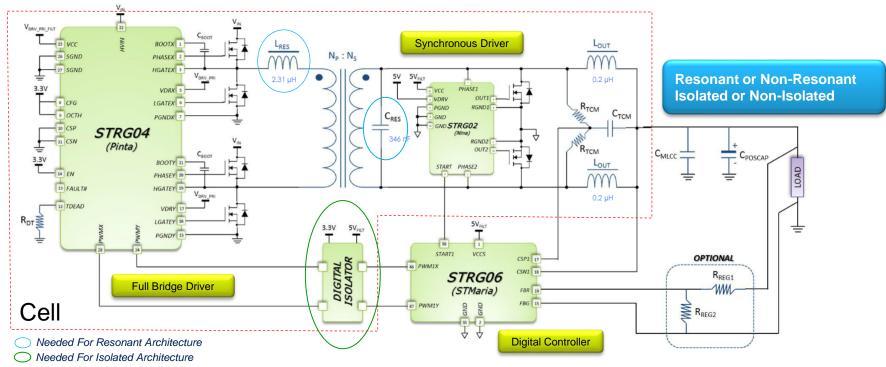

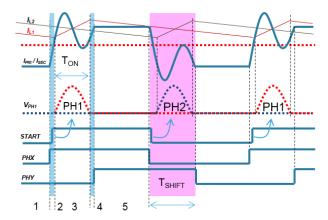

### New Architecture: Resonant Current Doubler

STRG06 Multiphase Resonant Constant On Time Digital Controller 6 interleaved Cells (automatically turned on/off by load request) with PMBUS

STRG04 100V Full Bridge Driver with programmable predictive control for zero voltage operations in constant phase shift control

STRG02 Single wire controlled Synchronous Rectifier able to zero voltage and zero current operations

#### STRG06 **Digital Commands and Current Sensing** Cell Cell Cell Cell Cell Cell #2 #3 #1 #4 #5 #6 Load **Power Level**

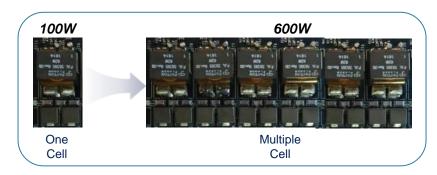

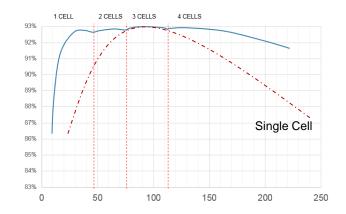

### Architecture Scalablility

7

#### More Power $\rightarrow$ More Cells

- Design Only One Cell to Design a Flexible System

- Support up to 6 Cells

- Automatic Interleaving Among Cells

- Automatic Cell Turn on/off Management

- Active Current Balancing Among Cells

- Pulse Skipping Mode When in Single Cell

## Architecture Key Advantages

- Fully Isolated, Resonant or Non-Resonant Direct Conversion

- 54V  $\rightarrow$  V<sub>CORE</sub>(1.xV), V<sub>DDR</sub>(1.2V), V<sub>SOC</sub>(0.8V), V<sub>IBC</sub>(12V, 5V, 3.3V)

- Maximum Efficiency Across Full Load Range

- ZVS and ZCS under any working conditions

- Energy Proportional Management → Dynamic Cell Management, Pulse Skipping

- No Heat Sink Required

- OpEx savings enhances system and datacenter performance/watt

- Scalable and Flexible

- · Converter Cells are paralleled and interleaved

- · System scalability according to the load power demand

- Variable Frequency in CCM and DCM

- Instantaneous turn-on of resonant converters when load increases

- · Resonant or Non-Resonant Mode of Operations

- Any Digital Load (CPU, GPU, DDR, ASICs)

- · High Bandwidth to sustain CPUs' load transient

- · Easy to design and to compensate like a Buck converter

- Up and down reference transitions → Sink mode operations

- Minimized noise content for closer proximity to Digital Loads

- High Power Density and Telemetry (PMBus™, AVS1.3)

### Fully Isolated Option

- This Architecture Natively Supports Full Isolation

- Controller at secondary side for direct interaction with SVI/PMBus signals from Load

- Controller directly manages remote sense functions •

- Primary side is driven through digital isolator (when isolation is needed) •

- Electrical Isolation provided by the transformer •

- No direct connection of the 48V, or -48V, input line to the load

- Safety Isolation

- Required above 60VDC

- 400V Input ready topology

- **Optional Feature**

- If Isolation is not Required Digital Isolator can be Removed

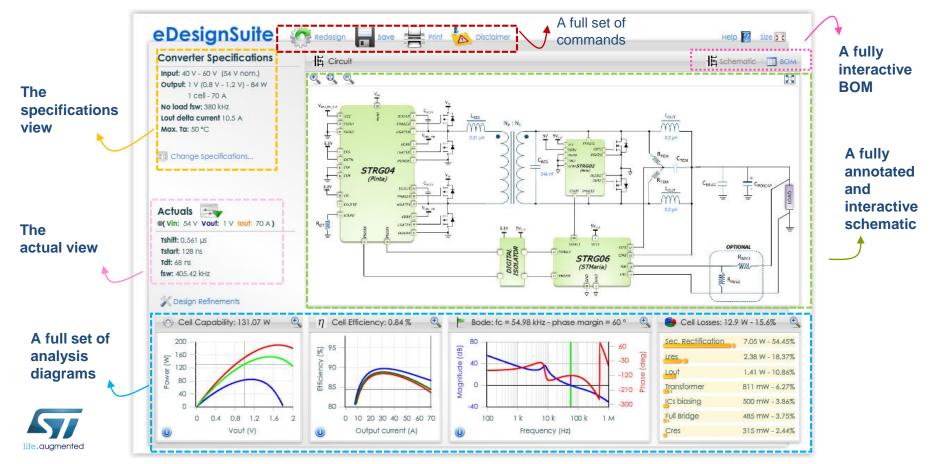

# eColumbus Design Tool

## Developments Tools

A complete set of software tools, HW programmers and Technical Collaterals are available to support custom application designs

- NVM Flasher Tool (2<sup>nd</sup>)

- Allows Programming STRG06 on board in a few simple steps

- Totally safe process since it is impossible altering the parameters by this tool

- POWER MASTER Tool (1<sup>st</sup>)

- Device & Application Configuration definition

- Security: different rights for different operators

- NVM file (Non Volatile Memory) generation

Technical documentation available (3<sup>rd</sup>)

• Detailed command sequence to support writing the NVM file by PMBUS on board in production line

54V → 1.8V Intel VR13

life.augmented

| Conversion<br>Type    | Application    | Output Current<br>and Power | Number of<br>Cells |

|-----------------------|----------------|-----------------------------|--------------------|

| 54V <del>→</del> 1.8V | Intel VR13 CPU | 165W TDC<br>360W Peak       | 4                  |

| 54V → 1.2V            | VDDQ DDR3/4    | 120A - 150W                 | 2                  |

| 54V → 0.9V            | ASIC Core      | 300A - 270W                 | 6                  |

| 54V <del>→</del> 12V  | Point of Load  | 42A - 500W                  | 1                  |

| 54V → 1V              | Point of Load  | 80A - 80W                   | 1                  |

| 54V → 3.3V            | Point of Load  | 46A - 150W                  | 1                  |

Same Scalable Topology for Different Point of Load Ideal for Power Modules Applications

54V -> 12V POL

54V -> 1V POL

54V -> 3.3V POL 1/8th Brick

## Summary 13

Innovative Resonant Current Doubler Architecture for 48V to PoL Direct Conversion Addressing Data Center Power Needs

Fully Isolated, Scalable, Maximized Flat Efficiency (ZVS, ZCS), Energy Proportional Able to Support Any Load (DDR, GPU, ASIC)

Fully Compliant to Intel and Other Brand CPUs

Flexible Architecture Extendable to Direct Conversion from 400V Bus

Available in Mass Production Since 2016

## **OPEN** Compute Project