# Inspur 4 Socket Server Whistler System Design SPEC

# Rev 0.1

Author:

**Inspur Whistler Team**

# Table of Contents

| 1. | Licen            | se                        | . 4 |

|----|------------------|---------------------------|-----|

| 2. | Revision History |                           |     |

| 3. | Scope            | 2                         | 12  |

| 4. | Over             | /iew                      | 12  |

|    | 4.1              | Overview                  | 12  |

|    | 4.2              | Product Overview          | 12  |

|    | 4.3              | Product standard          | 12  |

| 5. | Physi            | cal Specifications        | 14  |

|    | 5.1              | Block Diagram             | 14  |

|    | 5.2              | Placement and Form Factor | 15  |

|    | 5.3              | CPU and Memory            | 17  |

|    | 5.4              | PCH                       | 17  |

|    | 5.5              | PCIe Usage                | 18  |

|    | 5.6              | MB PCB Stack Up           | 19  |

| 6. | I/O Sy           | ystem                     | 20  |

|    | 6.1              | PCle x 16 Slot            | 20  |

|    | 6.2              | Riser Card Type           | 21  |

|    | 6.3              | DIMM Slot                 | 24  |

|    | 6.4              | Network                   | 24  |

|    | 6.5              | USB                       | 24  |

|    | 6.6              | sSATA                     | 25  |

|    | 6.7              | M.2                       | 26  |

|    | 6.8              | Fan                       | 26  |

|    | 6.9              | LED                       | 27  |

|    | 6.10             | TPM                       | 27  |

|    | 6.11             | Header                    | 27  |

| 7. | Powe             | r system                  | 27  |

|    | 7.1              | System Power budget       | 27  |

|     | 7.2    | Power Simple Topology                | 28 |

|-----|--------|--------------------------------------|----|

|     | 7.3    | Input voltage Level                  | 28 |

|     | 7.4    | DC-DC Power Design                   | 29 |

| 8.  | BIOS   |                                      | 31 |

|     | 8.1    | BIOS Description                     | 31 |

|     | 8.2    | BIOS Features                        | 31 |

| 9.  | вмс    |                                      | 36 |

|     | 9.1 N  | Main Feature                         | 37 |

|     | 9.2 lr | ntegrated BMC Hardware               | 37 |

| 10. | Ther   | mal Design Requirements              | 38 |

|     | 10.1   | Data Center Environmental Conditions | 38 |

|     | 10.2   | Server operational condition         | 39 |

|     | 10.3   | Thermal kit requirements             | 40 |

| 11. | Envir  | onmental and Regulations             | 41 |

|     | 11.1   | Motherboard high altitude            | 41 |

|     | 11.2   | Motherboard relative humidity        | 41 |

|     | 11.3   | Motherboard Temperature              | 41 |

|     | 11.4   | Full system high altitude            | 41 |

|     | 11.5   | Full system relative humidity        | 41 |

|     | 11.6   | Full system Temperature              | 41 |

|     | 11.7   | Full system Vibration & Shock        | 42 |

| 12. | Mecl   | nanical                              | 42 |

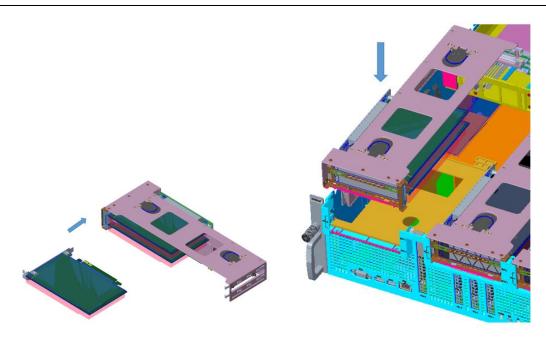

|     | 12.1   | External Chassis                     | 42 |

|     | 12.2   | HDD Carrier                          | 43 |

|     | 12.3   | Fan Module                           | 44 |

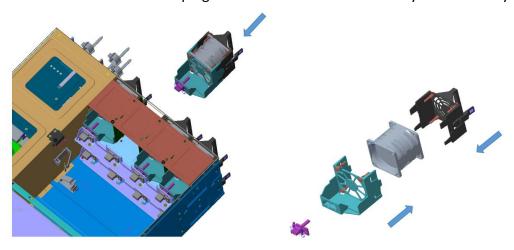

|     | 12.4   | PCIE Module                          | 44 |

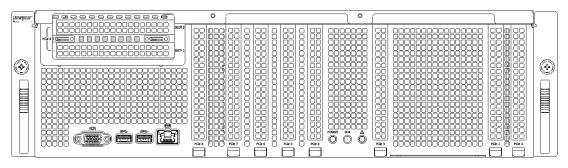

|     | 12.5   | Front View                           | 45 |

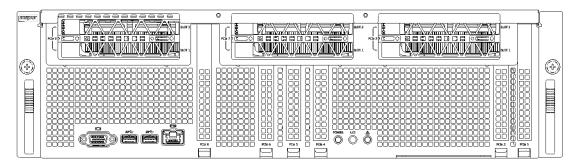

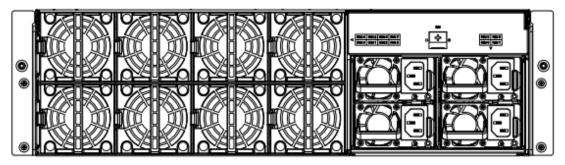

|     | 12.6   | Rear View                            | 46 |

| 13. | Labe   | ls and Markings                      | 46 |

| 13.1 | Labels   | 46 |

|------|----------|----|

| 13.2 | Markings | 46 |

### 1. License

## Open Compute Project Contribution License Agreement

### As of November 2, 2018

This Contribution License Agreement ("Agreement") is entered into between the entity identified below and its Bound Entities (collectively, "Contributor"), and Open Compute Project Foundation ("OCP") as of the date set forth below ("Effective Date").

#### Definitions.

- a. "Bound Entities" means the entity identified below and any entities that the Bound Entity Controls.

- b. "Contribution(s)" means the proposed specification(s) or portion(s) thereof submitted by Contributor, as identified in the Appendices.

- "Control" means direct or indirect control of more than 50% of the voting power to elect directors of that corporation, or for any other entity, the power to direct management of such entity.

- d. "Granted Claims" are those patent claims that Contributor owns or controls, including those patent claims that Contributor acquires or controls after the Effective Date, that are infringed by the Permitted Uses. Granted Claims include only those patent claims that are infringed by the implementation of any portions of the Specification where the Specification described the functionality causing the infringement in detail and does not merely reference the functionality causing the infringement. Granted Claims under this Agreement exclude those patent claims that would be infringed by an implementation of the Specification if Contributor's Contribution to that Specification were removed.

- "Licensee" means any person or entity who exercises copyright or patent rights granted under this Agreement, and any person or entity Licensee Controls.

- f. "Permitted Uses" means making, selling, offering for sale, importing or distributing any implementation of the Specification 1) only to the extent it implements the Specification and 2) so long as all required portions of the Specification are implemented. Permitted Uses do not extend to any portion of an implementation that is not included in the Specification.

- g. "Related Entity" means 1) any entity that Controls the Bound Entity ("Upstream Entity"), and 2) any other entity that is Controlled by an Upstream Entity that is not itself a Bound Entity.

- "Specification" means the proposed specification identified in the attached Appendices and any Versions thereof.

- i. "Version" means the version of the Specification to which the Contribution is made and any subsequent versions thereof or revisions thereto leading up to or culminating in the final adopted Specification. For the avoidance of doubt, this Agreement, together with the applicable Appendix, will apply to each subsequent version of the Specification without the need for separately executed Appendices for all such subsequent versions of the Specification.

- 2. Contributions and Structure. Contributor must sign an Appendix, referencing and incorporating this Agreement, before submitting any Contribution for approval or incorporation into a Specification by OCP. There will be one or more Appendices attached to this Agreement in the form of the Appendix attached hereto. Contributor may make multiple Contributions by completing and executing an Appendix for each Contribution. Contributor may make Contributions to multiple Specifications through the use of Appendices with different letters indications. Each Appendix will be lettered for each Specification to which the Contributor makes a Contribution (e.g. Appendix A-1, B-1, and C-1 for Contributions to different Specifications), and numbered for each Contribution made to a particular Specification (e.g. Appendix A-1, A-2, and A-3 for multiple Contributions to the same Specification).

#### Licenses.

a. <u>Copyright Grant</u>. Contributor hereby grants Licensee a perpetual (for the duration of the applicable copyright), worldwide, nonexclusive, no-charge, royaltyfree, copyright license, without any obligation of accounting to Contributor, to reproduce, prepare derivative works of, publicly display, publicly perform, sublicense, distribute and implement any Contribution to the full extent of Contributor's copyright interest in the Contribution.

#### b. Patents

- i. Patent Non-Assert. Contributor, on behalf of itself and its successors in interest and assigns, irrevocably promises not to assert Contributor's Granted Claims against Licensee for Licensee's Permitted Uses, subject to the terms and conditions of this Section 3(b). This is a personal promise directly from Contributor to Licensee, and Licensee acknowledges as a condition of benefiting from it that no rights from Contributor are received from suppliers, distributors or otherwise in connection with this promise. This promise also applies to Licensee's Permitted Uses of any other specifications incorporating all required portion of the Specification.

- Bankruptcy. Solely for purposes of Section 365(n) of Title 11, United States Bankruptcy Code and any equivalent law in any foreign jurisdiction, this promise will be treated as if it were a license and Licensee may elect to retain Licensee's rights under this promise if Contributor (or any owner of any patents or patent applications referenced herein), as a debtor in possession, or a bankruptcy trustee, reject this non-assert.

Open Compute Project Contribution License Agreement 112018

2

ii. Patent License Commitment. In addition to the rights granted in Section 3(b)(i), Contributor, on behalf of itself and its successors in interest and assigns, agrees to grant Licensee a no-charge, royalty-free license to its Granted Claims on reasonable and non-discriminatory terms, where such license applies only to those Granted Claims infringed by the implementation of the Contribution(s) alone or by combination of the Contribution with the Specification solely for Licensee's Permitted Uses.

#### iii. Termination

- <u>Due to Claims by Licensee</u>. All rights, grants, and promises made by Contributor to Licensee under this Agreement are terminated if Licensee files, maintains, or voluntarily participates in a lawsuit against Contributor or any person or entity asserting that its Permitted Uses infringe any Granted Claims Licensee would have had the right to enforce had Licensee signed this Agreement, unless that suit was in response to a corresponding suit first brought against Licensee.

- Due to Claims by Contributor or Contributor's Related Entities. If a

Related Entity of Contributor files, maintains, or voluntarily

participates in a lawsuit asserting that a Permitted Use infringes

any Granted Claims Patents it would have had the right to enforce

had it signed this Agreement, then Contributor relinquishes any

rights, grants, and promises Contributor has received from other

signatories of this Agreement, unless a) Contributor's promise to

Licensee was terminated pursuant to Section 3(b)(iii)(1), or b) that

suit was in response to a corresponding suit first brought by

Licensee against the Related Entity.

- Other Rights Reserved. Contributor hereby reserves all rights not expressly granted in this Agreement. No additional licenses or rights whatsoever (including without limitation any patent licenses) are granted by implication, exhaustion, estoppel or otherwise.

- 5. Representations, Warranties, Disclaimers and Limitation of Liability. Contributor represents and warrants that the Contribution is Contributor's original work, except to the extent Contributor may have informed OCP in writing prior to or at the time of Contribution. EXCEPT FOR THE WARRANTIES EXPRESSLY STATED IN THIS SECTION 5, THE CONTRIBUTION IS PROVIDED WITHOUT WARRANTY OF ANY KIND, AND OCP ACKNOWLEDGES THAT CONTRIBUTOR DISCLAIMS ALL OTHER WARRANTIES, INCLUDING WITHOUT LIMITATION WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. IN NO EVENT WILL OCP BE LIABLE TO CONTRIBUTOR FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS AGREEMENT, WHETHER BASED IN BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Open Compute Project Contribution License Agreement 112018

6. General. This Agreement is the entire agreement between the parties on the subject matter hereof. No amendment of this Agreement will be valid unless made in writing and signed by both parties. This Agreement will be governed by the laws of the State of California, without regard to its conflict of laws principles. The parties consent to the personal and exclusive jurisdiction of courts located in California. Waiver by either party of a breach of any provision of this Agreement or the failure by either party to exercise any right hereunder will not operate or be construed as a waiver of any subsequent breach of that right or as a waiver of any other right

[Signatures on Following Page]

Open Compute Project Contribution License Agreement 112018

4

| Contributor (corporate name): Inspur                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contributor (contact information):  Email Address:chenyl@inspur.com  Mailing Address:47451 fremont blvd.  Fremont CA 93852                                                                                                                                                                                                                                                                                      |

| BY SIGNING BELOW, I CERTIFY THAT I AM AUTHORIZED TO EXECUTE THE OPEN COMPUTE PROJECT LICENSE AGREEMENT ON BEHALF OF THE CONTRIBUTOR NAMED ABOVE, THAT THE CONTRIBUTOR ABOVE IS BOUND BY THE OPEN COMPUTE PROJECT LICENSE AGREEMENT, AND THAT ALL PROMISES MADE HEREIN RELATING TO THE CONTRIBUTIONS OR THE SPECIFICATIONS ARE COMMITMENTS OF THE CONTRIBUTOR.  Signature:  Director  Effective Date: 03/11/2019 |

| OPEN COMPUTE PROJECT FOUNDATION                                                                                                                                                                                                                                                                                                                                                                                 |

| Accepted by:                                                                                                                                                                                                                                                                                                                                                                                                    |

| Title:                                                                                                                                                                                                                                                                                                                                                                                                          |

| P.O. Box 82287<br>Austin, Texas 78708                                                                                                                                                                                                                                                                                                                                                                           |

Open Compute Project Contribution License Agreement 112018

8 May, 2019

5

# Open Compute Project Contribution License Agreement

# Form of Appendix

| Name of Proposed Specification:                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Whistler                                                                                                                                                                                                                                                                                                                                                                      |

| Contribution (e.g. Entire proposed Specification, or portion of proposed specification):  4 Socket Olympus server                                                                                                                                                                                                                                                             |

| Contributor (corporate name): Inspur                                                                                                                                                                                                                                                                                                                                          |

| Contributor (contact information):                                                                                                                                                                                                                                                                                                                                            |

| Email Address:chenyl@Inspur.com                                                                                                                                                                                                                                                                                                                                               |

| Mailing Address: 47451 Fremont Blvd.                                                                                                                                                                                                                                                                                                                                          |

| Fremont CA                                                                                                                                                                                                                                                                                                                                                                    |

| BY SIGNING BELOW, I CERTIFY THAT I AM AUTHORIZED TO EXECUTE THE OPEN COMPUTE PROJECT LICENSE AGREEMENT ON BEHALF OF THE CONTRIBUTOR NAMED ABOVE, THAT THE CONTRIBUTION AND CONTRIBUTOR ABOVE ARE BOUND BY THE OPEN COMPUTE PROJECT LICENSE AGREEMENT, AND THAT ALL PROMISES MADE HEREIN RELATING TO THE CONTRIBUTION OR THE SPECIFICATION ARE COMMITMENTS OF THE CONTRIBUTOR. |

| Signature:                                                                                                                                                                                                                                                                                                                                                                    |

| Title: Director                                                                                                                                                                                                                                                                                                                                                               |

| Effective Date: 03/11/2019                                                                                                                                                                                                                                                                                                                                                    |

Open Compute Project Contribution License Agreement Form of Appendix 6

# Open Compute Project Contribution License Agreement

# Appendix A-1

| Name of Proposed Specification:                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Contribution (e.g. Entire proposed Specification, or portion of proposed specification):                                                                                                                                                                                                                                                                                      |

| Contributor (corporate name):                                                                                                                                                                                                                                                                                                                                                 |

| Contributor (contact information):                                                                                                                                                                                                                                                                                                                                            |

| Email Address:                                                                                                                                                                                                                                                                                                                                                                |

| Mailing Address:                                                                                                                                                                                                                                                                                                                                                              |

| BY SIGNING BELOW, I CERTIFY THAT I AM AUTHORIZED TO EXECUTE THE OPEN COMPUTE PROJECT LICENSE AGREEMENT ON BEHALF OF THE CONTRIBUTOR NAMED ABOVE, THAT THE CONTRIBUTION AND CONTRIBUTOR ABOVE ARE BOUND BY THE OPEN COMPUTE PROJECT LICENSE AGREEMENT, AND THAT ALL PROMISES MADE HEREIN RELATING TO THE CONTRIBUTION OR THE SPECIFICATION ARE COMMITMENTS OF THE CONTRIBUTOR. |

| Signature: The Fr Fr                                                                                                                                                                                                                                                                                                                                                          |

| Title:                                                                                                                                                                                                                                                                                                                                                                        |

| Effective Date:                                                                                                                                                                                                                                                                                                                                                               |

| Open Compute Project Contribution License Agreement Appendix A-1 8                                                                                                                                                                                                                                                                                                            |

## Signature Certificate

Document Reference: 2LYBC4IT83UP8BE3R78VR9

Muti-Factor Digital Fingerprint Checksum william chen Party ID: C9U3K5JALKR6JESZYWY3D9 IP Address: 12.222.9.98

VERHIED EMAIL: Chenyl@Inspur.com

ba77f2bfbf22c01d2ee83233b1f731a0da4f03ba

Timestamp Audit

2019-03-11 15:38:38 -0700 All parties have signed document. Signed copies sent to: Michael Schill and

william chen.

2019-03-11 15:38:38 -0700 Document signed by william chen (chenyl@inspur.com) with drawn signature.

12.222.9.98

2019-03-11 15:38:37 -0700 william chen verified email address 'chenyl@inspur.com', - 12.222.9.98

2019-03-11 15:32:48 -0700 Generated Document from Online Form OCPCLA 11022018 (OCPCLA-11022018-7680ff).

- 12.222.9.98

2019-03-11 15:27:18-0700 Online Form viewed by william chen (chenyl@inspur.com). - 12.222.9.98

This signature page provides a record of the online activity executing this contract,

Page 1 of 1

## 2. Revision History

| Version | Date      | Description     |

|---------|-----------|-----------------|

| 0.1     | 5/21/2019 | Initial Release |

|         |           |                 |

|         |           |                 |

|         |           |                 |

Note: Because the product version upgrade or other reasons, the contents of this document will not be updated on a regular basis. Unless otherwise agreed, this document used only as a guide, in this document, all statements, information and advice does not constitute any express or implied guarantees.

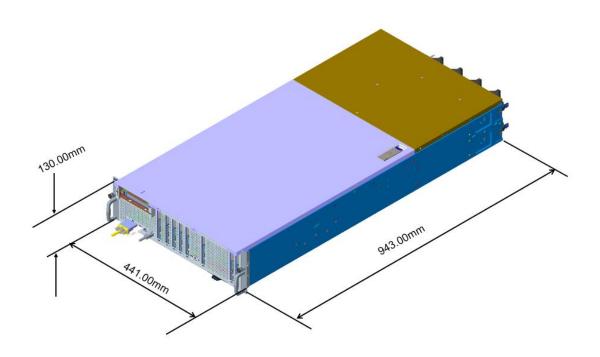

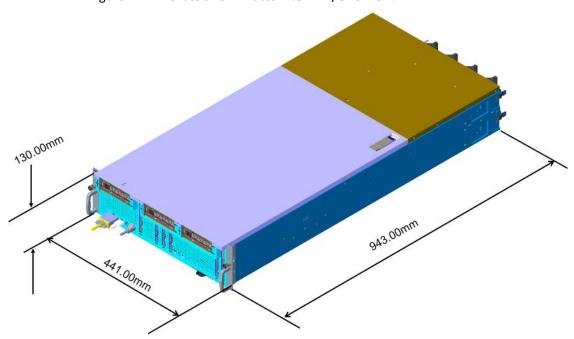

### 3. Scope

This specification describe a kind of 3U, 4 sockets server system. It is designed a flexible system architecture based on Intel Purley Platform. It can be expanded to GPU BOX, 32\*M.2 SSD and maximum support 3\*GPU cards. There are 2 kinds of different mechanical structure.

### 4. Overview

### 4.1 Overview

Whistler is based on Intel® Sky Lake-SP CPU architecture. The motherboard supports up to 48 DIMMs. Whistler was designed in the Q1 of 2018.

#### 4.2 Product Overview

Whistler is a completely independent research and development of server products. Based on Intel® Sky lake-SP CPU architecture, using Lewisburg chipset. Support four mainstream Intel Xeon Sky Lake-SP 81xx/61xx/51xx series processors. Support 48 DIMMs DDR4 memory, the biggest support to 2666 MHZ. Support Lewisburg-1G PCH and AST2500 is managed chipset. There are 9 pcs PCIe Slots on board and maximum support 12 pcs slots. Supports 5 pcs M.2 SSD on board. Structure, storage, PCI extension, power supply, fan and other parts modular design. Centralized power supply design, to realize saving energy and reducing consumption.

### 4.3 Product standard

| СРИ      |          |      |        |     |         |

|----------|----------|------|--------|-----|---------|

| CPU type | Supports | four | Intel® | Sky | Lake-SP |

|                    | 81xx/61xx/51xx series processors (TDP 205W)                                                                                                                                                                      |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Connecter          | Four Socket-P0 slots                                                                                                                                                                                             |

| Chipset            |                                                                                                                                                                                                                  |

| Chipset type       | PCH LBG-1G                                                                                                                                                                                                       |

| RAM                |                                                                                                                                                                                                                  |

| RAM type           | DDR4 RDIMM/LRDIMM/AEP/NVDIMM                                                                                                                                                                                     |

| RAM slot quantity  | 48                                                                                                                                                                                                               |

| RAM total capacity | Total capacity 6144GB (single 128GB)                                                                                                                                                                             |

| I/O Connecter      |                                                                                                                                                                                                                  |

| USB                | Two external USB 3.0 ports(Front), Internal                                                                                                                                                                      |

| ОЗВ                | USB 2.0 port                                                                                                                                                                                                     |

| VGA                | One external VGA (Front)                                                                                                                                                                                         |

| UID                | One ID pilot lamp inlay                                                                                                                                                                                          |

| Manager chipset    |                                                                                                                                                                                                                  |

|                    | Integrated one independent 1000 Mbps                                                                                                                                                                             |

| Manager chipset    | network interface, specifically for remote                                                                                                                                                                       |

|                    | management of IPMI.                                                                                                                                                                                              |

| DCI Express clot   | The motherboard supports 9 pcs PCI Express                                                                                                                                                                       |

| PCI Express slot   | 3.0 slots                                                                                                                                                                                                        |

| HDD                |                                                                                                                                                                                                                  |

| HDD type           | Support one 3.5-inch SAS/SATA HDDs and 32                                                                                                                                                                        |

| поо суре           | M.2 SSD                                                                                                                                                                                                          |

| Power supply       |                                                                                                                                                                                                                  |

| PSU spec           | The whole system adopts three specifications of PSU, the power is 1600W, and the maximum configuration is 4 power supplies.  According to the system configuration, the appropriate PSU and PSU redundancy modes |

|                    | are selected to support 2+2 redundancy under certain configuration conditions.                                                                                                                                   |

|                                  | The main specifications is 1600W PSU                                                          |  |  |  |

|----------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| Input power                      | AC 180-264V, Typical 230V                                                                     |  |  |  |

|                                  | DC 164-300V, Typical 270V                                                                     |  |  |  |

| Environmental Requirements       |                                                                                               |  |  |  |

| Altitude (Mathematics and)       | 1500m (operational) or 12192m(non -                                                           |  |  |  |

| Altitude (Motherboard)           | operational)                                                                                  |  |  |  |

| Altitudo (Full quetoro)          | 1500m (operational) or 12192m(non -                                                           |  |  |  |

| Altitude (Full system)           | operational)                                                                                  |  |  |  |

| Operating and storage relative   | 100/ to 000/ (non condensing)                                                                 |  |  |  |

| humidity (Full system)           | 10% to 90% (non-condensing)                                                                   |  |  |  |

|                                  | -5°C to +45°C ;                                                                               |  |  |  |

| Operating temperature rang       | Note: It is suggested to power on to work after                                               |  |  |  |

| (Motherboard)                    | standing for 1 hour in the data center, after                                                 |  |  |  |

|                                  | long time transportation.                                                                     |  |  |  |

| Operating townships reacciffull  | -5°C to +35°C;                                                                                |  |  |  |

| Operating temperature range(Full | Note: It is suggested to power on to work after standing for 1 hour in the data center, after |  |  |  |

| system)                          | long time transportation.                                                                     |  |  |  |

|                                  |                                                                                               |  |  |  |

| Storage temperature range        | -40°C to +70°C                                                                                |  |  |  |

| (Motherboard)                    |                                                                                               |  |  |  |

| Storage temperature range(Full   | -40°C to +70°C                                                                                |  |  |  |

| system)                          |                                                                                               |  |  |  |

| Transportation temperature       | -40°C to +70°C (short-term storage)                                                           |  |  |  |

| range(Motherboard)               | ,                                                                                             |  |  |  |

| Transportation temperature       | -40°C to +70°C (short-term storage)                                                           |  |  |  |

| range(Full system)               |                                                                                               |  |  |  |

# **5. Physical Specifications**

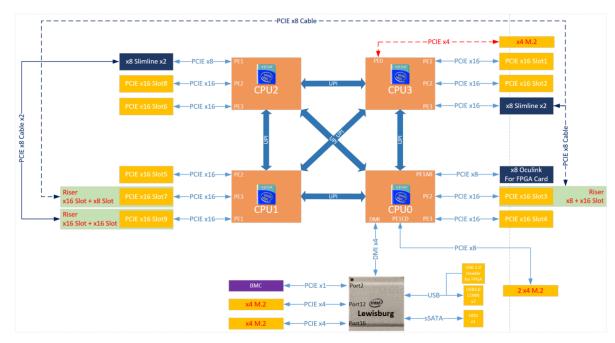

# 5.1 Block Diagram

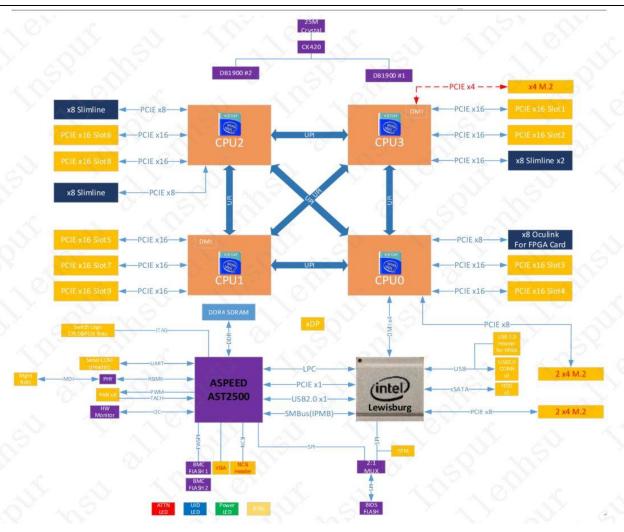

Figure 5-1 illustrates the functional block diagram of the Motherboard.

Figure 5-1 Block Diagram

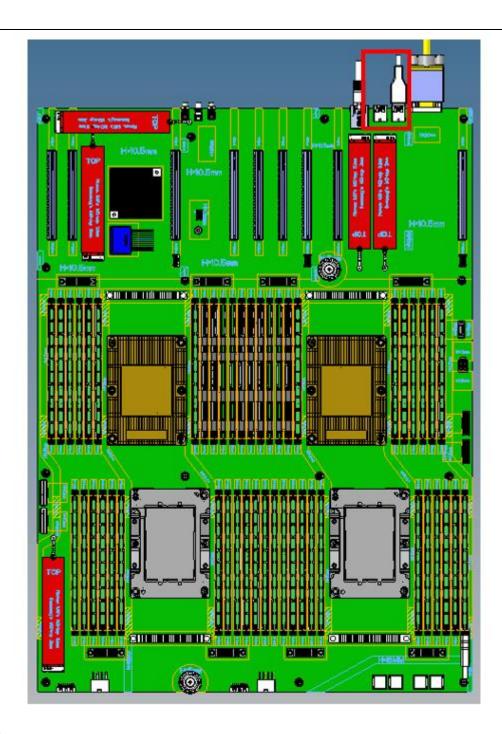

### 5.2 Placement and Form Factor

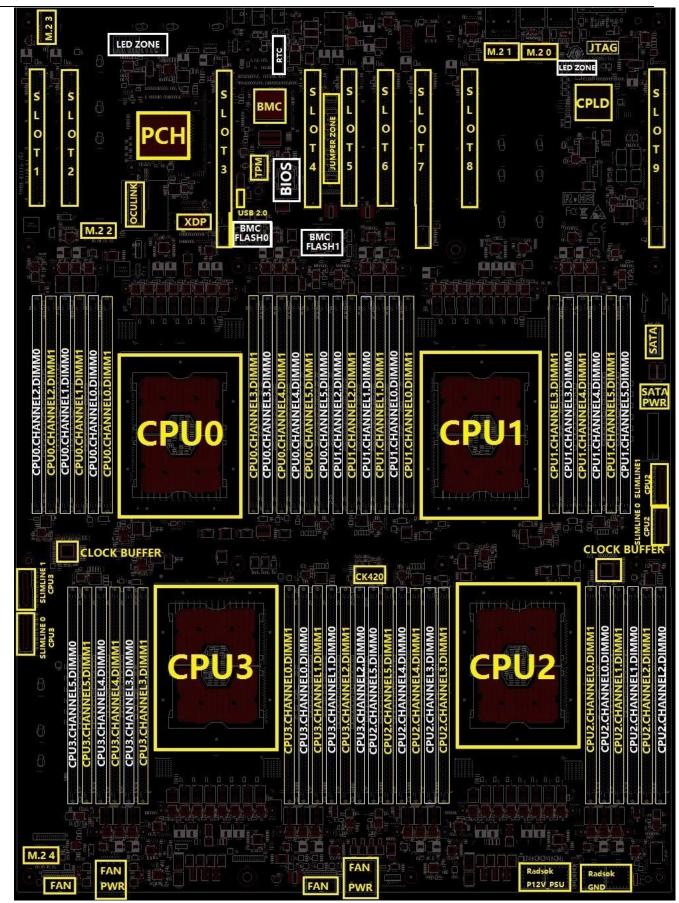

Board form factor is 16.7 inch by 22.7 inch (16.7"x22.7"). Figure 5-2 is board placement. The placement is meant to show key components 'relative positions, exact dimension and position information would be exchanged by DXF format for layout and 3D model of mechanical.

Figure 5-2 Placement

### 5.3 CPU and Memory

#### 5.3.1 CPU

The motherboard supports all Intel® Sky Lake -SP processors with TDP up to 205W.

- Support four Sky Lake-SP processors up to 205W TDP.

- Three full-width Intel UPI links up to 10.4 GT/s/direction for Sky Lake-SP processor.

- Up to 28 cores per CPU (up to 56 threads with Hyper-Threading Technology).

- Single Processor mode and Two-CPU mode are both supported

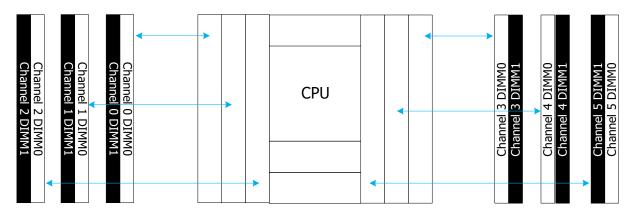

#### 5.3.2 DIMM

The motherboard has DIMM subsystem designed as below:

- DDR4 direct attach memory support on CPU0, CPU1, CPU2 and CPU3.

- 6x channels DDR4 registered memory interface on each CPU

- 2x DDR4 slots on each Chanel (total 48x DIMMs)

- Support DDR4 speeds up to 2666MT/s 1DCP and 2DCP

- Support DDR4 RDIMM/LRDIMM/AEP/NVDIMM

- Support SR, DR, QR and 8R DIMMs

- Up to maximum 6144 GB with 128 GB DRAM DIMM

- Follow updated JEDEC DDR4 specification with 288 pin DIMM socket

- Memory support matrix for DDR4 is as Table 5-1

| 2 Slots Per Channel |                    |  |

|---------------------|--------------------|--|

| 1 DIMM Per Channel  | 2 DIMM per Channel |  |

| 2666 MT/s           | 2666 MT/s          |  |

Table 5-1

### 5.4 PCH

The motherboard uses Intel<sup>®</sup> Lewisburg chipset, which supports following features:

- Two external USB 3.0 port(Front), One internal USB 2.0 port;

- 4x slimline x8 connector use x16 PCIE riser card;

- 1x Oculink connector use FPGA card;

- LPC interface, mux with BMC to enable BMC the capability to perform BIOS upgrade and Recovery

- SPI interface for TPM header

- SMBUS interface (master & slave)

- Intel® Server Platform Services (SPS) 4.0 Firmware with Intel® Node Manager

- PECI access to CPU

- SMLink0 connect to BMC

- Intel® Manageability Engine (ME) obtain HSC PMBus related information directly.

- Intel® ME SMLink1 connects to Hot swap controller PMBus interface by default.

- BMC connected to HSC PMBus, so it masters HSC PMBus related feature flexibly.

- Temperature sensors reading from BMC

- PCH SKUs

- Board design shall support all PCH SKUs in terms of power delivery and thermal design.

### 5.5 PCIe Usage

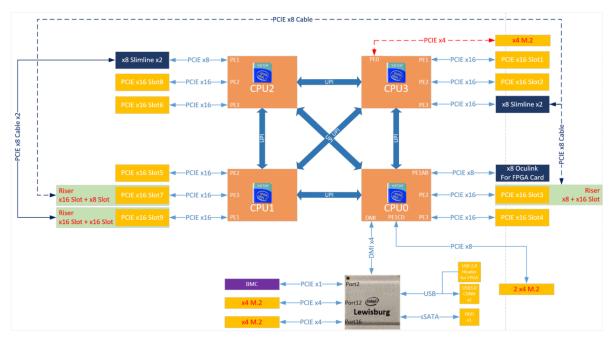

PCIe lanes are configured according to Figure 5-3 and Table 5-2:

Figure 5-3 PCIe Usage

| PCIE Resource Configuration |               |      |                       |  |

|-----------------------------|---------------|------|-----------------------|--|

|                             | PE1(Lane0-7)  | X8   | Oculink for FPGA card |  |

| CPU0                        | PE1(Lane8-15) | 2 X4 | M.2                   |  |

| CPUU                        | PE2(Lane0-15) | X16  | PCIe Slot 3           |  |

|                             | PE3(Lane0-15) | X16  | PCIe Slot 4           |  |

|                             | PE1(Lane0-15) | x16  | PCIe Slot 9           |  |

| CPU1                        | PE2(Lane0-15) | X16  | PCIe Slot 5           |  |

|                             | PE3(Lane0-15) | X16  | PCIe Slot 7           |  |

|                             | PE1(Lane0-15) | 2 x8 | 2 x8 Slimline         |  |

| CPU2                        | PE2(Lane0-15) | x16  | PCIe Slot 8           |  |

|                             | PE3(Lane0-15) | X16  | PCIe Slot 6           |  |

|                             | PE0(Lane0-7)  | 2 X4 | M.2                   |  |

| CPU3                        | PE1(Lane0-15) | x16  | PCIe Slot 1           |  |

|                             | PE2(Lane0-15) | X16  | PCIe Slot 2           |  |

|                             | PE3(Lane0-15) | 2 x8 | 2 x8 Slimline         |  |

Table 5-2

# 5.6 MB PCB Stack Up

| Layer     | Plane Description | Plane Description |       | COPPER | Copper<br>Weight | DK   |

|-----------|-------------------|-------------------|-------|--------|------------------|------|

|           |                   |                   | (mil) |        | (oz)             |      |

|           | solder mask       |                   | 0.4   |        |                  |      |

| Signal1   | SIGNAL            |                   | 1.6   | HTE    | 1                |      |

| PP        | 1080 RC65%*1      |                   | 2.7   |        |                  | 3.68 |

| Plane 2   | GND               |                   | 1.2   | RTF    | 1                |      |

| Core      | 3313 RC56%*1      |                   | 4     |        |                  | 3.86 |

| Signal 3  | SIGNAL            |                   | 1.2   | RTF    | 1                |      |

| PP        | 2116 RC60*1       |                   | 4.4   |        |                  | 3.78 |

| Plane 4   | GND               |                   | 1.2   | RTF    | 1                |      |

| Core      | 3313 RC56%*1      |                   | 4     |        |                  | 3.86 |

| Signal 5  | SIGNAL            |                   | 1.2   | RTF    | 1                |      |

| PP        | 2116 RC60*1       |                   | 4.4   | 10000  |                  | 3.78 |

| Plane 6   | GND               |                   | 1.2   | RTF    | 1                |      |

| Core      | 1086 RC58%*1      |                   | 3     |        |                  | 3.78 |

| Signal 7  | SIGNAL            |                   | 1.2   | RTF    | 1                |      |

| PP        | 2113 RC60%*3      |                   | 11    |        |                  | 3.78 |

| Plane 8   |                   |                   | 2.4   | RTF    | 2                |      |

| Core      | 3313 RC56%*1      |                   | 4     |        |                  | 3.86 |

| Plane 9   | POWER             |                   | 2.4   | RTF    | 2                |      |

| PP        | 2113 RC60%*3      | - 4               | 11    |        |                  | 3.78 |

| Signal 10 | SIGNAL            |                   | 1.2   | RTF    | 1                |      |

| Core      | 1086 RC58%*1      |                   | 3     |        |                  | 3.78 |

| Plane11   | GND               |                   | 1.2   | RTF    | 1                |      |

| PP        | 2116 RC60*1       |                   | 4.4   |        |                  | 3.78 |

| Signal 12 | SIGNAL            |                   | 1.2   | RTF    | 1                |      |

| Core      | 3313 RC56%*1      |                   | 4     |        |                  | 3.86 |

| Plane13   | GND               |                   | 1.2   | RTF    | 1                |      |

| PP        | 2116 RC60*1       |                   | 4.4   |        |                  | 3.78 |

| Signal 14 | SIGNAL            |                   | 1.2   | RTF    | 1                |      |

| Core      | 3313 RC56%*1      |                   | 4     |        |                  | 3.86 |

| Plane 15  | GND               |                   | 1.2   | RTF    | 1                |      |

| PP        | 1080 RC65%*1      |                   | 2.7   |        |                  | 3.68 |

| Signal 16 | SIGNAL            |                   | 1.6   | HTE    | 1                |      |

|           | solder mask       |                   | 0.4   |        |                  |      |

| Material  | IT170GRA with RTF | Total             | 94.2  |        |                  |      |

Figure 5-4 stack up

# 6. I/O System

This section describes the motherboard I/O system.

## **6.1** PCIe x 16 Slot

The motherboard has 9 pcs PCle x16 slots used by four kinds of PCle riser cards.

Figure 6-1 illustrates the source of PCIe x16 slots.

Figure 6-1 PCIe x16 slot

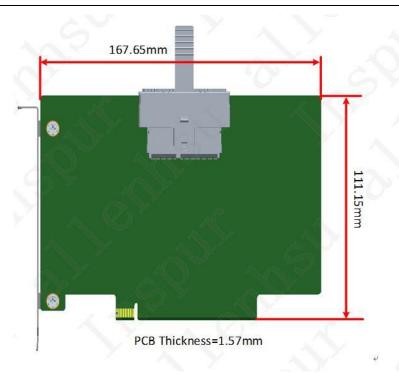

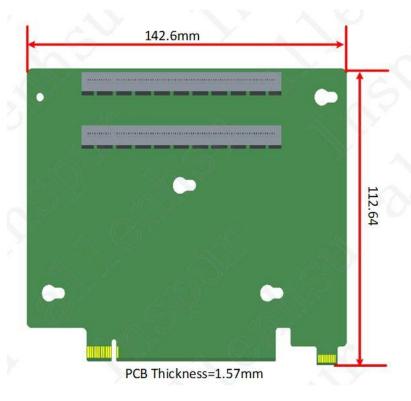

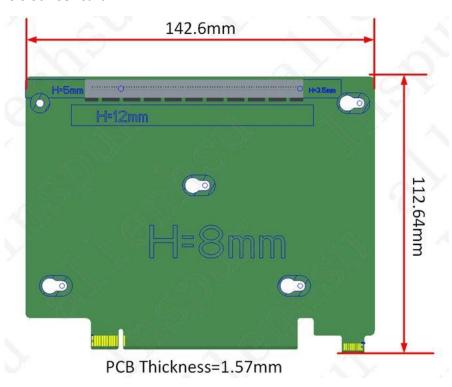

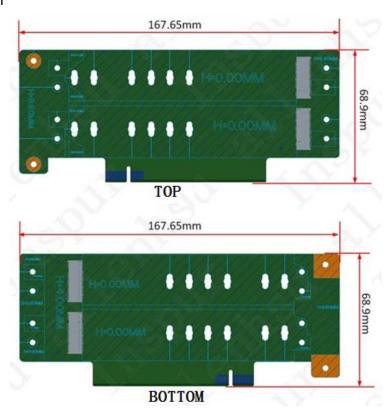

## 6.2 Riser Card Type

There are four kinds of PCIe riser cards as follow.

### 6.2.1 GPU BOX Sliver riser card

This riser card connect to HGX-1GPU BOX.

### 6.2.2 2x16 Slot riser card

This riser card can support two standards PCle x16. One connector is from PCle slot, the other one is from 2\*x8 Slimline connectors.

### 6.2.3 GPU 1x16 slot riser card

This riser card support GPU board.

### 6.2.4 4 M.2 carrier

This riser card support four M.2 cards.

### 6.3 DIMM Slot

Total 48 DIMMs, DIMM 1 is Black, DIMM0 is White.

Figure 6-2 DIMM Topology

### 6.4 Network

### 6.4.1 Management network

The motherboard has one management network interface for BMC's connection. Dedicated RJ45 port for Board management, driven by BMC through RMII/NC-SI.

### 6.5 USB

The Motherboard has two external USB2.0/3.0 connectors located in Front edge of Motherboard and one internal USB 2.0 header. BIOS should support follow devices on USB ports available on Motherboard:

- USB Keyboard and mouse

- USB flash drive (bootable)

- USB hard drive (bootable)

- USB optical drive (bootable)

### 6.6 sSATA

The motherboard can support 1x 3.5" hard disks.

## 6.6.1 1x sSATA

The motherboard has Intel® Lewisburg PCH on board, which has a sSATA controller. It support 1x sSATA 3.0 port.

Figure 6-3 SATA Topology

### 6.7 M.2

The motherboard supports 5x PCIe M.2 devices on board and 8 pcs PCIe 4x M.2 carrier as chapter 6.2.4

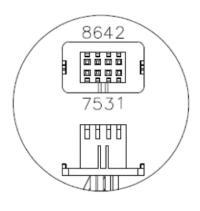

### 6.8 Fan

The motherboard holds 2 pcs system FAN connectors. Each FAN has 8 pins, which includes two DC power pins, two GND pins, two TACH pins, one PRESENT pin and one PWM pin. They are used to support dual rotor FAN that share PWM control signal and PRESENT signal but it has separate TACH signal. FAN connector pin's definition is listed in Table 6-1, and FAN connector diagram is shown in Figure 6-5. Rated voltage of FAN is 12 VDC, and rated current is 5000 mA/Max, 5750 mA.

| Pin | Definition         |

|-----|--------------------|

| 1   | INFAN 12 VDC       |

| 2   | OUTFAN 12 VDC      |

| 3   | INFAN TACH         |

| 4   | Present            |

| 5   | OUTFAN GND         |

| 6   | OUTFAN 12 VDC      |

| 7   | OUTFAN TACH        |

| 8   | INFAN & OUTFAN PWM |

Table 6-1

Figure 6-5 FAN connector

### 6.9 LED

- ► Power status LED, Green/Orange

- --When power on, turn on green LED

- --When Power off, turn on orange LED

- ► UID status LED, Blue

- --When device is selected, turn on LED

- --When device is not selected, turn off LED

- ► Attention status LED: RED

- --When system is abnormal, turn on LED

- --When system is normal or power off, turn off LED

### 6.10 TPM

The Motherboard supports one TPM with SPI interface.

### 6.11 Header

| Signal                  | Description                                 | Location | Default     |  |

|-------------------------|---------------------------------------------|----------|-------------|--|

| FM_MFG_MODE             | 1-2:Enable Manufacture Mode                 | J70      | Default 2-3 |  |

| FWI_MFG_WODE            | 2-3:Disable Manufacture Mode                | 370      |             |  |

| HDA SDO                 | 1-2:Disable Flash Override                  | J72      | Default 1-2 |  |

| HDA_SDO                 | 2-3:Enable Flash Override                   | 372      | Delault 1-2 |  |

| FM_ME_RECOVER_N         | 1-2:Normal                                  | J88      | Default 1-2 |  |

| FW_WE_RECOVER_IV        | 2-3:ME Force Update                         | 366      | Dolault 1-2 |  |

| RST RTCRST N            | 1-2:Normal Operation                        | J89      | Default 1-2 |  |

| KSI_KICKSI_N            | 2-3:Clear CMOS                              | J09      | Delault 1-2 |  |

| FM_PASSWORD_CLEAR_N     | 1-2:Normal Operation                        | J103     | Default 1-2 |  |

| FIVI_PASSVIORD_CLEAR_IN | 2-3:Clear Password                          | 3103     | Delault 1-2 |  |

|                         | 1-2: Normal Operation Also Top Swap Disable | J120     | Default 1-2 |  |

|                         | 2-3: Recover BIOS Also Top Swap Enable      |          |             |  |

|                         | 1-2: Normal                                 | J90      | Default 1-2 |  |

|                         | 2-3: BMC disable                            |          |             |  |

## 7. Power system

# 7.1 System Power budget

| Rail           | Volta | ge (V) | CPU(205W) | DIMM   | AEP    | Lewisbug-T | SATA HDD | SYS Fan | M. 2  | USB   | BMC  | PCIE (75W) | CRT  | BCM54612 | CPLD | Total (A) |

|----------------|-------|--------|-----------|--------|--------|------------|----------|---------|-------|-------|------|------------|------|----------|------|-----------|

| IC QTY         | IC    | Qtv    | 4.00      | 8.00   | 24.00  | 1.00       | 1.00     | 8.00    | 6.00  | 3.00  | 1.00 | 10.00      | 1.00 | 1.00     | 1.00 |           |

| PVCCIN CPUn    | SVID  | 1.80   | 228.00    |        |        |            |          |         |       |       |      |            |      |          |      | 912.00    |

| PVCCSA CPUn    | SVID  | 0.85   | 16.00     |        |        |            |          |         |       |       |      |            |      |          |      | 64.00     |

| PVCCIO CPUn    | SVID  | 1.00   | 21.00     |        |        |            |          |         |       |       |      |            |      |          |      | 84.00     |

| PVDDQ XXX      | SVID  | 1.20   | 17.50     | 71.60  | 2.68   |            |          |         |       |       |      |            |      |          |      | 712.80    |

| PVTT XXX       | 0.60  | 0.60   |           | 1.71   | 0.01   |            |          |         |       |       |      |            |      |          |      | 13.65     |

| PVPP XXX       | 2.50  | 2.50   | 1.20      | 8.90   | 0.20   |            |          |         |       |       |      |            |      |          |      | 76.00     |

| P3V3 STBY      | 3.30  | 3.30   | 0.08      |        |        | 1.30       |          |         |       |       | 0.40 | 0.38       |      | 0.50     | 1.00 | 7.36      |

| P2V5 STBY      | 2.50  | 2.50   |           |        |        |            |          |         |       |       | 0.10 |            |      |          |      | 0.10      |

| P1V8 STBY      | 1.80  | 1.80   |           |        |        | 1.00       |          |         |       |       | 0.10 |            |      |          |      | 1.10      |

| P1V2 STBY      | 1.20  | 1.20   |           |        |        |            |          |         |       |       | 0.60 |            |      |          |      | 0.60      |

| P1V15 STBY     | 1.15  | 1.15   |           |        |        |            |          |         |       |       | 0.80 |            |      |          |      | 0.80      |

| PVNN STBY PCH  | SVID  | 1.00   |           |        |        | 23.00      |          |         |       |       |      |            |      |          |      | 23.00     |

| P1V05 STBY PCH | 1.05  | 1.05   |           |        |        | 15.00      |          |         |       |       |      |            |      |          |      | 15.00     |

| P12V           | 12.00 | 12.00  |           |        | 1.60   |            | 2.00     | 10.00   |       |       |      | 5.50       |      |          |      | 175.40    |

| P12V STBY      | 12.00 | 12.00  |           |        |        |            |          |         |       |       |      |            |      |          |      | _         |

| P5V            | 5.00  | 5.00   |           |        |        |            | 1.50     |         |       | 0.90  |      |            | 0.50 |          |      | 4.70      |

| P3V3 A         | 3.30  | 3.30   |           |        |        |            |          |         | 5.00  |       |      | 3.00       |      |          |      | 16.00     |

| P3V3 B         | 3.30  | 3.30   |           |        |        |            |          |         | 5.00  |       |      | 3.00       |      | 0.00     |      | 44.00     |

| Power (max)    |       |        | 205.00    | 13.40  | 18.00  | 29.00      | 17.00    | 69.00   | 14.00 | 4.50  | 2.00 | 75.00      | 2.50 | 1.65     | 2.00 |           |

|                |       |        | 820.00    | 643.20 | 432.00 | 29.00      | 17.00    | 552,00  | 84.00 | 13,50 | 2.00 | 750.00     | 2.50 | 1.65     | 2.00 | 2922.44   |

Table 7-1 System Power Budget

## 7.2 Power Simple Topology

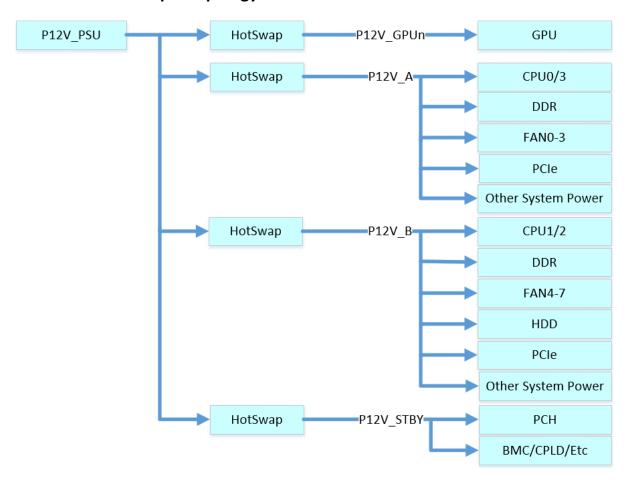

Figure 7-1 power topology

## 7.3 Input voltage Level

The nominal input voltage delivered by the power supply is 12.2V DC nominal at light loading with a range of 11.8V to 12.6V.

|             | Typical | Min   | Max   |

|-------------|---------|-------|-------|

| AC Input    | 230V    | 180V  | 264V  |

| DC Input    | 270V    | 164V  | 300V  |

| Output Main | 12.2V   | 11.8V | 12.6V |

| Output STBY | 12.0V   | 11.4V | 12.6V |

Table 7-2 PSU Output Characteristics

## 7.4 DC-DC Power Design

### 7.4.1 CPU VR

CPU VR follow latest VR13 SPEC. Using the minimum number of total phases to support the maximum CPU power. CPU VR have auto phase dropping feature, and run at optimized phase count among 1, 2, 3,..., and maximum phase count. CPU VR support all Power States to allow the VRM to operate at its peak efficiency at light loading.

### 7.4.2 DIMM VR

DIMM VR support auto phase dropping for high efficiency across loading. DIMM VR compliant to latest VR13 specification.

### 7.4.3 Detail design

| Power Rail                 | VOUT | VIN    | VR Type  | VR<br>QTY<br>/BRD | VR Controller IC<br>and FET             | SMBus Address                         |

|----------------------------|------|--------|----------|-------------------|-----------------------------------------|---------------------------------------|

| PVCCIN_CPU0<br>PVCCIN_CPU3 | SVID | P12V_A | Switcher | 2                 | MPS                                     | CPU0:0X40<br>CPU1:0X40<br>CPU2:0X40   |

| PVCCIN_CPU1 PVCCIN_CPU2    | SVID | P12V_B | Switcher | 2                 | MP2965+7Phase<br>MP86956;               | CPU3:0X40<br>CPU3:0X40<br>With I2C SW |

| PVCCSA_CPU0<br>PVCCSA_CPU3 | SVID | P12V_A | Switcher | 2                 | Infineon PXE1110C+1Phase TDA21470       | CPU0:0XC8 CPU1:0XC8                   |

| PVCCSA_CPU1<br>PVCCSA_CPU2 | SVID | P12V_B | Switcher | 2                 | Infineon<br>PXE1110C+1Phase<br>TDA21470 | CPU2:0XC8<br>CPU3:0XC8<br>With I2C SW |

| PVCCIO_CPU0<br>PVCCIO_CPU3 | SVID | P12V_A | Switcher | 2                 | Infineon<br>IR38163                     | CPU1:0X80<br>CPU2:0X80<br>CPU3:0X80   |

| PVCCIO_CPU1<br>PVCCIO_CPU2                       | SVID                           | P12V_B    | Switcher | 2 | Infineon<br>IR38163                      | CPU4:0X80<br>With I2C SW                                             |

|--------------------------------------------------|--------------------------------|-----------|----------|---|------------------------------------------|----------------------------------------------------------------------|

| PVDDQ_ABC PVDDQ_DEF PVDDQ_UVW PVDDQ_XYZ          | 1.2V                           | P12V_A    | Switcher | 4 | Infineon PXM1310C+3Phas e TDA21470       | PVDDQ_ABC:0XC0<br>PVDDQ_DEF:0XE4<br>PVDDQ_GHJ:0XC0<br>PVDDQ_KLM:0XE4 |

| PVDDQ_GHJ<br>PVDDQ_KLM<br>PVDDQ_NPQ<br>PVDDQ_RST | 1.2V                           | P12V_B    | Switcher | 4 | Infineon<br>PXM1310C+3Phas<br>e TDA21470 | PVDDQ_NPQ:0XC0 PVDDQ_RST:0XE4 PVDDQ_UVW:0XC0 PVDDQ_XYZ:0XE4          |

| PVTT_ABC PVTT_DEF PVTT_UVW PVTT_XYZ              | 0.6V                           | P12V_A    | Switcher | 4 | IR3897MTRPBF                             |                                                                      |

| PVTT_GHJ PVTT_KLM PVTT_NPQ PVTT_RST              | 0.6V                           | P12V_B    | Switcher | 4 | IR3897MTRPBF                             |                                                                      |

| PVPP_ABC<br>PVPP_DEF<br>PVPP_UVW<br>PVPP_XYZ     | 2.5V                           | P12V_A    | Switcher | 4 | TPS53515RVER                             |                                                                      |

| PVPP_GHJ<br>PVPP_KLM<br>PVPP_NPQ<br>PVPP_RST     | 2.5V                           | P12V_B    | Switcher | 4 | TPS53515RVER                             |                                                                      |

| PVNN_STBY_PC<br>H                                | 0.85V<br>0.9V<br>0.95V<br>1.0V | P12V_STBY | Switcher | 1 | IR38263MTRPBF                            | PVNN:0X86                                                            |

| P1V05_STBY_P<br>CH                               | 1.05V                          | P12V_STBY | Switcher | 1 | TPS53353DQPR                             |                                                                      |

| P1V8_STBY                                        | 1.8V                           | P12V_STBY | Switcher | 1 | MPQ8632GLE-6-Z                           |                                                                      |

| P3V3_STBY                                        | 3.3V                           | P12V_STBY | Switcher | 1 | TPS53515RVER                             |                                                                      |

| P2V5_STBY                                        | 2.5V                           | P3V3_STBY | LDO      | 1 | TPS7A7200RGTT                            |                                                                      |

| P1V2_STBY                                        | 1.2V                           | P2V5_STBY | LDO      | 1 | TPS7A7200RGTT                            |                                                                      |

| P1V15_STBY                                       | 1.15V                          | P12V_STBY | Switcher | 1 | MPQ8636GLE-4-Z                           |                                                                      |

| P5V                                              | 5.0V                           | P12V_B    | Switcher | 1 | TPS53515RVER                             |                                                                      |

| P3V3                                             | 3.3V                           | P12V_A    | Switcher | 1 | MP2951+2Phase<br>MP86945                 |                                                                      |

| P3V3_B    | 3.3V | P12V_B   | Switcher | 1 | TPS53355DQPR   |                |

|-----------|------|----------|----------|---|----------------|----------------|

| P12V_STBY | 12V  | P12V_PSU | Hot Swap | 1 | MP5023GV-000-Z | P12V_STBY:0X82 |

| P12V_A    | 12V  | P12V_PSU | Hot Swap | 1 | ADM1278        | P12V_A:0X8C    |

| P12V_B    | 12V  | P12V_PSU | Hot Swap | 1 | ADM1278        | P12V_B:0X8A    |

### 8. BIOS

## 8.1 BIOS Description

### 8.1.1 BIOS Chip

The BIOS chip uses PCH's SPI interface through BMC controlled MUX.

| Item             | Description |

|------------------|-------------|

| Code Base Vendor | AMI AptioV  |

| BIOS Image Size  | 16MB        |

| ROM Image Size   | 32MB        |

#### 8.1.2 BIOS Source Code

BIOS Code based on AMI Purley LightningRidge CRB code, using Intel EDKII software architecture.

### 8.2 BIOS Features

### 8.2.1 BIOS Supported Specifications

- Multiprocessor Specification, Version 1.4.

- PCI BIOS Specification, Version 2.1.

- PCI-to-PCI Bridge Architecture Specification, Version 1.2.

- PCI Express Base Specification Version 4.0

- PCI Local Bus Specification Version 3.0

- PCI Firmware Specification Version 3.2

- Advanced Configuration and Power Interface Specification 5.0 or later

- System Management BIOS (SMBIOS) Specification 3.2.0 or later

- Plug and Play BIOS Specification, Revision 1.0A

- PC System Design Guide 2001 Any conflict occurs between Windows Logo

Program System and Device Requirements and, follows Windows Logo Program

System and Device Requirements.

- Serial ATA Specification 3.0 or later

- AHCI Specification 1.3

- EDD (BIOS Enhanced Disk Drive) Specification V3.0 Revision 0.8

- Bootable CD-ROM Format Specification, Version 1.0

- TCG EFI Platform Specification

- Functionality and Interface Specification of Cryptographic Support Platform for Trusted Computing (Chinese TCM)

- UEFI Specification 2.3.1 or later

- UEFI PI Specification 1.7 or later

- UEFI SCT 2.3

- NIST 800-147 BIOS Protection Guidelines

- NIST 800-147B BIOS Protection Guidelines for Server

- Intelligent Platform Management Interface Specification V2.0

#### 8.2.2 BIOS Error Handle

The BIOS should support reporting the following POST or error SEL log to BMC and standard RAS feature. From the SEL log, the user may know the specific location of device that the error happens with. And the system could be more reliable with the RAS feature.

- BIOS support IPMI SEL Log

- BIOS support machine check error

- BIOS support DDR4 command/Address parity check

- BIOS support memory mirroring

- BIOS support memory demand/patrol scrubbing

- BIOS support memory rank/multi rank sparing

- BIOS support Intel QPI Clock Fail over

- BIOS support PCI Express Advanced Error Reporting

- BIOS support PCI Express Enhanced Root Port Error Reporting

- BIOS support EMCA gen 2

### 8.2.3 BIOS Setup Screen

BIOS setup options are included but not limited to the following options:

- BIOS setup support modifying active core numbers

The BIOS setup shall display the total core numbers and the active core numbers

of every CPU. And the user shall be allowed to disable any number of cores

supported.

- BIOS setup support enable/disable HT

Hyper Thread option shall be enabled by default. Only one thread is active if HT is disabled.

- BIOS setup support enable/disable VT-X/VT-D/SR-IOV

These items shall be enabled if virtualization function is need and could be disabled if not.

- BIOS setup support displaying the L1/L2/L3 cache of CPU

The L1/L2/L3 cache size of CPU should be displayed on the main page of BIOS Setup.

- BIOS setup support enable/disable Turbo Boost

Turbo Mode opportunistically, and automatically, allows processor cores to run faster than the marked frequency if the physical processor is operating below power, temperature and current specification limits. Turbo Mode can be enabled or disabled by the BIOS and it will increase the performance of workloads.

- BIOS setup support enable/disable P-state (EIST)

Enhanced Intel Speed Step Technology support shall be controlled by the BIOS.

EIST, which offers the capability to support a multitude of processor performance states, allows the processor to dynamically adjust frequency and voltage based on power versus performance needs. EIST should be enabled by default.

- BIOS setup support enable/disable C-state

Multiple low power idle states (CO/C1/C1E/C6) should be typically

implemented by the BIOS. Enable C state could minimize the idle power

consumption of the processor. C state may be set disabled by default for the

system performance.

- BIOS setup support enable/disable PCIE ASPM

ASPM operation may be controlled by the BIOS. Optimal power consumption could be obtained if ASPM is enabled, however, some instances of performance impact can be observed.

- BIOS setup support enable/disable PXE boot

The BIOS should support UEFI and Legacy PXE boot by default and they may be disabled under BIOS setup. PXE will be booted directly if F12 is pressed during the POST process.

- BIOS setup support performance/efficient/custom

The BIOS is set to performance mode by default. The user may change to efficient mode for power saving or to custom mode under BIOS setup if they want.

### 8.2.4 SMBIOS

The BIOS shall provide support for the System Management BIOS (SMBIOS) Reference Specification, Version 3.2.0 or later. The BIOS shall implement the following SMBIOS tables:

| Type | Structure                            |

|------|--------------------------------------|

| 0    | BIOS Information                     |

| 1    | System Information                   |

| 2    | Base Board Information               |

| 3    | System Enclosure or Chassis          |

| 4    | Processor Information                |

| 7    | Cache Information                    |

| 8    | Port Connector Information           |

| 9    | System Slots                         |

| 11   | OEM Strings                          |

| 13   | BIOS Language Information            |

| 16   | Physical Memory Array                |

| 17   | Memory Device                        |

| 19   | Memory Array Mapped Address          |

| 38   | IPMI Device Information              |

| 39   | System Power Supply                  |

| 41   | Onboard Devices Extended Information |

| 127  | End-of-Table                         |

|      |                                      |

### 8.2.5 Boot

BIOS Support SAS, SATA and PXE boot.

The BIOS shall support booting to SAS device, SATA disk or PXE boot option.

BIOS Support Changing boot priority

Boot priority shall be changed under BIOS setup and boot option shall be allowed to be disabled or enabled.

BIOS support modifying BOOT sequence via IPMI commands:

The sequence of boot option shall be adjusted with IPMI raw or chassis command. This change should be one-time or persistent.

BIOS support Boot Retry :

Enable: If there is no bootable device found, BIOS should keep loop searching for bootable device.

Disable: If there is no bootable device found, BIOS will stop boot and show"

Reboot and Select proper Boot device or Insert Boot Media in selected Boot device and press a key".

BIOS shall support UEFI and legacy boot mode options, and UEFI and legacy boot mode shall have independent boot loop.

### 8.2.6 BIOS Update

BIOS support USB Storage Device Recovery

The BIOS may supporting recovery via a USB storage with a BIOS image in it when the BIOS of the system is corrupted with incomplete functionality.

BIOS support Update BIOS Image through BMC

The BIOS shall support being flashed via BMC Web GUI. There may be two upgrade modes, "BIOS+ME" and "BIOS only". And there should be a checkbox of "Keep BIOS Setup Option" for users, so they can choose whether the NVRAM should be cleared.

BIOS support Update BIOS in UEFI Shell, Windows OS & Linux OS

The BIOS shall support for flashing BIOS under UEFI Shell, Windows and Linux with AMI AFU tools. And with different parameters, BIOS region, ME region or other region could be flashed separately.

#### **9. BMC**

BMC is an independent system of host server system. This independent system has its own

processor and memory; The host system can be managed by BMC system even if host hardware or OS hang or went down.

### 9.1 Main Feature

- Support IPMI 2.0, IPMI Interface include KCS, LAN, IPMB

- Management Protocol, IPMI2.0, HTTPS, SNMP, Smash CLI

- Web GUI

- Redfish

- Management Network Interface, Dedicated/NCSI

- Console Redirection(KVM) and Virtual Media

- Serial Over Lan(SOL)

- Diagnostic Logs, System Event Log (SEL), Blackbox Log, Audit Log

- Hardware watchdog timer, Fans will full speed when BMC no response in 4 mins

- Intel® Intelligent Power Node Manager 4.0 support

- Event Alert, SNMP Trap(v1/v2c/v3), Email Alert and Syslog

- Dual BMC firmware image support

- Storage, Monitor RAID Controller/HDD/Virtual HDD

- Firmware update, BMC/BIOS/CPLD

- Device State Monitor and Diagnostic

### 9.2 Integrated BMC Hardware

ASPEED AST2500 Baseboard Management Controller, at the center of the server management subsystem is the ASPEED AST2500 integrated Baseboard Management Controller. This device provides support for many platform functions including system video capabilities, legacy Super I/O functions, hardware monitoring functions, and incorporates an ARM1176JZF-S 32-bit RISC CPU microcontroller to host an IPMI 2.0 compliant server management firmware stack.

The following functionality is integrated into the component:

- Baseboard Management Controller (BMC) with peripherals

- Server class Super I/O (SIO)

- Graphics controller

- Remote KVM redirection, USB media redirection, and HW Encryption

The eSPI/LPC interface to the host is used for SIO and BMC communication. The eSPI/LPC Bus interface provides IPMI Compliant KCS and BT interfaces.

The PCI Express interface is mainly used for the graphics controller interface to communicate with the host. The graphics controller is a VGA-compliant controller with 2D hardware acceleration and full bus master support. The graphics controller can support up to 1920x1200

resolution at high refresh rates. The PCI Express interface is also used for BMC messaging to other system devices using MCTP protocol.

The USB 2.0 Hub interface is used for remote keyboard and mouse, and remote storage support. BMC supports various storage devices such as CDROM, DVDROM, CDROM (ISO image), floppy and USB flash disk. Any of the storage devices can be used as a boot device and the host can boot from this remote media via redirection over the USB interface.

For the main capabilities of the BMC AST2500.BMC provide the 10/100/1000M local RJ45 management connector through BCM54612 and enable the communication between BMC and OCP A/PCH with NCSI BUS.

### 10. Thermal Design Requirements

To meet thermal reliability requirement, the thermal and cooling solution should dissipate heat from the components when system operating at its maximum thermal power. The thermal solution should be found by setting a high power target for initial design in order to avoid redesign of cooling solution; however, the final thermal solution of the system should be most optimized and energy efficient under data center environmental conditions with the lowest capital and operating costs. Thermal solution should not allow any overheating issue for any components in system.

The heat dissipation system includes 8pcs 6056Fan & 4 CPU HS, which can support normal operation at 35 C without risk of over-temperature and device frequency reduction. According to the maximum configuration evaluation, the heat dissipation under 205W CPU\*4+3 300W GPU configuration is risk-free. The proportion of heat dissipation power is less than 12% under the normal operation of the system.

#### 10.1 Data Center Environmental Conditions

The thermal design needs to satisfy the data center operational conditions as described below.

#### 10.1.1 Altitude

Data centers could be located up to 1500 meters above sea level.

In the simulation, the influence of altitude factor is considered. The simulation is carried out according to the air density at 1500 meters altitude. The PA test is carried out at high altitude and low pressure, and the test data do not exceed the temperature.

#### 10.1.2 Cold-Aisle temperature

We adopt the most advanced PID control fan method in the industry. The fan speed is positively correlated with the device temperature. Within the maximum heat dissipation capacity of the system, it can ensure that all parts of the system are running in spec, so as to achieve the best point of system power consumption and heat dissipation reliability.

#### 10.1.3 R.H

Most data centers will maintain the relative humidity to be between 20% and 80%. In the thermal design, the environmental condition changes due to the high altitude may not be considered when the thermal design can meet the requirement with maximum relative humidity, 80%.

PA test and heat dissipation test will be carried out in the most stringent test environment, 80% humidity or even higher humidity are tested.

### 10.2 Server operational condition

#### 10.2.1 Inlet Temperature

Inlet sensor has an accuracy of (+1 C). We will test the heat dissipation at the temperature of 20, 25, 30 and 35 to verify our heat dissipation scheme. Heat dissipation test will grab as many temperatures as possible in the system to judge, all temperatures can be passed.

#### 10.2.2 Fan Redundancy

The server fans at N+1 redundancy should be sufficient for cooling server components to temperatures below their maximum spec to prevent server shut down or to prevent either CPU or memory throttling. Fan redundancy function is designed as our heat dissipation index at the beginning of the design.

#### 10.2.3 Thermal Margin

The thermal margin is the difference between the maximum theoretical safe temperature and the actual temperature. The board design operates at an inlet temperature of 35°C (95°F) outside of the system with a minimum 2% thermal margin for every component on the card. Otherwise, the thermal margin for every component in the system is at least 7% for inlet temperature up to 30°C.

According to the test results, the heat dissipation of high-risk heat dissipation components in the system can meet the margin requirement of 2%. The CPU part of the maximum heat dissipation pressure component has a residual of about 5 °C ~35 °C, and the GPU part has a residual of about 4 °C.

### 10.3 Thermal kit requirements

#### 10.3.1 Heat Sink

The heat sink design should choose to be most optimized design with lowest cost. The heat sink design should be reliable and the most energy efficient design that satisfies all the conditions described above.

The system uses 2U standard Purley platform radiator. In order to consider the power consumption and reliability of the system, under the CPU shadow layout, there is a differentiated design part to minimize the temperature difference of the CPU.

#### 10.3.2 System Fan

The system fan must be highly power-efficient with dual bearing. The propagation of vibration cause by fan rotation should be minimized and limited. The frame size of fan is 60x60x56mm and the quantity of fan is 8PCS. The power supply for fan should use 2 pin P12V to avoid current over spec. Under the normal operation condition of the system, the fan efficiency reaches more than 40%. The maximum current of the fan is 5.7A/unit.

#### 10.3.3 Air-Duct

The air duct needs to be part of the motherboard tray cover, and must be most energy efficient design. The air-duct design should be simple and easily serviceable. For

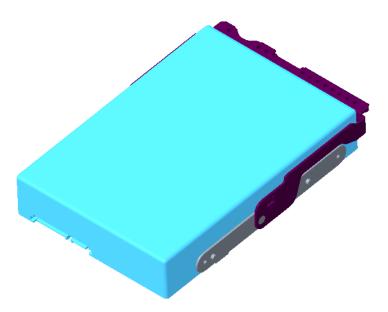

different config, system can change the air-duct to meet. Using highly green material or reusable material for the air duct is preferred.