## EDA for Multi-die System Integration in a Package Exploration → Design → Optimization → Validation → Analysis → Signoff

Rita Horner Sr. Product Marketing Manager, 3DIC Compiler September 2020

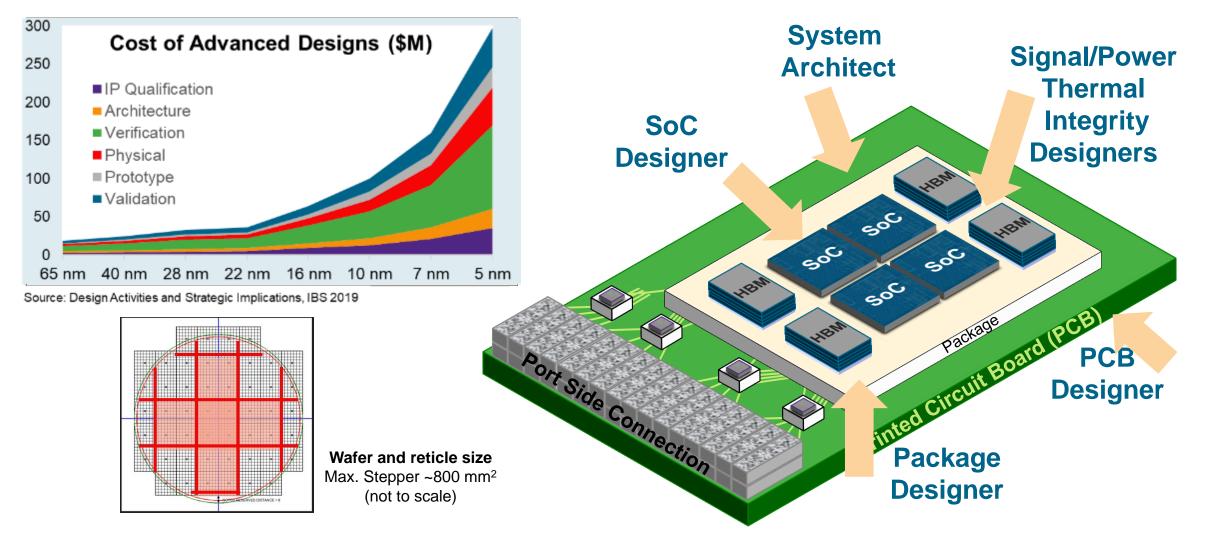

### Multi-Die Advanced Packaging

Bandwidth, Performance, Power, Latency, and Development Cycle

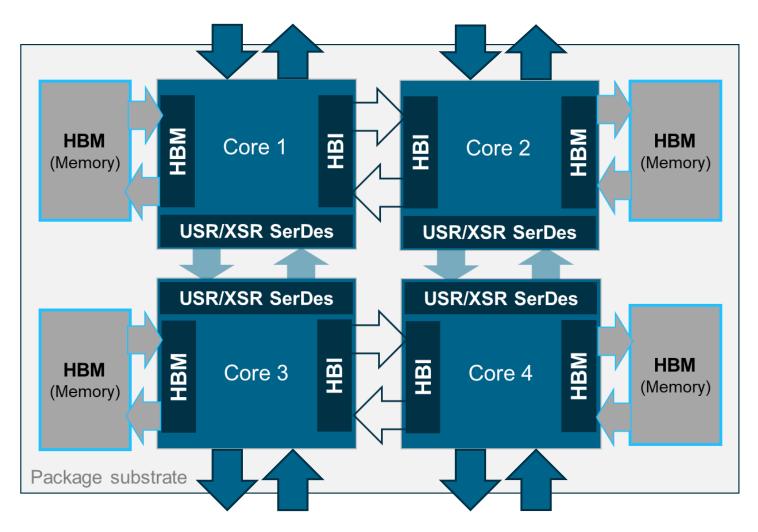

#### Example Die-to-Die Physical Interfaces (PHYs)

High Bandwidth Memory/Interconnect (HBM/HBI), Ultra/Extra Short Reach (USR/XSR)

Die-to-Die Interface

## Die-to-Die PHY Options in Advanced Process Nodes

#### Parallel vs. Serial Interfaces

|                                  | Parallel Interface                               |                                                | Serial Interface                                    |

|----------------------------------|--------------------------------------------------|------------------------------------------------|-----------------------------------------------------|

|                                  | Non-Memory                                       | Memory                                         | (SerDes)                                            |

| Standards &<br>Specifications    | DARPA, OCP-ODSA<br>AIB, HBI, BoW                 | JEDEC<br>HBM2, HBM2E HBM3                      | IEEE 802.3, PCI-SIG, OIF<br>1G - 56G & 112G URS/XSR |

| Data Rate per Lane<br>(Gbps)     | 1 to 2 $\rightarrow$ 2 to 4 $\rightarrow$ 4 to 6 | $2.4 \rightarrow 3.2$ to $3.6 \rightarrow 6.4$ | 1.25 to 112                                         |

| I/O number per link              | 30 to 2000+                                      | 1024                                           | 2 pairs (4) 🗸                                       |

| Latency                          | Low 🗸                                            | Low 🗸                                          | High                                                |

| Interconnect reach               | Short                                            | Short                                          | Long 🗸                                              |

| Interconnect<br>medium type need | High density routing<br>(Silicon Interposer)     |                                                | Low resistance<br>(High Density Fan-Out)            |

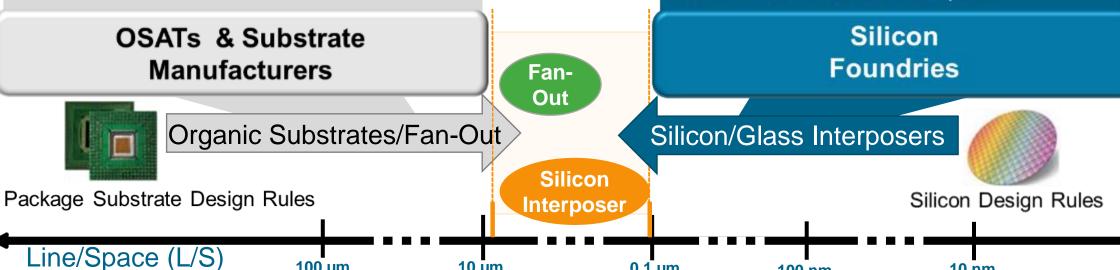

### IC Packaging "Adjacency" Rapidly Morphing into Core EDA

- Low density routing ٠

- Large width & spacing

- Design driven manufacturing

100 µm

Non-Manhattan shapes ٠

- High density routing

- Small width & spacing

- Manufacturing drives design (PDKs) •

- Manhattan based shapes •

100 nm

0.1 µm

10 µm

10 nm

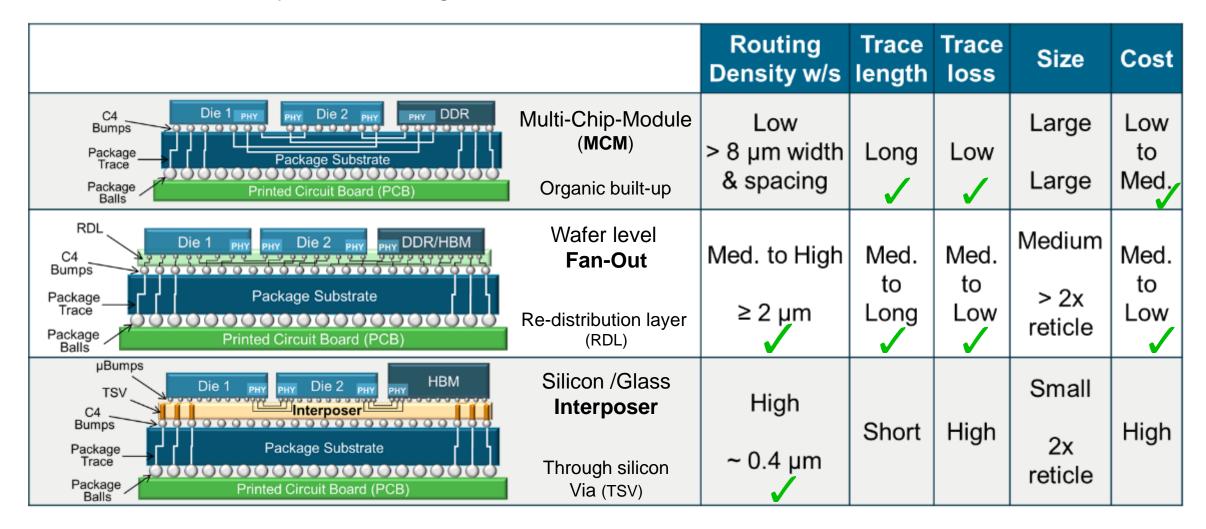

### **Advanced Packaging Technologies**

Interconnect Density, Trace Length, Performance, Size and Cost

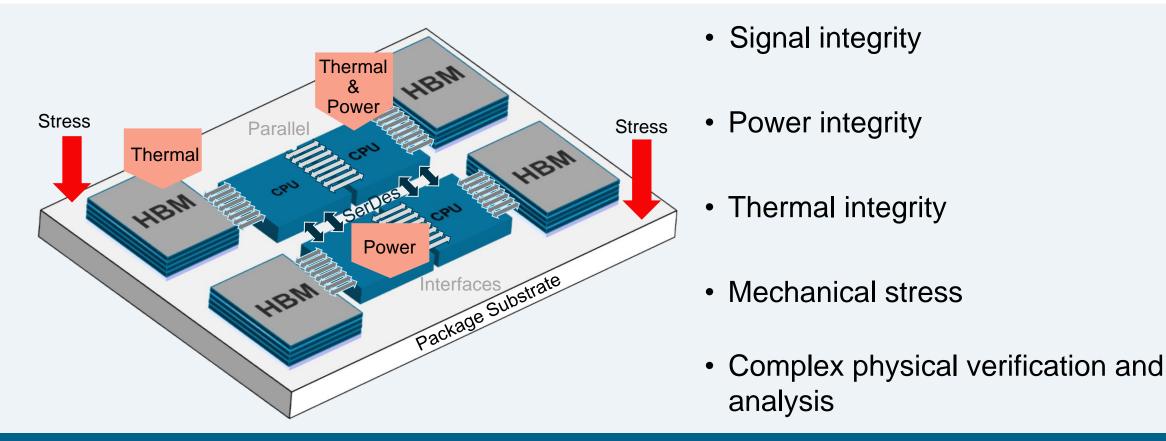

#### 2.5D/3DIC Design Challenges

Signal Quality, Power, Thermal & Mechanical Stress

#### **Chip-Package Co-Design for an Optimal Solution!**

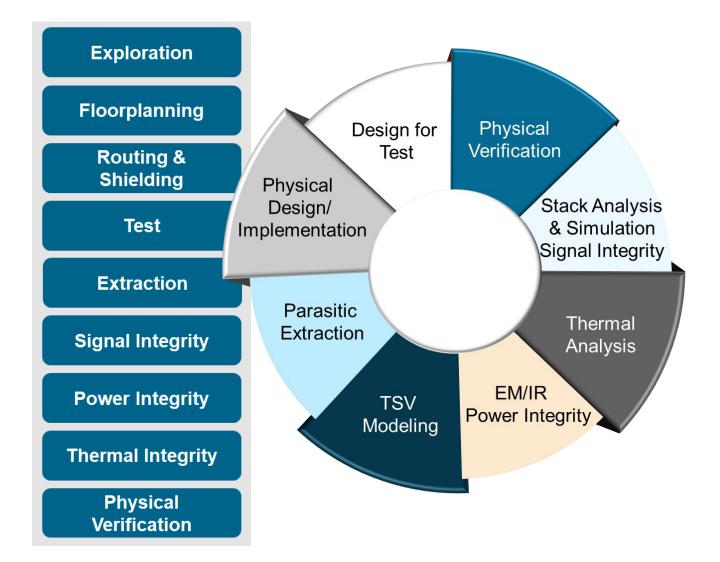

#### Multi-Die Package Design EDA Tools Today

| Existing Limitations and Challenges                                                                                                                                                                                                                                                                                    | Multi-Die Integration Solution                                                                                                                                                                                                                                                                                                     |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <ul> <li>Disjointed solutions with multiple point tools,</li> <li>Limited cross-discipline collaboration support</li> <li>Each with own interfaces and use models</li> <li>Large feedback loops for convergence</li> <li>Lack of automation</li> <li>Separate use models</li> <li>Database size limitations</li> </ul> | <ul> <li>A unified platform that enables cross-discipline<br/>co-design &amp; co-optimization</li> <li>Unified GUI interface, 3D &amp; 2D view</li> <li>DRC-aware environment</li> <li>Automation (routing/shielding, bump placement,)</li> <li>Common data model, enabling scalability in<br/>capacity and performance</li> </ul> |  |

| <ul> <li>Power/signal/thermal noise optimization starts too</li></ul>                                                                                                                                                                                                                                                  | <ul> <li>Power/signal/thermal noise aware design optimization</li></ul>                                                                                                                                                                                                                                                            |  |

| late in the design cycle                                                                                                                                                                                                                                                                                               | from early exploration to design signoff (die to PCB)                                                                                                                                                                                                                                                                              |  |

| <ul> <li>Multiple point tools each w/ separate capability and</li></ul>                                                                                                                                                                                                                                                | <ul> <li>SoC-scale integrated platform from early architectural</li></ul>                                                                                                                                                                                                                                                          |  |

| scripts. Lack support for early exploration and end                                                                                                                                                                                                                                                                    | exploration, to design/implementation, validation, to                                                                                                                                                                                                                                                                              |  |

| to end validation                                                                                                                                                                                                                                                                                                      | signoff                                                                                                                                                                                                                                                                                                                            |  |

#### Ideal Multi-Die Design Platform for a System in a Package

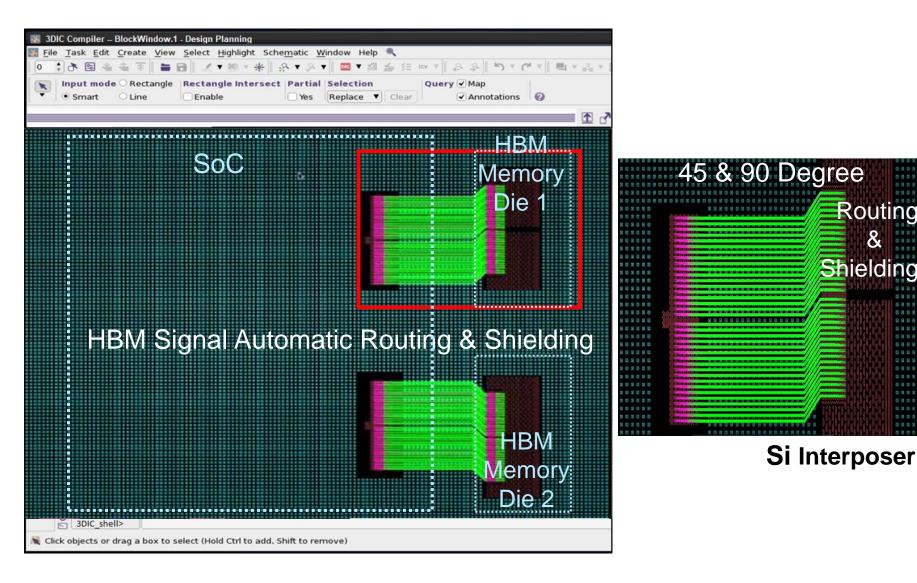

#### Auto-Routing & Auto-Shielding

Fan-Out routing (any-angle, teardrops & oblong shapes, degassing hole)

Routing

Shielding

&

.

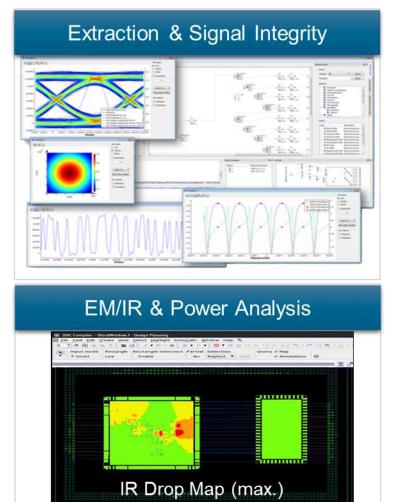

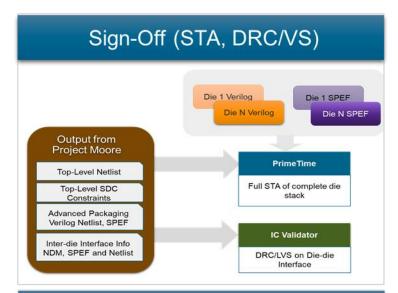

### Multi-Die System Integration – Analysis & Validation

Signal Integrity, Power Integrity, Thermal/Mechanical Integrity, DFT Rule Check -> Signoff

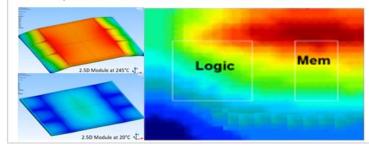

#### Thermal & Mechanical Analysis

Thermal hotspot detection & correction Temperature aware resistance, EM, IR

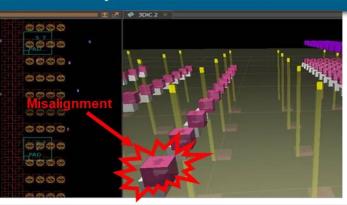

#### Physical Verification

objects or drag a box to select 04old Ctrl to add. Shif

# Thank You

# **Synopsys**<sup>®</sup> Silicon to Software<sup>™</sup>