# Micro-Server Card Hardware vo.5 MB-draco-etamin-o.5

Author: Chris Petersen, Hardware Systems Engineer, Facebook

# 1. Scope

This specification provides a common form factor for emerging micro-server and SOC (System-On-Chip) server designs. For the purposes of this specification, the term "card" is used to describe a PCIe-like card that hosts the SOC, dynamic memory for the SOC, and a storage device.

### 2. Contents

| 1.  | Scope                                     |    |

|-----|-------------------------------------------|----|

| 2.  | Contents                                  | 2  |

| 3.  | Overview                                  | 3  |

|     | 3.1. License                              | 3  |

| 4.  | Mechanical                                | 3  |

|     | 4.1. Card Mechanical Outline              |    |

|     | 4.2. PCIe Edge Connector                  |    |

|     | 4.3. Baseboard Design                     | _  |

| 5.  | Thermal                                   | 5  |

| ٠.  | 5.1. Data Center Environmental Conditions |    |

|     | 5.2. Server Operational Conditions        |    |

|     | 5.3. Heat Sink Requirements               |    |

|     | 5.4. Temperature Sensors                  |    |

| 6.  | Electrical                                | 7  |

| ٥.  | 6.1. Edge Connector                       | -  |

|     | 6.2. Pin Definitions                      |    |

|     | 6.3. Ethernet                             | _  |

|     | 6.4. SATA                                 |    |

|     | 6.5. PCIe                                 |    |

|     | 6.6. I2C                                  |    |

| 7.  | Power                                     | 17 |

|     | 7.1. Input                                | -  |

|     | 7.2. Hot-Plug Support                     | 17 |

|     | 7.3. VR Efficiency                        | 17 |

|     | 7.4. Input Capacitance                    | 17 |

| 8.  | Functional                                | 17 |

|     | 8.1. Memory                               |    |

|     | 8.2. Storage                              | 17 |

|     | 8.3. EEPROM                               | 17 |

|     | 8.4. BIOS                                 | 18 |

|     | 8.5. Management                           | 20 |

|     | 8.6. Battery                              | 21 |

|     | 8.7. LEDs                                 | 21 |

| 9.  | Environmental Requirements                | 21 |

|     | 9.1. Vibration and Shock                  | 21 |

| 10. | Prescribed Materials                      | 22 |

|     | 10.1. Disallowed Components               |    |

|     | 10.2. Capacitors and Inductors            |    |

|     | 10.3. Component De-rating                 |    |

|     | -                                         |    |

### 3. Overview

When data center design and hardware design move in concert, they can improve efficiency and reduce power consumption. To this end, the Open Compute Project is a set of technologies that reduces energy consumption and cost, increases reliability and choice in the marketplace, and simplifies operations and maintenance. One key objective is openness—the project is starting with the opening of the specifications and mechanical designs for the major components of a data center, and the efficiency results achieved at facilities using Open Compute technologies.

One component of this project is a micro-server or SOC (System-On-Chip) server design. The micro-server is a PCIe-like card that hosts the SOC, dynamic memory for the SOC, and a storage device. This micro-server can be installed in slots on a baseboard. The baseboard provides power distribution and control, BMC management capabilities, and network distribution. The baseboard may or may not be plugged into a midplane.

### 3.1. License

As of April 7, 2011, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at

http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0

Facebook, Inc.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at http://opencompute.org/licensing/, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 4. Mechanical

#### 4.1. Card Mechanical Outline

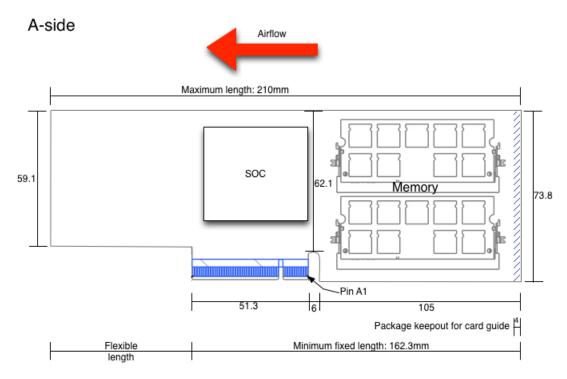

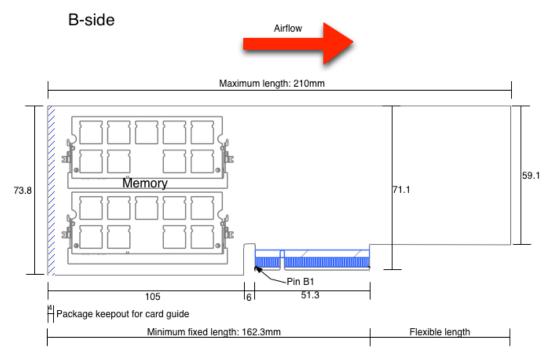

The card adheres to the mechanical dimensions provided in Figures 1 and 2. The dimensions are defined to accommodate multiple card lengths, but only on one end of the card.

Figure 1 Mechanical Outline of the "A" Side of the Card

#### Notes:

- Memory may be placed on A-side, B-side, or both sides, but must be placed ahead of the SOC (towards the cold-aisle).

- Memory may be oriented in any direction. The drawing is for illustration purposes only and is not intended to define specific placement or quantity of memory slots.

- SOC must be placed on A side.

Figure 2 Mechanical Outline of the "B" Side of the Card

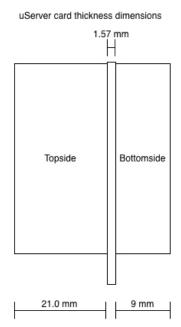

Figure 3 Mechanical Dimensions for Component Heights Including Tolerance

### 4.2. PCIe Edge Connector

The key dimensions, edge chamfer, pad layout, placement, and dimensions of the card edge connector match the PCI Express Card Electromechanical Specification.

# 4.3. Baseboard Design

One possible implementation of the baseboard provides 10x micro-server card slots. The slots are situated as two rows of 5x slots. The slots in each row are spaced at a pitch of 33mm (center to center).

Future designs may accommodate thicker card designs to support higher-power versions.

## 5. Thermal

### 5.1. Data Center Environmental Conditions

#### 5.1.1. Location of Data Center/Altitude

The data center may be located at a maximum of 1000m above sea level. Any variation of air properties or environmental differences due to the high altitude needs to be included in the thermal design.

#### 5.1.2. Cold-Aisle Temperature

The data center will maintain the cold aisle temperature between 18°C and 30°C (65°F to 85°F). The mean temperature in the cold aisle is 24°C with 3°C standard deviation. The cold aisle temperature in the data center may fluctuate depending on the outside air temperature. Every component on the card must be cooled and maintained below its maximum spec temperature across the full cold aisle temperature range.

### 5.1.3. Cold-Aisle Pressurization

The data center will maintain the cold aisle pressure between 0 "H2O and 0.05 "H2O. The thermal solution of the system accommodates the worst-case operational pressurization in the data centers which is 0 "H2O with no fan failures and 0.01 "H2O with a single fan (or rotor) failure.

#### 5.1.4. Relative Humidity

The data center will maintain the relative humidity between 20% and 85%. In the thermal design, the environmental condition changes due to the high altitude may not be considered when the thermal design can meet the requirement with maximum relative humidity (85%).

### 5.2. Server Operational Conditions

#### 5.2.1. System Airflow or Volumetric Flow

The unit of airflow (or volumetric flow) used for this spec is CFM (cubic feet per minute). The maximum allowable airflow per watt in the system is 0.16. Except for the condition when the inlet temperature is higher than 30°C, the maximum allowable airflow per watt is 0.13. The airflow per watt must be 0.1 or lower in the system at the mean temperature (plus or minus standard deviation). See section 5.1.2 for the temperature definitions.

#### 5.2.2. Delta T

The delta T is the air temperature difference across the system or the temperature difference between outlet air temperature of system and inlet air temperature of system. The delta T is greater than 11.7°C (21°F). The delta T must be 20°C (36°F) when the inlet air temperature to the system is lower than 30°C.

#### 5.2.3. Thermal Margin

The thermal margin is the difference between the maximum theoretical safe temperature and the actual temperature. The board design operates at an inlet temperature of 35°C (95°F) outside of the system with a minimum 2% thermal margin for every component on the card. Otherwise, the thermal margin for every component in the system is at least 7% for temperatures up to 30°C.

### 5.3. Heat Sink Requirements

The heat sink must be a thermally optimized design at the lowest cost. There must be no more than three heat pipes in the heat sink. Heat sink installation is simple and uncomplicated. Heat sinks must not block debug headers or connectors.

### 5.4. Temperature Sensors

Each card must provide temperature sensors for the SOC, the SO-DIMM(s) (if they are used), and one ambient temperature sensor. All temperature readings for each sensor must be readable via the management sideband interface to the baseboard. Additionally, over-temperature thresholds are configurable and an alert mechanism is provided to enable thermal shutdown and/or an increase in airflow. The sensors are accurate to +/-3C.

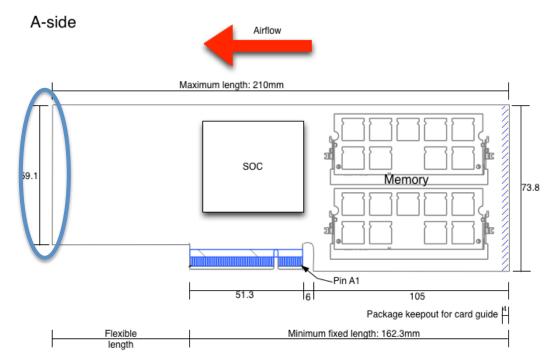

The ambient temperatures sensor is placed along the rear edge of the card on the A-side. Please see the blue, circled area in Figure 4 for more information.

Figure 4 Ambient Temperature Sensor Location (Circled Area in Blue)

### 6. Electrical

# 6.1. Edge Connector

The card must plug into an x8 PCIe edge connector. Specifically, the baseboard will use the following FCI SMT connector: 10061913-112TLF. Figure 5 shows the default pin-out,. Other variations are possible (see below for more details).

| Default Pin-out |                        |    |             |  |  |

|-----------------|------------------------|----|-------------|--|--|

| Pin Name        | Pin Name Side B Side A |    |             |  |  |

| P12V            | 1                      | 1  | PRSNT#      |  |  |

| P12V            | 2                      | 2  | P12V        |  |  |

| P12V            | 3                      | 3  | P12V        |  |  |

| GND             | 4                      | 4  | GND         |  |  |

| I2C_SCL         | 5                      | 5  | SVR_IDo     |  |  |

| I2C_SDA         | 6                      | 6  | SVR_ID1     |  |  |

| GND             | 7                      | 7  | COM_TX      |  |  |

| PWR_ON#         | 8                      | 8  | COM_RX      |  |  |

| USB_P           | 9                      | 9  | SVR_ID2     |  |  |

| USB_N           | 10                     | 10 | SVR_ID3     |  |  |

| SYS_RESET#      | 11                     | 11 | PCIE_RESET# |  |  |

| I2C_ALERT# | 12 | 12 | GND           |

|------------|----|----|---------------|

| GND        | 13 | 13 | PCIE_REFCLK_P |

| GND        | 14 | 14 | PCIE_REFCLK_N |

| PCIE_TX0_P | 15 | 15 | GND           |

| PCIE_TXo_N | 16 | 16 | GND           |

| GND        | 17 | 17 | PCIE_RXo_P    |

| GND        | 18 | 18 | PCIE_RXo_N    |

| PCIE_TX1_P | 19 | 19 | GND           |

| PCIE_TX1_N | 20 | 20 | GND           |

| GND        | 21 | 21 | PCIE_RX1_P    |

| GND        | 22 | 22 | PCIE_RX1_N    |

| PCIE_TX2_P | 23 | 23 | GND           |

| PCIE_TX2_N | 24 | 24 | GND           |

| GND        | 25 | 25 | PCIE_RX2_P    |

| GND        | 26 | 26 | PCIE_RX2_N    |

| PCIE_TX3_P | 27 | 27 | GND           |

| PCIE_TX3_N | 28 | 28 | GND           |

| GND        | 29 | 29 | PCIE_RX3_P    |

| GND        | 30 | 30 | PCIE_RX3_N    |

| SATAo_TX_P | 31 | 31 | GND           |

| SATAo_TX_N | 32 | 32 | GND           |

| GND        | 33 | 33 | SATAo_RX_P    |

| GND        | 34 | 34 | SATAo_RX_N    |

| SATA1_TX_P | 35 | 35 | GND           |

| SATA1_TX_N | 36 | 36 | GND           |

| GND        | 37 | 37 | SATA1_RX_P    |

| GND        | 38 | 38 | SATA1_RX_N    |

| RFU        | 39 | 39 | GND           |

| RFU        | 40 | 40 | GND           |

| GND        | 41 | 41 | RSVD          |

| GND        | 42 | 42 | RSVD          |

| GEo_RX_P   | 43 | 43 | GND           |

| GEo_RX_N   | 44 | 44 | GND           |

| GND        | 45 | 45 | RSVD          |

| GND        | 46 | 46 | RSVD          |

| GEo_TX_P   | 47 | 47 | GND           |

| GEo_TX_N   | 48 | 48 | GND           |

| GND        | 49 | 49 | RFU           |

Figure 5 Edge Connector Pin Assignments

Required connection

Configurable connection

Reserved for future use

Figure 6 Pin Assignment Color-Coding Definitions

### 6.2. Pin Definitions

Figure 7 provides a detailed explanation of the pins. The direction of the signals is always defined from the perspective of the micro-server module.

| Pin           | Direction    | Required/<br>Configurable | Pin Definition                                                                                                                                               |

|---------------|--------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P12V          | Input        | Required                  | 12VAUX power                                                                                                                                                 |

| I2C_SCL       | Input/Output | Required                  | I2C clock signal. I2C is the primary sideband interface for server management functionality. 3.3VAUX signal. Pull-up is provided on the baseboard.           |

| I2C_SDA       | Input/Output | Required                  | I2C data signal. I2C is the primary sideband interface for server management functionality. 3.3VAUX signal. Pull-up is provided on the baseboard.            |

| 12C_ALERT#    | Output       | Required                  | I2C alert signal. Alerts the BMC that event has occurred that needs to be processed. 3.3VAUX signal. Pull-up is provided on the baseboard.                   |

| PWR_ON#       | Input        | Required                  | Power on signal. When driven low, it indicates that the server will begin its power-on sequence. 3.3VAUX signal. Pull-up is provided on the baseboard.       |

| SYS_RESET#    | Input        | Required                  | System reset signal. When driven low, it indicates that the server will begin its warm reboot process. 3.3VAUX signal. Pull-up is provided on the baseboard. |

| PRSNT#        | Output       | Required                  | Present signal. This is pulled low on<br>the card to indicate that a card is<br>installed. 3.3VAUX signal. Pull-up is<br>provided on the baseboard.          |

| COM_TX        | Output       | Required                  | Serial transmit signal. Data is sent from the micro-server module to the BMC. 3.3VAUX signal.                                                                |

| COM_RX        | Input        | Required                  | Serial receive signal. Data is sent from the BMC to the micro-server module. 3.3VAUX signal.                                                                 |

| SVR_ID0/1/2/3 | Input        | Required                  | Slot ID bits. Each slot will be assigned a unique ID using pulldown resistors for 0 and open for a 1. Pull-ups should be provided on                         |

|                    |              |               | the card. The server can use this slot ID to identify its location in the system. 3.3VAUX signal.                                                                    |

|--------------------|--------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GEo_TX_P/N         | Output       | Required      | Primary Ethernet transmit signal. Data is sent from the micro-server module to the baseboard.                                                                        |

| GEo_RX_P/N         | Input        | Required      | Primary Ethernet receive signal. Data is sent from the baseboard to the micro-server module.                                                                         |

| PCI_RESET#         | Output       | Required      | PCIe reset signal. If a PCIe bus is connected, this signal provides the reset signal indicating the card VRs are stable.                                             |

| PCIE_TX0/1/2/3_P/N | Output       | Configurable  | PCIe x4 bus transmit signals. Data is sent from the micro-server module to the baseboard. These signals may or may not be connected on the baseboard.                |

| PCIE_RXO/1/2/3_P/N | Input        | Configurable  | PCIe x4 bus receive signals. Data is sent from the baseboard to the micro-server module. These signals may or may not be connected on the baseboard.                 |

| PCIE_REFCLK_P/_N   | Output       | Configurable  | PCIe reference clock. This signal may or may not be connected on the baseboard.                                                                                      |

| SATAO/1_TX_P/N     | Output       | Configurable  | SATA 2.0 or 3.0 transmit signals (two ports). Data is sent from the microserver module to the baseboard. These signals may or may not be connected on the baseboard. |

| SATAO/1_RX_P/N     | Input        | Configurable  | SATA 2.0 or 3.0 receive signals (two ports). Data is sent from the baseboard to the micro-server module. These signals may or may not be connected on the baseboard. |

| USB_P/N            | Input/Output | Configurable  | USB 2.0 differential pair.                                                                                                                                           |

| RSVD               | Input/Output | Configurable  | Available differential pairs that could be configured as PCIe, SATA, SAS, Ethernet, or other high-speed interfaces.                                                  |

| RFU                | Input/Output | Not connected | These pins are reserved for future use and are not used.                                                                                                             |

Figure 7 Detailed Pin Definitions

### 6.2.1. Required vs. Configurable Connections

The card pin-out is defined to provide basic functionality, but maintain flexibility for compatible alternate/future designs. All signals marked as "Required" must be connected on the card and will be connected on the baseboard. All signals marked "Configurable" may be used in some applications, but not in others. They may or may not

be connected on the baseboard or the card. It is possible to create multiple card designs that support alternate pin assignments for the reserved signals.

### 6.2.2. Configurable Pin Assignment Algorithm

The baseboard will provide a table that defines the usage of each pair of reserved pins. This table will be accessible over I2C. During the power-on sequence, the SOC will query the baseboard and retrieve the contents of the table. If the connection type of a pair of reserved pins on the card matches to the connection type of the reserved pins on the baseboard, those signals are enabled and the initialization sequence can begin. If a match is not found, the table cannot be retrieved, or the connections are mismatched, the SOC signals are disabled and/or powered-off. The tables below provide the reserved pin mapping and encoding values for different functions.

| Byte # | Field Definition                         |

|--------|------------------------------------------|

| 0      | 8 bit encoded value for pins A13 and A14 |

| 1      | 8 bit encoded value for pins A17 and A18 |

| 2      | 8 bit encoded value for pins A21 and A22 |

| 3      | 8 bit encoded value for pins A25 and A26 |

| 4      | 8 bit encoded value for pins A29 and A30 |

| 5      | 8 bit encoded value for pins A33 and A34 |

| 6      | 8 bit encoded value for pins A37 and A38 |

| 7      | 8 bit encoded value for pins A41 and A42 |

| 8      | 8 bit encoded value for pins A45 and A46 |

| 9      | 8 bit encoded value for pins B15 and B16 |

| 10     | 8 bit encoded value for pins B19 and B20 |

| 11     | 8 bit encoded value for pins B23 and B24 |

| 12     | 8 bit encoded value for pins B27 and B28 |

| 13     | 8 bit encoded value for pins B31 and B32 |

| 14     | 8 bit encoded value for pins B35 and B36 |

| 15     | 8 bit encoded value for pins B39 and B40 |

Figure 8 Byte to Configurable Pin Pair Mapping

| Encoding  | Signal Type |

|-----------|-------------|

| 0X00      | Off         |

| 0X01      | PCIe gen 2  |

| 0X02      | PCIe gen 3  |

| 0x03      | PCIe clock  |

| 0X04      | SATA 2.0    |

| 0x05      | SATA 3.0    |

| 0x06      | 1000BASE-KX |

| 0X07      | 10GBASE-KR  |

| 0x08      | SGMII       |

| 0x09-0xff | RFU         |

Figure 9 Table 1: Hex Value Encoding for Different Signal Types

### 6.2.3. Example Alternate Pin Assignments

Since it is possible to assign any of the reserved differential pairs to a variety of functions, several alternate pin assignment options are provided as examples. These examples are not intended to cover all possible options and future baseboard designs may differ from these options.

|            | Option 1: Kitchen Sink |        |               |  |  |

|------------|------------------------|--------|---------------|--|--|

| Pin Name   | Side B                 | Side A | Pin Name      |  |  |

| P12V       | 1                      | 1      | PRSNT#        |  |  |

| P12V       | 2                      | 2      | P12V          |  |  |

| P12V       | 3                      | 3      | P12V          |  |  |

| GND        | 4                      | 4      | GND           |  |  |

| I2C_SCL    | 5                      | 5      | SVR_IDo       |  |  |

| I2C_SDA    | 6                      | 6      | SVR_ID1       |  |  |

| GND        | 7                      | 7      | COM_TX        |  |  |

| PWR_ON#    | 8                      | 8      | COM_RX        |  |  |

| USB_P      | 9                      | 9      | SVR_ID2       |  |  |

| USB_N      | 10                     | 10     | SVR_ID3       |  |  |

| SYS_RESET# | 11                     | 11     | PCIE_RESET#   |  |  |

|            |                        |        |               |  |  |

| I2C_ALERT# | 12                     | 12     | GND           |  |  |

| GND        | 13                     | 13     | PCIE_REFCLK_P |  |  |

| GND        | 14                     | 14     | PCIE_REFCLK_N |  |  |

| PCIE_TX0_P | 15                     | 15     | GND           |  |  |

| PCIE_TX0_N | 16                     | 16     | GND           |  |  |

| GND        | 17                     | 17     | PCIE_RXo_P    |  |  |

| GND        | 18                     | 18     | PCIE_RXo_N    |  |  |

| PCIE_TX1_P | 19                     | 19     | GND           |  |  |

| PCIE_TX1_N | 20                     | 20     | GND           |  |  |

| GND        | 21                     | 21     | PCIE_RX1_P    |  |  |

| GND        | 22                     | 22     | PCIE_RX1_N    |  |  |

| PCIE_TX2_P | 23                     | 23     | GND           |  |  |

| PCIE_TX2_N | 24                     | 24     | GND           |  |  |

| GND        | 25                     | 25     | PCIE_RX2_P    |  |  |

| GND        | 26                     | 26     | PCIE_RX2_N    |  |  |

| PCIE_TX3_P | 27                     | 27     | GND           |  |  |

| PCIE_TX3_N | 28                     | 28     | GND           |  |  |

| GND        | 29                     | 29     | PCIE_RX3_P    |  |  |

| GND        | 30                     | 30     | PCIE_RX3_N    |  |  |

| SATAo_TX_P | 31                     | 31     | GND           |  |  |

|            |                        |        |               |  |  |

|                   | <u>.</u> |    |              |

|-------------------|----------|----|--------------|

| SATAo_TX_N        | 32       | 32 | GND          |

| GND               | 33       | 33 | SATAo_RX_P   |

| GND               | 34       | 34 | SATAo_RX_N   |

| $MGMT\_GE\_TX\_P$ | 35       | 35 | GND          |

| $MGMT\_GE\_TX\_N$ | 36       | 36 | GND          |

| GND               | 37       | 37 | MGMT_GE_RX_P |

| GND               | 38       | 38 | MGMT_GE_RX_N |

| RFU               | 39       | 39 | GND          |

| RFU               | 40       | 40 | GND          |

| GND               | 41       | 41 | RSVD         |

| GND               | 42       | 42 | RSVD         |

| GEo_RX_P          | 43       | 43 | GND          |

| GEo_RX_N          | 44       | 44 | GND          |

| GND               | 45       | 45 | RSVD         |

| GND               | 46       | 46 | RSVD         |

| GEo_TX_P          | 47       | 47 | GND          |

| GEo_TX_N          | 48       | 48 | GND          |

| GND               | 49       | 49 | RFU          |

|                   |          |    |              |

Figure 10 Pin Assignment Option 1, which Defines a Little Bit of Everything

| Option 2: 8x Ethernet |        |        |             |  |

|-----------------------|--------|--------|-------------|--|

| Pin Name              | Side B | Side A | Pin Name    |  |

| P12V                  | 1      | 1      | PRSNT#      |  |

| P12V                  | 2      | 2      | P12V        |  |

| P12V                  | 3      | 3      | P12V        |  |

| GND                   | 4      | 4      | GND         |  |

| I2C_SCL               | 5      | 5      | SVR_IDo     |  |

| I2C_SDA               | 6      | 6      | SVR_ID1     |  |

| GND                   | 7      | 7      | COM_TX      |  |

| PWR_ON#               | 8      | 8      | COM_RX      |  |

| USB_P                 | 9      | 9      | SVR_ID2     |  |

| USB_N                 | 10     | 10     | SVR_ID3     |  |

| SYS_RESET#            | 11     | 11     | PCIE_RESET# |  |

|                       |        |        |             |  |

| I2C_ALERT#            | 12     | 12     | GND         |  |

| GND                   | 13     | 13     | RSVD        |  |

| GND                   | 14     | 14     | RSVD        |  |

| GE6_RX_P              | 15     | 15     | GND         |  |

| GE6_RX_N              | 16     | 16     | GND         |  |

| GND                   | 17     | 17     | GE7_RX_P    |  |

| GND                   | 18     | 18     | GE7_RX_N    |  |

| GE6_TX_P | 19 | 19 | GND      |

|----------|----|----|----------|

| GE6_TX_N | 20 | 20 | GND      |

| GND      | 21 | 21 | GE7_TX_P |

| GND      | 22 | 22 | GE7_TX_N |

| GE4_RX_P | 23 | 23 | GND      |

| GE4_RX_N | 24 | 24 | GND      |

| GND      | 25 | 25 | GE5_RX_P |

| GND      | 26 | 26 | GE5_RX_N |

| GE4_TX_P | 27 | 27 | GND      |

| GE4_TX_N | 28 | 28 | GND      |

| GND      | 29 | 29 | GE5_TX_P |

| GND      | 30 | 30 | GE5_TX_N |

| GE2_RX_P | 31 | 31 | GND      |

| GE2_RX_N | 32 | 32 | GND      |

| GND      | 33 | 33 | GE3_RX_P |

| GND      | 34 | 34 | GE3_RX_N |

| GE2_TX_P | 35 | 35 | GND      |

| GE2_TX_N | 36 | 36 | GND      |

| GND      | 37 | 37 | GE3_TX_P |

| GND      | 38 | 38 | GE3_TX_N |

| RFU      | 39 | 39 | GND      |

| RFU      | 40 | 40 | GND      |

| GND      | 41 | 41 | GE1_RX_P |

| GND      | 42 | 42 | GE1_RX_N |

| GEo_RX_P | 43 | 43 | GND      |

| GEo_RX_N | 44 | 44 | GND      |

| GND      | 45 | 45 | GE1_TX_P |

| GND      | 46 | 46 | GE1_TX_N |

| GEo_TX_P | 47 | 47 | GND      |

| GEo_TX_N | 48 | 48 | GND      |

| GND      | 49 | 49 | RFU      |

Figure 11 Pin Assignment Option 2, which Provides 8 Ethernet Ports

| Option 3: 6x SATA + 2x 10GbE |                        |   |         |  |  |  |

|------------------------------|------------------------|---|---------|--|--|--|

| Pin Name                     | Pin Name Side B Side A |   |         |  |  |  |

| P12V                         | 1                      | 1 | PRSNT#  |  |  |  |

| P12V                         | 2                      | 2 | P12V    |  |  |  |

| P12V                         | 3                      | 3 | P12V    |  |  |  |

| GND                          | 4                      | 4 | GND     |  |  |  |

| I2C_SCL                      | 5                      | 5 | SVR_IDo |  |  |  |

| I2C_SDA    | 6  | 6  | SVR_ID1     |

|------------|----|----|-------------|

| GND        | 7  | 7  | COM_TX      |

| PWR_ON#    | 8  | 8  | COM_RX      |

| USB_P      | 9  | 9  | SVR_ID2     |

| USB_N      | 10 | 10 | SVR_ID3     |

| SYS_RESET# | 11 | 11 | PCIE_RESET# |

|            |    |    |             |

| I2C_ALERT# | 12 | 12 | GND         |

| GND        | 13 | 13 | RSVD        |

| GND        | 14 | 14 | RSVD        |

| SATA5_TX_P | 15 | 15 | GND         |

| SATA5_TX_N | 16 | 16 | GND         |

| GND        | 17 | 17 | SATA5_RX_P  |

| GND        | 18 | 18 | SATA5_RX_N  |

| SATA4_TX_P | 19 | 19 | GND         |

| SATA4_TX_N | 20 | 20 | GND         |

| GND        | 21 | 21 | SATA4_RX_P  |

| GND        | 22 | 22 | SATA4_RX_N  |

| SATA3_TX_P | 23 | 23 | GND         |

| SATA3_TX_N | 24 | 24 | GND         |

| GND        | 25 | 25 | SATA3_RX_P  |

| GND        | 26 | 26 | SATA3_RX_N  |

| SATA2_TX_P | 27 | 27 | GND         |

| SATA2_TX_N | 28 | 28 | GND         |

| GND        | 29 | 29 | SATA2_RX_P  |

| GND        | 30 | 30 | SATA2_RX_N  |

| SATA1_TX_P | 31 | 31 | GND         |

| SATA1_TX_N | 32 | 32 | GND         |

| GND        | 33 | 33 | SATA1_RX_P  |

| GND        | 34 | 34 | SATA1_RX_N  |

| SATAo_TX_P | 35 | 35 | GND         |

| SATAo_TX_N | 36 | 36 | GND         |

| GND        | 37 | 37 | SATAo_RX_P  |

| GND        | 38 | 38 | SATAo_RX_N  |

| RFU        | 39 | 39 | GND         |

| RFU        | 40 | 40 | GND         |

| GND        | 41 | 41 | GE1_RX_P    |

| GND        | 42 | 42 | GE1_RX_N    |

| GEo_RX_P   | 43 | 43 | GND         |

| GEo_RX_N   | 44 | 44 | GND         |

| GND        | 45 | 45 | GE1_TX_P    |

| GND      | 46 | 46 | GE1_TX_N |

|----------|----|----|----------|

| GEo_TX_P | 47 | 47 | GND      |

| GEo_TX_N | 48 | 48 | GND      |

| GND      | 49 | 49 | RFU      |

Figure 12 Pin Assignment Option 3, which Provides SATA and Ethernet Ports

### 6.3. Ethernet

At least one Ethernet connection (GEo\_TX/RX) is required on the card. To enable maximum compatibility and a variety of potential topologies, this Ethernet port is a PHY layer device and must be capable of the following:

| Mode        | Standard           | Encoding |

|-------------|--------------------|----------|

| 1000BASE-X  | IEEE Clause 36, 37 | 8b/10b   |

| 1000BASE-KX | IEEE 802.3ap       | 8b/10b   |

| 10GBase-KR  | IEEE 802.3ap       | 64b/66b  |

Ideally, the Ethernet port should be a 10Gb port, but a first generation design may support 1GbE or 2.5GbE. The port is capable of auto-negotiating down to lower speeds as necessary (1GbE is the minimum required).

To support 10Gb speeds, it is critical that the differential pairs for transmit and receive adhere to the following rules:

- Each differential pair must be no longer than 2" including SOC breakout and the connection to the edge connector pad

- No more than 1 via is allowed.

- A minimum spacing of 120mils is maintained at all times (with the exception of the SOC breakout) between the transmit or receive differential pairs, and any adjacent signals.

#### 6.4. SATA

The SATA connections are a minimum of SATA2.0 (3Gb/s) and may be SATA3.0 (6Gb/s).

#### 6.5. PCIe

The PCIe connection is a minimum of PCIe 2.0 and may be PCIe 3.0.

#### 6.6. I2C

The single I2C connection is the primary server management interface. It supports a speed of 1MHz. The card does not contain a BMC as the primary BMC will be located on the baseboard. The BMC on the baseboard will act as the master on the bus during normal operation. During POST, the SOC may also act as a master. It is acceptable to have a small amount of glue logic on the card to support translating and/or buffering SOC signals. The I2C alert is signal is required and is used as an interrupt for the BMC.

Both the SOC and the BMC on the baseboard may be masters on the bus so a multimaster environment must be supported.

### 7. Power

### 7.1. Input

Power for the card is provided via five 12V pins on the PCIe connector. Each pin supports up to 1.1A of current for a maximum of 5.5A per card. However, the card is designed to only support a maximum of 60W. The nominal voltage is 12.0V, but may vary between 10.8V and 13.2V.

### 7.2. Hot-Plug Support

Hot-plug circuitry is not required on the card.

### 7.3. VR Efficiency

All VRs providing over 15W on the card are at least 91% efficient when loaded between 30% and 90%.

### 7.4. Input Capacitance

The capacitance provided on the input 12V rail does not exceed 400uF.

### 8. Functional

### 8.1. Memory

Each card must support a minimum of 4GB of DDR3 low-voltage SDRAM memory. Memory may be provided as one or more modules, or soldered directly to the card.

### 8.2. Storage

Each card must support a minimum of 128GB of low-cost, MLC flash to be used as a boot device. If the flash is SATA-based, it must be connected to SATA port o. Additional SATA connections are connected to port 1 and higher. The flash may be provided as a mSATA or NGFF card, or be soldered directly to the card.

### 8.3. EEPROM

Each card must include an I2C-accessible EEPROM. The EEPROM must be accessible from the I2C connection going to the baseboard and be at least 128Kbits. The I2C address for the EEPROM should be set to 0xAo. The EEPROM will contain the FRUID information and any additional configuration information that may be required. The FRUID is formatted in accordance with the IPMI Platform Management FRU Information Storage Definition document.

The EEPROM must contain the following:

- Device Description

- Chassis Type: Micro-server

- Chassis Serial

- Board Mfg

- Board Product

- Board Serial

- Board Part Number

- Product Manufacturer

- Product Name

- Product Part Number

- Product Serial Number

- Product Asset Tag

- Product Build: e.g. EVT, DVT, PVT, MP

- Product Version: e.g. C1

- Product Comments: e.g.

- Manufacturing date code:

- Manufacturing lot code: (preferred, but optional)

- Manufacturing work order: (preferred, but optional)

- PCB revision

- SOC model name/number

- SOC revision

This information will be available via IPMI commands from the BMC.

#### 8.4. BIOS

The card supplier is responsible for supplying and customizing the BIOS for the SOC. The requirements are outlined in this section.

#### 8.4.1. Configuration and Features

The BIOS is tuned to minimize card power consumption. It has the following features:

- Unused devices are disabled including PCIe\* lanes, USB ports, SATA/SAS ports, etc

- BIOS setup menu

- SOC settings are provided to allow tuning to achieve the optimal combination of performance and power consumption.

#### 8.4.2. PXE Boot

The BIOS supports PXE boot and provide the ability to modify the boot sequence. When PXE booting, the card first attempts to boot from the first Ethernet device (etho). If this fails, PXE boot is attempted on the next Ethernet device.

The default boot device priority is:

- 1. Network (search all configured network interfaces)

- 2. HDD, SSD, or flash device (local or remote)

- 3. CD-ROM

- 4. Removable Device

This process loops indefinitely and requires no user-intervention.

#### 8.4.3. Other Boot Options

The BIOS also supports booting from SATA/SAS and USB interfaces. The BIOS provides the capability to select boot options.

#### 8.4.4. Remote BIOS Update

The BIOS can be updated remotely under these scenarios:

- Scenario 1: Sample/Audit BIOS settings

- o Return current BIOS settings, or

- Save/export BIOS settings in a human-readable form that can be restored/imported (as in scenario 2)

- Scenario 2: Update BIOS with pre-configured set of BIOS settings

- o Update/change multiple BIOS settings

- o Reboot

- Scenario 3: BIOS/firmware update with a new revision

- Load new BIOS/firmware on machine and update, retaining current BIOS settings

- Reboot

Additionally, the update tools have the following capabilities:

- Update from the operating system over the LAN the OS standard is CentOS v5.2

- Can complete BIOS update or setup change with a single reboot (no PXE boot, no multiple reboots)

- No user interaction (like prompts)

- BIOS updates and option changes do not take longer than five minutes to complete

- Can be scripted and propagated to multiple machines

#### 8.4.5. Event Log

An event log needs to be implemented to capture informational and error messages. Per SMBIOS specification Rev 2.6, the BIOS implements SMBIOS type 15 for an event log; the assigned area is large enough to hold more than 500 event records (assuming the maximum event record length is 24 bytes, then the size will be larger than 12KB), and follow the SMBIOS event log organization format for the event log.

A system access interface and application software must be provided to retrieve and clear the event log from the BIOS, including, at minimum, a Linux application for the CentOS operating system and driver as needed. The event log must be retrieved and stored as a readable text file that is easy to handle by a scripting language under Linux. Each event record includes enhanced information identifying the error source device's vendor ID, card slot ID, and device ID.

#### 8.4.6. Logged Errors

The following list of errors are logged by the BIOS and must include date, time, and location information which can be used to identify the failing component.

- CPU/Memory errors: Both correctable ECC and uncorrectable ECC errors are logged into the event log. Error categories include DRAM, Link, and L3 cache.

- PCIe\* errors: Any errors that have a status register are logged into the event log, including root complex, endpoint device, and any switch upstream/downstream ports if available. Link disable on errors are also be logged. Fatal, non-fatal, or correctable classification follows the chipset vendor's recommendation.

- POST errors: All POST errors detected by the BIOS during POST are logged into the event log.

- Power errors: Two power errors are logged:

- o 12.0VDC input power failure that causes all power rails to lose power.

- Unexpected system shutdown during system So/S1 while 12.0VDC input is still valid.

- MEMHOT# and PROCHOT# errors: Memory hot errors and processor hot errors are logged. The error log identifies the error source as internally coming from the processor or memory, or externally coming from the voltage regulator.

- SATA or SAS errors: All correctable and uncorrectable errors are logged.

#### 8.4.7. Error Thresholds

An error threshold setting must be enabled for both correctable and uncorrectable errors. Once the programmed threshold is reached, an event is triggered and logged.

• Memory Correctable ECC: The threshold value is 1000. When the threshold is reached, the BIOS logs the event and includes DIMM location.

#### 8.4.8. POST Codes

The BIOS outputs a set of POST codes identifying the current initialization step and any errors encountered along the way. The output is provided on the serial console and errors are logged.

### 8.5. Management

The primary server management functions will be provided using a BMC on the baseboard. The BMC on the baseboard will use the I2C connection as the sideband interface. This section identifies the required information that must be accessible from the BMC.

#### 8.5.1. Serial Console

The SOC provides a serial UART that is connected directly to the card edge. This connection will be used as the BIOS or OS serial console and will also be available as a Serial Over LAN (SOL) connection via the BMC.

#### 8.5.2. Power Control

The BMC controls power on, off, and reset directly via the signals defined in the pin-out. If 12V to the card is lost and returns ("AC Lost"), the BIOS must be configurable to enable immediate or delayed power-on, or the last power state prior to the event.

#### 8.5.3. Thermal Alerts

The SOC provides a mechanism to provide thermal alerts and overtemp notifications. The BMC must be able to receive these alerts in a timely fashion to allow it take action quickly. The I2C alert signal must be used. In some cases, an overtemp condition may occur which forces the SOC to power-off immediately. This condition must be logged.

#### 8.5.4. Sensors

The following list of analog and discrete sensors are provided and are reported by the BMC.

Analog sensors include:

- CPU temp/thermal margin

- DIMM temp

- Ambient temp

#### Discrete sensors include:

- CPU therm trip

- Power threshold event

- SEL status

- Battery low (if battery is used)

- DCMI watchdog

- POST error

- ProcHot assertion

- MemHot assertion

- Machine check error

- PCIe error

- Other IO error

- · Memory error

### 8.6. Battery

A battery on the card is not required. The BIOS pulls its settings from non-volatile memory.

#### 8.7. **LEDs**

Each card contains a power LED that illuminates when the power-on sequence on the card has completed successfully. The LED is blue in color and placed on the leading edge of the card (cold-aisle).

# 9. Environmental Requirements

The full system with the server card installed meets the following environmental requirements:

- Gaseous Contamination: Severity Level G1 per ANSI/ISA 71.04-1985

- Storage relative humidity: 10% to 90% (non-condensing)

- Storage temperature range: -40°C to +70°C (long-term storage)

- Transportation temperature range: -55°C to +85°C (short-term storage)

- Operating altitude with no de-rating to 1000m (3300 feet)

Operating temperatures and relative humidity can be found in section 5.2.

#### 9.1. Vibration and Shock

The motherboard meets shock and vibration requirements according to the following IEC specifications: IEC78-2-(\*) and IEC721-3-(\*) Standard & Levels.

|           | Operating                                                                                                                                  | Non-Operating                                                                                                                                   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Vibration | 0.5g acceleration, 1.5mm amplitude, 5 to 500 Hz, 10 sweeps at 1 octave / minute for each of the three axes (one sweep is 5 to 500 to 5 Hz) | 1g acceleration, 3mm amplitude, 5<br>to 500 Hz, 10 sweeps at 1 octave /<br>minute for each of the three axes<br>(one sweep is 5 to 500 to 5 Hz) |

| Shock | 6g, half-sine 11mS, 5 shocks for each of the | 12g, half-sine 11mS, 10 shocks for |

|-------|----------------------------------------------|------------------------------------|

|       | three axes                                   | each of the three axes             |

Figure 13 Vibration and Shock Requirements

### 10. Prescribed Materials

### 10.1. Disallowed Components

The following components are not used in the design of the motherboard:

- Components disallowed by the European Union's Restriction of Hazardous Substances Directive (RoHS 6)

- Trimmers and/or potentiometers

- Dip switches

### 10.2. Capacitors and Inductors

The following limitations apply to the use of capacitors:

- Only aluminum organic polymer capacitors made by high quality manufacturers are used; they must be rated 105°C

- All capacitors have a predicted life of at least 50,000 hours at 45°C inlet air temperature, under worst conditions

- Tantalum capacitors using manganese dioxide cathodes are forbidden

- SMT ceramic capacitors with case size > 1206 are forbidden (size 1206 are still allowed when installed far from the PCB edge and with a correct orientation that minimizes risks of cracks)

- Ceramic material for SMT capacitors must be X7R or better material (COG or NPo type are used in critical portions of the design) Only SMT inductors may be used. The use of through hole inductors is disallowed. 13.3

### 10.3. Component De-rating

For inductors, capacitors, and FETs, de-rating analysis is based on at least 20% de-rating.