Version 0.6

Authors:

ADLINK Technology, Inc.

# 1 Revision History

| Date       | Name                   | Description                                                   |

|------------|------------------------|---------------------------------------------------------------|

| 11-28-2016 | ADLINK Technology Inc. | Version 0.1 Content layout                                    |

| 12-16-2016 | ADLINK Technology Inc. | Version 0.5 Draft for internal review                         |

| 12-18-2016 | ADLINK Technology Inc. | Version 0.6 Updates based on Mondo, Jeff discussions          |

| 12-19-2016 | ADLINK Technology Inc. | Version 0.61 updated B2B connectors and compute zone section. |

|            |                        |                                                               |

|            |                        |                                                               |

|            |                        |                                                               |

|            |                        |                                                               |

|            |                        |                                                               |

# 2 Contents

| 1  | Revision History                                            | 2  |

|----|-------------------------------------------------------------|----|

| 2  | Contents                                                    | 3  |

| 3  | License                                                     | 5  |

| 4  | Scope                                                       | 5  |

| 5  | Overview                                                    | 6  |

|    | 5.1 Overview                                                | 6  |

|    | 5.2 CG-OpenRack-19 Introduction                             | 6  |

| 6  | OpenPOD Server Physical Specification                       |    |

|    | 6.1 OpenPOD Server Mechanical Dimensions                    |    |

|    | 6.2 OpenPOD Server Zone Layout                              | 9  |

|    | 6.3 OpenPOD Server Mechanical Retention and Handle Features |    |

| 7  | Connectivity Zone Specifications                            |    |

|    | 7.1 Power Connector Placement                               |    |

|    | 7.2 Optical Connector Placement                             |    |

| 8  | Cooling Zone Specifications                                 |    |

| 9  | Power Zone Specifications                                   |    |

|    | 9.1 Power and Fan Schema                                    |    |

|    | 9.2 Power Cable Connector                                   |    |

|    | 9.3 Fan Cable Connector                                     |    |

| 10 | Mezzanine Card Zone Specifications                          |    |

|    | 10.1 B2B Signal Connector                                   |    |

|    | 10.2 B2B Power Connector                                    |    |

|    | 10.3 B2B Guide Pin                                          |    |

|    | 10.4 10G Mezzanine Card Example                             |    |

| 11 | Compute Zone Specifications                                 |    |

|    | 11.1 Power System                                           |    |

|    | 11.2 Front Panel                                            |    |

|    | 11.3 Basic Input Output System (BIOS)                       |    |

|    | 11.4 Baseboard Management Controller (BMC)                  |    |

| 12 | Environmental Specifications                                | 41 |

| Shock & Vibration                                                     | 42                                                                                                                                                                                                                                 |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Appendix                                                              | 43                                                                                                                                                                                                                                 |

| 14.1 Appendix: Commonly Used Acronyms                                 | 43                                                                                                                                                                                                                                 |

| 14.2 Appendix: ADLINK Modular Industrial Cloud Architecture CPU board | 44                                                                                                                                                                                                                                 |

| 14.3 Appendix: OEM IPMI Command                                       | . 49                                                                                                                                                                                                                               |

|                                                                       | <ul> <li>Shock &amp; Vibration</li> <li>Appendix</li> <li>14.1 Appendix: Commonly Used Acronyms</li> <li>14.2 Appendix: ADLINK Modular Industrial Cloud Architecture CPU board</li> <li>14.3 Appendix: OEM IPMI Command</li> </ul> |

# 3 License

As of 12-20-2016, the following persons or entities have made this Specification available under the OWFa1.0, which is available at [To be replaced by permanent link after license has been decided]. ADLINK Technology Inc.

You can review the signed copies of the Contributor License for this Specification on the OCP website http://opencompute.org/, which may also include additional parties to those listed above. Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 4 Scope

CG-OpenRack-19 OpenPOD server is scalable carrier-grade rack level system that integrates high performance compute, storage and networking in a standard rack. As such, there are many possible system configurations. However, certain rules and requirements ensure that different modules will operate properly in compliant systems.

This document provides the detailed interoperability requirements of a CG-OpenRack-19 OpenPOD server. This document describes the physical makeup of the OpenPOD server with a focus on the board to board interfaces between the compute board and the mezzanine card. This includes mechanical requirements as well as requirements related to electrical power feeds, optical and electrical interfaces, airflow and cooling, and environmental robustness.

# **5** Overview

#### 5.1 Overview

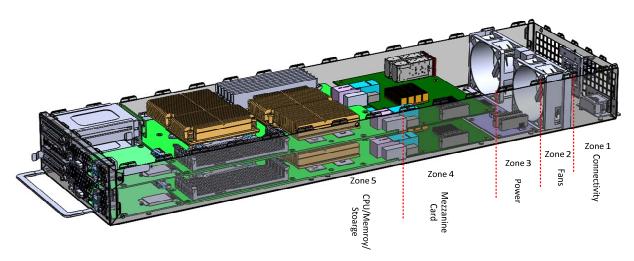

The OpenPOD server is a half-width sled in the CG-OpenRack-19 form factor. The OpenPOD server is constructed based on zones, which are partitioned chassis spaces that are reserved to implement different functionalities for the server.

- Zone 1: Defines the rear compartment (should be fairly open for air flow requirements), optical and power connectors.

- Zone 2: Defines the types of fans to be used in order to provide the required airflow for half-width sled.

- Zone 3: Defines the power specification for the half-width OpenPOD server to support CPU/memory/storage, mezzanine, and fans.

- Zone 4: Defines the mezzanine card area for networking options.

- Zone 5: Defines the compute board size, shape and interconnectivity to mezzanine card.

The zone partition of OpenPOD server makes it easier to upgrade the networking and computing capability independent of each other. In case that a higher bandwidth is required, the OpenPOD server supports upgrading the mezzanine board alone. The reverse is also true. When upgrading the computing sled in accord with Intel update cycle, the other zones can be kept without any changes.

#### Figure 1. OpenPOD Server with Different Functional Zones

#### 5.2 CG-OpenRack-19 Introduction

CG-OpenRack-19 is scalable carrier-grade rack level system that integrates high performance compute, storage and networking in a standard rack. In general, the system is made up of compute and storage-centric sleds, Ethernet switches, a power source, and supporting rack infrastructure as shown in Figure 2.

There are five major system component types: the system rack, power conversion/distribution, Top-of-Rack (ToR) switches, and two types of pluggable modules (sleds) which are differentiated by form factor (width).

- System Rack: The rack provides physical structure for the system, airflow control, security, and network interconnects.

- Power Source: Rack-mount power conversion and distribution infrastructure that provides a nominal 12VDC to two bus bar pairs mounted at the rear of the system.

- Half-Width Sled: A 2U enclosure that takes up half of the shelf width. A common use of this sled size is to provide high density compute resources.

- Full-Width Sled: A 2U enclosure that takes up the full shelf width. A common use of this sled size is to provide high capacity/throughput storage resources.

- Top-of-Rack (ToR) Switch: Each rack can be equipped with a variable number of management plane and data plane switches, also referred to as Top of Rack switches. Each of these aggregates management and/or data traffic to internal network switching planes.

#### Figure 2. Rack with Half-Width and Full-Width Sleds

# 6 OpenPOD Server Physical Specification

# 6.1 **OpenPOD Server Mechanical Dimensions**

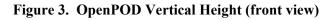

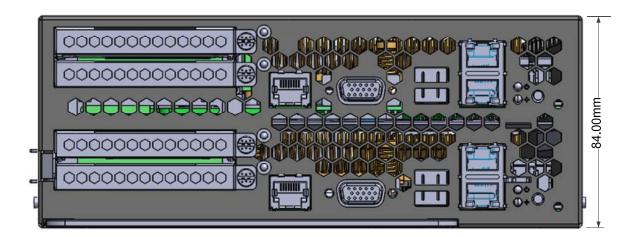

The OpenPOD server occupies a vertical spacing of 2 Rack Units (RU). The vertical height from the bottom face to the top face is 84.00mm.

#### Need to add the mechanical dimensions of each connector

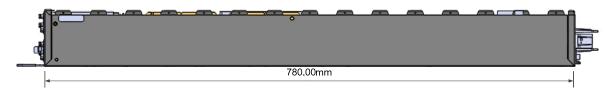

The OpenPOD server has a horizontal depth of 780.00mm as measured from the front face to the rear face.

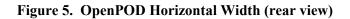

The OpenPOD server has a horizontal width of 215.00mm as measured from the left face to the right face.

The layout of the rear panel is defined in the CG-OpenRack 19 as defined by Radisys

# 6.2 **OpenPOD Server Zone Layout**

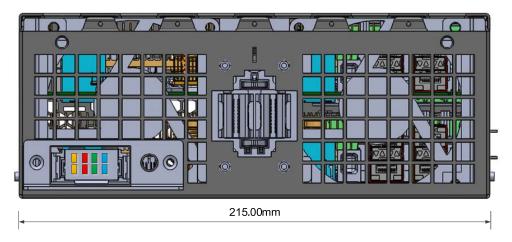

Figure 6. OpenPOD Zone Layout (Top view)

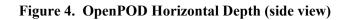

The OpenPOD server includes five functional zones. The Zone 1 is for connectivity, and has a depth of 75.00mm. The Zone 2 is for fan, and has a depth of 50.00mm. The Zone 3 is for power board, and has a depth of 70.00mm. The zone 4 is for mezzanine card, and has a depth of 145.00mm. The zone 5 is for compute sled, and has a depth of 440.00mm.

The zone 1, zone 2 and zone 3 are using single-layer structure, and they provide the common power, cooling, and blind-mate optical connector infrastructure for the OpenPOD server. The zone 4 and zone 5 are using two-layer structure, and each layer includes a compute board and a mezzanine card to

implement the required networking to blind-mate optical connector. Totally the OpenPOD server provides two independent server nodes with shared power input and cooling facility.

# 6.3 **OpenPOD Server Mechanical Retention and Handle Features**

The mechanical retention and handle features of the OpenPOD server are following the mechanical retention and handle requirements described in Section 6.6 of CG-OpenRack-19 Sled and Rack Specification.

# 7 Connectivity Zone Specifications

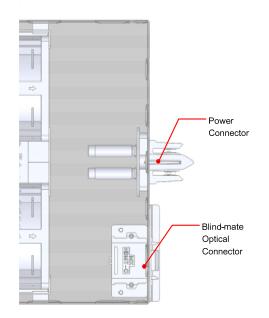

Zone 1 defines for the connectivity zone for power and optical connectors.

#### 7.1 Power Connector Placement

The power is retrieved from the two vertical bus bars in the rear of the CG-OpenRack-19 shelf. When the half-width OpenPOD server is installed in the left side of the shelf, it takes 12VDC power input from the left bus bar. When the half-width OpenPOD server is installed in the right side of the shelf, it takes 12VDC power input from the right bus bar.

The power connector of the OpenPOD server is following the power connector and bus bar pair requirements described in Section 6.3 and Section 7.1 of CG-OpenRack-19 Sled and Rack Specification.

Figure 7. OpenPOD Power Connector Placement (Top view)

# 7.2 Optical Connector Placement

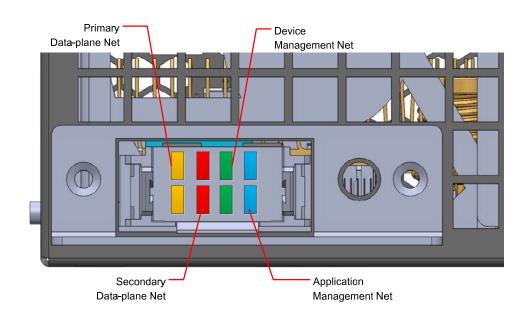

The main network connections of the OpenPOD server is implemented by following the sled optical data port requirements described in Section 8 of CG-OpenRack-19 Sled and Rack Specification.

There are totally eight pairs of rear-mounted blind-mate "daughtercard" optical housing that mate with a compatible "backplane" hosing on the rear of a CG-OpenRack-19 shelf. The eight interfaces are organized into two groups, and each group provides four links between a server node and the TOR switches.

- Yellow optic connector: 10/40GbE primary data-plane link

- Red optic connector: 10/40GbE secondary data-plane link

- Green optic connector: 1GbE IPMI-based device management link

- Blue optic connector: 1GbE application management link

Figure 8. OpenPOD Server Blind-mate Optical Connector Assignment (rear view)

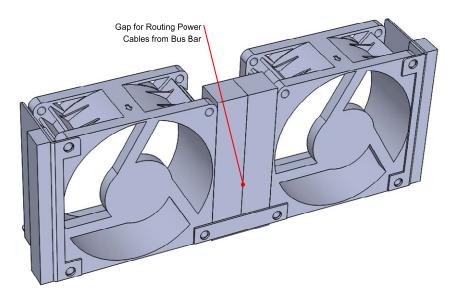

# 8 Cooling Zone Specifications

Zone 2 defines for the cooling zone to place two PWM fans. In the middle of the two fans, there is a small gap that is reserved to the cabling of the power line from the bus bar.

Figure 9. OpenPOD Server FAN Zone

There is a BMC on each server node, which is responsible for monitoring the temperature sensors on the compute board and its supporting mezzanine card, and then a proper fan speed is selected and a corresponding PWM value is outputted by each BMC. A PWM comparator on the power board will select the larger PWM to driver the fans.

The types of fans and airflow to cool zones 3-5 should be engineered based on the modules installed.

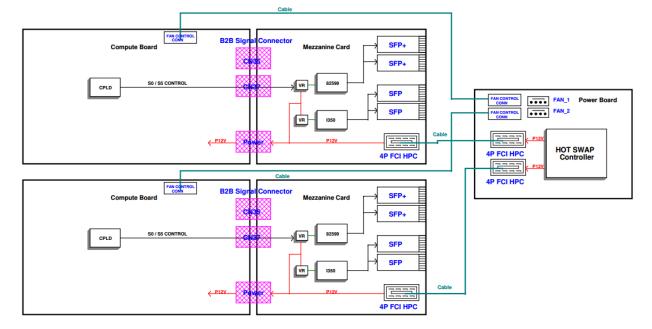

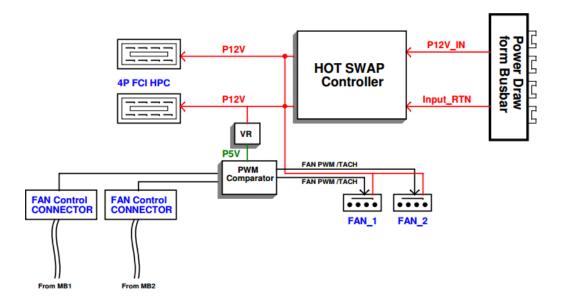

Figure 10. The Power and Fan Scheme of OpenPOD Server

# 9 Power Zone Specifications

Zone 3 defines for power zone to place the power board, which takes power form the rear bus-bar and supplies it to the mezzanine cards, compute boards, and also the cooling fans.

#### 9.1 Power and Fan Schema

The power supply board includes a hot-swap controller which is used to support the hot-swapping of the whole OpenPOD server. When the power board detects the insertion of the OpenPOD server is put in place, it will enable the +12V power supply from bus-bar to the mezzanine card directly.

The electronic components on the mezzanine cards draw power via a voltage regulator behind the +12V power supply. There is board to bard connector between compute board and mezzanine card, which is used to route the +12V power supply from the mezzanine card to the front server board. There are several voltage regulators on the compute board that transform the +12V power supply into the required voltage levels on the compute board. The cooling fans draw its power directly from a voltage regulator on the power board.

Figure 11. Block Diagram of Power Board

#### Provide the physical dimensions of the power card including placement of connectors

#### 9.2 Power Cable Connector

The power board and mezzanine card use one pair of HPC connectors from FCI Electronics for power delivery from power board to mezzanine card via a cable. The pin definitions are described in the following table.

| Net name | Pin | Description                          | Group  |

|----------|-----|--------------------------------------|--------|

| P12V     | A1  | P12V power delivery from power board | Power  |

| P12V     | B1  | to mezzanine card                    | Tower  |

| GND      | A2  | Ground return                        | Ground |

| GND      | B2  |                                      | Ground |

Table 1. The Pin Definitions of Power Cable Connectors

#### 9.3 Fan Cable Connector

The power board is also responsible for the PWN splitting and driver the cooling FAN. Because there are two server nodes in the OpenPOD server, so there are two PWM signals from two independent compute board, and they are all routed to a PWM comparator on the power board via fan cables, and the PWM comparator selects the higher PWM signal and uses it to determine the speed of the cooling fans.

The fan cable connector is from HIROSE (P/N: DF11-14DP-2DSA), and the pin definitions of the fan cable connector is shown in the table 2.

| Net name           | Pin | I/O | Description                                                   |

|--------------------|-----|-----|---------------------------------------------------------------|

| GND                | 1   |     | Ground return                                                 |

| GND                | 2   |     | Ground return                                                 |

| BBC_FAN_PWM3       | 3   | 0   | FAN PWM output from motherboard to FAN board                  |

| BBC_FAN_TACH3      | 4   | Ι   | FAN TACH input from FAN board to motherboard                  |

| BBC_FAN_PWM2       | 5   | 0   | FAN PWM output from motherboard to FAN board                  |

| BBC_FAN_TACH2      | 6   | Ι   | FAN TACH input from FAN board to motherboard                  |

| BBC_FAN_PWM1       | 7   | 0   | FAN PWM output from motherboard to FAN board                  |

| BBC_FAN_TACH1      | 8   | Ι   | FAN TACH input from FAN board to motherboard                  |

| BBC_FAN_PWM3_EN    | 9   | 0   | FAN board power control signal from motherboard to FAN board  |

| FAN_PWM3_PRESENT_N | 10  | Ι   | FAN present signal from FAN board to motherboard, Low active. |

| BBC_FAN_PWM2_EN    | 11  | 0   | FAN board power control signal from motherboard to FAN board  |

| FAN_PWM2_PRESENT_N | 12  | Ι   | FAN present signal from FAN board to motherboard, Low active. |

| BBC_FAN_PWM1_EN    | 13  | 0   | FAN board power control signal from motherboard to FAN board  |

| FAN_PWM1_PRESENT_N | 14  | Ι   | FAN present signal from FAN board to motherboard, Low active. |

# **10 Mezzanine Card Zone Specifications**

Zone 4 defines for a replaceable mezzanine card in order to support different network configurations. By now, both 2x10G and 2x40G data plane net can be supported.

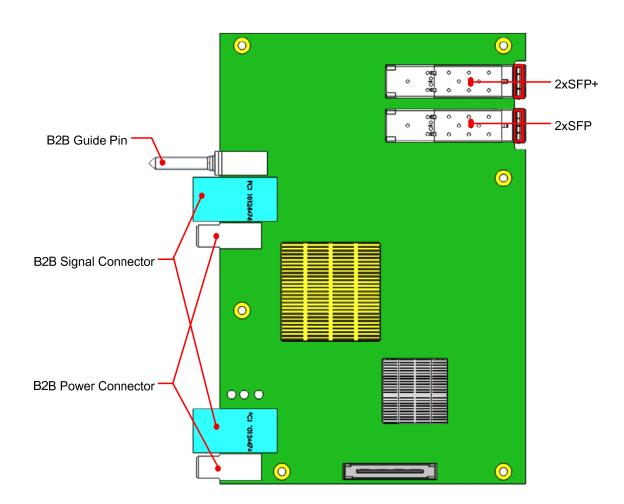

On the front side, the mezzanine card has 5 board to board (B2B) connectors. Two of them are used for signal connection, two of them are used for power connection, and the remained one is guide pin.

On the rear side, the mezzanine card has 2xSFP and 2xSFP+ interfaces that provide the required optical connection to the rear blind-mate connector. The mezzanine card(s) should be attached to the botoom of the Open Pod via screws as the Mezzanine cards will be stationary for Zone 5 boards to slide into.

Figure 12. OpenPOD Server Mezzanine Card (top view)

Add all dimensions of the mezzanine card specifically for the connectors

#### **10.1 B2B Signal Connector**

The mezzanine card uses two FCI AirMax VSe R.A. connectors (P/N:10124474) for the signal connection.

There are two B2B signal connectors (CN35 and CN37). The signal connector (CN35) includes one group of PCIex8 Gen3 lanes. The pin definition of CN35 is shown in Table 3.

| Net name         | Pin | Drive  | IO/Signal<br>Type | AC<br>Cap on<br>board | Description                                                 | PCIE root<br>port<br>or Group |

|------------------|-----|--------|-------------------|-----------------------|-------------------------------------------------------------|-------------------------------|

| BBC_PCIE-P0      | A1  | РСН    | O/CLK             | N/A                   | 100 MHz PCIe 3.0 specification compliant differential clock |                               |

| BBC_PCIE-N0      | B1  | РСН    | O/CLK             | N/A                   | 100 MHz PCIe 3.0 specification compliant differential clock |                               |

| GND              | C1  |        |                   |                       |                                                             |                               |

| CPU0_BBC_C_TXP24 | D1  | CPU0   | O/PCIe            | Yes                   | PCIe Transmit Data Output                                   | PE1A                          |

| CPU0_BBC_C_TXN24 | E1  | CPU0   | O/PCIe            | Yes                   | PCIe Transmit Data Output                                   | PE1A                          |

| GND              | F1  |        |                   |                       |                                                             |                               |

| CPU0_BBC_C_TXP28 | G1  | CPU0   | O/PCIe            | Yes                   | PCIe Transmit Data Output                                   | PE1B                          |

| CPU0_BBC_C_TXN28 | H1  | CPU0   | O/PCIe            | Yes                   | PCIe Transmit Data Output                                   | PE1B                          |

| GND              | I1  |        |                   |                       |                                                             |                               |

| CPU0_BBC_RXP27   | J1  | DEVICE | I/PCIe            | No                    | PCIe Receive Data Input                                     | PE1A                          |

| CPU0_BBC_RXN27   | K1  | DEVICE | I/PCIe            | No                    | PCIe Receive Data Input                                     | PE1A                          |

| GND              | L1  |        |                   |                       |                                                             |                               |

| CPU0_BBC_RXP31   | M1  | DEVICE | I/PCIe            | No                    | PCIe Receive Data Input                                     | PE1B                          |

| CPU0_BBC_RXN31   | N1  | DEVICE | I/PCIe            | No                    | PCIe Receive Data Input                                     | PE1B                          |

| GND              | 01  |        |                   |                       |                                                             |                               |

|                  |     |        |                   |                       |                                                             |                               |

| GND              | A2  |        |                   |                       |                                                             |                               |

#### Table 3. The Pin Definitions of B2B Signal Connector CN35

| SATA_C_TX-P2     | B2 | РСН    | O/SATA | Yes | PCH Serial ATA 2 Differential<br>Transmit Pair |      |

|------------------|----|--------|--------|-----|------------------------------------------------|------|

| SATA_C_TX-N2     | C2 | РСН    | O/SATA | Yes | PCH Serial ATA 2 Differential<br>Transmit Pair |      |

| GND              | D2 |        |        |     |                                                |      |

| CPU0_BBC_C_TXP25 | E2 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1A |

| CPU0_BBC_C_TXN25 | F2 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1A |

| GND              | G2 |        |        |     |                                                |      |

| CPU0_BBC_C_TXP29 | H2 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1B |

| CPU0_BBC_C_TXN29 | I2 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1B |

| GND              | J2 |        |        |     |                                                |      |

| CPU0_BBC_RXN26   | K2 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1A |

| CPU0_BBC_RXP26   | L2 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1A |

| GND              | M2 |        |        |     |                                                |      |

| CPU0_BBC_RXP30   | N2 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1B |

| CPU0_BBC_RXN30   | 02 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1B |

| GND              | Р2 |        |        |     |                                                |      |

|                  |    |        |        |     |                                                |      |

| SATA_C_RX-P2     | A3 | DEVICE | I/SATA | No  | PCH Serial ATA 2 Differential<br>Receive Pair  |      |

| SATA_C_RX-N2     | В3 | DEVICE | I/SATA | No  | PCH Serial ATA 2 Differential<br>Receive Pair  |      |

| GND              | C3 |        |        |     |                                                |      |

| CPU0_BBC_C_TXP26 | D3 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1A |

| CPU0_BBC_C_TXN26 | E3 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1A |

| GND              | F3 |        |        |     |                                                |      |

| CPU0_BBC_C_TXP30 | G3 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1B |

| CPU0_BBC_C_TXN30 | Н3 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1B |

| GND              | 13 |        |        |     |                                                |      |

|------------------|----|--------|--------|-----|------------------------------------------------|------|

| CPU0_BBC_RXP25   | J3 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1A |

| CPU0_BBC_RXN25   | К3 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1A |

| GND              | L3 |        |        |     |                                                |      |

| CPU0_BBC_RXP29   | M3 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1B |

| CPU0_BBC_RXN29   | N3 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1B |

| GND              | 03 |        |        |     |                                                |      |

|                  |    |        |        |     |                                                |      |

| GND              | A4 |        |        |     |                                                |      |

| SATA_C_TX-P3     | B4 | РСН    | O/SATA | Yes | PCH Serial ATA 3 Differential<br>Transmit Pair |      |

| SATA_C_TX-N3     | C4 | РСН    | O/SATA | Yes | PCH Serial ATA 3 Differential<br>Transmit Pair |      |

| GND              | D4 |        |        |     |                                                |      |

| CPU0_BBC_C_TXP27 | E4 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1A |

| CPU0_BBC_C_TXN27 | F4 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1A |

| GND              | G4 |        |        |     |                                                |      |

| CPU0_BBC_C_TXP31 | H4 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1B |

| CPU0_BBC_C_TXN31 | I4 | CPU0   | O/PCIe | Yes | PCIe Transmit Data Output                      | PE1B |

| GND              | J4 |        |        |     |                                                |      |

| CPU0_BBC_RXN24   | K4 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1A |

| CPU0_BBC_RXP24   | L4 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1A |

| GND              | M4 |        |        |     |                                                |      |

| CPU0_BBC_RXP28   | N4 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1B |

| CPU0_BBC_RXN28   | O4 | DEVICE | I/PCIe | No  | PCIe Receive Data Input                        | PE1B |

| GND              | P4 |        |        |     |                                                |      |

|                  |    |        |        |     |                                                |      |

| CPU0_P0_ATT_PWR_<br>LED  | A5 | PCA9555<br>PW  | O/CMOS | N/A | This indicator is connected to the<br>Attention LED or Power LED on<br>the baseboard (PCI Express Hot-<br>Plug Interface)           | PCI-E hot<br>plug |

|--------------------------|----|----------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| CPU0_P0_RRC_RDY_<br>N    | В5 | RRC            | I/CMOS | N/A | Low when switch Ready AND<br>Present AND Power Good                                                                                 | PCI-E hot<br>plug |

| GND                      | C5 |                |        |     |                                                                                                                                     |                   |

| BBC_PCIE-P1              | D5 | РСН            | O/CLK  | N/A | 100 MHz PCIe 3.0 specification compliant differential clock                                                                         |                   |

| BBC_PCIE-N1              | E5 | РСН            | O/CLK  | N/A | 100 MHz PCIe 3.0 specification<br>compliant differential clock                                                                      |                   |

| GND                      | F5 |                |        |     |                                                                                                                                     |                   |

| LS_RRC_PRESENT_N         | G5 | PCIe<br>device | I/CMOS | N/A | Input signal that indicates PCIE device is plugged into the slot                                                                    | PCI-E hot<br>plug |

| Reserved                 | Н5 |                |        |     |                                                                                                                                     |                   |

| GND                      | 15 |                |        |     |                                                                                                                                     |                   |

| Reserved                 | J5 |                |        |     |                                                                                                                                     |                   |

| Reserved                 | K5 |                |        |     |                                                                                                                                     |                   |

| GND                      | L5 |                |        |     |                                                                                                                                     |                   |

| Reserved                 | M5 |                |        |     |                                                                                                                                     |                   |

| Reserved                 | N5 |                |        |     |                                                                                                                                     |                   |

| GND                      | O5 |                |        |     |                                                                                                                                     |                   |

| GND                      | A6 |                |        |     |                                                                                                                                     |                   |

| CPU0_P0_PCIE_RESE<br>T_N | B6 | CPLD           | O/CMOS | N/A | Reset singal for PCIE hot plug device                                                                                               | PCI-E hot<br>plug |

| CPU0_P0_MRL_SW_N         | C6 | PCIe<br>device | I/CMOS | N/A | Manual retention latch status or<br>Electromechanical latch status<br>input indicates that the retention<br>latch is closed or open | PCI-E hot<br>plug |

| GND                      | D6 |                |        |     |                                                                                                                                     |                   |

| Reserved                 | E6 |                |        |     |                                                                                                                                     |                   |

| Reserved                 | F6 |               |        |     |                                                                                                                        |                    |

|--------------------------|----|---------------|--------|-----|------------------------------------------------------------------------------------------------------------------------|--------------------|

| GND                      | G6 |               |        |     |                                                                                                                        |                    |

| Reserved                 | Н6 |               |        |     |                                                                                                                        |                    |

| Reserved                 | 16 |               |        |     |                                                                                                                        |                    |

| GND                      | J6 |               |        |     |                                                                                                                        |                    |

| FC_RX0_L0_P              | K6 | DEVICE        | I/KR   | Yes | Serial Data Input for Ethernet interface                                                                               | Group B,<br>Port 0 |

| FC_RX0_L0_N              | L6 | DEVICE        | I/KR   | Yes | Serial Data Input for Ethernet interface                                                                               | Group B,<br>Port 0 |

| GND                      | M6 |               |        |     |                                                                                                                        |                    |

| Reserved                 | N6 |               |        |     |                                                                                                                        |                    |

| Reserved                 | O6 |               |        |     |                                                                                                                        |                    |

| GND                      | P6 |               |        |     |                                                                                                                        |                    |

|                          |    |               |        |     |                                                                                                                        |                    |

| CPU0_P0_ATT_BUTT<br>ON_N | A7 | RRC<br>board  | I/CMOS | N/A | Input signal per slot which<br>indicates that the user wishes to<br>hot remove or hot add a PCI<br>Express card/module | PCI-E hot<br>plug  |

| CPU0_P0_PWREN            | B7 | PCA9555<br>PW | O/CMOS | N/A | Output signal that indicates power<br>enable for PCIe device                                                           | PCI-E hot<br>plug  |

| GND                      | C7 |               |        |     |                                                                                                                        |                    |

| Reserved                 | D7 |               |        |     |                                                                                                                        |                    |

| Reserved                 | E7 |               |        |     |                                                                                                                        |                    |

| GND                      | F7 |               |        |     |                                                                                                                        |                    |

| Reserved                 | G7 |               |        |     |                                                                                                                        |                    |

| Reserved                 | H7 |               |        |     |                                                                                                                        |                    |

| GND                      | Ι7 |               |        |     |                                                                                                                        |                    |

| Reserved                 | J7 |               |        |     |                                                                                                                        |                    |

| Reserved                 | K7 |               |        |     |                                                                                                                        |                    |

| GND                      | L7 |               |        |     |                                                                                                                        |                    |

| Reserved       | M7 |        |        |     |                    |  |

|----------------|----|--------|--------|-----|--------------------|--|

| Reserved       | N7 |        |        |     |                    |  |

| GND            | 07 |        |        |     |                    |  |

|                |    |        |        |     |                    |  |

| GND            | A8 |        |        |     |                    |  |

| LS_I2C_ALERT_N | B8 | DEVICE | I/CMOS | N/A | SMBus Alert to PCH |  |

| Reserved       | C8 |        |        |     |                    |  |

| GND            | D8 |        |        |     |                    |  |

| Reserved       | E8 |        |        |     |                    |  |

| Reserved       | F8 |        |        |     |                    |  |

| GND            | G8 |        |        |     |                    |  |

| Reserved       | H8 |        |        |     |                    |  |

| Reserved       | 18 |        |        |     |                    |  |

| GND            | J8 |        |        |     |                    |  |

| Reserved       | K8 |        |        |     |                    |  |

| Reserved       | L8 |        |        |     |                    |  |

| GND            | M8 |        |        |     |                    |  |

| Reserved       | N8 |        |        |     |                    |  |

| Reserved       | 08 |        |        |     |                    |  |

| GND            | Р8 |        |        |     |                    |  |

|                |    |        |        |     |                    |  |

| BBC_SMB_L_CLK  | A9 | РСН    | IO/I2C | N/A | PCH I2C bus        |  |

| BBC_SMB_L_DAT  | В9 | РСН    | IO/I2C | N/A | PCH I2C bus        |  |

| GND            | С9 |        |        |     |                    |  |

| Reserved       | D9 |        |        |     |                    |  |

| Reserved       | Е9 |        |        |     |                    |  |

| GND                 | F9  |      |        |     |                                    |  |

|---------------------|-----|------|--------|-----|------------------------------------|--|

| Reserved            | G9  |      |        |     |                                    |  |

| Reserved            | Н9  |      |        |     |                                    |  |

| GND                 | 19  |      |        |     |                                    |  |

| Reserved            | J9  |      |        |     |                                    |  |

| Reserved            | К9  |      |        |     |                                    |  |

| GND                 | L9  |      |        |     |                                    |  |

| Reserved            | M9  |      |        |     |                                    |  |

| Reserved            | N9  |      |        |     |                                    |  |

| GND                 | 09  |      |        |     |                                    |  |

|                     |     |      |        |     |                                    |  |

| GND                 | A10 |      |        |     |                                    |  |

| IPMB_CLK_B          | B10 | BMC  | IO/I2C | N/A | IPMB I2C Bus                       |  |

| IPMB_DAT_B          | C10 | BMC  | IO/I2C | N/A | IPMB I2C Bus                       |  |

| GND                 | D10 |      |        |     |                                    |  |

| Reserved            | E10 |      |        |     |                                    |  |

| Reserved            | F10 |      |        |     |                                    |  |

| GND                 | G10 |      |        |     |                                    |  |

| Reserved            | H10 |      |        |     |                                    |  |

| Reserved for hybrid | I10 |      |        |     |                                    |  |

| GND                 | J10 |      |        |     |                                    |  |

| PCIE_SCL_CN_L       | K10 | BMC  | IO/I2C | N/A | BMC I2C bus                        |  |

| PCIE_SDA_CN_L       | L10 | BMC  | IO/I2C | N/A | BMC I2C bus                        |  |

| GND                 | M10 |      |        |     |                                    |  |

| BUF_SLPS5_N         | N10 | CPLD | 0      | N/A | SLP_S5# is for power plane control |  |

| BBC_RST_N           | O10 | РСН  | O/P3V3 | N/A | Platform Reset                     |  |

|--|

The signal connector (CN35) includes serval groups of PCIex1 Gen3 lanes and NC-SI for implementing IPMI-based device management net. The pin definitions of CN37 is shown in table 4.

Table 4. The Pin Definitions of B2B Signal Connector CN37

| Net name      | Pin | Drive | IO/Signal<br>Type | AC Cap<br>on board | Description    | Group |

|---------------|-----|-------|-------------------|--------------------|----------------|-------|

| Reserved      | A1  |       |                   |                    |                |       |

| Reserved      | B1  |       |                   |                    |                |       |

| GND           | C1  |       |                   |                    |                |       |

| Reserved      | D1  |       |                   |                    |                |       |

| Reserved      | E1  |       |                   |                    |                |       |

| GND           | F1  |       |                   |                    |                |       |

| Reserved      | G1  |       |                   |                    |                |       |

| Reserved      | H1  |       |                   |                    |                |       |

| GND           | I1  |       |                   |                    |                |       |

| PLTRST_DEV2-L | J1  | РСН   | O/P3V3            | N/A                | Platform Reset | MISC  |

| Reserved      | K1  |       |                   |                    |                |       |

| GND           | L1  |       |                   |                    |                |       |

| Reserved      | M1  |       |                   |                    |                |       |

| Reserved      | N1  |       |                   |                    |                |       |

| GND           | 01  |       |                   |                    |                |       |

|               |     |       |                   |                    |                |       |

| GND           | A2  |       |                   |                    |                |       |

| Reserved      | B2  |       |                   |                    |                |       |

| Reserved      | C2  |       |                   |                    |                |       |

| GND           | D2  |       |                   |                    |                |       |

| Reserved | E2 |  |  |

|----------|----|--|--|

| Reserved | F2 |  |  |

| GND      | G2 |  |  |

| Reserved | H2 |  |  |

| Reserved | 12 |  |  |

| GND      | J2 |  |  |

| Reserved | К2 |  |  |

| Reserved | L2 |  |  |

| GND      | M2 |  |  |

| Reserved | N2 |  |  |

| Reserved | 02 |  |  |

| GND      | P2 |  |  |

|          |    |  |  |

| Reserved | A3 |  |  |

| Reserved | B3 |  |  |

| GND      | C3 |  |  |

| Reserved | D3 |  |  |

| Reserved | E3 |  |  |

| GND      | F3 |  |  |

| Reserved | G3 |  |  |

| Reserved | Н3 |  |  |

| GND      | 13 |  |  |

| Reserved | J3 |  |  |

| Reserved | К3 |  |  |

| GND      | L3 |  |  |

| Reserved | M3 |  |  |

| Г              |    |     | 1     |     |                                                             | 1     |

|----------------|----|-----|-------|-----|-------------------------------------------------------------|-------|

| Reserved       | N3 |     |       |     |                                                             |       |

| GND            | 03 |     |       |     |                                                             |       |

|                |    |     |       |     |                                                             |       |

| GND            | A4 |     |       |     |                                                             |       |

| Reserved       | B4 |     |       |     |                                                             |       |

| Reserved       | C4 |     |       |     |                                                             |       |

| GND            | D4 |     |       |     |                                                             |       |

| Reserved       | E4 |     |       |     |                                                             |       |

| Reserved       | F4 |     |       |     |                                                             |       |

| GND            | G4 |     |       |     |                                                             |       |

| Reserved       | H4 |     |       |     |                                                             |       |

| Reserved       | I4 |     |       |     |                                                             |       |

| GND            | J4 |     |       |     |                                                             |       |

| CSA_LAN1_CLK-P | K4 | РСН | O/CLK | N/A | 100 MHz PCIe 3.0 specification compliant differential clock | CLOCK |

| CSA_LAN1_CLK-N | L4 | РСН | O/CLK | N/A | 100 MHz PCIe 3.0 specification compliant differential clock | CLOCK |

| GND            | M4 |     |       |     |                                                             |       |

| Reserved       | N4 |     |       |     |                                                             |       |

| Reserved       | 04 |     |       |     |                                                             |       |

| GND            | P4 |     |       |     |                                                             |       |

|                |    |     |       |     |                                                             |       |

| Reserved       | A5 |     |       |     |                                                             |       |

| Reserved       | B5 |     |       |     |                                                             |       |

| GND            | C5 |     |       |     |                                                             |       |

| Reserved       | D5 |     |       |     |                                                             |       |

| Reserved       | E5 |     |       |     |                                                             |       |

| GND            | F5        |                        |       |     |                                                             |       |

|----------------|-----------|------------------------|-------|-----|-------------------------------------------------------------|-------|

| Reserved       | G5        |                        |       |     |                                                             |       |

| Reserved       | Н5        |                        |       |     |                                                             |       |

| GND            | 15        |                        |       |     |                                                             |       |

| CSA_LAN2_CLK-N | J5        | РСН                    | O/CLK | N/A | 100 MHz PCIe 3.0 specification compliant differential clock | CLOCK |

| CSA_LAN2_CLK-P | К5        | РСН                    | O/CLK | N/A | 100 MHz PCIe 3.0 specification compliant differential clock | CLOCK |

| GND            | L5        |                        |       |     |                                                             |       |

| Reserved       | M5        |                        |       |     |                                                             |       |

| Reserved       | N5        |                        |       |     |                                                             |       |

| GND            | 05        |                        |       |     |                                                             |       |

|                |           |                        |       |     |                                                             |       |

| GND            | A6        |                        |       |     |                                                             |       |

| C_RMII_RXD0    | <b>B6</b> | Ethernet controller    | 0     | N/A | Receive Data                                                | NC-SI |

| Reserved       | C6        |                        |       |     |                                                             |       |

| GND            | D6        |                        |       |     |                                                             |       |

| C_NCSI_ARB_IN  | E6        | Ethernet controller    | Ι     | N/A | Hardware Arbitration Input                                  | NC-SI |

| Reserved       | F6        |                        |       |     |                                                             |       |

| GND            | G6        |                        |       |     |                                                             |       |

| C_NCSI_ARB_OUT | H6        | Ethernet<br>controller | 0     | N/A | Hardware Arbitration Output                                 | NC-SI |

| C_LAN4_50M_CLK | 16        | Clock<br>buffer        | O/CLK | N/A | Reference Clock                                             | NC-SI |

| GND            | J6        |                        |       |     |                                                             |       |

| Reserved       | K6        |                        |       |     |                                                             |       |

| Reserved       | L6        |                        |       |     |                                                             |       |

| GND                        | M6         |                     |           |     |                                          |        |

|----------------------------|------------|---------------------|-----------|-----|------------------------------------------|--------|

| Reserved                   | N6         |                     |           |     |                                          |        |

| Reserved                   | <b>O</b> 6 |                     |           |     |                                          |        |

| GND                        | P6         |                     |           |     |                                          |        |

|                            |            |                     |           |     |                                          |        |

| C_RMII_IPMC_NIC_T<br>XD1   | A7         | BMC                 | Ι         | N/A | Transmit Data                            | NC-SI  |

| Reserved                   | B7         |                     |           |     |                                          |        |

| GND                        | C7         |                     |           |     |                                          |        |

| C_RMII_NIC_IPMC_C<br>RS_DV | D7         | Ethernet controller | O/P3V3_SB | N/A | Carrier Sense/Receive Data<br>Valid      | NC-SI  |

| C_RMII_IPMC_NIC_T<br>XD0   | E7         | BMC                 | Ι         | N/A | Transmit Data                            | NC-SI  |

| GND                        | F7         |                     |           |     |                                          |        |

| Reserved                   | G7         |                     |           |     |                                          |        |

| Reserved                   | H7         |                     |           |     |                                          |        |

| GND                        | 17         |                     |           |     |                                          |        |

| CSA_LAN2_C_RXP             | J7         | DEVICE              | I/PCIE    | No  | PCI Express Differential<br>Receive Pair | PORT 8 |

| CSA_LAN2_C_RXN             | K7         | DEVICE              | I/PCIE    | No  | PCI Express Differential<br>Receive Pair | PORT 8 |

| GND                        | L7         |                     |           |     |                                          |        |

| Reserved                   | M7         |                     |           |     |                                          |        |

| Reserved                   | N7         |                     |           |     |                                          |        |

| GND                        | 07         |                     |           |     |                                          |        |

|                            |            |                     |           |     |                                          |        |

| GND                        | A8         |                     |           |     |                                          |        |

| C_RMII_RXD1                | B8         | Ethernet controller | 0         | N/A | Receive Data                             | NC-SI  |

| C_RMII_IPMC_NIC_T<br>X_EN | C8        | BMC    | Ι          | N/A | Transmit Enable                           | NC-SI  |

|---------------------------|-----------|--------|------------|-----|-------------------------------------------|--------|

| GND                       | D8        |        |            |     |                                           |        |

| Reserved                  | E8        |        |            |     |                                           |        |

| Reserved                  | F8        |        |            |     |                                           |        |

| GND                       | <b>G8</b> |        |            |     |                                           |        |

| CSA_VGA_C_TXN             | H8        | РСН    | O/PCIE     | Yes | PCI Express Differential<br>Transmit Pair | PORT 3 |

| CSA_VGA_C_TXP             | 18        | РСН    | O/PCIE     | Yes | PCI Express Differential<br>Transmit Pair | PORT 3 |

| GND                       | J8        |        |            |     |                                           |        |

| CSA_LAN1_C_RXP            | K8        | DEVICE | O/PCIE     | No  | PCI Express Differential<br>Receive Pair  | PORT 7 |

| CSA_LAN1_C_RXN            | L8        | DEVICE | O/PCIE     | No  | PCI Express Differential<br>Receive Pair  | PORT 7 |

| GND                       | M8        |        |            |     |                                           |        |

| Reserved                  | N8        |        |            |     |                                           |        |

| Reserved                  | 08        |        |            |     |                                           |        |

| GND                       | P8        |        |            |     |                                           |        |

| CSA_I2CCLK                | A9        | BMC    | O/P3V3_SB  | N/A | I2C bus                                   | I2C    |

| CSA_I2CDAT                | B9        | BMC    | IO/P3V3_SB | N/A | I2C bus                                   | I2C    |

| GND                       | С9        |        |            |     |                                           |        |

| Reserved                  | D9        |        |            |     |                                           |        |

| Reserved                  | E9        |        |            |     |                                           |        |

| GND                       | F9        |        |            |     |                                           |        |

| Reserved                  | G9        |        |            |     |                                           |        |

| Reserved                  | Н9        |        |            |     |                                           |        |

| GND                       | 19        |        |            |     |                                           |        |

| CSA_LAN1_C_TXN | J9  | РСН | O/PCIE | Yes | PCI Express Differential<br>Transmit Pair | PORT 7 |

|----------------|-----|-----|--------|-----|-------------------------------------------|--------|

| CSA_LAN1_C_TXP | К9  | РСН | O/PCIE | Yes | To MICA-5200                              | PORT 7 |

| GND            | L9  |     |        |     |                                           |        |

| Reserved       | M9  |     |        |     |                                           |        |

| Reserved       | N9  |     |        |     |                                           |        |

| GND            | 09  |     |        |     |                                           |        |

|                |     |     |        |     |                                           |        |

| GND            | A10 |     |        |     |                                           |        |

| Reserved       | B10 |     |        |     |                                           |        |

| Reserved       | C10 |     |        |     |                                           |        |

| GND            | D10 |     |        |     |                                           |        |

| Reserved       | E10 |     |        |     |                                           |        |

| Reserved       | F10 |     |        |     |                                           |        |

| GND            | G10 |     |        |     |                                           |        |

| CSA_LAN2_C_TXP | H10 | РСН | O/PCIE | Yes | PCI Express Differential<br>Transmit Pair | PORT 8 |

| CSA_LAN2_C_TXN | I10 | РСН | O/PCIE | Yes | PCI Express Differential<br>Transmit Pair | PORT 8 |

| GND            | J10 |     |        |     |                                           |        |

| Reserved       | K10 |     |        |     |                                           |        |

| Reserved       | L10 |     |        |     |                                           |        |

| GND            | M10 |     |        |     |                                           |        |

| Reserved       | N10 |     |        |     |                                           |        |

| Reserved       | O10 |     |        |     |                                           |        |

| GND            | P10 |     |        |     |                                           |        |

#### **10.2 B2B Power Connector**

The mezzanine card uses two pair of FCI Airmax 2x2 R/A power connectors (P/N: 10052620) for power delivery from Mezzanine card to compute sled. The pin definitions are described in the table 5.

| Net name | Pin | Description                    | Group  |  |

|----------|-----|--------------------------------|--------|--|

| P12V     | A1  |                                |        |  |

| P12V     | B1  |                                |        |  |

| P12V     | C1  | P12V power rail from backplane | Power  |  |

| P12V     | A2  | to motherboard                 | rowei  |  |

| P12V     | B2  |                                |        |  |

| P12V     | C2  |                                |        |  |

| GND      | A3  |                                |        |  |

| GND      | B3  |                                |        |  |

| GND      | С3  | Ground return                  | Ground |  |

| GND      | A4  |                                | Ground |  |

| GND      | B4  |                                |        |  |

| GND      | C4  |                                |        |  |

#### Table 5. The pin definitions of power connectors

#### 10.3 B2B Guide Pin

The compute server and mezzanine card uses one pair of FCI Airmax 10.8mm R/A guide pin (P/N: 10044366) to achieve blind mating.

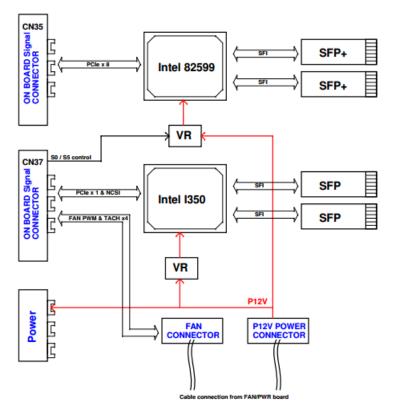

#### 10.4 10G Mezzanine Card Example

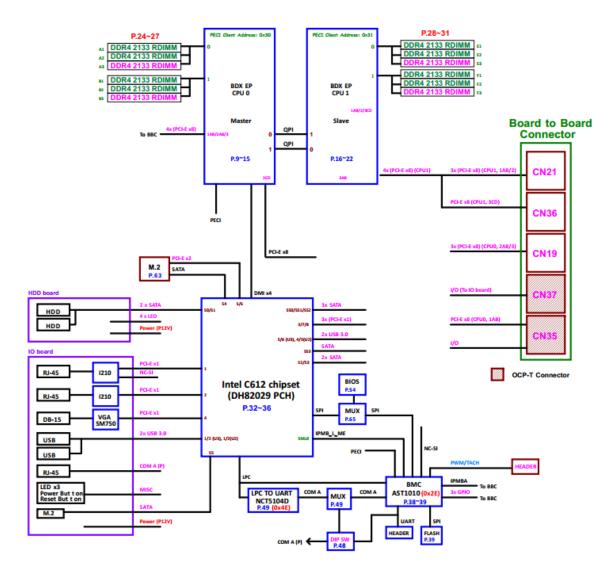

The block diagram in Figure 12 illustrates the design of a 10G mezzanine card. One Intel 82599 is used to implement the primary and secondary 10G data links. One Intel I350 with NC-SI interface is used to implement the 1GbE IPMI-based device management link and 1GbE application management link. The optical links are routed to the optical connector placement on the rear of the shelf.

The power supply to Intel 82599 is disabled when the computing board enters ACPI S0/S5 state. In order to provide out-of-band management, the power supply to Intel I350 is always enabled.

Figure 13. Block Diagram of 10G Mezzanine Card

# **11 Compute Zone Specifications**

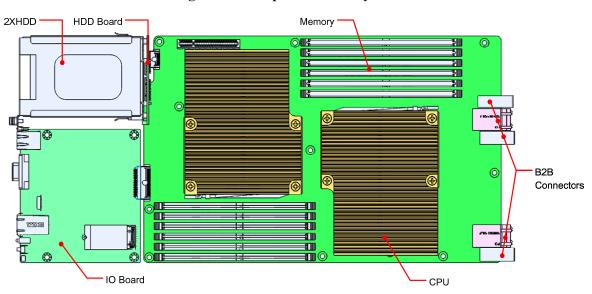

Zone 5 defines for the Open POD for the Compute, Memory, Storage and optional NIC front panel interface. Zone 5 is located in the front half of the Open POD and allocates 440mm(L) x 215mm(W) and 84mm (2U) (H) space.

The Compute zone is dedicated to specific CPU, BMC Management; front and rear connections enabling a wide range of applications that is specific to the required use case. Appendix.14.3 provides an example of the Zone 5 configuration which is based on the ADLINK Modular Industrial Cloud Architecture MCN-2600 CPU Sled.

Zone 5 Compute area includes (but not limited to):

- Stackable Compute boards based on X86 architecture

- ARM, ASIC, FPGA, etc Silicon architectures

- Memory

- Storage (HDD or SDD)

- Network Interface Controller (NIC)

- Interfaces to Mezzanine Zone, Storage and NIC

- System level management functions via BMC chipsets

- Power and storage management

- Front panel options if required

Zone 5 Compute area can be comprised of two stackable CPU boards providing a dense compute module in a 2U  $\frac{1}{2}$  width Pod. Each CPU board has the ability to connect to multiple storage devices initially, and expand to all storage sleds that can be used as storage pods.

This specification provides the internal connections between the CPU, Storage, Optional Network Interface, and Mezzanine card. Included in this section is the On-Board Management functions required to manage the CPU, Power, and Fans via IPMI 2.0 and a Board Management Controller (BMC).

Appendix 14.3 provides the specification of ADLINK's 2600-based CPU motherboard as a reference for Zone 5 CPU design.

Additional option for discussion with Radisys and Project team:

- Enable the ability for the sled to slide in and out from the front panel

- Allow rails to be installed on the sides to allow two sleds to slide into the front panel

- The rear guide pin assembly will enable the connections between the Zone 4 Mezzanine card and Zone 5 server sled.

- Ability to lock and latch the Zone 5 Server sled for improved shock/vibration protection

- Front panel to be hinged or removable to enable sleds to be inserted

#### B2B Connectors

The compute board shall use the following components to implement the board to board connection with mezzanine card.

- B2B signal connector: The compute board shall implement two signal connectors as described in Section 10.1, and connector type shall use FCI Airmax VSe connector (P/N: 10115913).

- B2B power connector: The compute board shall implement two power connectors as described in Section 10.2 and the connector type shall use FCI Airmax 2x2 R/A power connector (P/N: 10028917).

- B2B guide pin: The compute board shall implement one guide pin, and the connector type shall use FCI Airmax 10.8mm R/A guide receptacle module (P/N: 10037912).

#### **11.1 Power System**

The compute board takes its +12V power from the B2B power as mentioned above. The +12V power are transferred into the required voltages on the motherboard. The power supply on the motherboard is also divided into two different power domains.

The main power domain includes the main components to the host, like CPU, memory, Hard disk, PCIe interface, and so on. The main power is enabled when the user switch on the power on through a front plane button or send a "Chassis Control (Power on)" command to BMC via its IPMB or LAN interface.

The standby power domain includes BMC, NC-SI network cards, and PCH to enable out of band IPMI based management, and power button startup. The standby power domain is always enabled if the power supply is alive.

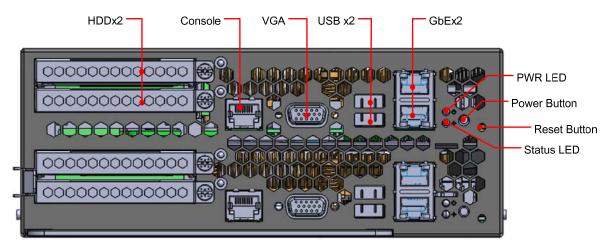

# **11.2 Front Panel**

There can be two server boards in an OpenPOD server, and each server shall have a front plane interface with the following required functionalities.

- Power button: The user can trigger a graceful shutdown of the operation system if pushing the button less than 4 seconds. The user can trigger a forceful shutdown of the operation system if pushing the button longer than 4 seconds.

- Reset button: The user can trigger a cold reset of the motherboard by pushing the invaginate reset button.

- Power LED: The power LED is green and controlled by hardware directly. The LED is on when main power is enabled, and the LED is off when main power is disabled.

- Status LED: The status LED is red/green dual-color LED and controlled by BMC. The red color is used to indicate BIOS post status. The green color is used to indicate system status after BIOS post, can be connected with the BMC watchdog status. The BMC also implements an OEM command to let the user control the green LED via IPMI command.

Optionally they can provide the following interfaces.

• GeE interface: The GeE interface can be used for local debugging in the development phase.

### CG-OpenRack-19 · Half-Width OpenPOD Server Specification

- USB interface: The USB interface is provided to install the mouse and keyboard.

- VGA interface: It benefits when local GUI is required.

- Console interface: It benefits when the user wants to access the system via a serial port.

- HDD bay: Hot-swappable HDD bay can be implemented to provide local storage.

Figure 14. Front Panel Interface of Compute sled

# 11.3 Basic Input Output System (BIOS)

The motherboard BIOS shall be customized to improve the power efficiency. The measures include:

- CPU Power Technology is set to "Energy Efficient"

- CPU EIST is enabled

### 11.3.1 Setup Menu

The BIOS setup utility shall provide the following setup screen.

- Main BIOS setup screen: BIOS Vendor, Core Version, Motherboard Name, BIOS Build Time, System Language, System Date, and System Time.

- Advanced BIOS setup screen: Board Automatic Power-up Configuration, ACPI Configuration, Super IO Configuration, Serial Port Console Redirection, iSCSI Configuration, PCIe SR-IOV Support, PXE boot Configuration, BMC Watchdog Configuration, LAN Bypass Configuration.

- Intel RefCode Setup screen: Processor Configuration, Advanced Power Management Configuration, Common RefCode Configuration, Memory Configuration, IIO Configuration, PCH Configuration.

- Server Management setup screen: BMC Firmware Revision, and BMC Watchdog Configuration.

- Security setup screen: Administered Password, User Password, and HDD Security Configuration.

- Boot setup screen: Setup Prompt Timeout, Bootup NumLock State, Quiet Boot Configuration, and Boot Option Priorities.

### 11.3.2 Post Error Code

| Error Code | Description                                                                      |

|------------|----------------------------------------------------------------------------------|

| 0x50       | Memory initialization error. Invalid memory type or incompatible memory speed    |

| 0x51       | Memory initialization error. SPD reading has failed                              |

| 0x52       | Memory initialization error. Invalid memory size or memory modules do not match. |

| 0x53       | Memory initialization error. No usable memory detected                           |

| 0x54       | Unspecified memory initialization error.                                         |

| 0x55       | Memory not installed                                                             |

| 0x56       | Invalid CPU type or Speed                                                        |

| 0x57       | CPU mismatch                                                                     |

| 0x58       | CPU self test failed or possible CPU cache error                                 |

| 0x59       | CPU micro-code is not found or micro-code update is failed                       |

| 0x5A       | Internal CPU error                                                               |

| 0x5B       | Reset PPI is not available                                                       |

|            |                                                                                  |

| 0xD0       | CPU initialization error                                                         |

| 0xD1       | North Bridge initialization error                                                |

| 0xD2       | South Bridge initialization error                                                |

| 0xD3       | Some of the Architectural Protocols are not available                            |

| 0xD4       | PCI resource allocation error. Out of Resources                                  |

| 0xD5       | No Space for Legacy Option ROM                                                   |

Table 6. BIOS POST Error Codes and Interpretation

| 0xD6 | No Console Output Devices are found                  |

|------|------------------------------------------------------|

| 0xD7 | No Console Input Devices are found                   |

| 0xD8 | Invalid password                                     |

| 0xD9 | Error loading Boot Option (LoadImage returned error) |

| 0xDA | Boot Option is failed (StartImage returned error)    |

| 0xDB | Flash update is failed                               |

| 0xDC | Reset protocol is not available                      |

|      |                                                      |

| 0xE8 | S3 Resume Failed                                     |

| 0xE9 | S3 Resume PPI not Found                              |

| 0xEA | S3 Resume Boot Script Error                          |

| 0xEB | S3 OS Wake Error                                     |

# 11.4 Baseboard Management Controller (BMC)

The BMC shall work as a standalone system, providing out-of-band IPMI management service that is not dependent on the health status of the host. The BMC is responsible to monitor the thermal situation of the board and control the fan speed adaptively, and as well as provide remote control for the x86 system.

# 11.4.1 LAN Interface

The BMC shall provide LAN accessing via the NC-SI interface built on the host network cards. And the host network cards are be powered from the standby power, and it can work even if the host is powered down (main power is cut off).

If the motherboard has more than one NC-SI packages. By default the IPMI LAN interface shall be directed to the 1G port on the rear optical connector. Optionally, the user can direct the IPMI LAN interface to the 1G GbE interface on the front panel via sending IPMI command to BMC.

### 11.4.2 Serial Over LAN (SOL)

Because a GUI interface does not scale, the BMC does not require supporting the graphic-based iKVM feature, instead the BMC shall provide the text-based Serial Over LAN (SOL) feature. With SOL

redirection system administrators can remotely view the text-based host console from anywhere and perform any task that doesn't require a GUI.

### 11.4.3 Power Monitoring and Controlling

The BMC shall support power monitoring through the hot-swap controller, and a current sensor shall be implemented to provide real-time power consumption of the motherboard. A series of voltage sensors shall also be implemented to monitor the key power rails on the motherboard.

The BMC shall support power on/off/cycle and cold/warm reset the host system through out-of-band IPMI commands. Use can execute a host recovery action by triggering the power control regardless of the host operation status.

The BMC can optionally enable the Intel Node Manager power limiting function. The user can enforce a power limit policy by bridging Intel Node Manager Commands to the Intel Management Engine (ME) via BMC.

### 11.4.4 Fan Speeding and Connector

The BMC shall implement a series of temperature sensors to monitor the thermal situation of the key components in the motherboard, including inlet air temperature, CPU, DIMM and PCH. When BMC works in a single board system, based on the aggregated thermal situation, the BMC will run the FAN based on an adaptive speeding algorithm.

When there are no thermal alarms, the BMC will run the FAN at a miniLevel speed, and the miniLevel speed is decided monotonously based on the inlet air temperature. A higher inlet air temperature will generate a higher miniLevel speed. When there are thermal alarms, the BMC will increase the FAN speed to eliminate the thermal alarms. The higher the thermal alarm level is, the faster the BMC increases the FAN speed, until the FANs reach their largest speed. After all thermal alarms are eliminated, the BMC will return the FAN speed gradually to a miniLevel, which is calculated based on the current inlet air temperature.

The BMC shall also implement tachometers to monitor the fan speed and OEM command to fix the fan speed.

#### 11.4.5 IPMI Sensors

The BMC can optional implement a serial of logical sensors to respect the operation status of the whole system. User can check the sensor reading or Sensor Event Log (SEL) to determine whether the system is running properly.

#### 11.4.6 System Event Log (SEL)

The BMC supports shall support Sensor Event Log (SEL) with a size larger than 10 KB. The BMC uses circular SEL type, and the SEL repository acts like a ring buffer. When the repository becomes full, oldest logs are overwritten by new logs.

# **12 Environmental Specifications**

The OpenPOD server shall meet the following environmental requirements:

- Operating temperature:  $0 \degree C \sim +40 \degree C$

- Short term operating: -5°C to +45°C, 5%-90% relative humidity

- Storage temperature: -40 °C~+70 °C

- Operating humidity:  $20\% \sim 90\%$ RH@40°C, non-condensing

- Non-operating: 5%-90% relative humidity

- EMI: NEBS Level-3 compliance, FCC class A, CE emission, CCC, UL, CB and RoHS compliant

# 13 Shock & Vibration