# Open. Together.

Consume. Collaborate. Contribute.

### **Open Domain Specific Architecture:** The Impact of ODSA

**By:** Bapi Vinnakota – OCP ODSA Sub-Project Lead Kevin Drucker – Facebook ODSA Lead

Consume. Collaborate. Contribute.

#### The Impact of Open Domain Specific Architecture (ODSA) Agenda

- Background on the Open Compute Project

- Open Domain Specific Architecture (ODSA) Sub-Project

- Drivers for Domain Specific Architectures

- Evolution of the industry

- Chiplet and SIP use cases

- Market Opportunity

- ODSA Collaboration

## **ODSA: Open Domain-Specific Architecture**

- Domain-specific architecture: Programmable devices optimized for specific applications or class of applications. Meet the demands of high-intensity workloads in the data center and at the edge – e.g. machine learning, video processing

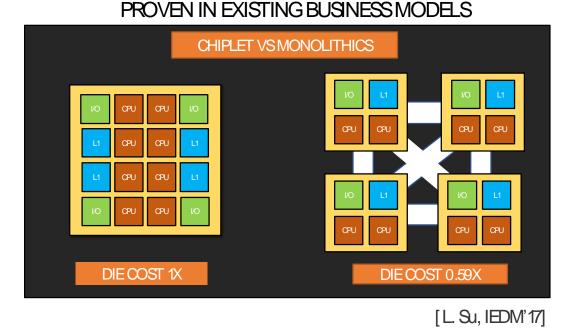

- Chiplets: Implement an integrated product as a <u>collection</u> of die in a single package, instead of a single die. Each die is a chiplet. Can reduce development and manufacturing costs.

#### The Impact of Open Domain Specific Architecture (ODSA) History of Open Compute Project (OCP)

- In 2009 Facebook, confronting exponential growth, was forced to rethink infrastructure architecture

- Small team of engineers spent next two years reenvisioning and designing software, servers, racks, power supplies, cooling and data center design

- In 2011 Facebook shared it's designs and released them to the public

- Along with Intel, Rackspace, Goldman Sachs and Andy Becholtsheim, the Open Compute Project (OCP) was launched and the Open Compute Project Foundation created

- Today, OCP has grown into a massive global community with over 150 member companies

#### The Impact of Open Domain Specific Architecture (ODSA) ODSA within OCP: A new Server Sub-Project)

- ODSA organized within the Open Compute Project (OCP):

- ODSA aligned as OCP Server sub-project

- Initial concept brought to OCP by Netronome

- First silicon focused effort within OCP

- Extending Moore's Law:

- Domain-Specific Architectures: Typically programmable silicon products that accelerate high-intensity workloads (e.g. Tensorflow, Network Processor, Antminer...)

- Chiplets / SIPs go beyond MCM → Build complex products from multiple die, instead of monolithic devices, to reduce TTM, R&D expense and manufacturing costs.

- Open Domain-Specific Architecture: An architecture for a domain-specific products

- Today: All multi-chiplet products are based on proprietary interfaces

- Tomorrow: Select best-of-breed chiplets from multiple vendors

- Incubating a new group, to define a new open interface and standards to build a PoC

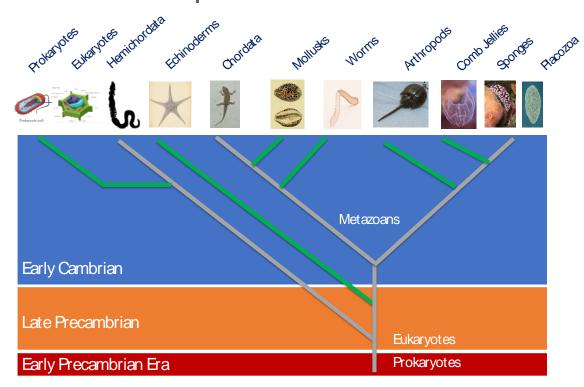

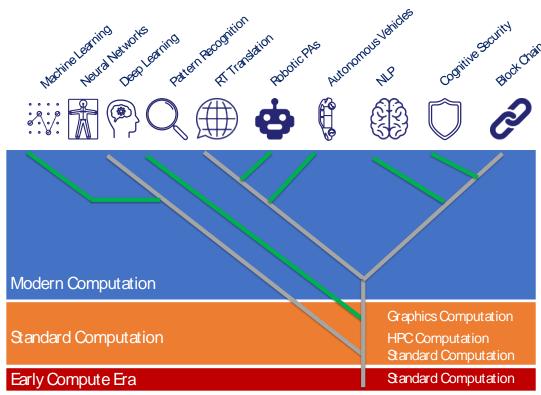

#### The Impact of Open Domain Specific Architecture (ODSA) Cambrian Explosion of Workloads

Bio-Diversity Exploded from single cells into multi-cell organisms during the Cambrian explosion; all major phylla were established in this transition

Al and Machine-learning and data-heavy workloads have exploded in past 5 years and will diversify as new applications are discovered constantly...

All images from Creative Commons

#### The Impact of Open Domain Specific Architecture (ODSA) Chiplet and SIP Technology Is Happening Today!

- Many major semiconductor companies have brought to market chiplet / SIP based products

- Developed using hybrid flows of internally developed tools and EDA industry available point solution

- ODSA seeks to enable internally developed and 3rd party chiplets to be readily integrated

- ODSA seeks to democratize this evolution of chiplet and SIP technology for the larger mass market through an open eco-system marketplace

- Focus on three (3) use cases:

- IO Disaggregation, Core Disaggregation, System Integration

## The Impact of Open Domain Specific Architecture (ODSA)

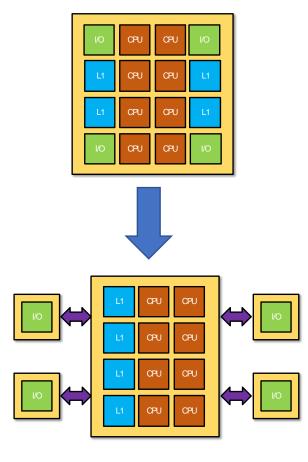

Major Chiplet / System in a Package (SIP) use cases: IO Disaggregation

- Use case: IO Disaggregation

- What:

- Separating core and un-core

- High speed IO Interfaces moved to chiplets

- Ex: PCIe I/F, Memory I/F, Network I/F

- Why:

- Focus resources on value added core functions

- Reduce development and qual intervals  $\rightarrow$  shorter TTM

- PPA: Target IP / Core to process nodes that yield highest Performance, Power, Area for a given function

#### The Impact of Open Domain Specific Architecture (ODSA) Major Chiplet / System in a Package (SIP) use cases: Logic Disaggregation

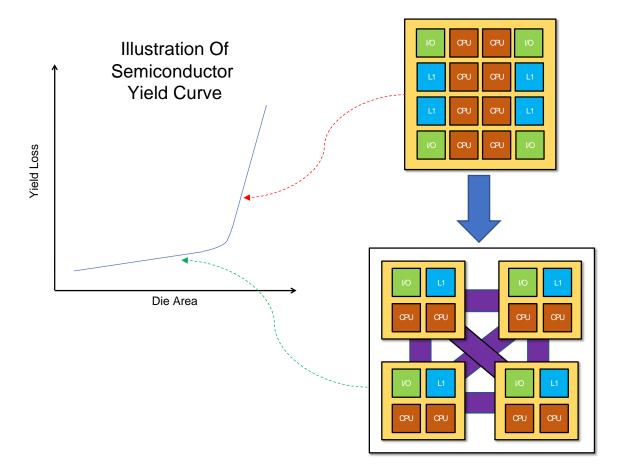

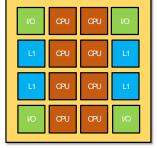

- Use case: Logic Disaggregation

- What:

- Sub-divide large area of monolithic low yield device into multiple lower area / higher yielding devices

- Why:

- Shift final product from costly, nonlinear portion of semiconductor yield curve to lower-cost, higher yielding linear portion

#### The Impact of Open Domain Specific Architecture (ODSA) Major Chiplet / System in a Package (SIP) use cases: Combined

- Optimize for process node vs. PPA →Select the best node for the given function

- Maximize yield curve for linear intercepts

- Amortize cost of development and qualification of the chiplets and reuse them for subsequent products

- Combine with known good die chiplets (KGD) from 3rd parties

## The Impact of Open Domain Specific Architecture (ODSA)

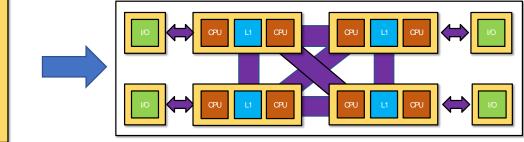

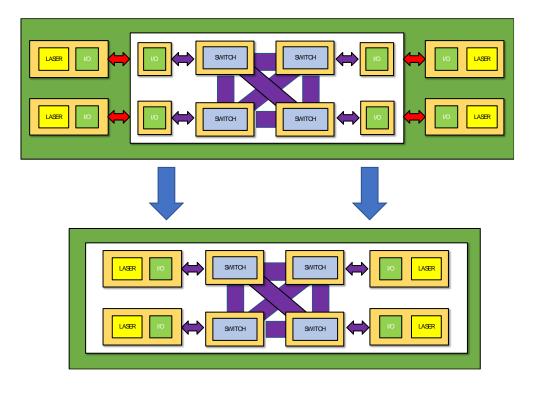

Major Chiplet / System in a Package (SIP) use cases: System Integration

- Use case: System Integration

- What:

- Integrate multiple SoCs and components into a single SIP package

- Obtain KGD from multiple 3rd party suppliers

- Ex: co-packaged optics and switch

- Why:

- Significant system footprint reduction

- IO power reduction: driving inches of PCB vs.

mm of substrate → mJ → pJ

- Huge win @ scale: even 5W ~ 10W savings power system adds up to MW savings

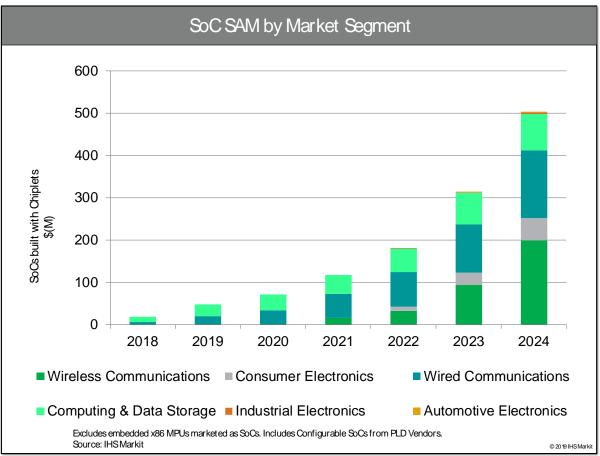

#### The Impact of Open Domain Specific Architecture (ODSA) Transformative Market Opportunity: The Tip of the Spear

- Independent research from IHS Markit

- Four (4) segments for chiplets analyzed (SoCs, MPU, GPU, PLD (FPGA/CPLDs)

- Six Verticals (wireless, wireline, consumer, computing, industrial, automotive)

Subset of IHS Markit Data:System on a Chip (SoC) segment

• **Conclusion**: Immediate opportunity for chiplets and an open interface

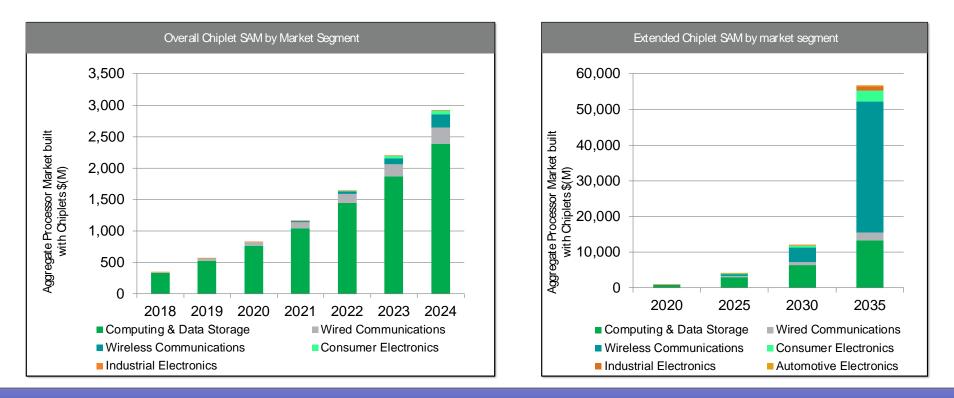

#### The Impact of Open Domain Specific Architecture (ODSA) Transformative Market Opportunity: The End Game

- Initially dominated by compute uses case, other market segments grow to dominate

- **Takeaway**: an open chiplet eco-system with open interface standards is a huge opportunity

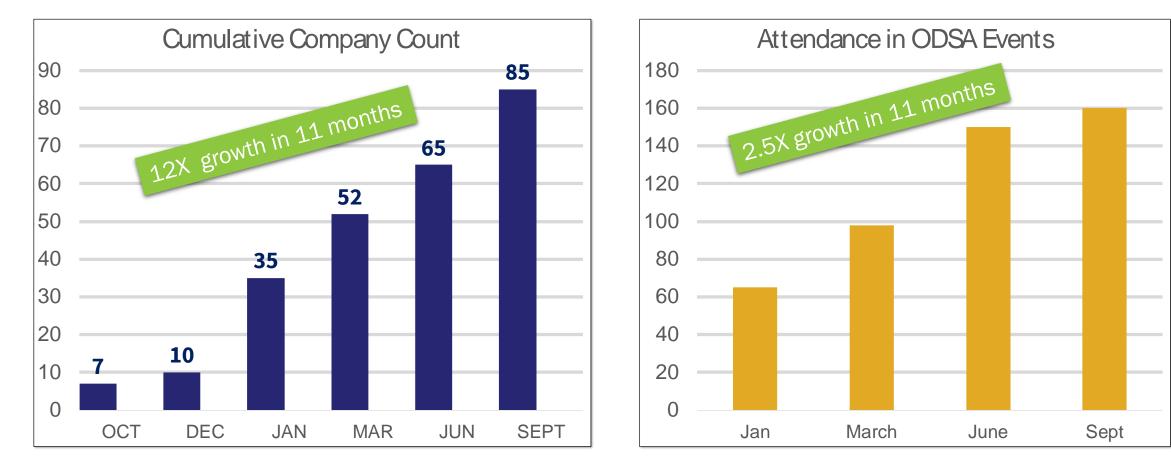

#### The Impact of Open Domain Specific Architecture (ODSA) Growth of ODSA since Inception

#### Source: OCPODSAS.rvey, Workshop Registration Data

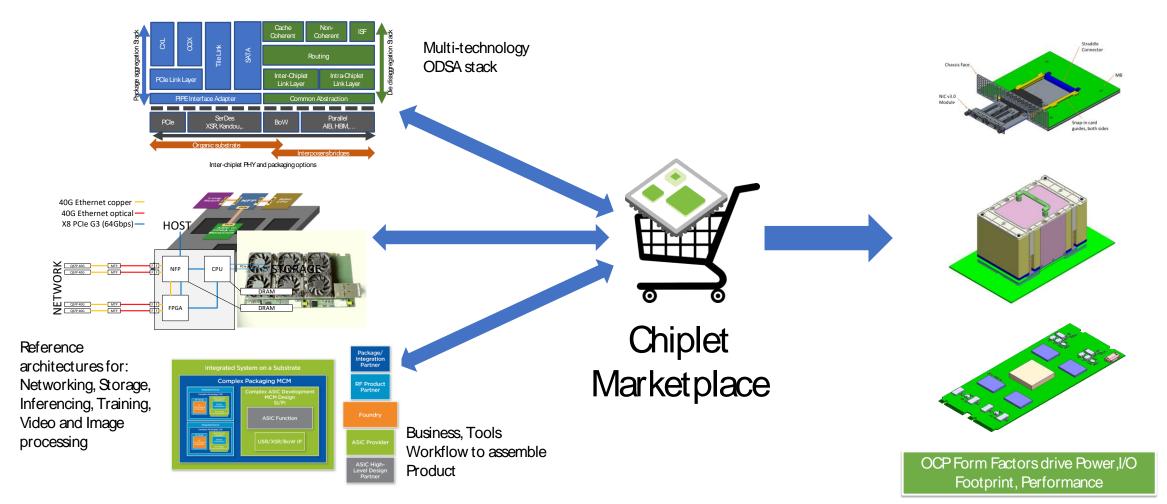

#### The Impact of Open Domain Specific Architecture (ODSA) ODSA Vision of Chiplet Eco-System

#### The Impact of Open Domain Specific Architecture (ODSA) ODSA Vision of Chiplet Eco-System

## The Impact of Open Domain Specific Architecture (ODSA)

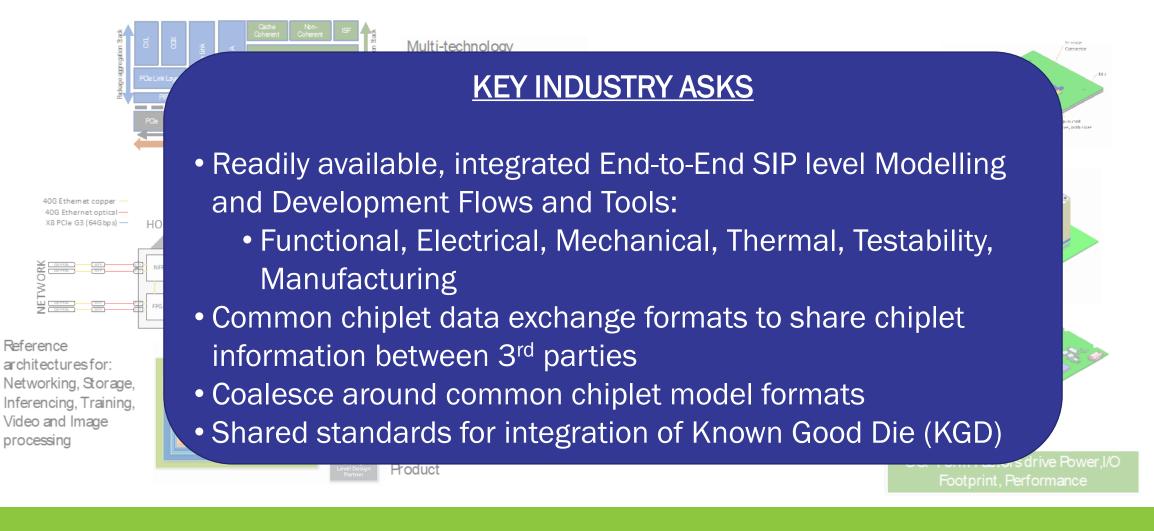

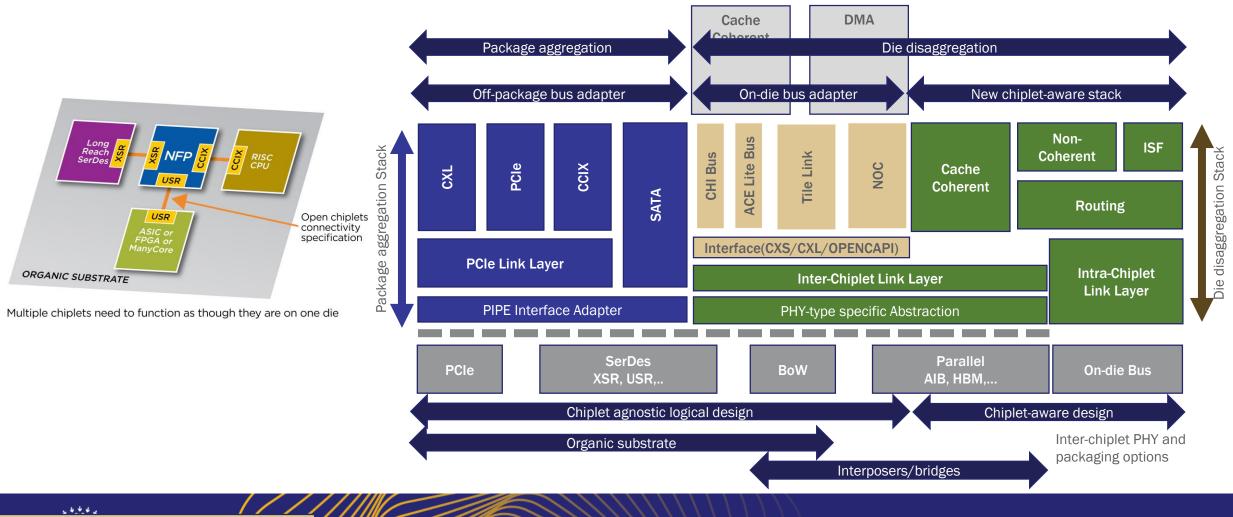

ODSA Stack: Current View

#### !! Coming Along Nicely !!

## Open. Together.

On-die custom protocol (could be open e.g. AXI) → CONAL II / AND Off-package protocol (e.g. PCIe)

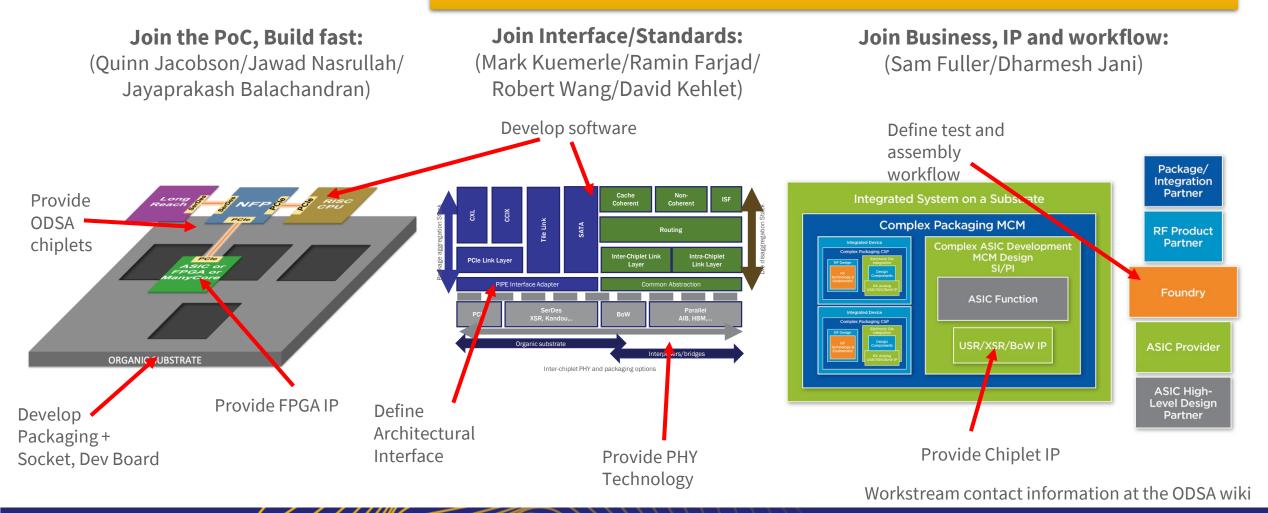

#### The Impact of Open Domain Specific Architecture (ODSA) **ODSA Workstreams**

DCP REGIONAL

#### The Impact of Open Domain Specific Architecture (ODSA) Active Projects

| Project                    | Objective                                                                        | Organizations Participating                                                                                                                                                                          | Recent Results                                            | Upcoming Milestones                          | Needs                                                      |

|----------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------|------------------------------------------------------------|

| PHY Analysis               | PHY requirements<br>PHY analysis<br>Cross-PHY abstraction (PIPE)                 | Alphawave, AnalogX,<br>Aquantia, Avera Semi,<br>Facebook, Intel, Kandou,<br>Netronome, zGlue,                                                                                                        | PHY Analysis paper<br>(published at Hot Interconnect)     | PIPE abstraction                             |                                                            |

| BoW Interface              | No technology license fee, easy to port inter-chiplet interface spec             | Aquantia, Avera Semi,<br>Netronome                                                                                                                                                                   | BoW Interface proposal<br>(published at Hot Interconnect) | BoW specification 0.7<br>End September, 2019 | Test chips, Chiplet library supporting interface           |

| Prototype                  | product that integrates existing die from<br>multiple companies into one package | Achronix, Cisco, Netronome,<br>NXP, Samtec, Sarcina, zGlue,<br>Macom, Facebook                                                                                                                       | Decomposable design flow.                                 | Committed schedule                           | End user<br>End user participation<br>~30% funding is open |

| Chiplet design<br>exchange | Open chiplet physical description format.                                        | Ayar, Cadence, NXP, zGlue,                                                                                                                                                                           | Draft spec                                                | ZEF Exchange format draft specification      |                                                            |

| Link and Network<br>Layer  | Interface and implementations – requirements and proposals                       | Achronix, Avera Semi, Intel,<br>Netronome, NXP, Xilinx                                                                                                                                               |                                                           |                                              |                                                            |

| Multi-chiplet test         | Test requirements for an open-chiplet interface                                  | Engineers from:<br>Achronix, AnalogX, ASE, Avera Semi, Ayar, Cadence, Cisco, Facebook,<br>Ferric, Intel, Kandou, Macom, Marvel, Netronome, NXP, On Semi,<br>Samtec, Sarcina, Synopsys, Xilinx, zGlue |                                                           |                                              |                                                            |

| Chiplet monitoring         | Monitoring infrastructure for chiplet operation                                  |                                                                                                                                                                                                      |                                                           |                                              |                                                            |

| Business workflow          | Formalize learnings from prototype effort                                        |                                                                                                                                                                                                      |                                                           |                                              |                                                            |

Wiki: <u>https://www.opencompute.org/wiki/Server/ODSA</u>, meet Fridays at 8 AM Pacific Time.

Please join us.

#### The Impact of Open Domain Specific Architecture (ODSA) ODSA Collaboration Results

- Physical Interface Definition:

- PHY: Multi-company (zGlue, Netronome, Alphawave, Aquantia) analysis. First cross-PHY analysis published at Hot Interconnect

- Bunch of Wires (BoW) PHY new low-cost inter-chiplet PHY. Developed cooperatively by Aquantia, Avera Semi and Netronome with input from Xilinx, Global Foundries. Published at Hot Interconnect, IEEE Micro (Jan'20).

- PIPE Abstraction a new layer to "abstract" the interface PHY. Supported by Intel in their most recent PHY specification.

- SIP Proof-of-concept / Prototype:

- Software development vehicle: Designed collaboratively by Cisco, Facebook, Macom, zGlue. Components from Achronix, NXP, Netronome. Working toward integrated into SIP. Design is highly scalable → able to add new participants easily.

- Chiplet Design Exchange (CDX) Project:

- Project to facilitate the design of physical chiplet information for CAD tool integration (zGlue, ASE, Cadence, Macom)

- Independent Market survey conducted by IHS Markit

- Everything is on our wiki <u>https://www.opencompute.org/wiki/Server/ODSA</u>

### The Impact of Open Domain Specific Architecture (ODSA) Looking Ahead

#### Time to begin planning Implementation

- PHY Layer:

- Open or nearly-open PHY layer

- Association to share development costs for proprietary PHY layer

- Combination of the two

- Adapter Logic

- PIPE adapter logic

- IO Coherent link layer protocol –an ODSA member company may offer

- Coherent link layer protocol open

- Bus adapters

- Easy to use no-friction interface will be widely used

- Open source implementation is a good start

#### Next ODSA Workshop: 2019-Dec-18 @ Facebook, Menlo Park Ca

#### IF YOU WANT TO GO FAST, GO ALONE IF YOU WANT TO GO FURTHER, GO TOGETHER

AFRICAN PROVERB

# Open. Together.

Consume. Collaborate. Contribute.