# Full Width HPM Form Factor (M-FLW) Base Specification

Part of the

Datacenter - Modular Hardware Systems (DC-MHS) Rev 1.0 Family

Version 0.90

August 22, 2022

5

#### **Revision 1.0 Authors/Contributors:**

Dell, Inc: Corey Hartman, Sanjiv Sinha, Shawn Dube

15 **Google LLC:** Siamak Tavallaei, Jim Levins, Mike Branch

Hewlett Packard Enterprise Company: Vincent Nguyen, David Paquin, Binh Nguyen

Intel Corporation: Brian Aspnes, Drew Damm, Gene Young, Brendan Pavelek, Cliff DuBay

Meta Platforms, Inc: Damien Weng Kong Chong, Todd Westhauser, Michael Haken

Microsoft Corporation: Priscilla Lam, Mark Shaw; Priya Raghu, Luke Gregory

20 Advanced Micro Devices, Inc: Paul Artman, Ravi Bingi, Andy Junkins, Greg Sellman

Note: For questions about this specification please contact Corey Hartman and / or Brian Aspnes at dcmhs@opencompute.org

## **Table of Contents**

|    | 1. Licer | nse                                                         | 7  |

|----|----------|-------------------------------------------------------------|----|

|    | 1.1.     | Open Web Foundation (OWF) CLA                               | 7  |

|    | 1.2.     | Acknowledgements                                            | 8  |

| 30 | 2. Vers  | ion Table                                                   | 9  |

|    | 3. Scop  | pe                                                          | 13 |

|    | 3.1.     | Items Not in Scope of Specification                         | 13 |

|    | 3.2.     | Typical OCP Sections Not Applicable                         | 13 |

|    | 4. Spec  | cification Compliance Table                                 | 14 |

| 35 | 5. Over  | rview                                                       | 15 |

|    | 6. Refe  | rences                                                      | 15 |

|    | 7. Term  | ninology                                                    | 17 |

|    | 8. Back  | kground and Assumptions                                     | 18 |

|    | 8.1.     | Rear Management (ie, OEM) Architecture Assumptions          | 19 |

| 40 | 8.2.     | Front Management (ie, Hyperscale) Architecture Assumptions: | 19 |

|    | 9. HPM   | 1 Layout                                                    | 20 |

|    | 9.1.     | Two Socket (CPU) Assumptions                                | 21 |

|    | 9.2.     | One Socket Assumptions                                      | 22 |

|    | 10. Mecl | hanical Requirements                                        | 23 |

| 45 | 10.1.    | HPM Outline                                                 | 24 |

|    | 10.2.    | Board Datum and Mounting holes                              | 25 |

|    | 10.3.    | HPM Board and Assembly Thickness                            | 26 |

|    | 10.4.    | HPM to Chassis Retention                                    | 28 |

|    | 10.4     | .1. Keepout Zone for Retention Hardware                     | 29 |

| 50 | 10.5.    | HPM Handle Hole                                             | 29 |

|    | 10.6.    | OCP NIC R3 and DC-SCM R2 at Near Edge Locations             | 32 |

|    | 10.7.    | Platform Custom Zone                                        | 33 |

|    | 10.7     | .1. Second OCP NIC R3                                       | 33 |

|    | 10.7     | .2. OCP NIC R3 LFF                                          | 34 |

| 55 | 10.7     | .3. Direct Dock E1.S                                        | 35 |

|    | 10.8.    | Control Panel Connector Locations                           | 36 |

|    | 10.9.    | Zone for PDB Management Connector Header                    | 37 |

|    | 10.10.   | Zone for Intrusion Switch and Internal Host USB3 Connection | 38 |

Date: 08/22/2022

#### Open Compute Project - M-FLW HPM Form Factor Base Spec Rev-1.0 Ver-0.90

|    | 10.11.   | Boot Storage Peripheral Connection                                | 39 |

|----|----------|-------------------------------------------------------------------|----|

| 60 | 10.12.   | Near Side IO Connectors                                           | 40 |

|    | 10.12    | 2.1. Location of Near Side M-XIO Connectors                       | 40 |

|    | 10.12    | 2.2. Mounting Hole Requirements for Near Side Riser Retention     | 42 |

|    | 10.13.   | Far Side IO Connector Choice and Placement                        | 43 |

|    | 10.14.   | Primary Side Component Height Restriction Zones                   | 43 |

| 65 | 10.15.   | Secondary Side KOZ and Height Restrictions                        | 47 |

|    | 10.15    | 5.1. Overall Secondary side Keep-in-Zone Requirements             | 47 |

|    | 10.15    | 5.2. Chassis-to-HPM Bracket (Board Pan) Requirements, and KOZs    | 47 |

|    | 10.15    | 5.3. Secondary Side Tall Component Exceptions                     | 49 |

|    | 10.16.   | HPM Secondary Support                                             | 49 |

| 70 | 10.17.   | Thermal Solution Bracketry Keepout Zones                          | 50 |

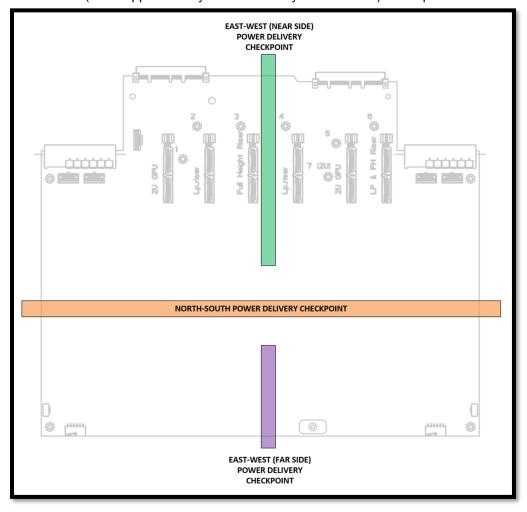

|    | 11. Powe | er Delivery                                                       | 51 |

|    | 11.1.    | HPM Power Zones                                                   | 51 |

|    | 11.1.    | .1. Zone A: M-CRPS Connector(s)                                   | 52 |

|    | 11.1.    | .2. Zone B: PICPWR Connector(s)                                   | 53 |

| 75 | 11.1.    | .3. Zone C: SFF-TA-1033 Connectors w/ PICPWR                      | 54 |

|    | 11.1.    | .4. Zone D: DC-SCM r2.0 Connector                                 | 55 |

|    | 11.1.    | .5. Zone E: NIC 3.0 and Platform Customization Zone Connector(s)  | 55 |

|    | 11.2.    | HPM Power Planes                                                  | 55 |

|    | -        | oted M-FLW HPMs                                                   |    |

| 80 | 13. Supp | olemental Information                                             | 58 |

|    | 13.1.    | Rack and Chassis Depth Stackup Assumptions                        | 58 |

|    | 13.2.    | 1U and 2U PCIe Slot Typical Configurations                        | 59 |

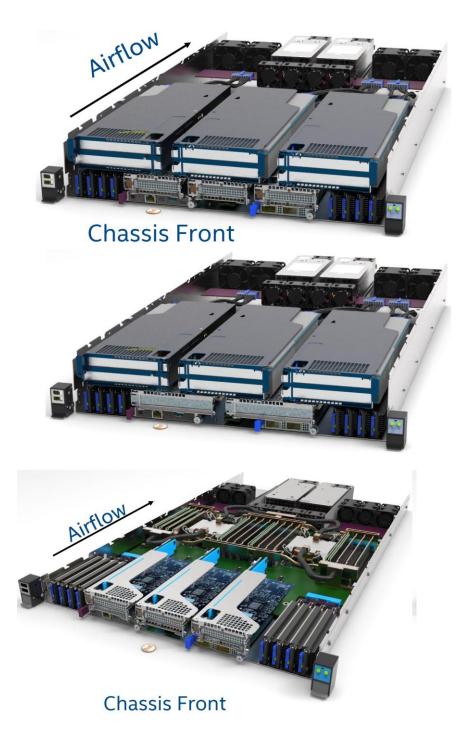

|    | 13.3.    | HPM with Far Side Panel Mount IO (FSPM) Requirements              | 61 |

|    | 13.3.    | .1. FSPM HPM Outline                                              | 61 |

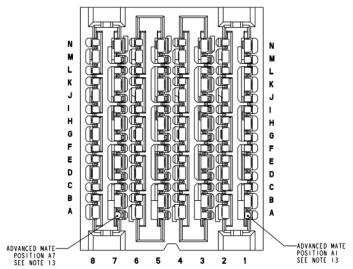

| 85 | 13.3.    | .2. Blade High Speed IO connector                                 | 62 |

|    | 13.3.    | .3. Ingress Power Connector                                       | 64 |

|    | 13.3.    | <u> </u>                                                          |    |

|    | 13.3.    | , , ,                                                             |    |

|    | 13.3.    |                                                                   |    |

| 90 | 13.4.    | Example Scenario for Near IO Population with less than 6x16 ports |    |

|    | 13.5.    | Additional Information on Near IO Riser Retention Holes           |    |

|    | 13.6.    | Reference System Architecture in 21" Chassis                      | 69 |

Date: 08/22/2022

####

15. Appendix B - <supplier name> - OCP Supplier Information and Hardware Product Recognition Checklist.......70

100

95

# **Table of Figures**

|     | Figure 1. Full Width HPM Layout Diagram                                              | 20 |

|-----|--------------------------------------------------------------------------------------|----|

| 105 | Figure 2. First CPU position relative to OCP NIC R3.0 and DC SCM R2.0                | 21 |

|     | Figure 3. Full Width HPM Outline                                                     |    |

|     | Figure 4. Board Mounting Holes with Pads and Keepout Zones (Top / Primary side view) | 25 |

|     | Figure 5. Board and Chassis Stackup Considerations                                   |    |

|     | Figure 6. HPM thickness and Straddle Mount Peripheral Offsets                        |    |

| 110 | Figure 7. HPM Assembly to Chassis Retention Enablement                               |    |

|     | Figure 8. HPM Handling Feature                                                       |    |

|     | Figure 9. HPM Handling Feature Detail                                                |    |

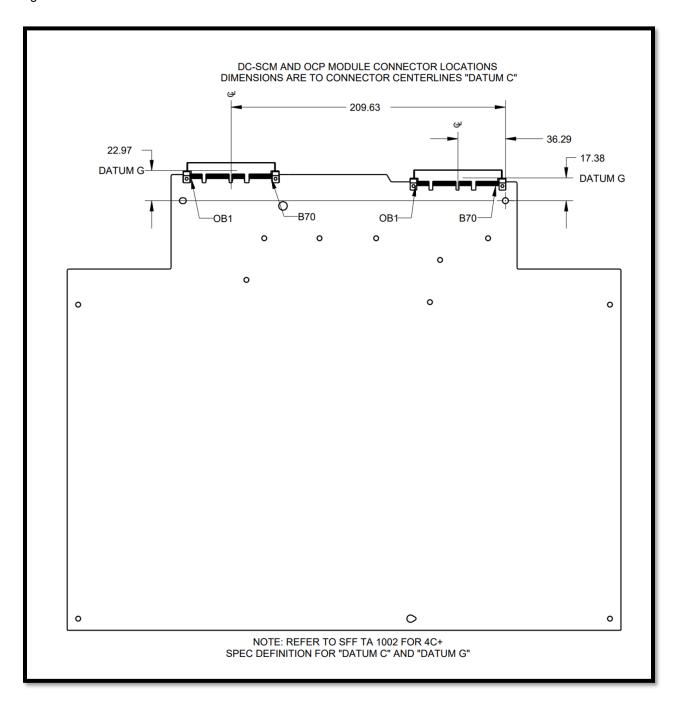

|     | Figure 10. Centerline Locations of OCP NIC R3.0 and DC-SCM R2.0                      | 32 |

|     | Figure 11. Location for Second OCP NIC R3 in Platform Custom zone                    |    |

| 115 | Figure 12. OCP NIC R3 LFF support                                                    |    |

|     | Figure 13. Direct Dock E1.S connector Enablement                                     |    |

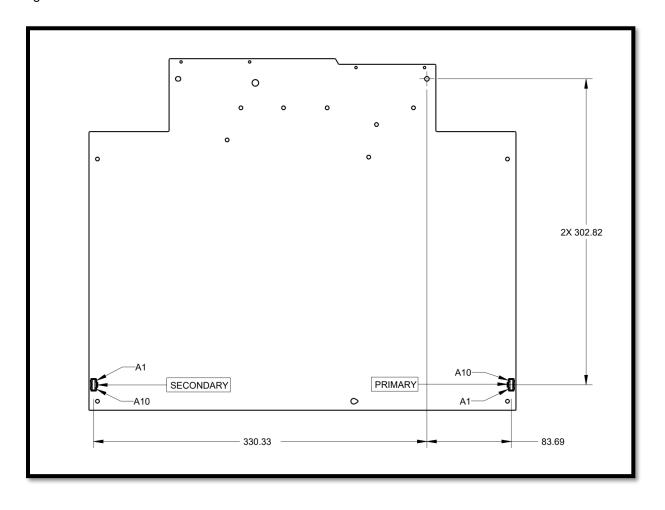

|     | Figure 14. Control Panel Connection Locations                                        |    |

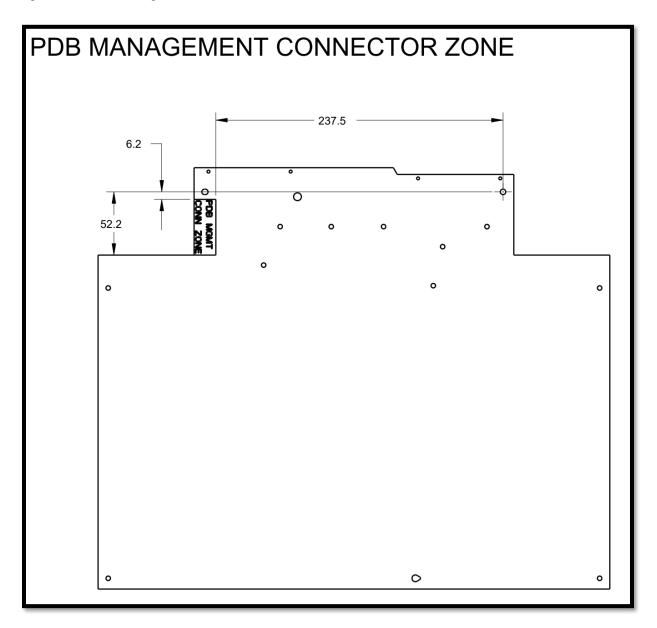

|     | Figure 15. PDB Management Connector Header Location                                  |    |

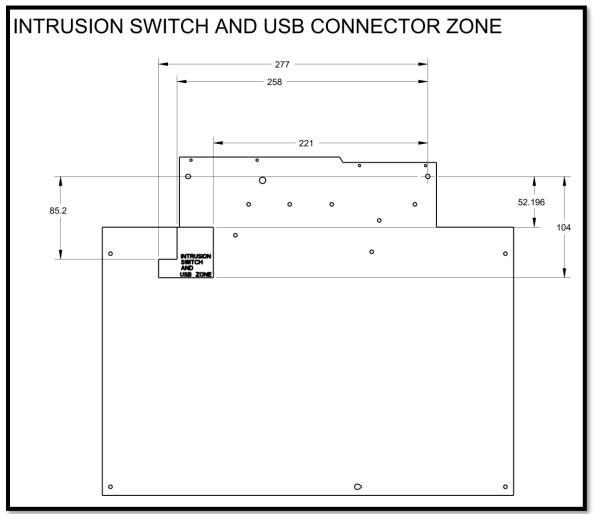

|     | Figure 16. Intrusion and USB Connection Placement Zone                               |    |

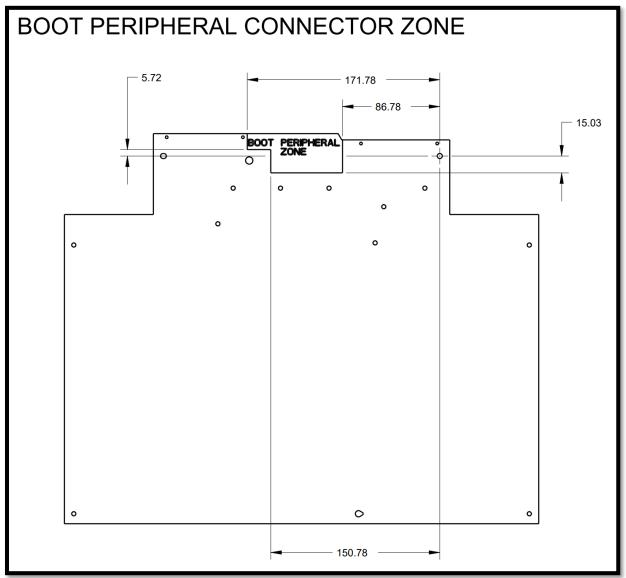

| 120 | Figure 17. Placement Zone for Boot Peripheral Connector                              |    |

|     | Figure 18. Near IO Connector Locations                                               |    |

|     | Figure 19. 1U and 2U Near Side Riser Retention Enablement Holes                      |    |

|     | Figure 20. Zones for Primary Side Component Height Restrictions                      |    |

|     | Figure 21. Example of Chassis-to-HPM Bracket (Board Pan)                             |    |

| 125 | Figure 22. HPM Secondary Side HPM Zero-Height Keepout Zones                          |    |

|     | Figure 23. HPM Secondary Support Diagram                                             |    |

|     | Figure 24. Thermal Solution Bracket Keepouts                                         |    |

|     | Figure 25. HPM Power Zone locations                                                  |    |

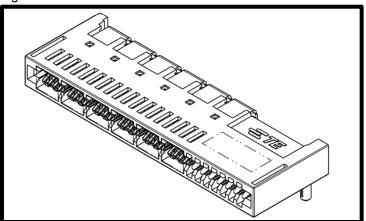

|     | Figure 26. M-CRPS Power Connector                                                    |    |

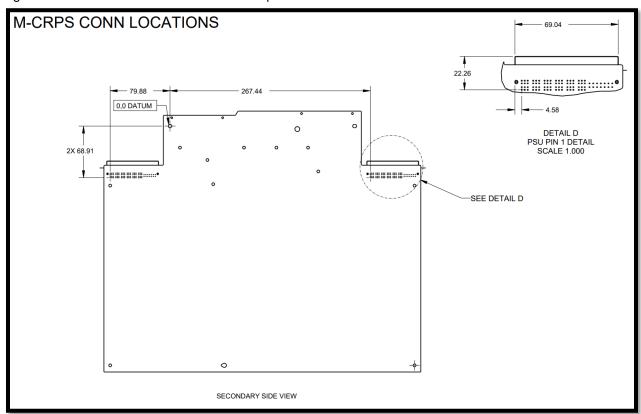

| 130 | Figure 27. M-CRPS Connector Location Requirements                                    |    |

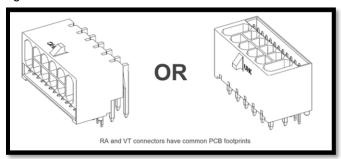

|     | Figure 28. 2x6+12s PICPWR Power Connectors                                           |    |

|     | Figure 29 PICPWR connector (2x6+12s) Location Requirement (6 locations)              |    |

|     | Figure 30. SFF-TA-1033 Connector                                                     |    |

|     | Figure 31 Power Plane (and Supplementary Power Delivery Mechanisms) Checkpoint Area  |    |

| 135 | Figure 32. Rack Depth Constraints                                                    |    |

|     | Figure 33. Typical 1U and 2U PCIe Slot Configurations for Rear Management System     |    |

|     | Figure 34. Typical 1U and 2U PCIe Slot Configurations for Front Management System    |    |

|     | Figure 35. Full Width HPM Outline Modifications for Far Side Panel Mount             |    |

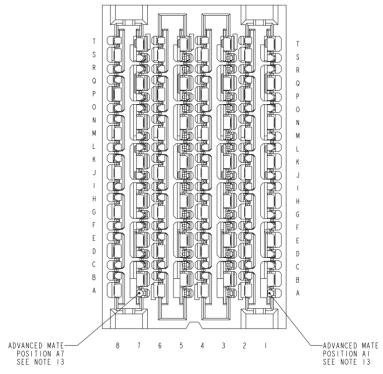

|     | Figure 36. ExaMAX 4x8 connector                                                      |    |

| 140 | Figure 37. ExaMAX 6x8 connector                                                      |    |

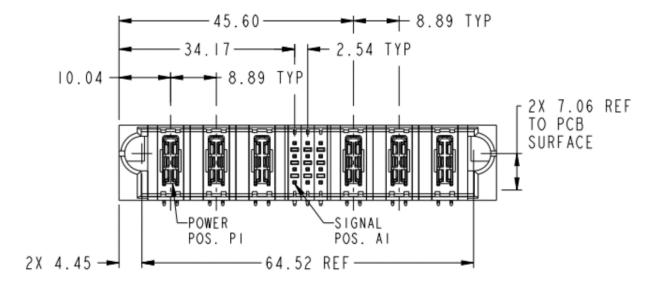

|     | Figure 38. PowerBlade+ Ingress Power Connector                                       |    |

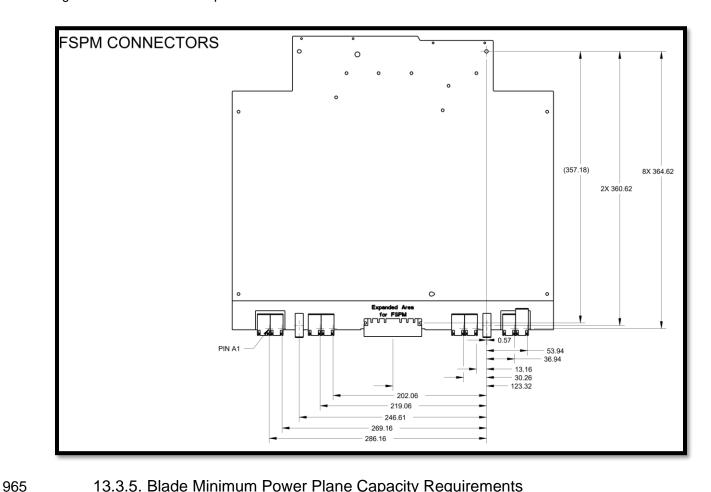

|     | Figure 39. FSPM HPM Required Connector Locations                                     |    |

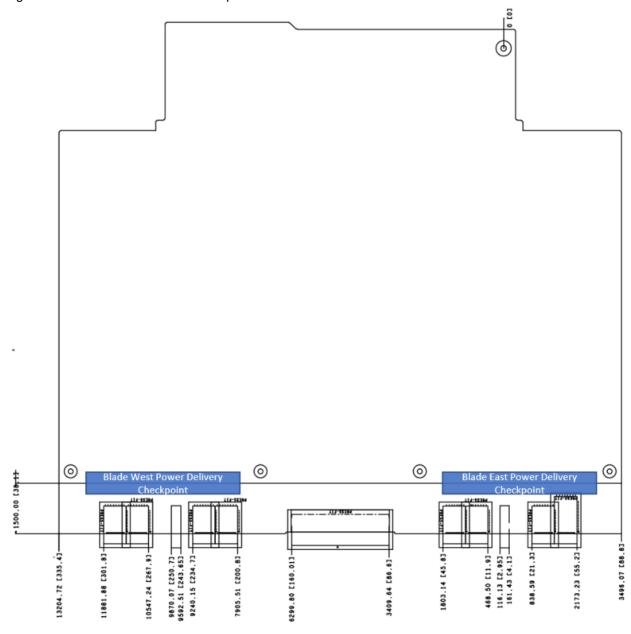

|     | Figure 40. FSPM Power Plane Checkpoint Areas                                         |    |

|     | Figure 41. Example Near IO Connector Population Scenario                             |    |

| 145 | Figure 42. Riser Retention Holes and Associated Near XIO Locations                   |    |

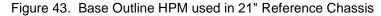

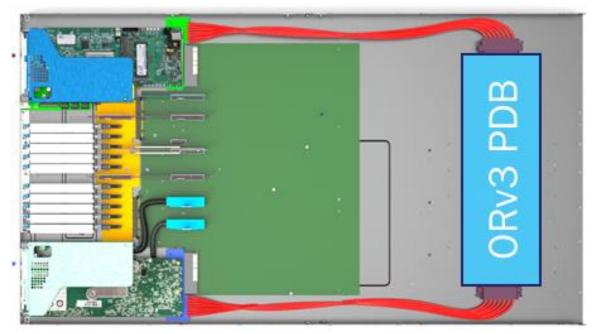

| •   | Figure 43. Base Outline HPM used in 21" Reference Chassis                            |    |

|     | Figure 44. Chassis Base Geometry to Interface Chassis-to-Board Bracketry             |    |

|     |                                                                                      |    |

#### 1. License

150

155

190

#### 1.1. Open Web Foundation (OWF) CLA

Contributions to this Specification are made under the terms and conditions set forth in Open Web Foundation Modified Contributor License Agreement ("OWF CLA 1.0") ("Contribution License") by:

Advanced Micro Devices, Inc.

THE POSSIBILITY OF SUCH DAMAGE.

- Dell, Inc

- Google LLC

- Hewlett Packard Enterprise Company

- Intel Corporation

- Meta Platforms, Inc

- Microsoft Corporation

Usage of this Specification is governed by the terms and conditions set forth in **Open Web** Foundation Modified Final Specification Agreement ("OWFa 1.0") ("Specification License").

You can review the applicable OWFa1.0 Specification License(s) referenced above by the contributors to this Specification on the OCP website at <a href="http://www.opencompute.org/participate/legal-documents/">http://www.opencompute.org/participate/legal-documents/</a>. For actual executed copies of either agreement, please contact OCP directly.

#### Notes:

The above license does not apply to the Appendix or Appendices. The information in the Appendix or Appendix or Appendices is for reference only and non-normative in nature.

NOTWITHSTANDING THE FOREGOING LICENSES, THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, 175 NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN, THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT 180 RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO, OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION, INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS 185 OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF

#### 1.2. Acknowledgements

The Contributors of this Specification would like to acknowledge the following companies for their feedback:

List all companies or individuals who may have assisted you with the specification by providing feedback and suggestions but did not provide any IP.

<<bla><<br/>blank>>

## 200 2. Version Table

| Date       | Version # | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4/22/2022  | 0.70      | Initial Public Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 06/07/2022 | 0.75      | <ul> <li>Added Spec Compliance Table Section 4</li> <li>Added 9.75mm to board under PSU Connectors</li> <li>Moved OCP NIC Connector 6mm to left. (from 204.29mm to 210.29mm)</li> <li>Moved IO Riser Connector #3 to left 5mm. Moved KOZ and Mount hole accordingly (From 136.02mm to 141.02mm)</li> <li>Rotated PIC Power Connectors 180°</li> <li>Defined Pins S1 &amp; S12 on Pic Power Connectors and Rear Power Connectors and revised dimensioning scheme to Pin S1</li> <li>Figure 18, Defined IO Connectors Pin A1 &amp; A77.</li> <li>Defined Pins OB1 &amp; B70 on NIC &amp; DCSCM Connectors</li> <li>Defined Pins OB1 &amp; B70 and Pins B1 &amp; B70 on Alternate NIC Connectors</li> <li>Defined Control Panel Connector Pins A1 &amp; A10</li> <li>New location for USB connector Zone</li> <li>Moved Retention Hardware Height Restriction Zone note to Detail L</li> <li>Combined 1U &amp; 2U PCIE Mount Holes to one sheet</li> <li>Revised references to "KIZ" to "Height Restriction Zone"</li> <li>Revised Bottom Side KOZ shape for Tempan to rectangle. Revised Y-dimensioning scheme to center of rectangle</li> <li>Added KOZ to Bottom side Mount Holes. Preliminary size at 13.8mm x 13.8mm.</li> <li>Changed Figure 3 to support OCP NIC move of 6mm</li> <li>Changed Figure 4 to show pads and KOZs around mounting holes</li> <li>Updated Figure 6 for clarity</li> <li>Changed Figure 10 to move OCP NIC by 6mm.</li> <li>Changed Figure 11, Control panel connector orientation, and primary/secondary designations.</li> <li>Changed Figure 17 and 18 into a new Figure 17. Moved 1U PCle Riser Mount holes down 7.5mm and left 4mm. Added Mount Hole detail with Ø8.0mm Pad size, Ø16mm Component KOZ.</li> <li>Changed Figure 21 to update Secondary size KOZs for mounting holes and chassis hooks</li> </ul> |

|            |      | <ul> <li>Updated Figure 29 for UBB outline updates</li> <li>Added Figure 32 for UBB connector locations</li> <li>Changed description of Adapted HPM in Section 13</li> <li>Figure 26 changed, rotating PIC Power connectors 180 degrees</li> <li>Relocated power plane fusing requirements to M-PIC spec in Section 11.2</li> <li>Clarified minimum power plane recommendation in Section 11.2</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 06/27/2022 | 0.80 | <ul> <li>Modified Table4 in Section 11.1 to describe zone power and range of supported power</li> <li>Clarified minimum power plane recommendation in Section 11.2</li> <li>Renamed Figure 22</li> <li>Figure 19, Sec 10.13, Changed primary side height restriction zones</li> <li>Sect 10.12, Figure 18 change KOZ around Riser retention holes</li> <li>Sect 10.8, Figure 12, moved Intrusion connector to same zone as USB</li> <li>Figure 21, updated MH KOZs on bottom / secondary side.</li> <li>Updated UBB Adapted outline in Figure 29 to update cutout options for cabled HSIO at far edge.</li> <li>Figure 33 updated, based on connector feature updates from vendors</li> <li>Figure 35, updated text in drawing</li> <li>Figure 25, updated title in drawing</li> <li>Added Guide pin part number to Sect 13.1.6</li> <li>Added bullet 6 to section 10.10.1</li> <li>Figure 18, 19, updated KOZ around riser retention holes</li> <li>Figure 22, updated Thermal solution Bracketry KOZ</li> <li>Section 10.8, new section for PDB to HPM header</li> <li>Moved section 12 into existing sections and deleted it</li> <li>Moved section 13.1 into Section 12 "Adapted HPMs" for spec clarity.</li> </ul> |

| 8/22/2022  | 0.9  | <ul> <li>Updated MH drawing Figure 4</li> <li>Added New handle hole geometry required dimensions, Figure 9</li> <li>Updated OCP NIC and DC SCM positions, Figure 10</li> <li>Moved PDB Management conn zone, Figure 15</li> <li>Moved boot connection zone, and modified to accommodate new HPM retention hole location and its associated KOZ, Figure 17</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

- Near IO connector and associated retention holes moved in Figure 18 and Figure 19

- Updated Sect 10.3, HPM Board and Assembly thickness section, to include details and tolerance allowance for the Secondary Side Exception Heights.

- Updated locations of Near side PIC Power (decreased pitch); maintained 10mm gap between pins of Near side Power connectors. Far Side PIC Power connectors moved outward to increase usable Far Edge space for CPU IO and VRs., Figure 29

- Updated Primary side height restrictions, Figure 20, Changed 20mm zone to 22mm and added note that numbers indicate max tol condition. Fixed an unattached dimension.

- Added Platform Custom Zone options of 2x OCP NIC SFF, or single LFF with recommended placements, or direct dock E1.S boot, Section 10.7

- Updated Figure 3 with updated Near side outline

- Updated Section Near Side IO Connectors 10.12, rewrite of requirements.

- Updated CRPS Connector location (near OCP NIC), Figure 27

- Update location of HPM retention hole, Figure 7

- Updated image for latest outline, Figure 42

- Updated Secondary side KOZ's for chassis hooks (board pan interfaces), to allow for more flexibility in DIMM socket placement. Reduced HPM-chassis retention KOZ from 29 to 21mm long. Figure 22

- DC SCM Y position adjusted by 0.18mm, to correct mistake. This correction aligns DC SCM with OCP NIC at rear wall.

- Changed Power Zone E rating to 160W

- Changed Power Rating Zone C to 250W per Near IO Connector instance

- Added Section 10.7 to define Platform Custom zone and a couple standard options that could be utilized. These drawings were in the Supplemental Info section, previously.

- Added E1.S enablement option, Figure 13

- Fixed KOZ around chassis retention hole to 21x21mm,

Figure 22

- Added implementors note about HPM handle hole and Mounting holes Figure 22. HPM Secondary Side HPM Zero-Height Keepout Zones

- Deleted chapter 12.2, which had old, adapted options that were pulled into the new Platform Custom Zone.

#### 3. Scope

205

This document defines technical specifications for the Server Product used in Open Compute Project. This document shall comprise the hardware product types complete technical specification. Any supplier seeking OCP recognition for a hardware product based on this spec must be 100% compliant with all features or requirements described in this specification.

210

215

#### 3.1. Items Not in Scope of Specification

- Compute Core (CPU/Memory/Voltage Regulators/SMP routing between CPUs)

- JTAG/Debug connectors for the Compute Core

- CPU, Memory, Heatsink, Liquid and any other thermal solutions

- Reliability requirements and design-in details

- BOM Population requirements

- Cooling System Connections (Fans, etc).

#### 3.2. Typical OCP Sections Not Applicable

- Open Compute documents are typically expected and desired to contain common document Sections. The DC-MHS specifications are comprised of Base Form Factor Specifications and Supporting Platform Connectivity specifications, and are structured such that the typical OCP document structure does not apply to this Base Form Factor Spec. This specification will not contain the following Sections.

- Rack Compatibility (See Section 13.1 Rack and Chassis Depth Stackup Assumptions)

- Physical Specifications

- Thermal Design Requirements

- Rear Side Power, I/O, Expansion

- Onboard Power System

- Environmental Regulations/Requirements

- Prescribed Materials

- Software Support

- System Firmware

- Hardware Management

- 235 Security

The content expected in these subject areas is expected to be documented in future private and/or public Design Specifications and/or Product Specifications.

Date: 08/22/2022

#### 4. Specification Compliance Table

240 (Not Fully Updated for v0.9, Subsequent Section Requirements supersede this until 1.0 Release.)

The following table is intended summarize the list of attributes and requirements for a design to be DC-MHS M-FLW Base Specification compliant.

Table 1. Specification Compliance Summary Table

| #  | Technical Specification                                                                                                                                                                                                                       | Document Reference                       |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| 1  | Base Mechanical Outline                                                                                                                                                                                                                       | Figure 3 and Section                     |

| -  |                                                                                                                                                                                                                                               | 10.1                                     |

| 2  | Minimum of 6 board mounting holes implemented                                                                                                                                                                                                 | Figure 4 Section 10.2                    |

| 3  | Mounting Hole pad and KOZ requirements                                                                                                                                                                                                        | Figure 4, Section 10.2                   |

| 4  | Maximum HPM Board thickness of 3.18mm, assuming 10% max tolerance                                                                                                                                                                             | Section 10.3                             |

| 5  | HPM Thickness + Backing plate shall not exceed 5.86mm                                                                                                                                                                                         | Section 10.310.15.3                      |

| 6  | In the Secondary Side height restriction exception zones (defined in Section 10.15.3 HPM Board and Assembly Thickness), HPM thickness + Secondary side components shall be a maximum of 5.66mm                                                | Section 10.3                             |

| 7  | Required Board hole for HPM retention to chassis                                                                                                                                                                                              | Figure 7, Section 10.4                   |

| 8  | KOZ required on top and bottom sides around HPM Retention hole                                                                                                                                                                                | Figure 20, Figure 22, and Section 10.4.1 |

| 9  | HPM requires a hole at Far side for interface to mechanical handle                                                                                                                                                                            | Section 10.5                             |

| 10 | The hole geometry for board handle shall follow the required dimensions and KOZ in Figure 9.                                                                                                                                                  | Figure 9, Section 10.5                   |

| 11 | HPM must fix OCP NIC R3 and DC-SCM R2 locations as defined                                                                                                                                                                                    | Figure 10, Section 10.6                  |

| 12 | HPM shall implement 2 instances of Control Panel Interface connectors per defined locations                                                                                                                                                   | Figure 14, Section 10.8,                 |

| 13 | HPM PDB Management Connector placement                                                                                                                                                                                                        | Figure 15, Section 10.9                  |

| 14 | HPM Shall implement Internal USB connection and Intrusion Switch connector in defined zone                                                                                                                                                    | Figure 16, Section 10.10                 |

| 15 | The Required connector for Near IO positions shall be SFF-TA-1033.                                                                                                                                                                            | Section 10.12.1, Figure 18               |

| 16 | Near IO Connector shall be placed at locations defined in Figure 18                                                                                                                                                                           | Figure 18, Section 10.12.1               |

| 17 | Mounting hole requirements for IO module retention                                                                                                                                                                                            | Figure 19, Section 10.12.2               |

| 18 | High Speed IO connector choices for the Far Side Shall meeting the Height Restriction requirements                                                                                                                                            | Section 10.13                            |

| 19 | Primary side component height restriction zone shall be implemented                                                                                                                                                                           | Figure 20, Section 10.14                 |

| 20 | If a cable connection (power, High speed IO, etc) is placed in the component height restriction zone, the max height restriction shall apply to the mated height of the plug and cable assembly, including component and assembly tolerances. | Section 10.14                            |

| 21 | The back side or secondary side of the HPM shall have a universal height restriction of 1.6 mm, unless otherwise specified in the areas of 0 height zones.                                                                                    | Section 10.15.1, Figure 22               |

| 22 | HPM shall support chassis to board bracketry (board pan) 0-Height KOZs                                                               | Section 10.15.2, Figure 22 |

|----|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 23 | No two instances of a secondary side exception shall be closer than 10mm, as to not drive excess cutouts in Chassis-to-HPM bracketry | Section 10.15.3            |

| 24 | The HPM shall have zones and provide HPM Secondary Supports that are 1.78mm +/- 0.10mm thick.                                        | Figure 23, Section 10.16   |

| 25 | HPM shall implement KOZ's on Far side mounting holes for Thermal solution brackets                                                   | Section 10.17, Figure 24   |

| 26 | Locations of M-CRPS connectors shall be placed as defined in Figure 27                                                               | Figure 27, Section 0       |

| 27 | HPM 2x6+12s PICPWR connector placement                                                                                               | Figure 29, Section 0       |

| 28 | Minimum HPM Power Supply Rail Requirements per PCIe CEM Slot                                                                         | Table 6, Section 1.1.1     |

|    | Note, additional Compliance Requirements from Section 11.2 have been omitted for 0.9 rev because they are likely to change for 1.0.  |                            |

|    |                                                                                                                                      |                            |

#### 5. Overview

The objective of this specification is to specify the requirements of a Full Width Host Processor Module (HPM). This is for use within products designed for minimum 19" rack, also known as compliant with EIA-310-E but can also accommodate larger 21" racks. This form factor enables a full width HPM usage for CPUs, DIMMs, and related features. This full width form factor generally allows for maximum IO of the CPUs to be offered and brought to accessible slots (although exceptions could occur in the future). This specification will NOT reference a specific CPU or memory technologies. The goals and success criteria of this specification is so that multiple generations of CPU/Memory (Compute Core) designs can be designed into this form factor specification, so that chassis and system designs can be reused as desired. This should have the benefits of reduced design investment, reduced validation investment, and faster development cycle time.

This specification shall define attributes and design requirements that are common and critical to the use and deployment of customers and vendors of Enterprise and Cloud Full Width Server rack products. Examples include mechanical form factor, placement guidance of common subsystems and placement guidance of motherboard Input-Output (IO) connections.

#### 6. References

The **D**ata **C**enter – **M**odular **H**ardware **S**ystem (DC-MHS) family of specifications are written to enable interoperability between key elements of datacenter and enterprise infrastructure by providing consistent interfaces and form factors among modular building blocks. At the time of this publication there are the following specification workstreams:

**M-FLW** (Modular Hardware System FulL Width Specification) – Host Processor Module (HPM) form factor specification optimized for using the full width of a Standard EIA-310-

Date: 08/22/2022 15

245

250

255

260

270

Open Compute Project - M-FLW HPM Form Factor Base Spec Rev-1.0 Ver-0.90

D Rack mountable server. The specification is not limited to use within the EIA-310 Rack but is used to serve as a template for a common target where the design is expected to be utilized.

**M-DNO** (Modular Hardware System Partial Width **Den**sity **O**ptimized Specification) – Host Processor Module (HPM) specification targeted to partial width (i.e. ½ width or ¾ width) form factors. Such form factors are often depth challenged and found not only in enterprise applications but also in Telecommunications, Cloud and Edge Deployments. While the EIA-310 Rack implementation is chosen as a key test case for use, the specification is not limited to use within the EIA-310-D Rack but is used to serve as a template for a common target where the design is expected to be utilized.

**M-CRPS** (Modular Hardware System Common Redundant Power Supply Specification) – Specifies the power supply solutions and signaling expected to be utilized by DC-MHS compatible systems.

**M-PIC** (Modular Hardware System Platform Infrastructure Connectivity Specification) – Specifies common elements needed to interface a Host Processor Module (HPM) to the platform/chassis infrastructure elements/subsystems. Examples include power management, control panel and cooling amongst others.

**M-XIO** (Modular Hardware System Extensible I/O) – Specifies the high-speed connector hardware strategy. An M-XIO source connector enables entry and exit points between sources such as Motherboards, Host Processor Modules & RAID Controllers with peripheral subsystems such as PCIe risers, backplanes, etc. M-XIO includes the connector, high speed and management signal interface details and supported pinouts. **M-PESTI** (Modular Hardware System **Pe**ripheral **S**ideband **T**unneling **I**nterface) – Specifies a standard method for discovery of subsystems, self-describing attributes, and status (e.g., versus a priori knowledge/hard coding firmware and BIOS for fixed/limited configurations). Examples: vendor/module class, physical connectivity descriptions, add-in card presence, precise source to destination cable coupling determination.

To access additional DC-MHS specification please visit OCP Server WIKI

#### **Additional References**

275

280

285

290

295

- 300 This specification also relies on the following Open Compute Project specifications

- OCP Server Network Interface Card (NIC) R3.0 Specifies NIC card form factors targeting a broad ecosystem of NIC solutions and system use cases.

Mezz (NIC) » Open Compute Project

- OCP Datacenter Secure Control Module (DC-SCM) R2.0 Specifies a SCM designed to interface to an HPM to enable a common management and security infrastructure across platforms within a data center.

Hardware Management/Hardware Management Module Open Compute

Date: 08/22/2022

# Terminology

| Standardized Term | Meaning                                                                                                                    | Alternative<br>Terms |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------|--|

| Shall             | Indicates a requirement for spec compliance                                                                                |                      |  |

| HPM (Host         | PCB or PCBA form-factor being defined by this spec                                                                         | Motherboard,         |  |

| Processor Module) |                                                                                                                            | board                |  |

| PCB               | Printed Circuit Board                                                                                                      |                      |  |

| DC-SCM            | Datacenter Secure Control Module Rev 2.0 as defined by OCP                                                                 |                      |  |

|                   | DC-SCM Rev 2.0 spec                                                                                                        |                      |  |

| CPU               | Central Processing Unit                                                                                                    |                      |  |

| Ю                 | Input Output, commonly referring to high speed connections to a CPU socket.                                                |                      |  |

| PCle              | Peripheral Component Interconnect Express                                                                                  |                      |  |

| CXL               | Compute Express Link, open standard for CPU to device and CPU to Memory connections.                                       |                      |  |

| Chassis-Board     | Bracket that attaches to a HPM assembly, that enables a variety of                                                         | Board Pan            |  |

| Bracket           | board outlines and hole locations to change over time, and still fit within same chassis base.                             | Sub-pan              |  |

| Near              | Board location or zone, related to section of board containing DC-                                                         |                      |  |

|                   | SCM Rev 2.0, Management subsystem                                                                                          |                      |  |

| Far               | Board location or zone, opposite of location of Management                                                                 |                      |  |

|                   | Subsystem                                                                                                                  |                      |  |

| Platform          | Complete system including HPM, power, peripherals, etc                                                                     |                      |  |

| Compute Core      | Elements of board design that are critical to processor and                                                                |                      |  |

|                   | memory support, inclusive of CPU and Memory sockets.                                                                       |                      |  |

|                   | Examples are Voltage Regulators, High Speed IO routing, High                                                               |                      |  |

|                   | speed trace routing between multiple processors, high speed trace                                                          |                      |  |

|                   | routing between processors and memory, etc                                                                                 |                      |  |

| Platform Custom   | Area of system board where space is allotted for Platform                                                                  |                      |  |

| Zone              | designers to implement custom features.                                                                                    |                      |  |

| HSIO              | High Speed IO, commonly referring to PCIe routing, PCIe                                                                    |                      |  |

|                   | connectors, CXL routing/connectors, etc.                                                                                   |                      |  |

| OCP               | Open Compute Project                                                                                                       |                      |  |

| OEM               | Original Equipment Manufacturer                                                                                            | Enterprise           |  |

| Platform          | A Specification that defines Platform Interconnect details for                                                             | M-PIC spec           |  |

| Infrastructure    | features that are common across many HPM Form Factors.                                                                     |                      |  |

| Connectivity Spec | Examples connectivity features include fans, backplanes, and                                                               |                      |  |

|                   | control panels.                                                                                                            |                      |  |

| KOZ               | Keepout Zone, a design term for PCB designs that defines area of                                                           |                      |  |

|                   | a board design where no components may be placed, usually to                                                               |                      |  |

|                   | enable mechanical attachments or mechanical features.                                                                      |                      |  |

| Compliant HPM     | An HPM which meets every item listed in the M-FLW specification                                                            |                      |  |

|                   | compliance table.                                                                                                          |                      |  |

| Adapted HPM       | An HPM which has strong correlation to base spec requirements                                                              |                      |  |

|                   | but does not meet every item in the base specification compliance                                                          |                      |  |

| HDM Dooisson      | table.                                                                                                                     |                      |  |

| HPM Designer      | The person or organization designing an HPM (whether compliant or adapted) which implements the M-FLW specification.       |                      |  |

| System Designer   | The person or organization designing a system which incorporates M-FLW HPMs (whether compliant or adapted) into the system |                      |  |

|                   | design.                                                                                                                    |                      |  |

#### 8. Background and Assumptions

- This Full Width HPM Form Factor specification is created to enable typical platform feature sets for both Front and Rear Management, in 1U and 2U chassis applications. Some of the platform features that are common in the industry, and influence the Form Factor constraints are:

- Chassis installation within minimum EIA-310-D racks (but not limited to).

- PCIe (Version 5.0 and future) Card configurations typically offered by Enterprise OEMs/Hyperscalers. See Figure 33. Typical 1U and 2U PCIe Slot Configurations.

- In the 1U PCIe offering, only Half-Length PCIe cards (167.6mm) are considered. This does not prevent Three-Quarter Length (254mm) cards, but support for Three-Quarter Length cards would require more restrictive Compute Core placement (not defined).

- HPM enabled minimum 75W of power per PCIe slot, with ability to scale up to 600W for some slots (likely 3~4).

- The specification details support for the Open Compute peripherals directly connected to board

- o OCP NIC R3.0

- o DC-SCM R2.0

- 330 O Note: A System is not limited to 1 device of each type; configurations with >1 OCP NIC R3.0 or DC-SCM R2.0 are possible, but outside the scope this specification will cover.

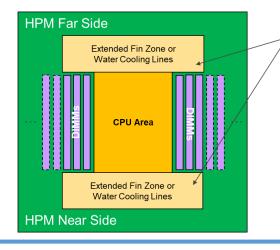

- Thermal Design Points considerations includes keepout zone to enable air cooling thermal solutions that extend beyond the CPU and Memory sockets. Memory TDPs under consideration are in the 20-25W range.

- Considerations for Liquid cooling solutions, including CPU cold plates and DIMM liquid cooling manifolds.

- Considerations for Power Delivery to important chassis subsystems.

340

335

320

325

#### Open Compute Project - M-FLW HPM Form Factor Base Spec Rev-1.0 Ver-0.90

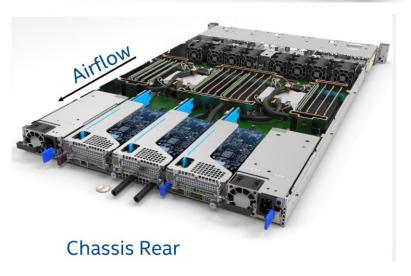

#### 8.1. Rear Management (ie, OEM) Architecture Assumptions

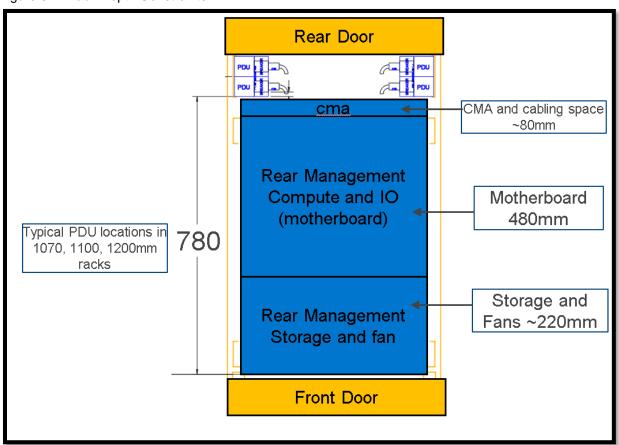

- a. Chassis depth constraints in consideration of Power Distribution Units placed approximately 780mm from front EIA mounting flange.

- b. Enterprise Storage and Fan subsystems requiring approximately 220mm. (See Figure 32. Rack Depth Constraints)

- c. Sliding rack rails that require a max overall chassis width of 434mm, with interior chassis width/opening of minimum 427mm.

- d. Considerations for Power and High-Speed IO Cabling

- e. Considerations for Ease of Installation and Removal of motherboard in a chassis.

- f. Adequate delivery power through HPM to enable typical Storage configuration power loads (See **Section 1**)

#### 8.2. Front Management (ie, Hyperscale) Architecture Assumptions:

- a. 1070mm rack depth

- All IO generally on cold aisle but may also include some architectures with hot aisle IO. Assuming Front/Near end of system supports IO devices such as PCI CEM, OCP NIC R3.0, SSD's, etc

- c. PCIe also distributed at Far end, such as to backplane, OAI Universal Baseboard, and other items.

- d. AC or DC rack power supplied by rack from the hot aisle

- e. If PSUs are used, they are not hot serviceable

Date: 08/22/2022

345

350

355

#### 9. HPM Layout

370

375

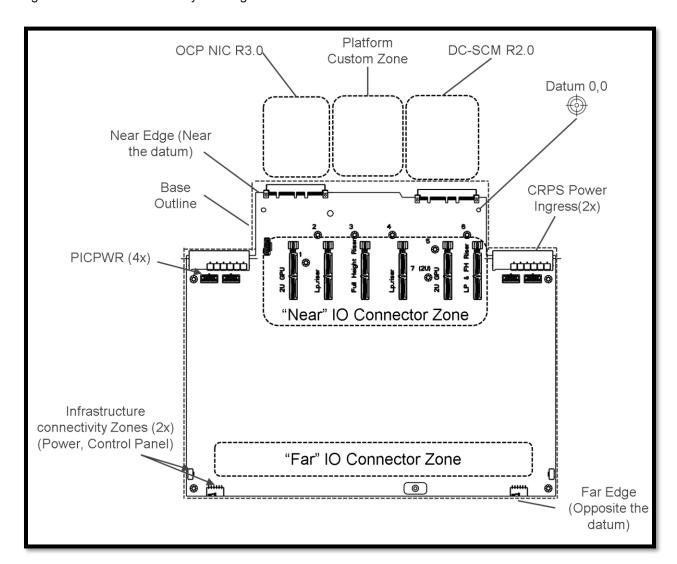

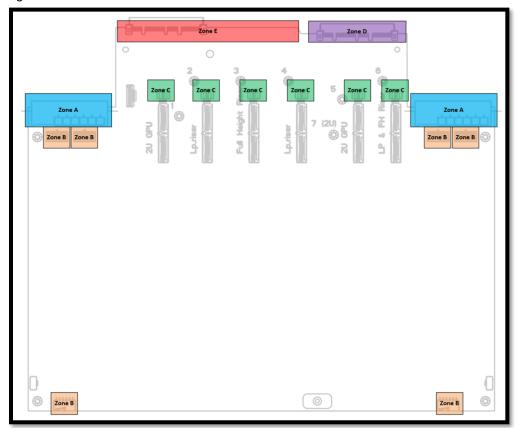

The following **Figure 1** shows the layout and approximate locations of major subsystems in the Enterprise and Hyperscale M-FLW HPM.

"Near" and "Far" are reference naming conventions to the side of the board and Compute Core, as to orient the reader as to which portion of the board and Compute Core is being referred to. This specification refers to the Near Side as where DC-SCM R2.0 Management subsystem resides as a board peripheral. This is also typically referred to Rear IO location for Enterprise products, in which products are designed with IO in the hot aisle of a rack deployment (air exit). This is also typically referred to Front IO location for Hyperscale products, in which products are designed with IO in the cold aisle of a rack deployment (air inlet).

Figure 1. Full Width HPM Layout Diagram

#### 9.1. Two Socket (CPU) Assumptions

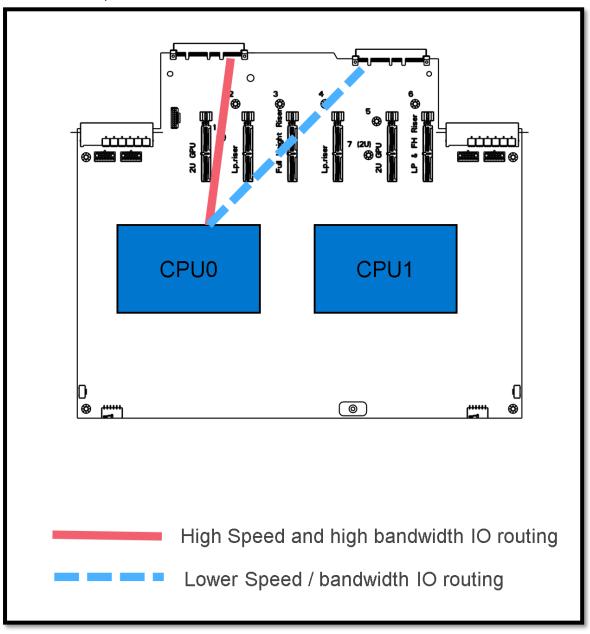

The OCP NIC R3.0 subsystem is positioned on the left based on two assumptions:

380

385

- In a 2S (CPU) system, the First/Boot CPU in a two CPU HPM is positioned on left.

- OCP NIC R3.0 is directly routed through the motherboard to the first/boot CPU.

The OCP NIC R3.0 is intended to be closer to this boot CPU to best enable the high-speed IO routing. The OCP NIC R3.0 will usually require higher bandwidth routing, and thus should be optimized for material selection and cost impacts. The routing from first/boot CPU to management subsystem (DC-SCM R2.0) has lower bandwidth requirements, and thus should not be the determining factor in board material selections and routing strategy. See **Figure 2**.

Figure 2. First CPU position relative to OCP NIC R3.0 and DC SCM R2.0

#### Open Compute Project - M-FLW HPM Form Factor Base Spec Rev-1.0 Ver-0.90

In this specification the CPU and Memory locations are intentionally not specified. This is for future flexibility in CPU/Memory quantities, locations, sizes, etc. The board area between DC-SCM R2.0 and OCP NIC R3.0 is designated as a "Platform Custom Zone", as shown in **Figure 1. Full Width HPM Layout Diagram**. The goal is to provide board area and system volume for individual platforms to provide system specific features.

#### 9.2. One Socket Assumptions

395

In theory, for a one socket (CPU) platform, the OCP NIC R3.0 location does not have a strong affinity to either side. <u>The OCP NIC R3.0 shall remain in the specified HPM location for chassis compatibility for all Full Width HPM products. The second OCP NIC shown in the Platform Customization Zone is optional, the OCP NIC on the left must always be populated.</u>

#### 10. Mechanical Requirements

In addition to the drawings and details within this document, DFX/CAD files will be provided for further detail. Unless otherwise specified all units are in mm. The following standard tolerances apply to all drawings unless otherwise specified. Unless otherwise specified, PCB dimensions shown in this specification shall comply to the following table.

#### 405 Note: This table is preliminary for V0.9 and subject to change for V1.0.

| Dimension Type                                    | Tolerance, unless otherwise specified |

|---------------------------------------------------|---------------------------------------|

| Drilled hole (origin) to round fiducial           | +/- 0.076mm (+/- 0.003 inch)          |

| Drilled hole (origin) to profiled card edge       | +/- 0.254mm (+/- 0.010 inch)          |

| Drilled hole (origin) to drilled hole             | +/- 0.127mm (+/- 0.005 inch)          |

| Profiled card edge to profiled card edge          | +/- 0.127mm (+/- 0.005 inch)          |

| Feature of size (hole diameter, slot width, etc.) | +/- 0.100mm (+/- 0.004 inch)          |

| PCB thickness                                     | +/- 10% of nominal                    |

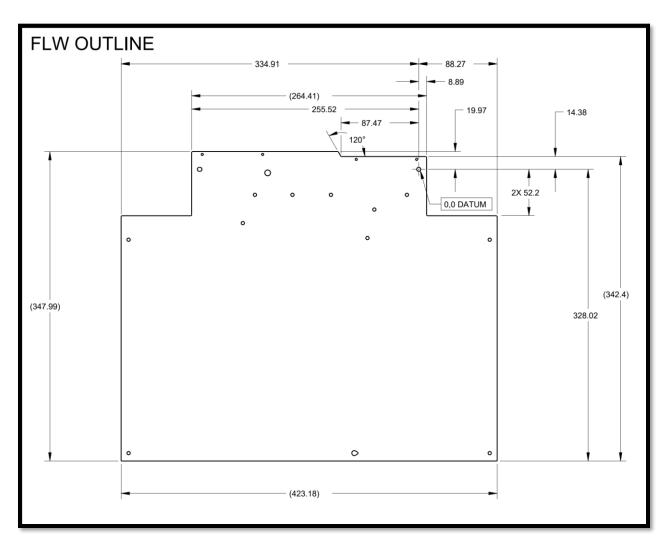

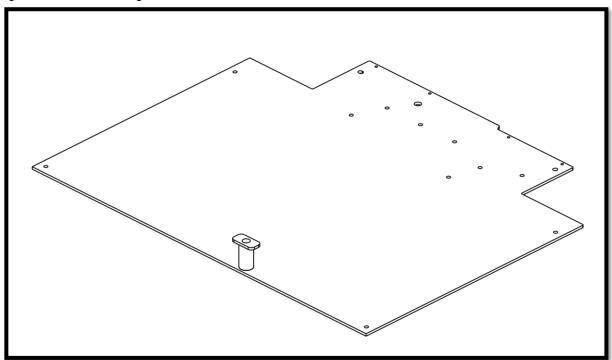

#### 10.1. HPM Outline

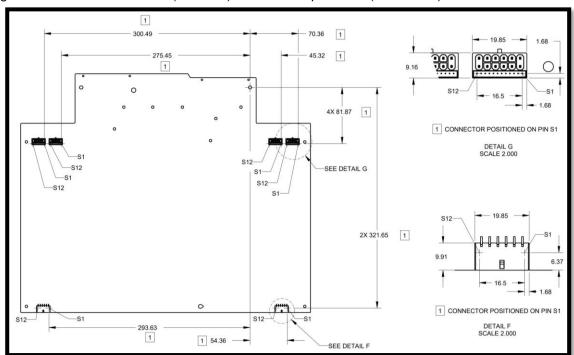

- The Full Width HPM (M-FLW) outline is defined in Figure 3 and shall be followed for a M-FLW Base Specification compliant HPM. This defines the outline and peripheral locations to fit compute core and IO elements in an FLW compliant chassis. This is intended to fit a wide variety of platform and chassis applications.

- The M-FLW HPM Outline is defined in Figure 3 below. The intent is to show overall dimensions of board outline. DFX/CAD file link will be in **Section 13.8 CAD files** section and provided in future specification releases.

Figure 3. Full Width HPM Outline

420

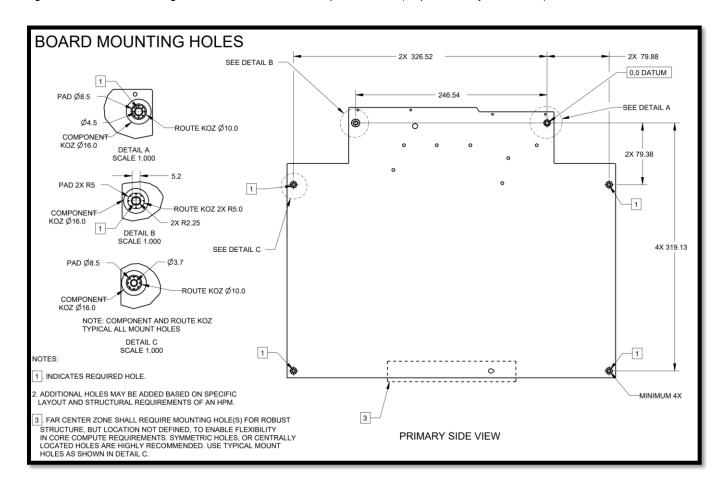

#### 10.2. Board Datum and Mounting holes

425

430

435

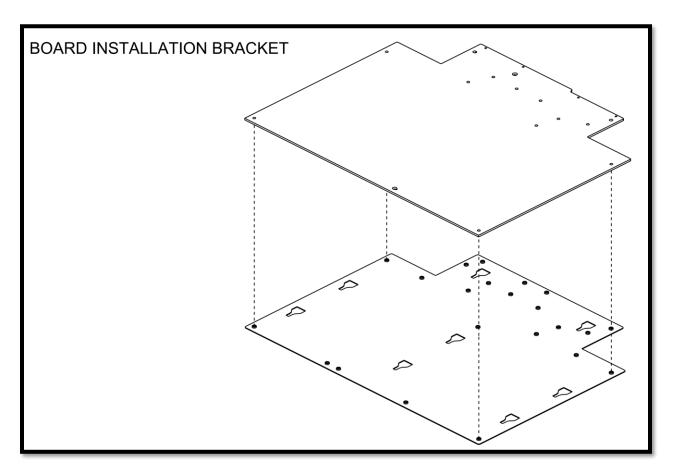

A set of six required board mounting holes specified shall be implemented around the board perimeter per Figure 4 and represent the minimum mounting hole requirements. These six boards mounting holes interface to the Chassis-to-Board Bracket (Board Pan). Additional mounting holes are allowed as needed, to ensure appropriate mechanical support of the Compute Core (not shown). These additional board holes are expected to interface to the board-chassis bracketry and should be designed in consideration of the bracket to chassis interface features, as defined in Section 10.4 HPM to Chassis Retention. A design should follow good engineering practices and in consideration of platform shock and vibration requirements. Shock and vibration requirements are not in scope of this specification.

<u>The mounting holes shall have a pad and component KOZ as defined in **Figure 4**. The component KOZ is intended to keep small components at risk of damage away from the hardware and assembly tools. If a component is larger than 10mm in any dimension, it is considered more robust, and an exception will allow such component to encroach on the Component KOZ's in **Figure 4**.</u>

Figure 4. Board Mounting Holes with Pads and Keepout Zones (Top / Primary side view)

#### **Implementors Note:**

The PCB Datum hole (Detail A) is defined such that a collared standoff with tight tolerance fit can be used to control X-Y tolerances in HPM mounting. Additionally, a slotted hole (Detail B) is defined to control rotation around the datum, by allowing, as an example, a collared standoff to be used with tight fit to the top/bottom edge of the slot.

All other mounting holes follow standard mounting hole guidance (Detail C). These mounting holes are expected to have clearance fits to screw hardware.

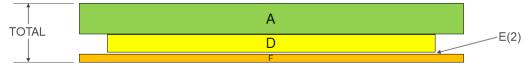

#### 10.3. HPM Board and Assembly Thickness

440

445

450

455

<u>The maximum board thickness allowed shall be 3.18mm nominal, assuming +10% max tolerance.</u> HPM Thickness choices may have impacts on chassis stackup. HPM thickness must consider the backing plate thickness and the secondary side components of a required Core Compute.

- M-FLW HPM shall have a maximum allowable HPM thickness + backing plate stackup of 5.86mm. Backing plates are assumed to be allowed to protrude thru cuts in the Chassis-to-Board bracketry.

- 2. <u>In the Secondary Side height restriction exception zones (defined in Section 10.15.3 HPM Board and Assembly Thickness)</u>, HPM thickness + Secondary side components shall be a maximum of 5.66mm

- a. Allowing for +/- 0.2 mm HPM mounting height tolerance in an assumed 5.86 HPM mounting height).

**Figure 5** and **Table 2** below demonstrate example scenarios HPM designers should consider when choosing HPM thickness.

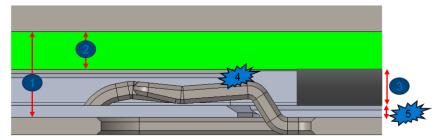

460 Figure 5. Board and Chassis Stackup Considerations

- HPM Top Surface Height to Chassis base

- 2. HPM Thickness

- 3. Backing Plate Thickness

- 4. Gap from HPM to Mounting hook

- Gap to chassis base (may cut thru sub-pan

#### **Implementors Note:**

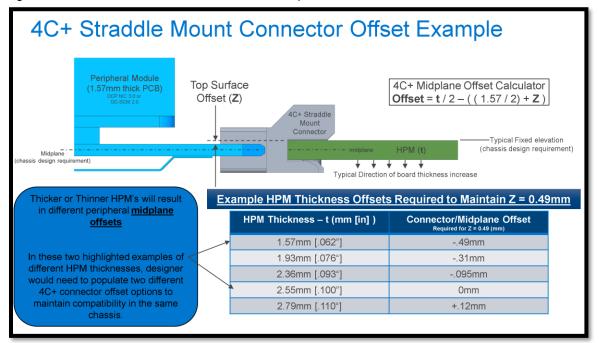

Designers should consider that variations in HPM thickness can result in variation of the offset locations of OCP NIC R3.0 and DC-SCM R2.0 peripherals (relative to fixed chassis openings).

A common chassis design intended to support two different thickness HPMs may have to populate different 4C+ connector offsets.

Designers may consult with vendors of SFF-TA-1002 4c+ to determine best options for their chassis application. See **Figure 6. HPM thickness and Straddle Mount Peripheral Offsets** below

Table 2. Board and Chassis Stackup Scenarios

| (Dimensions in mm)        | 1<br>HPM<br>Height | 2<br>HPM Thickness | 3<br>Backplate | 5<br>Gap<br>Backplate<br>to Base<br>Chassis |

|---------------------------|--------------------|--------------------|----------------|---------------------------------------------|

| Typical Nominal Range     | 5.0 -<br>5.86      | 1.57 - 3.18        | 2.0 – 2.6      |                                             |

| Scenario 1 Nominal        | 5.2                | 2.6                | 2.2            | 0.4mm                                       |

| Scenario 2 Nominal        | 5.86               | 3.18               | 2.6            | 0.08mm                                      |

| Worst case Gap 5 scenario | 5.5                | 3.5                | ~2.0mm         | 0                                           |

NOTE: Gap 4 not shown as it depends on customer chassis geometry

#### 465 Figure 6. HPM thickness and Straddle Mount Peripheral Offsets

#### 10.4. HPM to Chassis Retention

The HPM and Chassis-to-Board Bracket assembly requires retention to the chassis base.

There shall be a hole required in board to be used for HPM retention to the chassis, located at the required location in Figure 7 below. The hole is sized for common retention methods such as plungers, thumbscrews, etc.

Example Hardware

Figure 7. HPM Assembly to Chassis Retention Enablement

475

480

# 10.4.1. Keepout Zone for Retention Hardware <u>A keepout zone shall be implemented on both topside and bottom side around the Retention</u> Hardware hole.

The Primary (or Topside) KOZ is defined in **Section 10.14**, **Figure 20**. **Zones for Primary Side Component Height Restrictions**. For Secondary side KOZ, refer to **Section 10.15**, **Figure 22**. **HPM Secondary Side HPM Zero-Height Keepout Zones**

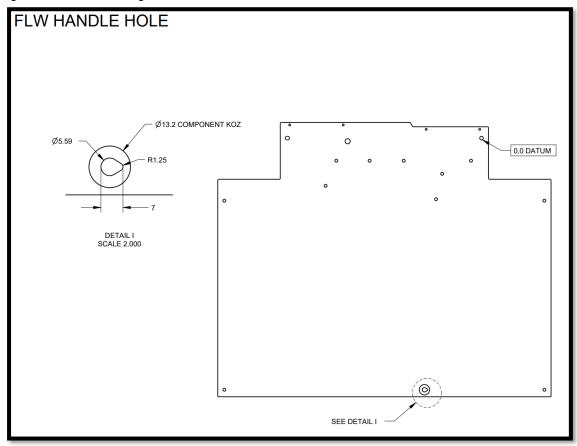

#### 10.5. HPM Handle Hole

The FLW HPM shall require a hole interface to a mechanical handle near the Far Side Edge.

This handle solution may be implemented with but not limited to a plastic handle. Example is shown in **Figure 8**.

Figure 8. HPM Handling Feature

The HPM Handle Hole is shown in **Figure 9**. The location of the hole on the Far side is not specified but should be placed considering Compute Core details, such as Far High-Speed IO cabling, and Thermal solution keepout. To balance handling of board with chassis retention feature (near DC-SCM R2.0), it is preferred to place the handle feature to right half of the HPM. The hole geometry for board handle shall follow the required dimensions and KOZ in **Figure 9**.

495 Figure 9. HPM Handling Feature Detail

#### **Implementors Note:**

The HPM Handle Hole may also be considered a mounting hole for structural purposes. Platform designers should ensure their handle design supports the HPM. For example, a designer does NOT need to place a board mounting hole near the HPM Handle Hole.

#### 10.6. OCP NIC R3 and DC-SCM R2 at Near Edge Locations

<u>The HPM Shall place the OCP NIC R3 and DC-SCM R2 at the locations defined by the centerline location of each of the connector subsystems in **Figure 10**. For further details of how the connector centerlines are defined, refer to SFF-TA-1002 specification.</u>

Figure 10. Centerline Locations of OCP NIC R3.0 and DC-SCM R2.0

500

505

#### 10.7. Platform Custom Zone

The Platform Custom Zone is defined as the Near Edge between the OCP NIC R3 and DC-SCM R2. This area is intentionally undefined, so that System Designers may provide their desired features for the target platform. The specification will define some options that are considered common use cases, to promote greater compatibility between future HPMs.

#### 515

510

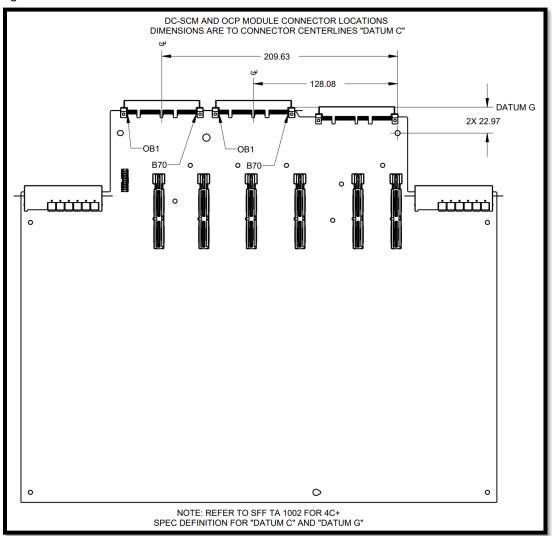

#### 10.7.1. Second OCP NIC R3

An HPM design may want to support a second OCP NIC R3. These HPM designs should follow the placement guidance **Figure 11** for the second connector.

520

Figure 11. Location for Second OCP NIC R3 in Platform Custom zone

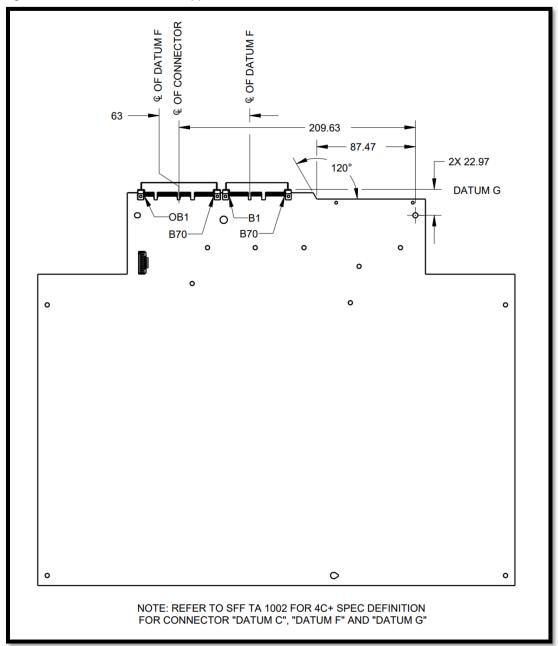

#### 10.7.2. OCP NIC R3 LFF

An HPM design may want to support an OCP NIC R3 LFF, instead of a single SFF. These HPM designs should follow the following placement guidance for the LFF connectors.

Figure 12. OCP NIC R3 LFF support

530

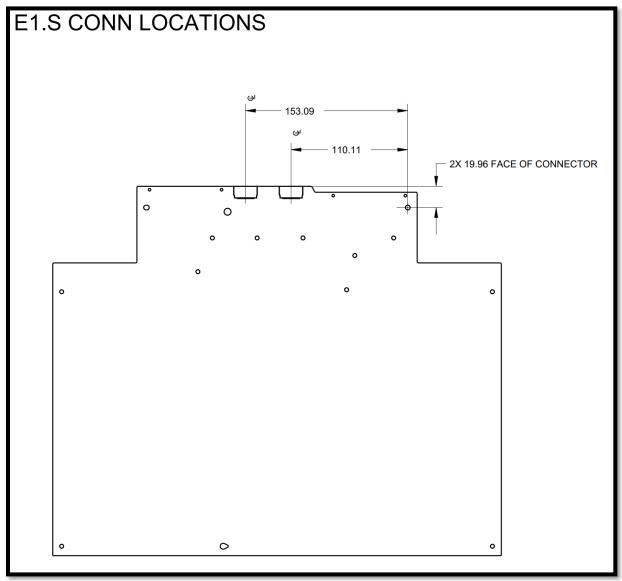

#### 10.7.3. Direct Dock E1.S

An HPM design may want to support direct docking E1.S (EDSFF) in the Platform Custom zone. These HPM designs should follow the following placement guidance for SFF-TA-1002, 1C connectors. See **Figure 13**. See M-PIC specification, chapter "E1.S Direct Attach Boot Storage" for complete connector and pinout guidance.

Figure 13. Direct Dock E1.S connector Enablement

540

535

#### 10.8. Control Panel Connector Locations

The HPM shall implement two instances of the M-PIC defined Control Panel connections as

shown in Figure 14. The Control Panel Connector details are further defined in M-PIC Section Reference: "Control Panel Interfacing".

Figure 14. Control Panel Connection Locations

550

## 10.9. Zone for PDB Management Connector Header

The HPM shall implement a PDB Management Connector Header. The connector must be placed in the HPM within the zone defined by Figure 15 (but can be depopulated in assembly BOM at a Design Specification level guidance). The PDB Management Connector details are further defined in M-PIC Section Reference: "PDB Management Connector Header".

Figure 15. PDB Management Connector Header Location

560

#### 10.10. Zone for Intrusion Switch and Internal Host USB3 Connection

<u>The HPM shall implement an internal USB3 connector.</u> The connector must be placed on the <u>HPM within the zone defined by **Figure 16**</u>. The USB Connector details are further defined in M-PIC Section Reference: "Internal Host USB3 Connector".

570

565

The HPM shall implement an intrusion switch connector. The connector must be placed on the HPM within the zone defined by **Figure 16**. The Intrusion Switch details are further defined in M-PIC Section Reference: "Intrusion Switch".

575 Figure 16. Intrusion and USB Connection Placement Zone

## 10.11. Boot Storage Peripheral Connection

The HPM is recommended to implement a Boot Storage Peripheral connector. The connector should be placed on the HPM within the zone defined by **Figure 17**. The Boot Storage Connector options and details are defined in M-PIC Section Reference: "Boot Storage".

Figure 17. Placement Zone for Boot Peripheral Connector

585

#### 10.12. Near Side IO Connectors

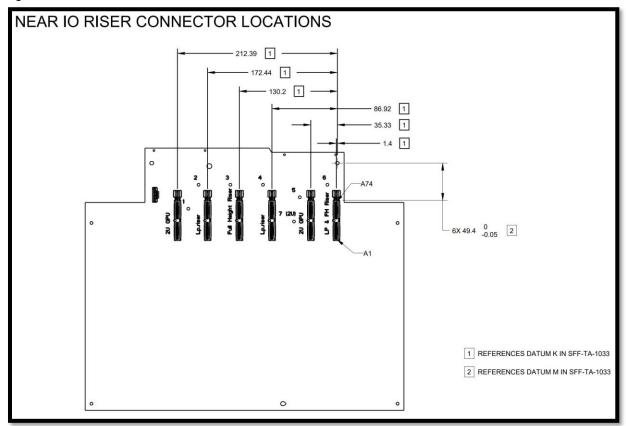

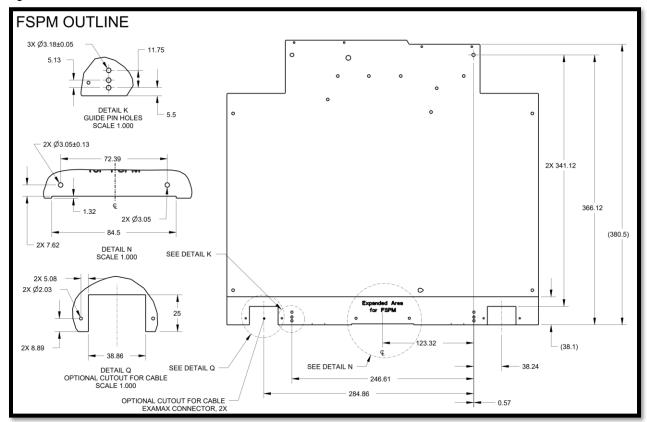

#### 10.12.1. Location of Near Side M-XIO Connectors

Note, that Near IO Requirements are mechanically focused to enable reuse of chassis and IO subsystems.

- 1) The required connector for Near IO Riser positions shall be SFF-TA-1033.

- a) This Near IO connector can support either rigid or cabled riser connections.

- 2) An HPM might not use all 6x Near IO positions, but designers are recommended to use maximum number of possible positions. <u>For Near IO implemented positions, the Near IO Connector shall be placed at locations defined in Figure 18.</u>

- 3) Additional and/or Alternate connectors used within the Near IO zone are allowed.

- Alternate connector types, location and use cases are outside the scope of this specification.

- 4) Adoption of the following allocation priority in is recommended. Following this recommendation may result in increased applicability and interoperability of the HPM.

Table 3. Table of IO allocation and connector priorities for Near IO connector SFF-TA-1033

| Recommended Priority | High speed connector housing | High speed routing | Power bay |

|----------------------|------------------------------|--------------------|-----------|

| 1                    | X16                          | X16                | power     |

| 2                    | X16                          | X8                 | power     |

| 3                    | X8                           | X8                 | Power     |

| 4                    | None                         | None               | Power     |

| 5                    | Depopulate all connectors    |                    |           |

610

600

605

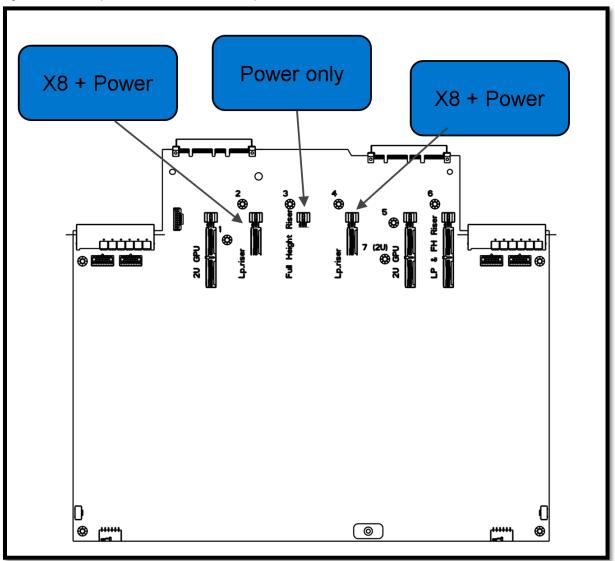

Figure 18. Near IO Connector Locations

615

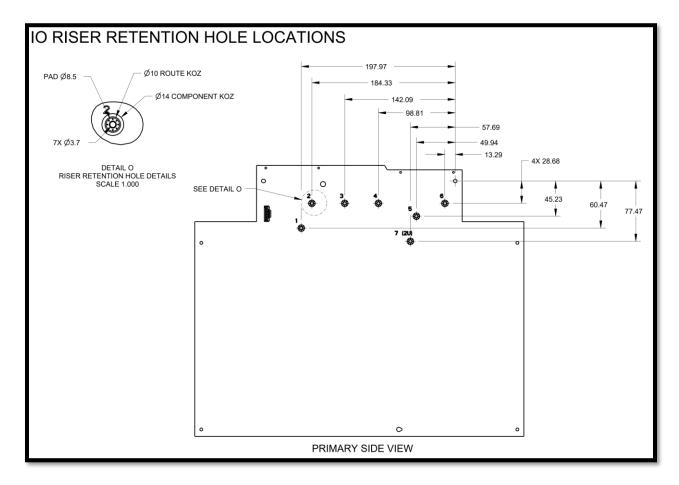

#### 10.12.2. Mounting Hole Requirements for Near Side Riser Retention

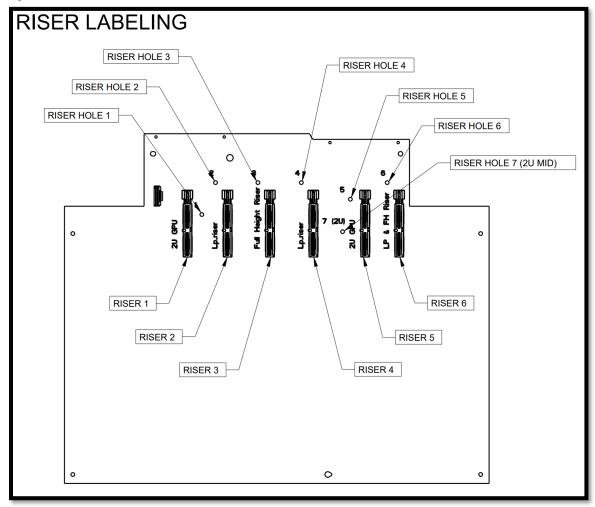

The HPM shall implement all mounting holes associated with each Near Side Riser location, as defined in Figure 19. These are intended to be used for mechanical module retention (such as PCIe Risers, or other modules that require mechanical retention in the HPM area). There is a total of 7x holes associated with the 6x IO connectors. These mounting holes are associated with both 1U and 2U PCIe Riser configurations. The riser retention holes are defined as a 3.7mm diameter hole, as shown in Figure 19, along with associated pads and component KOZ. Chassis Designers may choose the hardware and utilization method for riser retention.

Figure 19. 1U and 2U Near Side Riser Retention Enablement Holes

For further explanation on which mounting holes are associated with its Near IO connectors, see **Figure 42**. **Riser Retention Holes and Associated Near XIO Locations** in the Supplemental Information section.

630

#### 10.13. Far Side IO Connector Choice and Placement

The Far Side IO connector locations referenced in **Figure 1**. **Full Width HPM Layout Diagram** are not specified because they are all assumed to be cable-only connections and will not have major dependencies to chassis or subsystem reuse compatibility.

640 <u>High Speed IO connector choices for the Far Side shall meet the Height Restriction</u> requirements. The recommended connectors for use in the Far side are in **Table 4**

Table 4. Far Side HSIO Recommended Connectors

635

645

650

655

| Recommended Connector | Note                                                                      |  |

|-----------------------|---------------------------------------------------------------------------|--|

| SFF-TA-1016           | Must choose low profile variant                                           |  |

| SFF-TA-1026           | Appropriate due to low profile and ability to fit under thermal solutions |  |

## Implementors Note on SFF-TA -1016 Connectors

SFF-TA-1016 Connectors have mated height options above and below 12mm. System Designers should take these options into account with respect to the height restriction zones, if selecting SFF-TA-1016 connectors for an HPM.

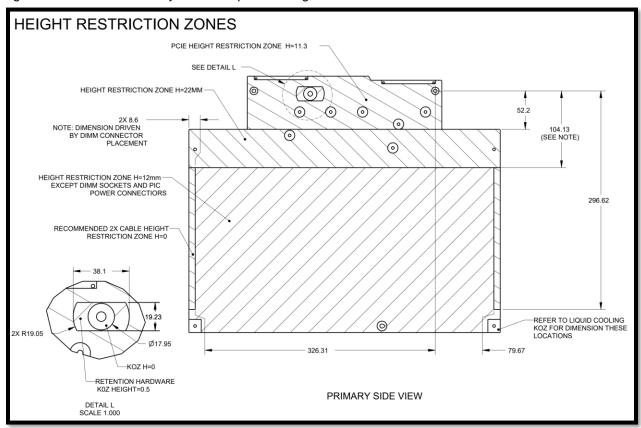

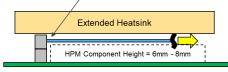

## 10.14. Primary Side Component Height Restriction Zones

A Component Height Restriction Zone shall be required, per Figure 20. Zones for Primary Side Component Height Restrictions; which applies to all soldered components. The exceptions are: DIMM sockets, special exceptions specified per zone, or zones that are Recommended.

The dimensions indicated in **Figure 20**. **Zones for Primary Side Component Height Restrictions** are maximum heights. <u>Component and assembly (solder) tolerances must be chosen to stay within the maximum height.</u>

The purpose for these height restrictions is to enable:

- Thermal solutions to interface to Compute Core items such as CPU and DIMMs (not shown). Thermal solutions in scope include extended air heatsinks and liquid cooling solutions.

- Cable routing channels along HPM edges

- PCIe CEM cards on 1U risers

- For thermal solutions, one must consider the allowable variance in numbers, types, and location of Compute Core items. Thus, a fixed 12mm for component height restriction in the Compute Core area is intended to allow air cooling heatsinks or liquid cooling hardware of any variance. DIMM sockets are exempt from the 12mm component height restriction. All other soldered

## board components must comply with exceptions noted in Figure 20. Zones for Primary Side Component Height Restrictions

If a cable connection (power, High speed IO, etc) is placed in the component height restriction zone, the max height restriction shall apply to the mated height of the plug and cable assembly, including component and assembly tolerances.

Figure 20. Zones for Primary Side Component Height Restrictions

670

665

675

#### **Implementation Note:**

The Height Restriction Zones defined in **Figure 20. Zones for Primary Side Component Height Restrictions** apply specifically to soldered circuit board components, mated connector heights or other mated assemblies of solder components. This does NOT apply to heatsinks of any kind, shrouds or other mechanical parts that are added to the board at a later integration stage.

It is assumed that items such as CPU heatsinks, VR heatsinks, and shrouds are all designed by System Designers. And thus, the height and location tradeoff between these items are assumed responsibilities of the System Designer and not the HPM designer. The HPM Designer should consider best practices when making component placement choices. This makes no assumptions on the compatibility of Chassis, Peripherals or Thermal solutions. For future chassis and HPM compatibility, a System Designer is advised NOT design elements that intersect with the Height Restriction zone (Fans, Heatsinks, Risers, etc).

Recommended Cable Zero Height Restriction Zone: It is strongly recommended to implement a keepout zone to left and right of outermost DIMM sockets with a minimum dimension to HPM edge of 8.6mm, shown as Cable Height Restriction Zone in **Figure 20. Zones for Primary Side Component Height Restrictions**.

This keepout is to enable HSIO cabling, power cabling and other platform infrastructure cabling to traverse from Near Side to Far Side zones, as needed by Platform Designers. (Designers should consider differences in DIMM socket widths from various vendors when determining DIMM placement.)

#### **Implementation Note:**

In some cases, a Compute Core design may only be able to deliver a desired capability by violating the cable keepout zone. By doing so, an HPM will cause issue with a platform's ability to cable High-Speed IO and Power delivery. In this case, a HPM Designer should make efforts to collaborate with Platform Designers on:

- 1. Increasing Near Side to Far Side power delivery and power egress capability to mitigate loss of power cabling

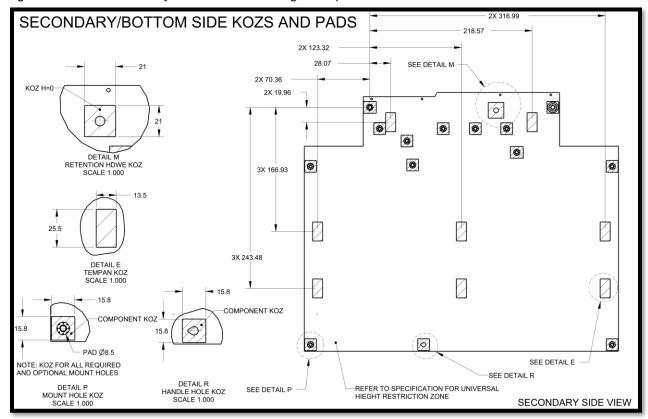

- 2. Identify available cabling space for High-Speed IO to meet a given platform configuration.