# Open CloudServer OCS Blade Specification Version 2.1

#### **Author:**

Mark Shaw, Director of Hardware Engineering, Microsoft

Martin Goldstein, Principal Hardware Engineer, Microsoft

Mark A. Shaw, Senior Hardware Engineering Manager, Microsoft

# **Revision History**

| Date       | Description                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 10/30/2014 | Version 2.0                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 2/3/2016   | <ul> <li>Version 2.1 – Major updates</li> <li>Support for full width blades</li> <li>Support for Future Intel® Xeon® Processor product family, 135W maximum</li> <li>Decreased HDD support to enable cooling for 135W processors</li> <li>Eliminated support for 10G networking</li> <li>Support for external SAS attached JBOD has been removed</li> </ul> |  |  |

© 2016 Microsoft Corporation.

As of October 30, 2014, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at <a href="http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0">http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0</a>

Microsoft Corporation.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at <a href="http://opencompute.org/licensing/">http://opencompute.org/licensing/</a>, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, noninfringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

CONTRIBUTORS AND LICENSORS OF THIS SPECIFICATION MAY HAVE MENTIONED CERTAIN TECHNOLOGIES THAT ARE MERELY REFERENCED WITHIN THIS SPECIFICATION AND NOT LICENSED UNDER THE OWF CLA OR OWFa. THE FOLLOWING IS A LIST OF MERELY REFERENCED TECHNOLOGY: INTELLIGENT PLATFORM MANAGEMENT INTERFACE (IPMI), I<sup>2</sup>C TRADEMARK OF PHILLIPS SEMICONDUCTOR. IMPLEMENTATION OF THESE TECHNOLOGIES MAY BE SUBJECT TO THEIR OWN LEGAL TERMS.

# **Contents**

| 1  | Overview of V2.1 Open CloudServer Specifications1 |                                              |    |  |  |

|----|---------------------------------------------------|----------------------------------------------|----|--|--|

| 2  | Intro                                             | Introduction to the Open CloudServer System1 |    |  |  |

| 3  | Blad                                              | le Block Diagram                             | 4  |  |  |

| 4  | Blad                                              | le Features                                  | 5  |  |  |

| 5  | Labe                                              | elling and Loading Guidelines                | 7  |  |  |

|    | 5.1                                               | Component Labelling                          | 7  |  |  |

|    | 5.2                                               | DIMMS                                        | 7  |  |  |

|    | 5.3                                               | PCIe Riser Slots                             | 8  |  |  |

|    | 5.4                                               | HDDs                                         | 8  |  |  |

| 6  | РСВ                                               | Stackup                                      | 8  |  |  |

| 7  | High                                              | n-Speed Interface Topologies                 | 10 |  |  |

|    | 7.1                                               | PCIe-to-Tray Backplane Mezzanine Topology    | 10 |  |  |

|    | 7.2                                               | Blade-to-NIC Mezzanine Topology              | 11 |  |  |

|    | 7.3                                               | PCIe M.2 Topology                            | 11 |  |  |

|    | 7.4                                               | Blade PCIe Riser Topology                    | 11 |  |  |

| 8  | Data                                              | asafe Storage Support                        | 12 |  |  |

|    | 8.1                                               | M.2                                          |    |  |  |

| 9  | Blad                                              | le Interconnects                             | 12 |  |  |

|    | 9.1                                               | Tray Backplane Interface                     |    |  |  |

|    | 9.1.1                                             |                                              |    |  |  |

|    | 9.1.2<br>9.1.3                                    |                                              |    |  |  |

|    | 9.1.4                                             |                                              |    |  |  |

|    | 9.2                                               | PCIe M.2 Interposer Modules                  |    |  |  |

|    | 9.3                                               | NIC Mezzanine Connector                      | 23 |  |  |

|    | 9.4                                               | SATA Cable Ports                             | 25 |  |  |

|    | 9.5                                               | SATA Power Connector                         | 25 |  |  |

|    | 9.6                                               | SATA HDD Connector                           | 26 |  |  |

|    | 9.7                                               | LED Cable Connector                          | 27 |  |  |

| 10 | 0 Man                                             | nagement Subsystem                           | 27 |  |  |

|    | 10.1                                              | Baseboard Management Controller              | 28 |  |  |

|    | 10.2                                              | DRAM                                         | 28 |  |  |

| -  | 10.3  | BMC Boot Flash                                                          | 29 |

|----|-------|-------------------------------------------------------------------------|----|

|    | 10.4  | BIOS Flash                                                              | 29 |

|    | 10.5  | Serial Links                                                            | 29 |

|    | 10.6  | PECI                                                                    | 29 |

|    | 10.7  | TPM Module                                                              |    |

|    | 10.8  | PCH/BMC I2C                                                             | 30 |

| -  | 10.8  | •                                                                       |    |

|    | 10.8  |                                                                         |    |

|    | 10.8  | .3 FRUID PROM                                                           | 31 |

|    | 10.8  | .4 Temperature Sensors                                                  | 31 |

|    | 10.8  | .5 Hot Swap Controller                                                  | 31 |

|    | 10.8  | .6 PCIe I2C                                                             | 34 |

|    | 10.9  | Intel® Node Manager Hardware Requirements                               | 34 |

|    | 10.10 | Blade LEDs                                                              | 35 |

|    | 10.1  | 0.1 Blade Power Status LED                                              | 35 |

|    | 10.1  | 0.2 Blade Attention LED                                                 | 36 |

|    | 10.11 | Debug Features                                                          | 36 |

| -  | 10.12 | Power Capping                                                           | 37 |

|    | 10.13 | Tray Mezzanine Power Control                                            | 38 |

| -  | 10.14 | Connector Quality                                                       | 38 |

|    | 10.15 | Overcurrent Protection                                                  |    |

| 11 |       | Mezzanine                                                               |    |

| 12 | Blad  | e Electrical Specifications                                             | 39 |

| -  | 12.1  | Input Voltage, Power, and Current                                       | 40 |

| -  | 12.2  | Current Interrupt Protection and Power, Voltage, and Current Monitoring | 40 |

| -  | 12.3  | Filtering and Capacitance                                               | 40 |

|    | 12.4  | Grounding and Return                                                    | 41 |

| 13 | Blad  | e Physical Specifications                                               | 41 |

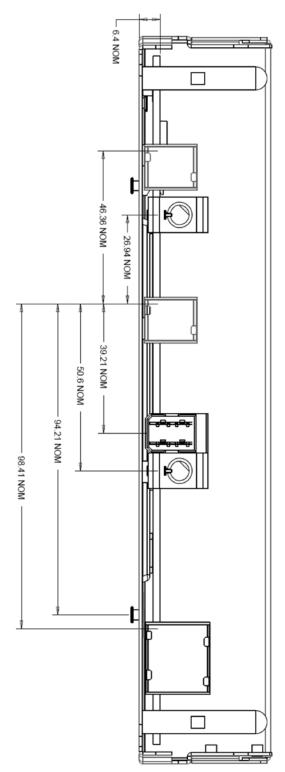

| -  | 13.1  | Blade Mechanical Control Outline                                        | 41 |

| -  | 13.2  | Volumetric Specifications                                               | 42 |

|    | 13.3  | Weight and Structure                                                    | 45 |

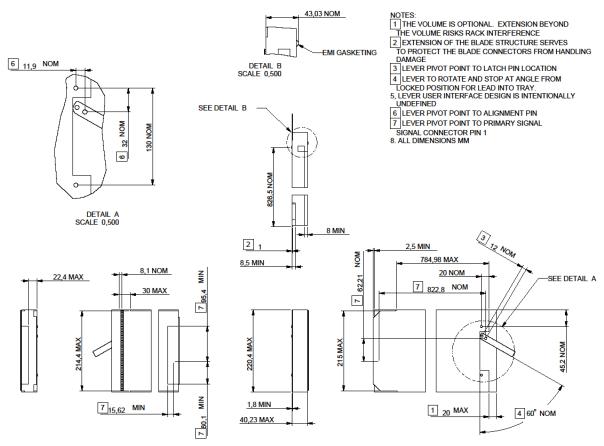

|    | 13.4  | Guiding and Latching Features                                           | 45 |

|    | 13.4  | .1 Latching Feature Identification                                      | 45 |

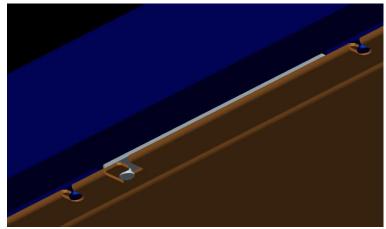

|    | 13.4  | .2 Guiding and Latching                                                 | 46 |

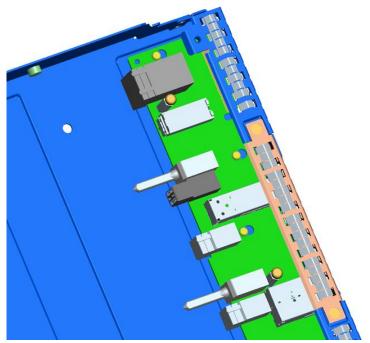

|    | 13.4  | .3 Electromagnetic Interference Mitigation                              | 48 |

| 14 | Blad  | e Thermal Design                                                        | 49 |

# **Table of Figures**

| Figure 1: View of OCS with rack                              | 2  |

|--------------------------------------------------------------|----|

| Figure 2: Second view of OCS                                 | 2  |

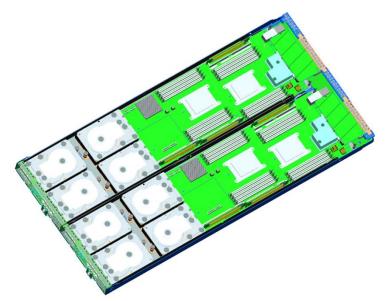

| Figure 3: V2.1 OCS half-width blade                          | 3  |

| Figure 4 V2.1 OCS full-width blade                           | 4  |

| Figure 5: Baseline configuration of blade                    | 5  |

| Figure 7 Major Component Labeling                            | 7  |

| Figure 8: PCB Stackup                                        | 9  |

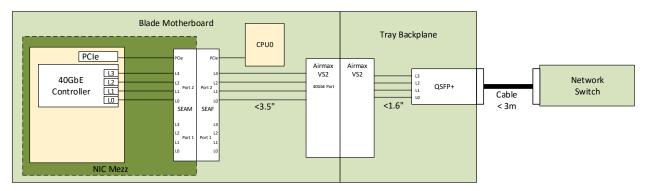

| Figure 9: CPU-to-tray backplane mezzanine PCIe link topology | 10 |

| Figure 10: NIC 40GbE Topology                                | 11 |

| Figure 11: PCIe M.2 topology                                 | 11 |

| Figure 12: Blade PCIe riser topology                         | 12 |

| Figure 13: AirMax power receptacle pinout arrangement        | 14 |

| Figure 14: Example of a coplanar blade signal connector      | 14 |

| Figure 15: AirMax VS2 pinout arrangement                     | 15 |

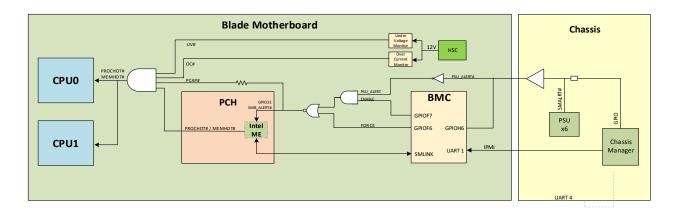

| Figure 16: Blade management block diagram                    | 28 |

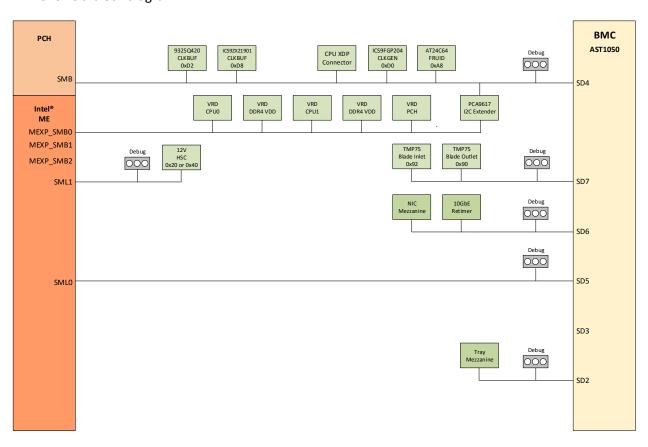

| Figure 17: PCH / BMC I2C block diagram                       | 30 |

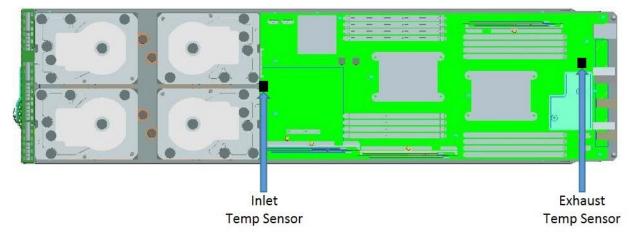

| Figure 18: Temperature sensor locations                      | 31 |

| Figure 19: HSC functional block diagram                      | 33 |

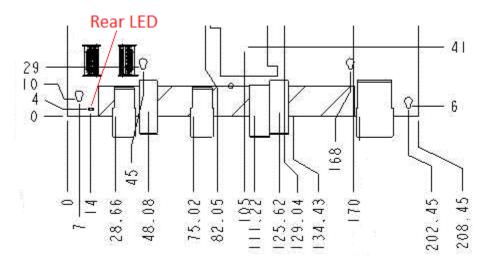

| Figure 20: Front blade LED locations                         | 35 |

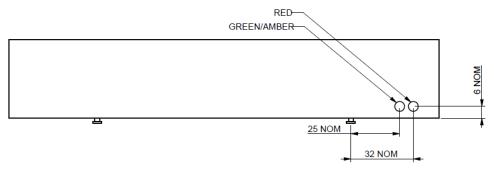

| Figure 21: Rear attention LED location                       | 35 |

| Figure 22. Power Capping Block Diagram                       | 38 |

| Figure 23: NIC block diagram                                 | 39 |

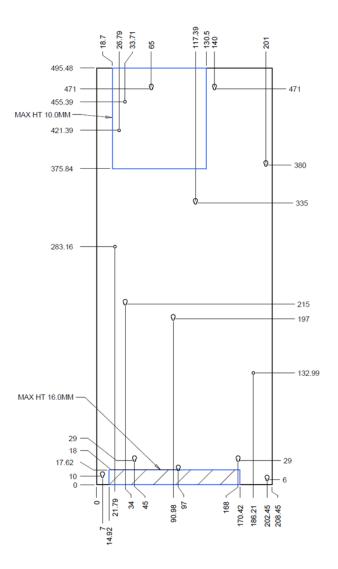

| Figure 24: Mechanical control outline                        | 42 |

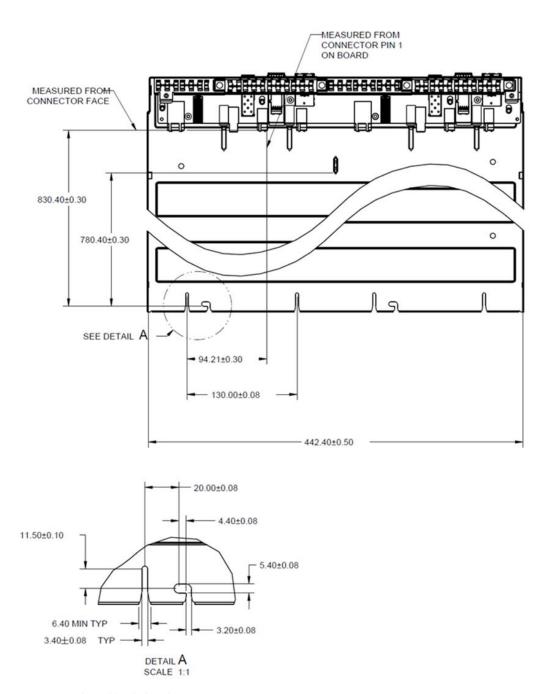

| Figure 25: Dimensions of the volume that holds the blade     | 43 |

| Figure 26: Two blades on a single tray                       | 43 |

| Figure 27: Blade-mounting envelope, rear view                | 44 |

| Figure 28: Front surface dimple                              | 45 |

| Figure 29: Guide and latch details, top view                 | 47 |

| Figure 30. Example of a front-blade guide and latch          | 48 |

| Figure 31: Example of a rear-blade guide pin                 | 48 |

| Figure 32: Tray with EMI enclosure, blade volume shown       | 49 |

| Figure 33: Blade EMI seal                                    | 49 |

|                                                              |    |

|                                                              |    |

| Table of Tables                                              |    |

| Table 1: List of specifications                              | 1  |

| Table 2: Blade features                                      | 6  |

| Table 3: Disk Drive SATA Port Assignments                    | 8  |

## Open Compute Project • Open CloudServer OCS Blade

| Table 4: PCIe port mapping                                         | 9  |

|--------------------------------------------------------------------|----|

| Table 5: Blade-to-tray backplane connector list                    | 12 |

| Table 6: Power connector pinout                                    | 14 |

| Table 7: AirMax VS2 PCIe connector pinout                          | 15 |

| Table 8: AirMax VS2 PCIe signal definitions                        | 16 |

| Table 9: PCIe bifurcation mapping                                  | 17 |

| Table 10: AirMax VS2 10/40GbE connector pinout                     | 18 |

| Table 11: AirMax VS2 40GbE signal definitions                      | 18 |

| Table 12: AirMax VS2 SAS connector pinout                          | 19 |

| Table 13: AirMax VS2 SAS signal definitions                        | 19 |

| Table 14: PCIe M.2 interposer connector pinout                     | 20 |

| Table 15: PCIe M.2 carrier signal definitions                      | 22 |

| Table 16: NIC mezzanine connector part numbers                     | 23 |

| Table 17: NIC mezzanine connector pinout                           | 24 |

| Table 18: NIC mezzanine signal descriptions                        | 24 |

| Table 19: SATA power connector signal names and current capacities | 26 |

| Table 20: SATA HDD connector pinout                                | 26 |

| Table 21: Signal interpretation                                    | 34 |

| Table 22: Blade power status LED description                       | 36 |

| Table 23: Blade attention LED description                          | 36 |

| Table 24: Input voltage range                                      | 40 |

| Table 25: Input power and current allocation                       | 40 |

# 1 Overview of V2.1 Open CloudServer Specifications

Table 1 lists the Open CloudServer (OCS) system specifications.

**Table 1: List of specifications**

| Specification title                                                     | Description                                                                                                            |  |  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Open CloudServer OCS Chassis<br>Specification Version 2.0               | Describes the hardware used in the Version 2.0 (V2.0) OCS system, including the chassis, tray, and systems management. |  |  |

| Open CloudServer OCS Blade<br>Specification Version 2.1                 | Describes the blade used in the V2.1 OCS system, including interconnect and blade hardware and blade management.       |  |  |

| Open CloudServer OCS Tray<br>Mezzanine Specification Version 2.0        | Describes the tray mezzanine card used in the V2.0 OCS system, including interconnect, hardware, and management.       |  |  |

| Open CloudServer OCS NIC<br>Mezzanine Specification Version 2.0         | Describes the Network Interface Controller (NIC) mezzanine card used in the V2.0 OCS system.                           |  |  |

| Open CloudServer OCS Chassis<br>Management Specification Version<br>2.0 | Describes the chassis manager command-line interface (CLI).                                                            |  |  |

This document is intended for designers and engineers who will be building blades for an OCS system.

# 2 Introduction to the Open CloudServer System

The V2.0 OCS system is a fully integrated rack of servers and IT equipment that is highly optimized and streamlined for large, web-scale deployments.

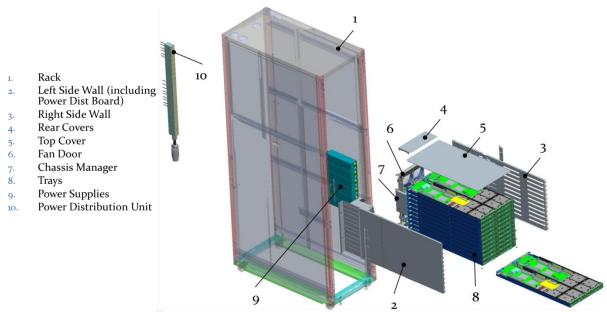

OCS is an off-the-shelf (OTS) commodity rack that is loaded with up to four modular chassis, each with trays, power supplies, power distribution, rack management, system fans, and two side-walls, as shown in Figure 1 and Figure 2.

Figure 1: View of OCS with rack

Figure 2: Second view of OCS

Each chassis supports 12 rack unit (EIA 310-E standard U or 1U, each 17.7" wide and 1.75" tall) trays that house up to 24 individual OCS blades (two blades per tray). Blades can be designed to use the full width of the tray. It is also possible to use multiple rack units to house a single tall blade, with certain restrictions.

Power, management, and networking are delivered through the tray backplane (TB) and the power distribution backplane (PDB). The tray backplane is located at the back of each tray. The power distribution backplane attaches vertically to the individual trays on one side and to the power

supply unit (PSU) on the other side. This arrangement reduces the current carrying requirements of the distribution board, eliminates cabling, and reduces costs.

Power and management signals are received from the PDB and distributed to the blades by Ethernet networking cables that pass through a blind-mate connector and are routed to attachments at the rear of the chassis. Note that running the cables through the rear of the blade eliminates the need to connect directly to the servers. Once provisioned, the network cabling should only be touched when a cable or switch fails or the typology is changed. The type and number of networking switches depends on the specific deployment.

Following are the significant changes from the previous generation (V2.0) of the blade:

- Support for full width blades

- Support for the future Intel® Xeon® Processor product family, 135W maximum

- Support for 8 M.2 Solid-State Drive (SSD) modules

- Support for a tray mezzanine on the tray backplane

- Decreased HDD support to enable cooling for 135W processors

- Eliminated support for 10G networking

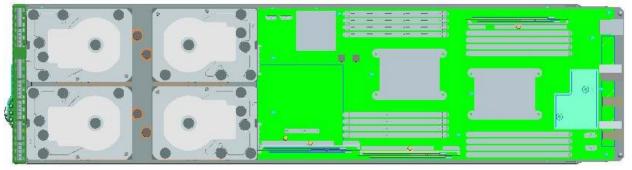

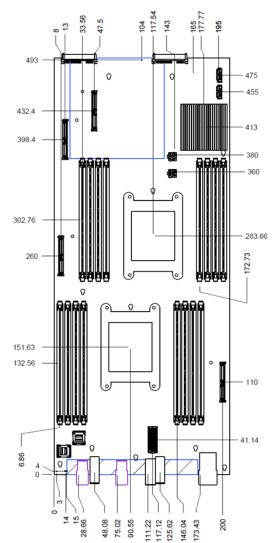

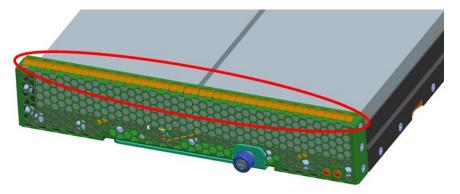

Figure 3 shows an example of a V2.1 OCS blade.

Figure 3: V2.1 OCS half-width blade

Figure 4 shows an example of a full-width blade V2.1 OCS blade.

Figure 4 V2.1 OCS full-width blade

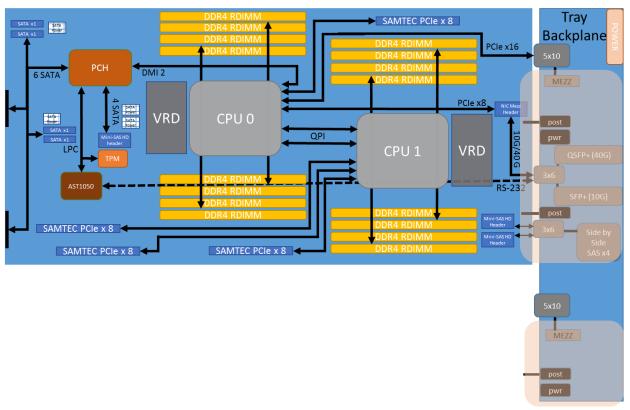

# 3 Blade Block Diagram

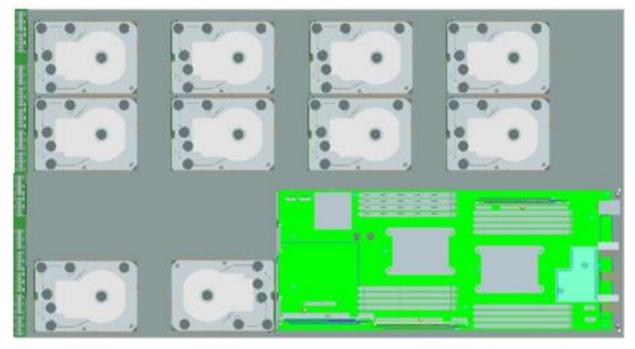

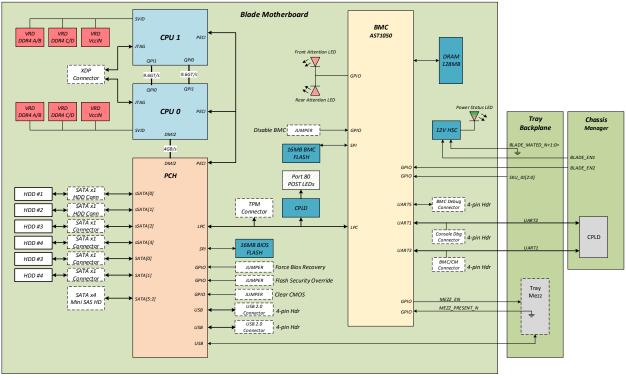

Figure 4 shows the baseline configuration for the blade. Note that this diagram is provided for illustration and is not to scale. Note also that all requirements are specified in the text of this document.

Figure 5: Baseline configuration of blade

Key features of the blade include:

- Support for up to four HDDs: two via motherboard connector, two via Serial AT Attachment (SATA) cables to the Platform Control Hub (PCH)

- Support for up to four SATA Small Form Factor (SFF) SSDs via SATA cable to the PCH

- Support for up to four Samtec Peripheral Component Interconnect Express (PCIe) x8 slots, with each slot capable of supporting two M.2 modules through an interposer board

- Support for a standard PCIe x8 card via a riser attached to the Samtec PCIe x8 edge connector

- Support for a Network Interface Controller (NIC) mezzanine card

- Support for a tray backplane mezzanine card

## 4 Blade Features

Table 2 lists features supported by the new blade design.

#### **Table 2: Blade features**

| Processor                                                                                                               |                                                                                                                  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Platform                                                                                                                | Future Intel® Xeon® Processor product family platform                                                            |  |  |  |  |

| СРИ                                                                                                                     | Future Intel® Xeon® Processor product family                                                                     |  |  |  |  |

| Sockets                                                                                                                 | Sockets Dual and single socket operation                                                                         |  |  |  |  |

| TDP Wattage                                                                                                             | Up to 135W                                                                                                       |  |  |  |  |

| Memory                                                                                                                  |                                                                                                                  |  |  |  |  |

| DIMM Slots                                                                                                              | 16 total DIMM slots<br>8 DIMMs per CPU<br>2 DIMMs per channel                                                    |  |  |  |  |

| DIMM Type                                                                                                               | Double data rate fourth generation (DDR4) Registered DIMM (RDIMM) with Error-Correcting Code (ECC)               |  |  |  |  |

| DIMM Speed                                                                                                              | DDR4-1866, DDR4-2133                                                                                             |  |  |  |  |

| DIMM Size                                                                                                               | 16GB, 32GB                                                                                                       |  |  |  |  |

| Capacities Supported                                                                                                    | 128GB, 192GB, 256GB, 512GB                                                                                       |  |  |  |  |

| On-board devices                                                                                                        |                                                                                                                  |  |  |  |  |

| PCH Intel® C610 series chipset                                                                                          |                                                                                                                  |  |  |  |  |

| SATA                                                                                                                    | 10 ports @ 6.0 Gb/s                                                                                              |  |  |  |  |

| Server management                                                                                                       |                                                                                                                  |  |  |  |  |

| Chipset Baseboard Management Controller (BMC)-lite BMC Aspeed AST1050, ser through the Chassis Manager                  |                                                                                                                  |  |  |  |  |

| Interface Representational State Transfer (REST) API Windows Management Interface (WMI) Open Management Interface (OMI) |                                                                                                                  |  |  |  |  |

| System firmware                                                                                                         | Command-Line Interface (CLI)  System firmware                                                                    |  |  |  |  |

| Version, Vendor                                                                                                         | Unified Extensible Firmware Interface (UEFI) 2.3.1                                                               |  |  |  |  |

| Security                                                                                                                | +                                                                                                                |  |  |  |  |

| PCI-Express expansion                                                                                                   | PCI-Express expansion                                                                                            |  |  |  |  |

| 4 Samtec PCle x8 slot                                                                                                   | Slots 1-3 supports M.2 interposer modules Slot 4 supports 1 PCI-Express (PCIe) x8 riser or M.2 interposer module |  |  |  |  |

| Tray Mezzanine Card                                                                                                     | Tray Mezzanine Card Supports PCIe x16 mezzanine with bifurcation down to PCIe 4x4                                |  |  |  |  |

|                                                                                                                         | •                                                                                                                |  |  |  |  |

| NIC Mezzanine Card Supports PCIe x8 mezzanine              |              |  |

|------------------------------------------------------------|--------------|--|

| Networking                                                 |              |  |

| NIC mezzanine card                                         | Single 40GbE |  |

| Tray mezzanine card Expansion slot funded by PCIe Gen3 x16 |              |  |

# **5** Labelling and Loading Guidelines

# **5.1 Component Labelling**

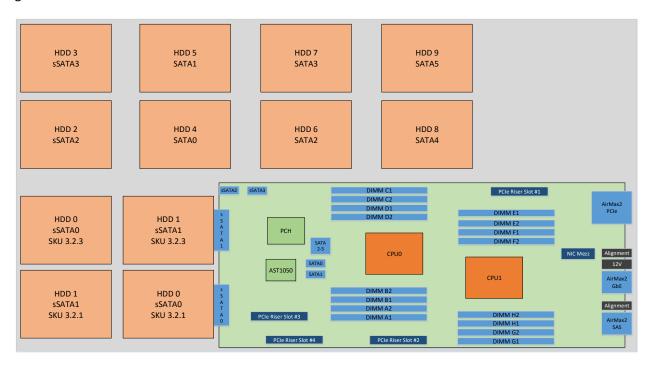

Figure 6 shows the approximate locations of major components on the blade motherboard, along with labelling information for referencing the CPU, DIMMs, PCIe riser slots, Hard-Disk Drives (HDDs), and SSDs. The sections that follow provide more detail about labelling and loading guidelines.

**Figure 6 Major Component Labeling**

## 5.2 DIMMS

Figure 6 shows how the DIMMs will be labelled. The DIMMs will be color coded to ease loading. Two colors will be used: one color for DIMMs A1,B1,C1,D1,E1,F1,G1,H1, and a second color for

DIMMs A2,B2,C2,D2,E2,F2,G2,H2. Color coding can use either the DIMM connector body or the latch. Note that color selection is at the discretion of the manufacturer.

## 5.3 PCIe Riser Slots

The blade contains four PCIe riser slots, as shown in Figure 6. The slots use Samtec connectors to provide PCIe connectivity and to meet the height restrictions of the PCIe modules. All slots can support M.2 modules. Slot #4 can support either an M.2 module or a standard PCIe card (via PCIe riser). The blade can support both low profile and full height PCIe cards.

### **5.4 HDDs**

HDDs shall be labelled as shown in Figure 6. A label detailing the HDD numbers shall be available on the frame for reference by service personnel. The drives shall be assigned SATA ports as shown in Table 3: Disk Drive SATA Port Assignments so that drive locations are common across WCS blades and so that the location of a failed drive can be readily serviced. Loading of the drives shall typically be governed by the configuration, but in the event of a configuration supporting partial loading, drives should be loaded in numerical order.

**Table 3: Disk Drive SATA Port Assignments**

| Disk Drive | 10 HDD Config |

|------------|---------------|

| sSATA0     | HDD 0         |

| sSATA1     | HDD 1         |

| sSATA2     | HDD 2         |

| sSATA3     | HDD 3         |

| SATA0      | HDD 4         |

| SATA1      | HDD 5         |

| SATA2      | HDD 6         |

| SATA3      | HDD 7         |

| SATA4      | HDD 8         |

| SATA5      | HDD 9         |

# 6 PCB Stackup

Figure 7 shows the recommended 10-layer dual stripline PCB stackup. The stackup uses standard FR4 PCB material. The PCB thickness requirement will be ~93mils.

| Layer Name |        | Layer Type |        | Thickness | Copper<br>Weight (oz) |

|------------|--------|------------|--------|-----------|-----------------------|

|            |        | Soldermask |        | 0.5       |                       |

| Signal 1   |        | SIGNAL     |        | 1.9       | 1.5                   |

|            |        | Prepreg    |        | 2.7       |                       |

| Plane 2    | GND    | VDD        | GND    | 1.3       | 1.0                   |

|            |        | Core       |        | 4.0       |                       |

| Signal 3   | SIGNAL | GND        | SIGNAL | 1.3       | 1.0                   |

|            |        | Prepreg    |        | 25.0      |                       |

| Signal 4   | GND    | SIGNAL     | GND    | 1.3       | 1.0                   |

|            |        | Core       |        | 4.0       |                       |

| Plane 5    | Power  | GND        | Power  | 2.6       | 2.0                   |

|            |        | Prepreg    |        | 4.0       |                       |

| Plane 6    | Power  | GND        | Power  | 2.6       | 2.0                   |

|            |        | Core       |        | 4.0       |                       |

| Signal 7   | GND    | SIGNAL     | GND    | 1.3       | 1.0                   |

|            |        | Prepreg    |        | 25.0      |                       |

| Signal 8   | SIGNAL | GND        | SIGNAL | 1.3       | 1.0                   |

|            |        | Core       |        | 4.0       |                       |

| Plane 9    | GND    | VDD        | GND    | 1.3       | 1.0                   |

|            |        | Prepreg    |        | 2.7       |                       |

| Signal 10  |        | SIGNAL     |        | 1.9       | 1.5                   |

|            |        | Soldermask |        | 0.5       |                       |

|            |        | Total      |        | 93.2      | +/-9                  |

Figure 7: PCB Stackup

Table 4 lists the recommended PCIe mapping for the design. This mapping is used to determine feasibility of stackup support for the PCIe routing. Note that this is informational only; actual implementation may vary.

**Table 4: PCIe port mapping**

| СРИ | PCIe bus | Destination              | Layer    |

|-----|----------|--------------------------|----------|

| 0   | PE1A     | PCIe riser slot #1       | 1 and 10 |

| 0   | PE1B     | PCIe riser slot #1       | 1 and 10 |

| 0   | PE2A     | NIC                      | 3 and 8  |

| 0   | PE2B     | NIC                      | 3 and 8  |

| 0   | PE2C     | Not used                 |          |

| 0   | PE2D     | Not used                 |          |

| 0   | PE3A     | Tray backplane mezzanine | 1 and 10 |

| 0   | PE3B     | Tray backplane mezzanine | 1 and 10 |

| 0   | PE3C     | Tray backplane mezzanine | 3 and 8  |

| 0   | PE3D     | Tray backplane mezzanine | 3 and 8  |

| СРИ | PCle bus | Destination        | Layer    |

|-----|----------|--------------------|----------|

| 1   | PE1A     | PCIe riser slot #4 | 3 and 8  |

| 1   | PE1B     | PCIe riser slot #4 | 3 and 8  |

| 1   | PE2A     | PCIe riser slot #2 | 1 and 10 |

| 1   | PE2B     | PCIe riser slot #2 | 1 and 10 |

| 1   | PE2C     | PCIe riser slot #3 | 1 and 10 |

| 1   | PE2D     | PCIe riser slot #3 | 1 and 10 |

| 1   | PE3A     | Not used           |          |

| 1   | PE3B     | Not used           |          |

| 1   | PE3C     | Not used           |          |

| 1   | PE3D     | Not used           |          |

# **7** High-Speed Interface Topologies

The sections that follow detail the electrical topologies for the high-speed interfaces connecting the external boards/assemblies to the blade.

# 7.1 PCIe-to-Tray Backplane Mezzanine Topology

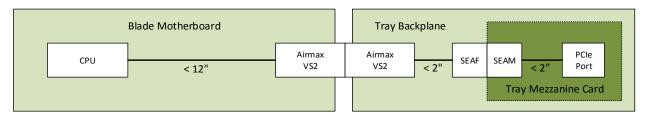

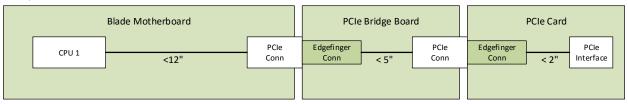

The blade contains a PCle x16 Gen3 interface to a mezzanine card on the tray backplane. This link connects the CPU to a PCle port on the mezzanine card. The block diagram in Figure 8 shows the connector interfaces and net length estimates for the tray backplane (TBP) and tray mezzanine card (TMC). The connector interface between the TBP and the TMC is defined in the *V2.0 Open CloudServer OCS Chassis Specification*. It is estimated that the blade motherboard can support <12" of trace between the CPU and the AirMax VS2 connector on the blade. (Note that this is an estimate derived for architectural planning and is not intended to replace signal integrity analysis.)

Figure 8: CPU-to-tray backplane mezzanine PCIe link topology

## 7.2 Blade-to-NIC Mezzanine Topology

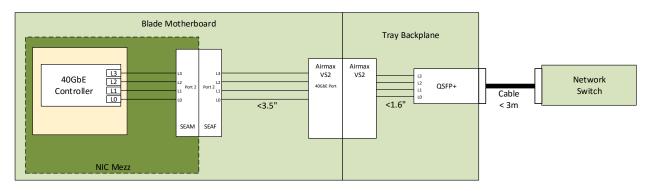

The blade contains a NIC mezzanine card to provide small form-factor pluggable (SFP+) and Quad SFP (QSFP+) cable connectivity to the network switch, as shown in Figure 9. It is expected that this topology will require a retimer on the blade motherboard close to the AirMax VS2 connector to support the SFP+.

Figure 9: NIC 40GbE Topology

## 7.3 PCIe M.2 Topology

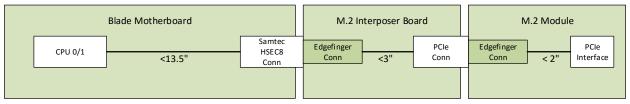

The blade contains a PCle Gen3 interface to an M.2 SSD module. The block diagram in Figure 10 shows the connector interface for this topology. It is estimated that the blade can support <13.5" of trace between the CPU and the HSEC8 high-speed edge card connector on the blade. (Note that this is an estimate derived for architectural planning and is not intended to replace signal integrity analysis.)

Figure 10: PCIe M.2 topology

# 7.4 Blade PCIe Riser Topology

The blade contains a PCIe Gen3 interface to standard PCIe card through a riser bridge board. The block diagram in Figure 11 shows the connector interface for this topology. It is estimated that the blade can support <12" of trace between the CPU and the standard PCIe connector on the blade. (Note that this is an estimate derived for architectural planning and is not intended to replace signal integrity analysis.)

Figure 11: Blade PCIe riser topology

# 8 Datasafe Storage Support

The design will support datasafe storage solutions. A datasafe storage device is a device that contains nonvolatile storage backup for volatile memory. Backup power for these devices can be supplied by a device local energy source such as a lithium battery or Pfail circuit (M.2. Supported datasafe devices include:

#### • M.2

Uses device local PFAIL circuit. Save initiated by PERST#.

#### 8.1 M.2

The design will support M.2 storage in PCle SLOTS 1-4. If the M.2 contains a local PFAIL solution, the solution will reside within the volume space designated for the M.2 module.

# 9 Blade Interconnects

The tray (or other supporting infrastructure) provides the electrical interface to the blade using the connectors listed in Table 5 (or their functional equivalents). Note that the choice of these connectors is based on a coplanar PCB for power and network distribution.

Table 5: Blade-to-tray backplane connector list

| Qty | Connector description                                                          | Blade connector<br>Manufacturer Part Number<br>(MPN) | TBP mating connector MPN                    |

|-----|--------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------|

| 1   | AirMax VS power header, 1x2                                                    | (FCI) 10028918-001LF<br>(or equivalent)              | (FCI) 10052620-4555P00LF<br>(or equivalent) |

| 2   | AirMax VS2 R/A header —3 pair x 6 column, 54 contact, 2mm spacing, 17mm pitch, | (FCI) 10123543-101LF<br>(or equivalent)              | (FCI) 10122643-101LF<br>(or equivalent)     |

| 1   | AirMax VS2 R/A header —5 pair x 10 column, 150                                 | (FCI) 10123529-101LF<br>(or equivalent)              | (FCI) 10122665-101LF<br>(or equivalent)     |

| Qty | Connector description                               | Blade connector<br>Manufacturer Part Number<br>(MPN) | TBP mating connector MPN                |  |

|-----|-----------------------------------------------------|------------------------------------------------------|-----------------------------------------|--|

|     | contact, 2mm spacing, 17mm pitch                    |                                                      |                                         |  |

| 2   | Guide pin receptacle—<br>10.8mm right angle, 0° key | (FCI) 10037912-101LF<br>(or equivalent)              | (FCI) 10044366-101LF<br>(or equivalent) |  |

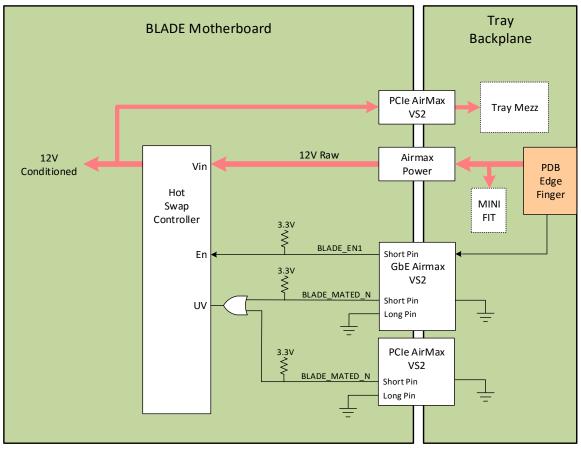

The chassis will provide electrical power and signaling to the tray. The tray will provide power to the blade. The blade interface to the tray backplane will provide power and high speed signaling for the tray mezzanine card on the tray backplane.

The interface to the tray backplane from a motherboard shall consist of four connectors:

- 1. An AirMax power connector for sourcing 12V power from PDB to blade motherboard.

- 2. An AirMax VS2 5x10 primarily to interface PCle x16 Gen 3 to the tray backplane.

- 3. An AirMax VS2 3x6 to interface 10GbE and management signals to the tray backplane.

- 4. An AirMax VS2 3x6 primarily to interface SAS channels to the tray backplane.

The total amount of force required to mate the blade to the tray backplane will not exceed 18.6 pounds throughout the expected service life of the connector set. With the leverage provided by the latch at the face of the blade, the force required will not exceed 3.15 pounds. The retention force of the connectors is a minimum of 5.66 pounds, which equates to 0.94 pounds minimum force at the latch.

## 9.1 Tray Backplane Interface

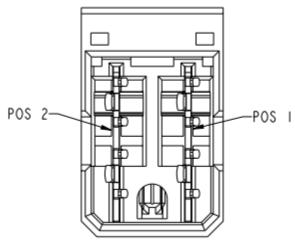

The power connector used is in the FCI AirMax VS connector family. Figure 12 shows the power connector layout.

Figure 12: AirMax power receptacle pinout arrangement

Table 6 shows the power receptacle pinout

**Table 6: Power connector pinout**

| Pin        | Signal name | Capacity (in A) |

|------------|-------------|-----------------|

| Position 1 | GND         | 40A             |

| Position 2 | 12V supply  | 40A             |

The maximum power that can be delivered to a blade through this connector is 480W, assuming the connector supports 40A with 30°C rise. Above this current, the Hot Swap Controller (HSC) should disable power to protect the hardware.

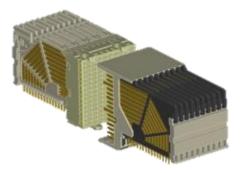

The signal connectors used are from the FCI AirMax VS2. Figure 13 shows an example of an AirMax coplanar connector pair.

Figure 13: Example of a coplanar blade signal connector

There are three AirMax connectors interfacing the blade to the tray backplane:

#### AirMax VS2 5x10 connector

This connector is primarily responsible for interfacing PCIe x16 Gen 3 from the blade CPU to the tray mezzanine card on the tray backplane.

#### • AirMax VS2 3x6 connector

This connector is responsible for interfacing 10GbE, 40GbE, and management signals from the Blade to the tray backplane. This connector is mate compatible with the V1.0 Open CloudServer blade.

#### • AirMax VS2 3x6 connector

This connector is primarily responsible for interfacing eight 12G SAS channels to the tray backplane for storage expansion. This connector is mate compatible with the V1.0 Open CloudServer blade.

The previous-generation blade used the AirMax VS 3x6 connector. Note that the VS and VS2 family connectors are plug-in compatible.

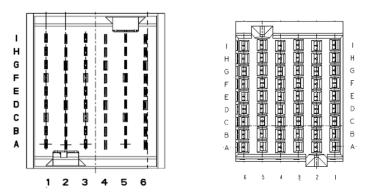

The AirMax connector is organized as a grid, with rows A through L and columns 1 through 10. Note that the columns flip from header to receptacle so that the mated pairs match. Figure 14 shows the signal connector layout, with the blade header on the left and the tray backplane receptacle on the right.

Figure 14: AirMax VS2 pinout arrangement

#### 9.1.1 AirMax VS2 PCle Connector

Table 7 shows the signal breakout for the AirMax PCIe header.

Table 7: AirMax VS2 PCIe connector pinout

| GND       | O.K_100M_P+0  | GND                | POIE_T2B_RX_DP<1> | GND                 | POIE_T28_RX_DPk3>  | GND                | PCIE_T2B_RX_DP<5>  | GND                | PCIE_T28_RX_DPx7>  | Α |

|-----------|---------------|--------------------|-------------------|---------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---|

| USB+      | OLK_100M_Nx0> | PCIE_T2B_RX_DP+O>  | PCIE_T2B_RX_DN<1> | PCIE_T2B_RX_DP<2>   | PCIE_T2B_RX_DNk3>  | PCIE_T2B_RX_DP<4>  | PCIE_T2B_RX_DN-5>  | PCIE_T2B_RX_DP<6>  | PCIE_T2B_RX_DN-7>  | В |

| USB-      | GND           | PCIE_T2B_RX_DN-cb- | GND               | PCIE_T2B_RX_DN<2>   | GND                | PCIE_T2B_RX_DN <4> | GND                | PCIE_T2B_RX_DN <6> | GND                | С |

| GND       | OLK_100M_P<1> | GND                | PCIE_T2B_RX_DPk9> | GND                 | POE_T2B_RX_DP<11>  | GND                | PG E_T2B_RX_DP<13> | GND                | PG E_T2B_RX_DP<15> | D |

| P5V_USB   | OLK_100M_Nx1> | PCIE_T28_RX_DP48>  | PCIE_T2B_RX_DN<9> | PCIE_T2B_RX_DP<10>  | PGE_T2B_RX_DN-11>  | PO E_T2B_RX_DP<12> | PGE_T28_RX_DN-13>  | PO E_T2B_RX_DP<14> | PGE_T2B_RX_DN-15>  | E |

| GND       | GND           | PCIE_T2B_RX_DN <8> | GND               | PCIE_T2B_RX_DN-4.0> | GND                | PCIE_T2B_RX_DN-12> | GND                | POE_T2B_RX_DN-14>  | GND                | F |

| GND       | OLK_100M_P<2> | GND                | RSVD              | GND                 | MEZZ_SCL           | GND                | PGE_CFG_ID0        | GND                | PCIE_RESET_N-8>    | G |

| GND       | CLK_100M_N-2> | RSVD               | RSVD              | MEZZ PRESENT N      | MEZZ_EN            | POE WAKE N         | POE_CFG_ID1        | PO E RESET N<1>    | PCIE_RESET_N-2>    | н |

| P12V_MEZZ | GND           | RSVD               | GND               | BLADE_MATED_N       | GND                | MEZZ_SDA           | GND                | PO E_RESET_N (O)   | GND                | 1 |

| P12V_MEZZ | OLK_100M_P-3> | GND                | PCIE_B2T_TX_DP<1> | GND                 | PCIE_B2T_TX_DP <3> | GND                | PCIE_B2T_TX_DPx5>  | GND                | PCIE_B2T_TX_DP+7>  | J |

| P12V_MEZZ | CLK_100M_Nd>  | PCIE_B2T_TX_DPx0x  | PCIE_BZT_TX_DNx1> | PCIE_B2T_TX_DP<2>   | PCIE_BZT_TX_DNx3>  | PCIE_B2T_TX_DP<4>  | PCIE_B2T_TX_DNx5x  | PCIE_B2T_TX_DP<6>  | PCIE_B2T_TX_DNx7>  | K |

| P12V_MEZZ | GND           | PCIE_BZT_TX_DNx0x  | GND               | PCIE_B2T_TX_DNx2>   | GND                | PCIE_B2T_TX_DNx4>  | GND                | PCIE_B2T_TX_DNx6>  | GND                | L |

| GND       | GND           | GND                | PCIE_B2T_TX_DP49> | GND                 | POE_B2T_TX_DP<11>  | GND                | POE_B2T_TX_DP<13>  | GND                | PGE_B2T_TX_DP<15>  | М |

| P12V_MEZZ | GND           | PCIE_B2T_TX_DPk8>  | PCIE_BZT_TX_DNk9> | PCIE_B2T_TX_DP<10>  | POE_B2T_TX_DN<11>  | PG E_82T_TX_DP<12> | PG E_B2T_TX_DN<13> | PGE_B2T_TX_DP<14>  | POE_B2T_TX_DN<15>  | N |

| P12V_MEZZ | GND           | PCIE_BZT_TX_DNx8>  | GND               | PCIE_B2T_TX_DN<10>  | GND                | PCIE_B2T_TX_DN<12> | GND                | PO E_B2T_TX_DN<14> | GND                | 0 |

| GND       | N/A           | GND                | N/A               | GND                 | N/A                | GND                | N/A                | GND                | N/A                | P |

| 10        | 9             | 8                  | 7                 | 6                   | 5                  | 4                  | 3                  | 2                  | 1                  |   |

Table 8 describes the signals used in this interface.

Table 8: AirMax VS2 PCIe signal definitions

| Bus type               | 1/0 | Logic                             | Definition for three pair, eight column                                                                                                                                                                                                                                                                                         |

|------------------------|-----|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCIE_B2T_TX_DP/N[15:0] | 0   | Current<br>Mode<br>Logic<br>(CML) | PCIe Gen 3 data from blade to tray mezzanine                                                                                                                                                                                                                                                                                    |

| PCIE_T2B_RX_DP/N[15:0] | 1   | CML                               | PCIe Gen3 data from tray mezzanine to blade                                                                                                                                                                                                                                                                                     |

| CLK_100M_P/N[3:0]      | 0   | CML                               | 100MHz PCIe Gen 3 clocks                                                                                                                                                                                                                                                                                                        |

| PCIE_RESET_N[3:0]      | 0   | 3.3V                              | PCIe reset signals                                                                                                                                                                                                                                                                                                              |

| WAKE_PCIE_N            | I   | 3.3V                              | PCIe wake signal                                                                                                                                                                                                                                                                                                                |

| PCIE_CFG_ID[1:0]       | I   | 3.3V                              | PCIe configuration ID bits Should be connected to General Purpose Input/Output (GPIO) on the PCH Should be pulled up with minimum 10K ohm resistor Has 1K pulldown on tray mezzanine $00 = 1 \text{ x}16 \text{ bifurcation}$ $01 = 2 \text{ x}8 \text{ bifurcation}$ $10 = 4 \text{ x}4 \text{ bifurcation}$ $11 = \text{N/A}$ |

| PCIE_B2T_TX_DP/N[15:0] | 0   | CML                               | PCIe Gen 3 data from blade to tray mezzanine                                                                                                                                                                                                                                                                                    |

| MEZZ_SDA/SCL           | I/O | 3.3V                              | I2C from blade BMC to tray mezzanine                                                                                                                                                                                                                                                                                            |

| MEZZ_PRESENT_N         | I   | 3.3V                              | Indicates tray mezzanine card is installed This signal should be pulled up on the blade and grounded on the tray mezzanine card                                                                                                                                                                                                 |

| MEZZ_EN                | 0   | 3.3V                              | Enable for tray mezzanine card on-board power                                                                                                                                                                                                                                                                                   |

| Bus type      | 1/0 | Logic | Definition for three pair, eight column                              |

|---------------|-----|-------|----------------------------------------------------------------------|

| P12V_MEZZ     | 0   | 12V   | Tray mezzanine card 12V power from blade 12V HSC (3A)                |

|               |     |       | Indicates blade is mated to tray backplane through AirMax 5x10       |

| BLADE_MATED_N | I   | 3.3V  | Grounded on tray backplane                                           |

|               |     |       | Should be pulled up on blade and used to qualify 12V in-rush turn on |

| USBP/N        | 1/0 | CML   | USB 2.0 from blade                                                   |

| P5V_USB       | 0   | 5V    | 5V USB power (500mA)                                                 |

| RSVD          | - 1 |       | Reserved—do not connect                                              |

| GND           |     |       | Ground                                                               |

P12V\_MEZZ and P5V\_USB pins are assumed to support a derated 500mA per pin; therefore, P12V\_MEZZ supports a derated maximum of 3A, and P5V\_USB supports 500mA.

Table 9 shows how the reset and clock signals are mapped to support each of the bifurcation cases for PCIe to the tray mezzanine.

**Table 9: PCIe bifurcation mapping**

|                 | 1x16 | 2x8  |     | 4x4   |      |     |     |

|-----------------|------|------|-----|-------|------|-----|-----|

| SIGNAL NAME     | 15:0 | 15:8 | 7:0 | 15:12 | 11:8 | 7:4 | 3:0 |

| PCIE_RESET_N[0] | Х    | Х    |     | Х     |      |     |     |

| PCIE_RESET_N[1] |      |      | Х   |       | Х    |     |     |

| PCIE_RESET_N[2] |      |      |     |       |      | Х   |     |

| PCIE_RESET_N[3] |      |      |     |       |      |     | Х   |

| CLK_100M_P/N[0] | Х    | Х    |     | Х     |      |     |     |

| CLK_100M_P/N[1] |      |      | Х   |       | Х    |     |     |

| CLK_100M_P/N[2] |      |      |     |       |      | Х   |     |

| CLK_100M_P/N[3] |      |      |     |       |      |     | Х   |

## 9.1.2 AirMax VS2 10/40GbE Connector

Table 10 shows the pinout for the AirMax 10Gb/40Gb Ethernet header.

Table 10: AirMax VS2 10/40GbE connector pinout

| GND         | ETH40G_RX1P   | GND         | ETH40G_RX2P | GND           | ETH40G_TX3P | А |

|-------------|---------------|-------------|-------------|---------------|-------------|---|

| ETH40G_TX1P | ETH40G_RX1N   | ETH40G_TX2P | ETH40G_RX2N | ETH40G_RX3P   | ETH40G_TX3N | В |

| ETH40G_TX1N | GND           | ETH40G_TX2N | GND         | ETH40G_RX3N   | GND         | С |

| GND         | P3V3_QSFP     | GND         | ETH10G_SDA  | GND           | ETH10G_RXP  | D |

| ETH40G_RX0P | P3V3_QSFP     | ETH40G_SDA  | ETH10G_SCL  | RSVD          | ETH10G_RXN  | E |

| ETH40G_RX0N | GND           | ETH40G_SCL  | SKU_ID0     | SKU_ID2       | GND         | F |

| GND         | PSU_ALERT_N   | SERIAL_RX2  | SERIAL_RX1  | GND           | ETH10G_TXP  | G |

| ETH40G_TX0P | ETH40G_PRES_N | SERIAL_TX2  | SERIAL_TX1  | BLADE_EN1     | ETH10G_TXN  | н |

| ETH40G_TX0N | BLADE_MATED_N | SKU_ID1     | P3V3_QSFP   | ETH10G_PRES_N | GND         | Ī |

| 6           | 5             | 4           | 3           | 2             | 1           |   |

Table 11 describes the signals used in this interface. Note that 10G is no longer supported, but still defined in the connectors.

Table 11: AirMax VS2 40GbE signal definitions

| Bus type          | I/O | Logic | Definition for three pair, eight column                             |

|-------------------|-----|-------|---------------------------------------------------------------------|

| ETH40G_TX[3:0]P/N | 0   | CML   | 40Gb Ethernet from blade LOM to QSFP+ connector                     |

| ETH40G_RX[3:0]P/N | ı   | CML   | 40Gb Ethernet from QSFP+ connector to blade NIC mezz                |

| ENET_40G_SDA/SCL  | I/O | 3.3V  | I2C from Ethernet controller on blade to QSFP+ connector/cable      |

| ENET40G_PRES_N    | 1   | 3.3V  | Indicates presence of 40GbE cable from QSFP+ connector              |

| SKU_ID<2:0>       | ı   | 3.3V  | 3.3V Pu/Pd on TBP indicating the SKU of the tray backplane          |

| P3V3_QSFP         | 0   | 3.3V  | QSFP+ and SFP+ cable power                                          |

|                   |     |       | Indicates blade is mated to tray backplane through AirMax 3x6       |

| BLADE_MATED_N     | I   | 3.3V  | Grounded on tray backplane                                          |

|                   |     |       | Should be pulled up on blade and used to qualify 12V inrush turn on |

| SERIAL_TX[2:1]    | ı   | 3.3V  | Serial communication ports from the Chassis Manager (CM) to blade   |

|                   |     |       | Two nodes per blade from CM                                         |

| CEDIAL DV[2.4]    | 0   | 3.3V  | Serial communication port from blade to CM                          |

| SERIAL_RX[2:1]    | 0   | 3.3V  | Two nodes per blade from CM                                         |

| DIADE EN1         | ı   | 3.3V  | Blade enable signal from CM                                         |

| BLADE_EN1         |     | 3.3V  | Used to enable the 12V in-rush controller                           |

| Bus type    | I/O | Logic | Definition for three pair, eight column                                                                       |

|-------------|-----|-------|---------------------------------------------------------------------------------------------------------------|

| PSU_ALERT_N | ı   | 3.3V  | Power supply failure alert  This signal is active low (open drain) and should be pulled up on the motherboard |

| RSVD        | 1/0 |       | Reserved—do not connect                                                                                       |

| Ground      |     |       | Ground pins                                                                                                   |

#### 9.1.3 AirMax VS2 SAS Connector

Table 12 shows the pinout for the AirMax SAS connector. Connector #1 supports SAS lanes 1-8. Since external JBODs are no longer supported, this connector may be depopulated.

Table 12: AirMax VS2 SAS connector pinout

| GND      | SAS_TX6P | GND      | RSVD     | GND      | SAS_TX1P | А |

|----------|----------|----------|----------|----------|----------|---|

| SAS_RX8P | SAS_TX6N | RSVD     | RSVD     | SAS_RX3P | SAS_TX1N | В |

| SAS_RX8N | GND      | RSVD     | GND      | SAS_RX3N | GND      | С |

| GND      | SAS_RX6P | GND      | SAS_RX4P | GND      | SAS_RX1P | D |

| SAS_TX8P | SAS_RX6N | SAS_TX5P | SAS_RX4N | SAS_TX3P | SAS_RX1N | E |

| SAS_TX8N | GND      | SAS_TX5N | GND      | SAS_TX3N | GND      | F |

| GND      | SAS_TX7P | GND      | SAS_TX4P | GND      | SAS_TX2P | G |

| SAS_RX7P | SAS_TX7N | SAS_RX5P | SAS_TX4N | SAS_RX2P | SAS_TX2N | Н |

| SAS_RX7N | GND      | SAS_RX5N | GND      | SAS_RX2N | GND      | I |

| 6        | 5        | 4        | 3        | 2        | 1        |   |

Table 13 describes the signals used in this interface.

Table 13: AirMax VS2 SAS signal definitions

| Bus type    | 1/0 | Logic | Definition for three pair, eight column |

|-------------|-----|-------|-----------------------------------------|

| SAS_TX[8:1] | 0   | CML   | SAS 8-channels from Blade to SAS cable  |

| SAS_RX[8:1] | I   | CML   | SAS 8-channels from SAS cable to blade  |

| RSVD        | I/O |       | Reserved—do not connect                 |

| Ground      |     |       | Ground pins                             |

## 9.1.4 Connector Skew Compensation

Right-angle AirMax VS2 connector interfaces between the tray backplane and the blade motherboard will require signal delay compensation in the PCB to account for differences in pin length of a P/N differential pair in the mated connectors. The pin-pair skew can be obtained from the connector manufacturer.

Following are the skew compensation divisions between the blade motherboard and the tray backplane:

#### AirMax VS2 PCle connector

All skew compensation is contained on the blade motherboard.

#### • AirMax VS2 GbE connector

All skew compensation is contained on the Blade Motherboard.

#### • AirMax VS2 SAS connector

Half (50%) of skew compensation is contained on the blade motherboard. Skew compensation for the VS2 connector pair is divided equally between the blade motherboard and the tray backplane.

## 9.2 PCIe M.2 Interposer Modules

The blade will support the M.2 interposer module, a custom edge card that supports two M.2 SSD modules (Next Generation Form Factor [NGFF] cards) in the connectorized SSD socket 3 format per the PCIe M.2 specification.

The interposer edge card interfaces to the blade motherboard through a Samtec HSEC8-150-01-S-DV-A connector (or equivalent). The interposer module supports the 60mm, 80mm, and 110mm form factors (Type 2260, 2280, and 22110). To support two M.2 modules, the connector interface is designed to support two PCIe Gen3x4 interfaces as well as the SSD specific signals, per the PCIE M.2 specification.

The interface is also designed to support a standard PCIe x8 interface through a separate riser card. The bifurcation is communicated through the LINK\_WIDTH signal (Pin B3), which should be connected to the PCH. The PCIe card will not require I2C or Joint Test Action Group (JTAG) connections to the motherboard. Table 14 shows the pinout for supporting only the M.2 interposer module.

Table 14: PCIe M.2 interposer connector pinout

|     | Sic            | de B connector                |    |         | Side B connector         |

|-----|----------------|-------------------------------|----|---------|--------------------------|

| Pin | Name           | ne Description                |    | Name    | Description              |

| 1   | 12V            | 12V power                     | 2  | PRSNT1# | Hot plug presence detect |

| 3   | 12V            | 12V power                     | 4  | 12V     | 12V power                |

| 5   | LINK_WIDT<br>H | 0=1 x8, 1= 2x4<br>bifurcation | 6  | 12V     | 12V power                |

| 7   | GND            | Ground                        | 8  | GND     | Ground                   |

| 9   | REFCLK2+       |                               | 10 | CLKREQ1 | Ref clock request (OD)   |

|        | Si        | ide B connector                            |     |          | Side B connector         |

|--------|-----------|--------------------------------------------|-----|----------|--------------------------|

| Pin    | Name      | Description                                | Pin | Name     | Description              |

| 11     | REFCLK2-  | Module 2 reference clock differential pair | 12  | CLKREQ2  | Ref clock request (OD)   |

| 13     | GND       | Ground                                     | 14  | SUSCLK   | Suspend cock (32.768Khz) |

| 15     | 3.3V      | 3.3V power                                 | 16  | DAS/DSS# | Drive active indicator   |

| 17     | DEVSLP    | Device sleep                               | 18  | 3.3V     | 3.3V power               |

| 19     | 3.3V      | 3.3V power                                 | 20  | 3.3V     | 3.3V power               |

| 21     | WAKE#     | Ground                                     | 22  | PERST#   | PCle reset               |

| 23     | 3.3V STBY | 3.3V standby power                         | 24  | GND      | Ground                   |

| 25     | GND       | Ground                                     | 26  | REFCLK1+ | Module 1 reference clock |

| 27     | PETp(0)   | Transmitter module 1                       | 28  | REFCLK1- | differential pair        |

| 29     | PETn(0)   | lane 0 differential pair                   | 30  | GND      | Ground                   |

| 31     | GND       | Ground                                     | 32  | PERp(0)  | Receiver module 1 lane 0 |

| 33     | PRSNT2#   | Hotplug detect                             | 34  | PERn(0)  | differential pair        |

| 35     | GND       | Ground                                     | 36  | GND      | Ground                   |

| 37     | PETp(1)   | Transmitter module 1                       | 38  | RSVD     | Reserved                 |

| 39     | PETn(1)   | lane 1 differential pair                   | 40  | GND      | Ground                   |

| 41     | GND       | Ground                                     | 42  | PERp(1)  | Receiver module 1 lane 1 |

| 43     | GND       | Ground                                     | 44  | PERn(1)  | differential pair        |

| 45     | PETp(2)   | Transmitter module 1                       | 46  | GND      | Ground                   |

| 47     | PETn(2)   | lane 2 differential pair                   | 48  | GND      | Ground                   |

| 49     | GND       | Ground                                     | 50  | PERp(2)  | Receiver module 1 lane 2 |

| 51     | GND       | Ground                                     | 52  | PERn(2)  | differential pair        |

| 53     | GND       | Ground                                     | 54  | GND      | Ground                   |

| Mechar | nical key |                                            |     |          |                          |

| 55     | PETp(3)   | Transmitter module 1                       | 56  | GND      | Ground                   |

| 57     | PETn(3)   | lane 3 differential pair                   | 58  | GND      | Ground                   |

| 59     | GND       | Ground                                     | 60  | PERp(3)  | Receiver module 1 lane 3 |

| 61     | RSVD      | Reserved                                   | 62  | PERn(3)  | differential pair        |

| 63     | PRSNT3#   | Hot plug detect                            | 64  | GND      | Ground                   |

| 65     | GND       | Ground                                     | 66  | RSVD     | Reserved                 |

|     | S       | ide B connector          |     |         | Side B connector        |

|-----|---------|--------------------------|-----|---------|-------------------------|

| Pin | Name    | Description              | Pin | Name    | Description             |

| 67  | PETp(4) | Transmitter module 2     | 68  | RSVD    | Reserved                |

| 69  | PETn(4) | lane 0 differential pair | 70  | GND     | Ground                  |

| 71  | GND     | Ground                   | 72  | PERp(4) | Receiver module2 lane 0 |

| 73  | GND     | Ground                   | 74  | PERn(4) | differential pair       |

| 75  | PETp(5) | Transmitter module 2     | 76  | GND     | Ground                  |

| 77  | PETn(5) | lane 1 differential pair | 78  | GND     | Ground                  |

| 79  | GND     | Ground                   | 80  | PERp(5) | Receiver module2 lane 1 |

| 81  | GND     | Ground                   | 82  | PERn(5) | differential pair       |

| 83  | PETp(6) | Transmitter module 2     | 84  | GND     | Ground                  |

| 85  | PETn(6) | lane 2 differential pair | 86  | GND     | Ground                  |

| 87  | GND     | Ground                   | 88  | PERp(6) | Receiver module2 lane 2 |

| 89  | GND     | Ground                   | 90  | PERn(6) | differential pair       |

| 91  | PETp(7) | Transmitter module 2     | 92  | GND     | Ground                  |

| 93  | PETn(7) | lane 3 differential pair | 94  | GND     | Ground                  |

| 95  | GND     | Ground                   | 96  | PERp(7) | Receiver module2 lane 3 |

| 97  | PRSNT4# | Hot plug detect          | 98  | PERn(7) | differential pair       |

| 99  | GND     | Ground                   | 100 | GND     | Ground                  |

Signals will satisfy the electrical requirements of the PCIe M.2 Specification and the PCIe Card Electromechanical Specification. Note that table includes columns to indicate whether a signal is required for use by the M.2 interposer module and/or the PCIe riser. Only slot 4 is required to support both the M.2 Interposer and PCIe Riser.

Table 15 provides a brief functional description of each signal.

Table 15: PCIe M.2 carrier signal definitions

| Bus type | 1/0 | Voltage | M.2 interposer | PCIe riser | Definition for three pair, eight column |

|----------|-----|---------|----------------|------------|-----------------------------------------|

| P12V     | 0   | 12V     |                | Х          | 12V Input                               |

| P3V3     | 0   | 3.3V    | Х              | Х          | 3.3V Input                              |

| WAKE#    | ı   | 3.3V    | х              | Х          | PCIe Wake for M.2 modules 1 and 2       |

| Bus type    | I/O | Voltage | M.2 interposer | PCIe riser | Definition for three pair, eight column                          |

|-------------|-----|---------|----------------|------------|------------------------------------------------------------------|

| PERST#      | 0   | 3.3V    | х              | Х          | PCIe Reset for M.2 modules 1 and 2                               |

| PETP/N(3:0) | 0   |         | Х              | Х          | PCIe Transmit to M.2 module 1                                    |

| PERP/N[3:0] | 0   |         | X              | Х          | PCIe Receiver from M.2 module 1                                  |

| REFCLK1LP/N | 0   |         | X              | Х          | Reference Clock for module 1                                     |

| PETP/N[7:4] | 0   |         | Х              | Х          | PCIe Transmit to M.2 module 2                                    |

| PERP/N[7:4] | 0   |         | Х              | Х          | PCIe Receive from M.2 module 2                                   |

| REFCLK2P/N  | 0   |         | Х              |            | Reference clock for module 2                                     |

| SUSCLK      | I   |         | х              |            | Suspend Clock for modules 1 and 2 (32.768Khz)                    |

| CLKREQ1     | I   |         | х              |            | Reference Clock Request for module 1                             |

| CLKREQ2     | I   |         | х              |            | Reference Clock Request for module 2                             |

| DEVSLP      | 0   |         | Х              |            | Device Sleep to M.2 modules 1 and 2 (should be pulled low on MB) |

| RSVD        | N/A |         | Х              | Х          | Reserved (do not connect)                                        |

| PRSNT[3:1]  | I/O |         | х              | х          | Present Should be connected on MB per PCIe specification         |

| GND         | I/O |         | Х              | Х          | Ground                                                           |

## 9.3 NIC Mezzanine Connector

The blade will support a single NIC mezzanine card. The mezzanine will interface to the blade through a Samtec SEAF-20-06.5-L-08-2-A-K-TR connector or equivalent.

Table 16 lists the compatible connectors.

Table 16: NIC mezzanine connector part numbers

| Manufacturer | Card connector MPN         | Motherboard connector MPN  |

|--------------|----------------------------|----------------------------|

| Samtec       | SEAM-20-03.5-L-08-2-A-K-TR | SEAF-20-06.5-L-08-2-A-K-TR |

| Molex        | 45970-2385                 | 45971-2385                 |

Table 17 shows the pinout for the NIC mezzanine connector.

Table 17: NIC mezzanine connector pinout

| 8   | CLK_100M_NIC_PE_DP | GND            | SMB_ALERT_N    | NIC_MEZZ_ID0 | PCIE_WAKE_N           | GND                   | PCIE_RESET_N          | GND                   | 1   |

|-----|--------------------|----------------|----------------|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----|

| 16  | CLK_100M_NIC_PE_DN | GND            | NWK2_PRESENT_N | SMB_SCL      | GND                   | P3E_CPU1_LAN_RX_DP<7> | GND                   | P3E_CPU1_LAN_TX_DP<0> | 9   |

| 24  | GND                | MEZZ_PRESENT_N | GND            | SMB_SDA      | GND                   | P3E_CPU1_LAN_RX_DN<7> | GND                   | P3E_CPU1_LAN_TX_DN<0> | 17  |

| 32  | NWK_2_TX0P         | GND            | NWK_1_TX1P     | GND          | P3E_CPU1_LAN_RX_DP<6> | GND                   | P3E_CPU1_LAN_TX_DP<1> | GND                   | 25  |

| 40  | NWK_2_TX0N         | GND            | NWK_1_TX1N     | GND          | P3E_CPU1_LAN_RX_DN<6> | GND                   | P3E_CPU1_LAN_TX_DN<1> | GND                   | 33  |

| 48  | GND                | NWK_2_TX1P     | GND            | NWK_1_TX2P   | GND                   | P3E_CPU1_LAN_RX_DP<5> | GND                   | P3E_CPU1_LAN_TX_DP<2> | 41  |

| 56  | GND                | NWK_2_TX1N     | GND            | NWK_1_TX2N   | GND                   | P3E_CPU1_LAN_RX_DN<5> | GND                   | P3E_CPU1_LAN_TX_DN<2> | 49  |

| 64  | NWK_2_TX2P         | GND            | NWK_1_TX3P     | GND          | P3E_CPU1_LAN_RX_DP<4> | GND                   | P3E_CPU1_LAN_TX_DP<3> | GND                   | 57  |

| 72  | NWK_2_TX2N         | GND            | NWK_1_TX3N     | GND          | P3E_CPU1_LAN_RX_DN<4> | GND                   | P3E_CPU1_LAN_TX_DN<3> | GND                   | 65  |

| 80  | GND                | NWK_2_TX3P     | GND            | NWK_1_RX1N   | GND                   | P3E_CPU1_LAN_RX_DP<0> | GND                   | P3E_CPU1_LAN_TX_DP<4> | 73  |

| 88  | GND                | NWK_2_TX3N     | GND            | NWK_1_RX1P   | GND                   | P3E_CPU1_LAN_RX_DN<0> | GND                   | P3E_CPU1_LAN_TX_DN<4> | 81  |

| 96  | NWK_2_RXOP         | GND            | NWK_1_RX2N     | GND          | P3E_CPU1_LAN_RX_DP<1> | GND                   | P3E_CPU1_LAN_TX_DP<5> | GND                   | 89  |

| 104 | NWK_2_RX0N         | GND            | NWK_1_RX2P     | GND          | P3E_CPU1_LAN_RX_DN<1> | GND                   | P3E_CPU1_LAN_TX_DN<5> | GND                   | 97  |

| 112 | GND                | NWK_2_RX1N     | GND            | NWK_1_RX3N   | GND                   | P3E_CPU1_LAN_RX_DP<2> | GND                   | P3E_CPU1_LAN_TX_DP<6> | 105 |

| 120 | GND                | NWK_2_RX1P     | GND            | NWK_1_RX3P   | GND                   | P3E_CPU1_LAN_RX_DN<2> | GND                   | P3E_CPU1_LAN_TX_DN<6> | 113 |

| 128 | NWK_2_RX2N         | GND            | NWK_1_TX0P     | GND          | P3E_CPU1_LAN_RX_DP<3> | GND                   | P3E_CPU1_LAN_TX_DP<7> | GND                   | 121 |

| 136 | NWK_2_RX2P         | GND            | NWK_1_TX0N     | GND          | P3E_CPU1_LAN_RX_DN<3> | GND                   | P3E_CPU1_LAN_TX_DN<7> | NWK2_I2C_SDA          | 129 |

| 144 | GND                | NWK_2_RX3N     | GND            | NWK_1_RX0P   | GND                   | NIC_MEZZ_ID1          | GND                   | NWK2_I2C_SCL          | 137 |

| 152 | NWK1_I2C_SDA       | NWK_2_RX3P     | GND            | NWK_1_RX0N   | GND                   | P3V3                  | P3V3_AUX              | P12V_AUX              | 145 |

| 160 | NWK1_I2C_SCL       | GND            | NWK1_PRESENT_N | GND          | P3V3                  | P3V3                  | P3V3_AUX              | P12V_AUX              | 153 |

Table 18 describes the signals used in this interface.

**Table 18: NIC mezzanine signal descriptions**

| Bus type                  | I/O | Logic | Definition                                              |

|---------------------------|-----|-------|---------------------------------------------------------|

| P3E_CPU1_LAN_RX_DP/N[7:0] | 1   | CML   | PCIe Gen3 from the NIC mezzanine to the CPU             |

| P3E_CPU1_LAN_TX_DP/N[7:0] | О   | CML   | PCIe Gen3 from the CPU to the NIC mezzanine             |

| CLK_100M_NIC_PE_DP/N      | О   | CML   | 100MHz PCIe clock                                       |

| PCIE_RESET_N              | 0   | 3.3V  | PCIe reset                                              |

| MEZZ_PRESENT_N            | I   | 3.3V  | Mezzanine present Should be GND on mezzanine            |

| NWK_1_TX[3:0]P/N          | I   | CML   | Port 1 10GbE transmit from mezzanine to tray backplane  |

| NWK_1_RX[3:0]P/N          | 0   | CML   | Port 1 10GbE receive from motherboard to tray backplane |

| NWK_2_TX[3:0]P/N          | I   | CML   | Port 2 40GbE transmit from mezzanine to tray backplane  |

| NWK_2_RX[3:0]P/N          | 0   | CML   | Port 2 40GbE receive from tray backplane to mezzanine   |

| SMB_ALERT_N               | I   | 3.3V  | I2C Alert from NIC mezzanine to BMC                     |

| NWK1_PRESENT_N            | О   | 3.3V  | Port 1 cable present indicator from tray backplane      |

| NWK1_I2C_SDA              | I/O | 3.3V  | Port1 I2C data to SFP+ cable                            |

| Bus type         | I/O | Logic | Definition                                         |

|------------------|-----|-------|----------------------------------------------------|

| NWK1_I2C_SCL     | I   | 3.3V  | Port 1 I2C clock to SFP+ cable                     |

| NWK2_PRESENT_N   | 0   | 3.3V  | Port 2 cable present Indicator from tray backplane |

| NWK2_I2C_SDA     | I/O | 3.3V  | Port 2 I2C data to QSFP+ cable                     |

| NWK2_I2C_SCL     | I   | 3.3V  | Port 2 I2C clock to QSFP+ cable                    |

| PCIE_WAKE_N      | I   | 3.3V  | PCIe wake                                          |

| SMB_SCL          | 0   | 3.3V  | I2C to BMC                                         |

| SMB_SDA          | 1/0 | 3.3V  | I2C to BMC                                         |

| NIC_MEZZ_ID[1:0] | I   | 3.3V  | NIC mezzanine ID Should connect to BMC             |

| P3V3             | О   | 3.3V  | 3.3V input power                                   |

| P3V3_AUX         | О   | 3.3V  | 3.3V auxiliary input power                         |

| P12V_AUX         | О   | 12V   | 12V input power                                    |

| Ground           |     |       | Ground pins                                        |

## 9.4 SATA Cable Ports

The board will include support for one x4 Mini-SAS HD connector, supporting the SFF-8643 (or equivalent) cable and four x1 SATA connectors for cabling SATA ports from the PCH to the HDDs and SSDs.

#### 9.5 SATA Power Connector

The board will include four 4-pin Mini-Fit® Jr 5566 series power connectors, P/N: Molex 5566-04A (or equivalent). Two connectors are intended to provide power to the Large Form Factor (LFF) HDDs and SSDs. Each connector is intended to provide cabled power to two drives. Each connector pin has a maximum 13A current capacity.