# Open CloudServer OCS Chassis Specification Version 2.0

Author: Mark Shaw, Director of Hardware Engineering, Microsoft

# **Revision History**

| Date       | Description |

|------------|-------------|

| 10/30/2014 | Version 2.0 |

© 2014 Microsoft Corporation.

As of October 30, 2014, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at <u>http://www.openwebfoundation.org/legal/the-owf-1-0-agreements/owfa-1-0</u>

Microsoft Corporation.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at <a href="http://opencompute.org/licensing/">http://opencompute.org/licensing/</a>, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, noninfringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

CONTRIBUTORS AND LICENSORS OF THIS SPECIFICATION MAY HAVE MENTIONED CERTAIN TECHNOLOGIES THAT ARE MERELY REFERENCED WITHIN THIS SPECIFICATION AND NOT LICENSED UNDER THE OWF CLA OR OWFA. THE FOLLOWING IS A LIST OF MERELY REFERENCED TECHNOLOGY: INTELLIGENT PLATFORM MANAGEMENT INTERFACE (IPMI), I<sup>2</sup>C TRADEMARK OF PHILLIPS SEMICONDUCTOR. IMPLEMENTATION OF THESE TECHNOLOGIES MAY BE SUBJECT TO THEIR OWN LEGAL TERMS.

# Contents

| 1 | Over  | view of V2.0 Open CloudServer Specifications1    |

|---|-------|--------------------------------------------------|

| 2 | Intro | duction to the Open CloudServer System1          |

| 3 | Chas  | sis Specification3                               |

|   | 3.1   | Chassis Physical Specification                   |

|   | 3.1.1 | Volumetric Specification4                        |

|   | 3.1.2 | Latching Features and Fasteners6                 |

|   | 3.1.3 | Power Distribution Unit Placement7               |

|   | 3.2   | Power Delivery                                   |

|   | 3.3   | Power Distribution Backplane                     |

|   | 3.4   | Tray Specifications                              |

|   | 3.4.1 | Volumetric Specifications10                      |

|   | 3.4.2 | Guiding and Latching                             |

|   | 3.5   | Tray Interconnect                                |

| 4 | Cool  | ing System Specifications16                      |

|   | 4.1   | Thermal Design Considerations                    |

|   | 4.2   | Airflow and Thermal Requirements                 |

|   | 4.3   | Fan Speed Control                                |

|   | 4.3.1 | Pulse-Width Modulation Input18                   |

|   | 4.3.2 | Fan Speed Correction for Altitude19              |

|   | 4.3.3 | Fan Speed Correction for Fan Failures20          |

|   | 4.3.4 | Sensor Failure                                   |

|   | 4.4   | Fan Failure21                                    |

|   | 4.4.1 | Fan Failure Rate21                               |

|   | 4.4.2 | Fan Repair21                                     |

|   | 4.5   | Thermal Considerations for the Blade             |

| 5 | Syste | ems Management                                   |

|   | 5.1   | Systems Management Connectivity23                |

|   | 5.2   | Chassis Manager Specifications                   |

|   | 5.2.1 | Communication Ports25                            |

|   | 5.2.2 | Power Control                                    |

|   | 5.2.3 | Chassis Manager Software and Programming Model27 |

|   | 5.2.4 | Blade Numbering27                                |

|   | 5.2.5 | Chassis LEDs                                     |

| 6 | Tray  | Backplane Specification                          |

|   | 6.1   | Tray Backplane Overview                          |

| 6.2   | 12V Power Distribution                    |    |

|-------|-------------------------------------------|----|

| 6.3   | SAS Channels                              | 31 |

| 6.4   | 10 Gb/40Gb Ethernet                       | 31 |

| 6.5   | Tray Mezzanine Card                       | 32 |

| 6.5.1 | L Chassis Management                      | 33 |

| 6.5.2 | 2 Guide Pins                              | 34 |

| 6.6   | Connector Pinouts and Signal Descriptions |    |

| 6.6.1 | PDB 12V Power Connector                   | 35 |

| 6.6.2 | 2 Blade 12V Power Connector               | 36 |

| 6.6.3 | Blade SAS Interface                       | 37 |

| 6.6.4 | Mini-SAS HD Connector                     | 38 |

| 6.6.5 | 5 Blade 10Gb Ethernet Connector           | 40 |

| 6.6.6 | 5 10GbE SFP+ Connector                    | 41 |

| 6.6.7 | 7 40GbE QSFP+ Connector                   | 42 |

| 6.6.8 | Blade PCIe Gen3 Connector                 | 44 |

| 6.6.9 | 9 Tray Mezzanine Card Connector           | 47 |

| 6.7   | 12V Power Cable                           | 49 |

| 6.8   | USB Cable                                 | 50 |

| 6.9   | Connector Part Number Summary             | 50 |

| 6.10  | Board Stackup                             | 51 |

| 6.11  | Tray Backplane Electrical Specifications  | 53 |

| 6.11. | .1 Input Voltage, Power, and Current      | 53 |

| 6.11. | .2 Grounding and Return                   | 54 |

| 6.12  | Component and Hole Locations              | 54 |

# **Table of Figures**

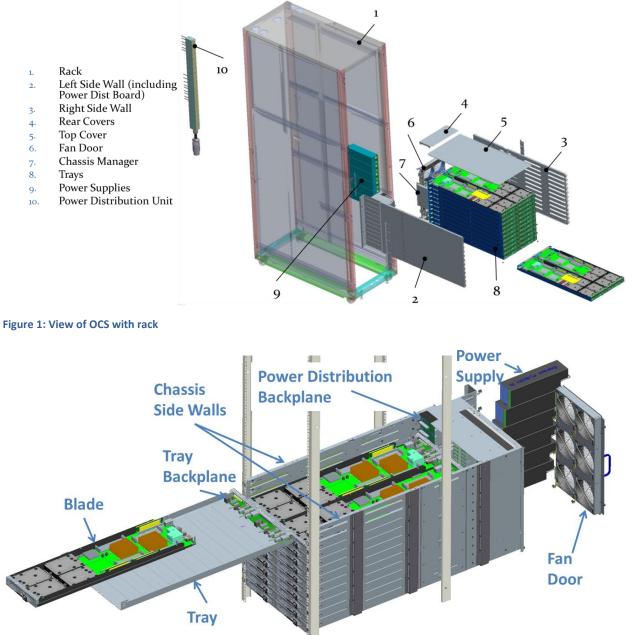

| Figure 1: View of OCS with rack                                              | . 2 |

|------------------------------------------------------------------------------|-----|

| Figure 2: Second view of OCS                                                 | . 2 |

| Figure 3: V2.0 OCS blade                                                     | .3  |

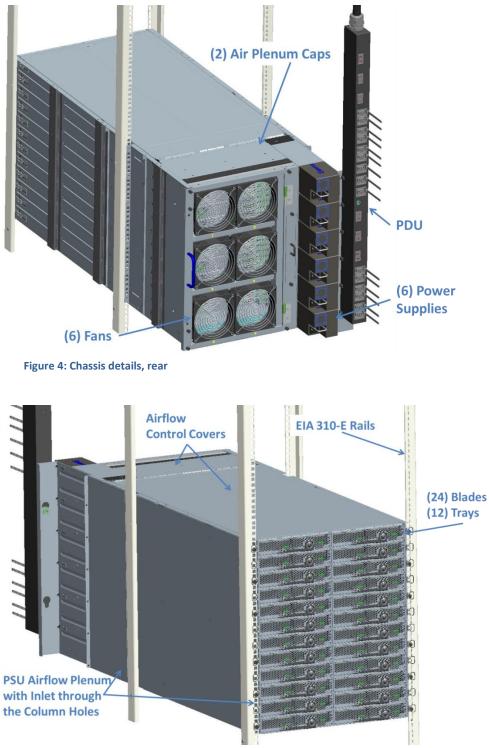

| Figure 4: Chassis details, rear                                              | .4  |

| Figure 5: Chassis details, from the front                                    | .4  |

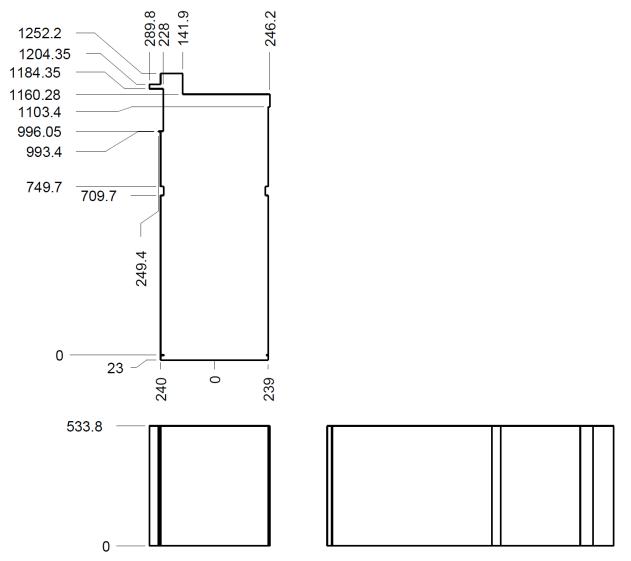

| Figure 6: V2.0 OCS chassis volumetric requirements (PDU volume is not shown) | . 5 |

| Figure 7: Rear rack column seal                                              | .6  |

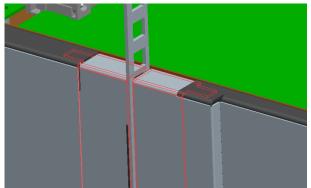

| Figure 8: Column air flow passage                                            | .6  |

| Figure 9: PDU placement                                                      | . 7 |

| Figure 10: PDU mounting strip                                                | . 8 |

| Figure 11: Power distribution board                                          | .9  |

| Figure 12: Example of a chassis/tray arrangement                             | 10  |

| Figure 13: Tray detail                                                       | 1   |

| Figure 14: Interior tray opening chassis volumetric                          | 2   |

| Figure 15: Interior tray opening volumetric detail                           |     |

| Figure 16: Side view of chassis                                              |     |

| Figure 17: View of the push to release the spring latch                      | 4   |

| Figure 18: Power connector pin out                                           |     |

| Figure 19: Fan tray (includes six 140 x 140 mm fans in parallel)             | 17  |

| Figure 20: Single fan airflow chart                                          | 17  |

| Figure 21: Maximum allowable impedance curve for a single blade              |     |

| Figure 22: Example of altitude correction factor                             | 20  |

| Figure 23: Tray and blade management connectivity                            | 23  |

| Figure 24: Chassis Manager block diagram                                     | 24  |

| Figure 25: Chassis Manager hardware block diagram                            | 25  |

| Figure 26: V2.0 OCS tray backplane block diagram                             | 29  |

| Figure 27: 12V power distribution                                            | 30  |

| Figure 28: SAS block diagram                                                 | 31  |

| Figure 29: Ethernet block diagram                                            | 32  |

| Figure 30: Tray mezzanine card block diagram                                 |     |

| Figure 31: Management block diagram                                          | 34  |

| Figure 32: Front view of header pins                                         |     |

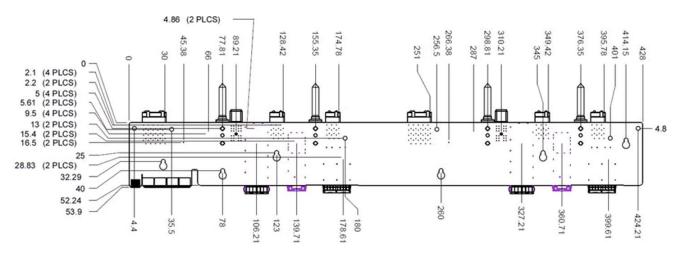

| Figure 33: Component and hole locations                                      | 54  |

# **Table of Tables**

| Table 1: List of specifications                                         | 1  |

|-------------------------------------------------------------------------|----|

| Table 2: Pinout for signal portion of power connector on tray backplane | 15 |

| Table 3: Pinout for power connector                                     | 15 |

| Table 4: Fan control variables                                          | 19 |

| Table 5: Serial RJ-45 cable definition for port 1 and port 2            | 26 |

| Table 6: Serial RJ-45 cable definition for port 5 and port 5            | 26 |

| Table 7: Blade numbers                                                  | 27 |

| Table 8: Chassis health status LED description                          | 28 |

| Table 9: Chassis attention LED description                              | 29 |

| Table 10: PDB 12V power connector pinout                                | 35 |

| Table 11: PDB 12V power connector signal descriptions                   | 35 |

| Table 12: Blade 12V power connector pinout                              | 36 |

| Table 13: AirMax Power connector header pinout                          |    |

| Table 14: Blade SAS interface connector pinout                          |    |

| Table 15: SAS connector signal description                              |    |

| Table 16: Mini-SAS HD connector pinout                                  |    |

| Table 17: Blade 10GbE connector pinout                                  | 40 |

| Table 18: Blade 10GbE signal definitions                                | 40 |

| Table 19: 10GbE SFP+ connector pinout                                   | 42 |

| Table 20: 40GbE QSFP+ connector pinout                                  | 43 |

| Table 21. PCIe interface connector pinout                               | 45 |

| Table 22: PCIe Gen3 connector signal definitions                        | 46 |

| Table 23: Tray mezzanine card connector pinout                          | 48 |

| Table 24: Tray mezzanine card signal definitions                        | 49 |

| Table 25: USB pinout                                                    | 50 |

| Table 26: Summary of connector part numbers                             | 50 |

| Table 27: Recommended stackup for tray backplane                        | 51 |

| Table 28: Required impedance and recommended trace widths               | 52 |

| Table 29: Input voltage and current from the PDB                        | 53 |

| Table 30: Output voltage and current to blades                          | 53 |

| Table 31: Input voltage and current from blade to tray mezzanine card   | 53 |

# **1** Overview of V2.0 Open CloudServer Specifications

Table 1 lists the Open CloudServer (OCS) system specifications.

#### Table 1: List of specifications

| Specification title                                                 | Description                                                                                                            |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| Open CloudServer Chassis<br>Specification Version 2.0               | Describes the hardware used in the Version 2.0 (V2.0) OCS system, including the chassis, tray, and systems management. |  |

| Open CloudServer Blade<br>Specification Version 2.0                 | Describes the blade used in the V2.0 OCS system, including interconnect and blade hardware and blade management.       |  |

| Open CloudServer Tray Mezzanine<br>Specification Version 2.0        | Describes the tray mezzanine card used in the V2.0 OCS system, including interconnect, hardware, and management.       |  |

| Open CloudServer NIC Mezzanine<br>Specification Version 2.0         | Describes the Network Interface Controller (NIC) mezzanine card used in the V2.0 OCS system.                           |  |

| Open CloudServer Chassis<br>Management Specification Version<br>2.0 | Describes the chassis manager command-line interface (CLI).                                                            |  |

This document is intended for designers and engineers who will be building chassis for an OCS system.

## 2 Introduction to the Open CloudServer System

The V2.0 OCS system is a fully integrated rack of servers and IT equipment that is highly optimized and streamlined for large, web-scale deployments.

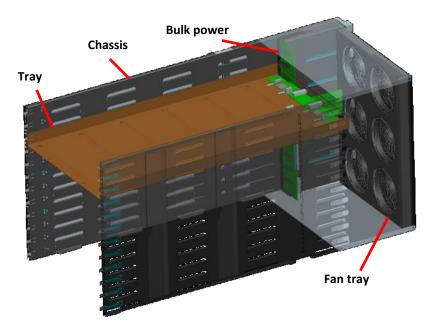

OCS is an off-the-shelf (OTS) commodity rack that is loaded with up to four modular chassis, each with trays, power supplies, power distribution, rack management, system fans, and two side-walls, as shown in Figure 1 and Figure 2.

OCS blades are highly configurable, and are usually compute blades or storage "just a bunch of disks" (JBOD) blades.

Figure 3 shows an example of a V2.0 OCS blade.

Figure 3: V2.0 OCS blade

Each chassis supports 12 rack unit (EIA 310-E standard U or 1U, each 17.7" wide and 1.75" tall) trays that house up to 24 individual OCS blades (two blades per tray). Blades can be designed to use the full width of the tray. It is also possible to use multiple rack units to house a single tall blade, with certain restrictions.

Power, management, and networking are delivered through the tray backplane (TB) and the power distribution backplane (PDB). The tray backplane is located at the back of each tray. The power distribution backplane attaches vertically to the individual trays on one side and to the power supply unit (PSU) on the other side. This arrangement reduces the current carrying requirements of the distribution board, eliminates cabling, and reduces costs.

Power and management signals are received from the PDB and distributed to the blades by Ethernet networking cables that pass through a blind-mate connector and are routed to attachments at the rear of the chassis. Note that running the cables through the rear of the blade eliminates the need to connect directly to the servers. Once provisioned, the network cabling should only be touched when a cable or switch fails or the typology is changed. The type and number of networking switches depends on the specific deployment.

### **3** Chassis Specification

The following sections describe the OCS chassis.

The chassis is an assembly of supporting components designed to be individually mounted to the rack. It provides structure and airflow to the blades and other electrical subsystems

### 3.1 Chassis Physical Specification

The physical specifications for the chassis include the dimensions and a description of the guiding and latching features.

### 3.1.1 Volumetric Specification

Figure 4 shows details of the chassis from the rear. Figure 5 shows details of the chassis from the front.

Figure 5: Chassis details, from the front

The chassis is enclosed at the top and bottom of the rear airflow plenum to minimize recirculation and maximize blade cooling. The top of the chassis is also enclosed to ensure that air passes through the blades. Note that airflow blanks are required for slots that are not occupied by blades. These blanks must be closed to airflow to avoid short-circuiting the adjacent blades.

Figure 6 shows the chassis dimensions.

Figure 6: V2.0 OCS chassis volumetric requirements (PDU volume is not shown)

There is a separate inlet air plenum for the power supplies routed along the "Zero U" space of the rack. Features in the side plenum help seal this inlet when the chassis is secured in the rack so that the air from the hot aisle cannot enter the power supplies, as shown in Figure 7.

Figure 7: Rear rack column seal

The chassis can accommodate a rack column spacing of 736.6mm. The columns must use 9.5mm square holes. Air for the power supplies is drawn through the columns, as shown in Figure 8.

Figure 8: Column air flow passage

Sliding sub-assemblies are keyed to ensure that they are connected correctly unless incorrect installation causes no damage. For example, the trays and blades are keyed so they will not be installed upside down; power supplies are not keyed because they cause no damage if installed upside down.

Note that if the blades will be shipped within the chassis, additional braces are required for support. The braces transfer forces directly to the rack columns and provide load-bearing support for the front of the blades.

Note also that the chassis is not intended to provide EMI containment.

### 3.1.2 Latching Features and Fasteners

Latches, as well as thumb screws and other components used to lock, unlock, or remove a subassembly from the chassis, are colored blue (Pantone code 285 C blue) to make them easy to identify.

In the chassis, these latching features include:

- Fan door securing features

- Power supply unit latch covers

- Chassis Manager module securing features

To avoid confusion when removing a blade, the tray release wire form loops should not be colored blue.

Fasteners that require Torx drivers can be used to secure the chassis to the rack. Assembling the trays, blades, power supplies, and the fan tray does not require tools.

#### 3.1.3 Power Distribution Unit Placement

Figure 9 shows the location of the Power Distribution Unit (PDU) with respect to the chassis. The PDU mounting features are meant to wrap around the rack outer shell for clearance of a 1200mm long rack.

Figure 9: PDU placement

The chassis includes mounting key holes to secure the PDU in the correct position, as shown in Figure 10. The PDU has corresponding standoffs.

Figure 10: PDU mounting strip

### 3.2 Power Delivery

The chassis delivers power to the trays through the power distribution backplane. Using six PSUs on a shared power backplane provides nearly ideal phase balancing of three-phase AC inputs, which allows a higher utilization of the incoming power.

Note that most of the weight of the power supplies is supported by the chassis, not by the power connector.

### **3.3 Power Distribution Backplane**

The power distribution backplane (PDB) provides power to each tray assembly, to the fan assembly, and to the Chassis Manager card.

The power distribution backplane also acts as the center point for chassis data communications, and includes the following cable connections:

- LAN 1, 2

- Serial COM 1, 2, 5, 6

- Power control switch outputs 1, 2, 3

- Chassis Manager power control input

- Fan door power, control, and monitoring

The power distribution backplane accepts 19 assemblies:

- Chassis Manager

- 12 tray backplane connectors

- 6 power supply connectors

0 Power Switch 1 NO. Power Switch 2 Tray BP 12 TRAY BP 12 Power Switch 3 Ö ett. Tray BP 11 Fan Connector TRAY BP 11 0 LAN2 Tray BP 10 TRAY BP 1 0 Tray BP 9 211 TRAY BP 0 Tray BP 8 TRAY BP Chassis Manager Tray BP 7 TRAY BP Tray BP 6 TRAY BP :(0 С Tray BP 5 TRAY BP 318 8**0** O Tray BP 4 LAN1 TRAY BI 0 С COM 6 Tray BP 3 Remote 12V Pwr TRAY BP COM 5 Tray BP 2 COM 2 RAY B CM Power Control О COM 1 Tray BP 1

#### Figure 11 shows details of the power distribution backplane.

Figure 11: Power distribution board

### 3.4 Tray Specifications

The sections that follow describe the V2.0 Open CloudServer trays.

For service and debugging, the tray must be able to function in standalone mode (external to the chassis) for debugging. The tray can attach and receive power, Blade\_EN, and serial signals without impacting cost or operation in production environments. The preferred method to attach to the tray is through headers that are not loaded for operation within the chassis.

The physical specifications for the trays include the dimensions of the tray volume and a description of the guiding and latching features.

#### 3.4.1 Volumetric Specifications

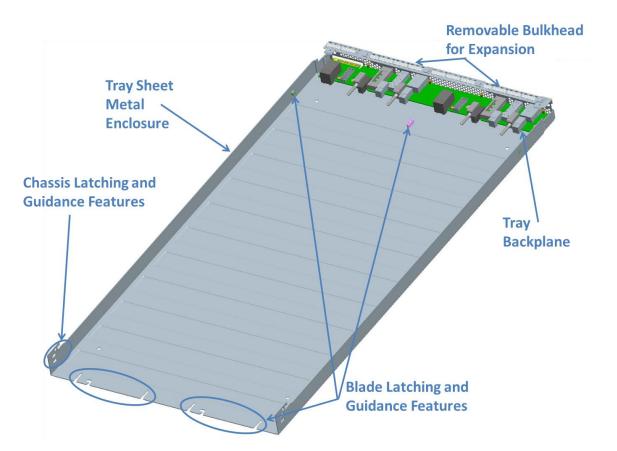

Figure 12 shows an example of a chassis/tray arrangement. Figure 13 provides mechanical feature details of the tray.

Figure 12: Example of a chassis/tray arrangement

#### Figure 13: Tray detail

The figures that follow describe the mechanical mating locations of the tray into the chassis. The tray's outer dimensions must not exceed those described, with all tolerances for different manufacturing methods (such as soft and hard tooling) accounted for; the tray's interior must be able to accept a blade as described in <u>Section 3.1: Volumetric Specifications</u>. The tray mechanically interlocks to the power backplane support to minimize the load the connector must support.

The chassis is designed to be installed into a rack that complies with the EIA-310-D standard (the current revision of the Electronic Industries Alliance standard for a 19" rack) without modification.

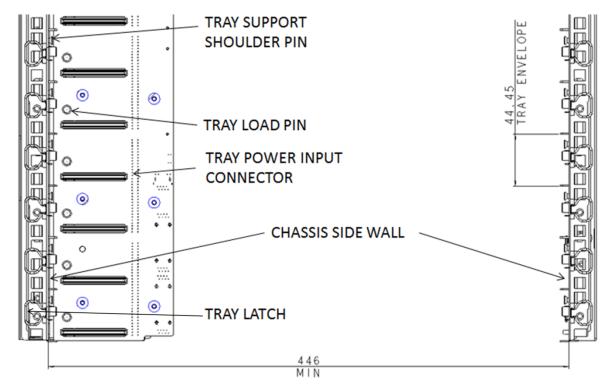

Figure 14 describes the opening in the chassis that accepts the trays, as viewed from the front of the system.

Figure 14: Interior tray opening chassis volumetric

The chassis interior consists of a series of shelves that extend from the side walls to support the trays. The power distribution board is located at the rear of the opening, on the left side as viewed from the front, to transfer power from the bulk power supply units to the trays.

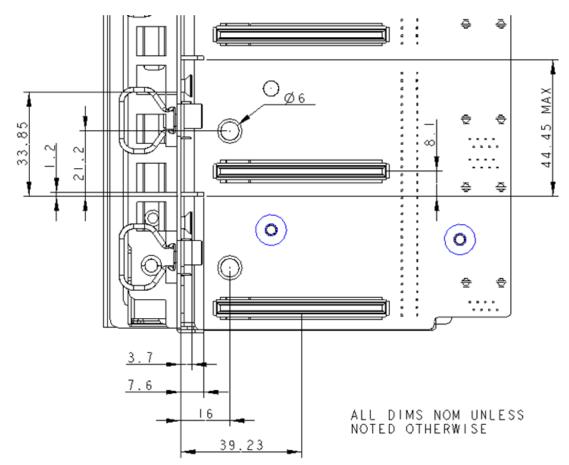

Figure 15 shows the tray volume as seen from the front and defines the location of the tray supports as related to the power connector. A tray latch release is integrated into the chassis structure located on the left and right sides of the chassis opening.

Figure 15: Interior tray opening volumetric detail

Figure 16 shows a side view of the chassis. These dimensions are critical to the fit and function of the tray.

Figure 16: Side view of chassis

### 3.4.2 Guiding and Latching

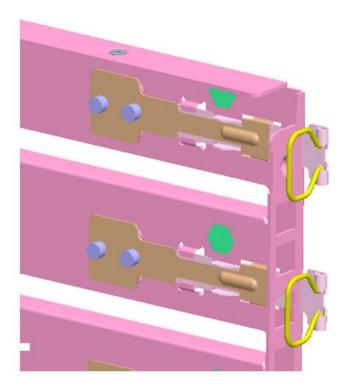

The chassis supports the tray on a series of shelves located on each side wall. These are designed and manufactured to prevent metallic slivers from forming when the tray is inserted into the chassis. Shoulder pins are included in the chassis side walls to secure the walls of the tray during insertion and prevent the tray from sagging under the load of the blades.

A pull-to-release spring latch is incorporated into the left-side and right-side panels to keep the tray in the chassis. Figure 17shows a pull-to-release latch. Figure 16 shows the dimensions of the latch

Figure 17: View of the push to release the spring latch

### 3.5 Tray Interconnect

The chassis provides electrical power and signaling to the tray.

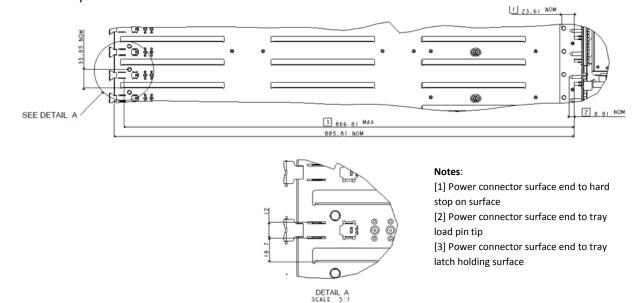

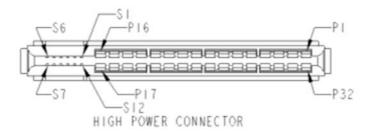

Figure 18 shows the recommend connectors.

Figure 18: Power connector pin out

The power connector supports a maximum of 1,382W per tray (12V x 16 pins x 9A/pin x 80 percent derating). The power per rack unit is limited to 600W. This connector allows a future 2U server to consume 1200W.

Table 2 shows the pinout for the signal part of the power connector on the tray backplane

| Pin | Signal name    | Tray input/output | Definition              |

|-----|----------------|-------------------|-------------------------|

| S1  | SERIAL_B1_TX1  | Input             | Blade 1 serial input 1  |

| S2  | SERIAL_B1_RX1  | Output            | Blade 1 serial output 1 |

| S3  | BLADE_B1_EN1   | Input             | Blade 1 power enable    |

| S4  | PSU_B1_ALERT_N | Input             | Blade 1 PSU Alert       |

| S5  | SERIAL_B1_TX2  | Input             | Blade 1 serial input 2  |

| S6  | SERIAL_B1_RX2  | Output            | Blade 1 serial output 2 |

| S12 | SERIAL_B2_TX1  | Input             | Blade 2 serial input 1  |

| S11 | SERIAL_B2_RX1  | Output            | Blade 2 serial output 1 |

| S10 | BLADE_B2_EN1   | Input             | Blade 2 power enable    |

| S9  | PSU_B2_ALERT_N | Input             | Blade 2 PSU Alert       |

| S8  | SERIAL_B2_TX2  | Input             | Blade 2 serial input 2  |

| S7  | SERIAL_B2_RX2  | Output            | Blade 2 serial output 2 |

Table 2: Pinout for signal portion of power connector on tray backplane

Table 3 shows the power connector pin-out.

#### Table 3: Pinout for power connector

| Pin            | Signal name | Capacity   |

|----------------|-------------|------------|

| P1 through P4  | 12V return  | 9A per pin |

| P5 through P8  | 12V return  | 9A per pin |

| P9 through P12 | 12V supply  | 9A per pin |

| Pin             | Signal name | Capacity   |

|-----------------|-------------|------------|

| P13 through P16 | 12V supply  | 9A per pin |

| P17 through P20 | 12V supply  | 9A per pin |

| P21 through P24 | 12V supply  | 9A per pin |

| P25 through P28 | 12V return  | 9A per pin |

| P29 through P32 | 12V return  | 9A per pin |

# **4** Cooling System Specifications

The following sections describe the V2.0 Open CloudServer cooling system.

Cooling for the blades is provided by six 140mm x 140mm shared rear-system fans mounted on the chassis. The fans are configured in an N+1 arrangement; if a fan fails, the system can maintain the required cooling with the remaining fans.

Power supplies are cooled by their internal fans and supplied with fresh air by a channel along the side of the server.

### 4.1 Thermal Design Considerations

The fans provide all of the cooling and airflow required by the blades; it is therefore critical to design the blades so that all of their components are sufficiently cooled by the system fans.

The V2.0 Open CloudServer cooling system was designed so that the fans consume the least amount of power possible while maintaining the necessary cooling.

The blade server exhaust temperature directly reflects the hot-aisle temperature of a data center.

### 4.2 Airflow and Thermal Requirements

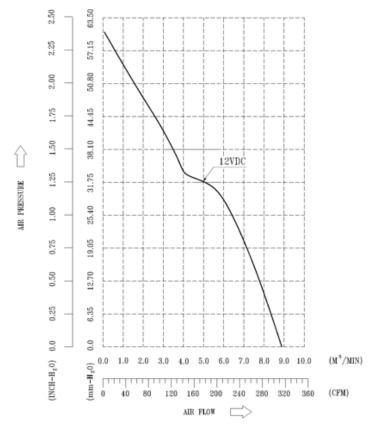

The chassis is intended to provide adequate airflow to the servers if the servers are designed to meet the following airflow requirements. Figure 19 shows the fan tray, and Figure 20 shows individual fan airflow curve of one manufacturer.

Figure 19: Fan tray (includes six 140 x 140 mm fans in parallel)

Figure 20: Single fan airflow chart

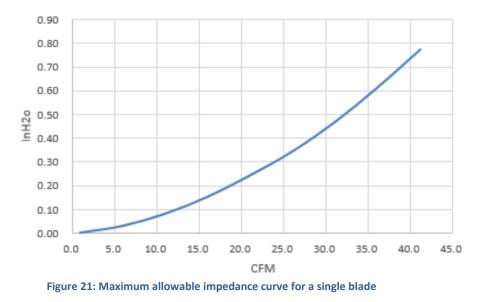

Figure 21 shows the maximum allowable impedance curve of single blade (in cubic foot per minute [CFM] versus inches of water [inH2O]. The target airflow is less than 31 CFM at full fan speed.

### 4.3 Fan Speed Control

The fans have variable speed capability; this lets the system drive the fans at speeds only as high as necessary to cool the components, minimizing power consumption, noise, and fan failures.

### 4.3.1 Pulse-Width Modulation Input

The blades exchange thermal information with the Chassis Manager through an intelligent platform management interface (IPMI). The first sensor value in the IPMI table is the pulse-width modulation (PWM) duty cycle fan speed, a value between the non-critical limits of 0 (fan off) and 100 (fan running at full speed). Note that the minimum fan speed is 20 percent of duty cycle to ensure that the fan has enough torque to maintain rotation.

Using PWM signals simplifies the system-level control strategy and allows the system to be blade agnostic. Blades request their own fan speeds. The Chassis Manager polls each blade periodically for its fan flow rate request through a PWM signal, and then drives the fan speeds based on the highest request.

Blades are responsible for monitoring all thermally critical component temperatures and determining an appropriate fan speed. A closed-loop method for monitoring temperature and adjusting speed requests is highly recommended. At minimum, a fan speed table based on measured inlet temperature is required, and the inlet and outlet temperatures of thermally critical components (such as processors, DIMMs, and PCHs) should be available through the IPMI interface. These sensors should have identification values other than 1 and should not have metadata limits.

Table 4 lists important variables in fan control strategy.

Table 4: Fan control variables

| Variable                      | Value and description                                                                                                                  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                               | Used to control limits of processor temperature                                                                                        |  |  |

| Target temperature band       | Upper = target temperature<br>Lower = target temperature – 4 <sup>o</sup> C                                                            |  |  |

| Blade poll frequency          | Frequency of blade temperature requests<br>10 seconds                                                                                  |  |  |

| Fan speed decrease hysteresis | The amount of time the fan must wait between speed changes (prevents the fan speed from rising and falling too frequently)<br>1 minute |  |  |

| Altitude compensation         | Increase speed by 3.2 percent for every 1000 ft (304m) above sea level (see Figure 20)                                                 |  |  |

|                               | $DC = DC_{base} * ({}^{5}/_{N_{active}})$                                                                                              |  |  |

|                               | <i>DC</i> is the fan speed duty cycle requested by the Chassis Manager                                                                 |  |  |

| Active fan correction factor  | <i>DC</i> <sub>base</sub> is the base fan speed duty cycle before fan count and altitude correction                                    |  |  |

|                               | $N_{active}$ is the number of active system fans (if no fans have failed, this is six)                                                 |  |  |

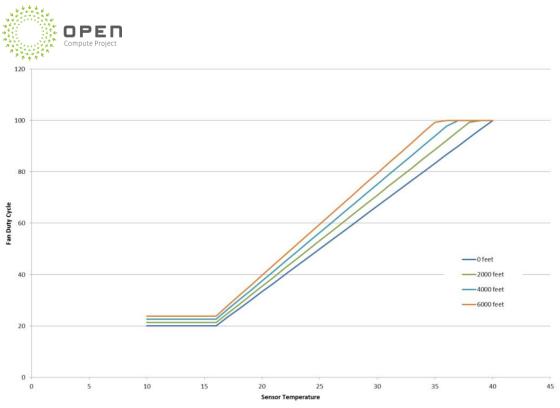

### 4.3.2 Fan Speed Correction for Altitude

In blades that choose to operate fan speed based on inlet temperature readings, fan speed must be increased by 3.2 percent for every 1000 ft (304 m) above sea level. The location of the system must therefore be recorded during installation so that the correction can be made.

Figure 22 shows an example of fan speed correction for altitude with the following non-critical limits:

- Lower = 15°C ambient

- Upper = 35°C ambient

Figure 22: Example of altitude correction factor

### 4.3.3 Fan Speed Correction for Fan Failures

The Chassis Manager monitors the number of active fans and makes appropriate adjustments to the fan speed if a fan is detected to have failed (<u>Section 4.4: Fan Failure</u> provides more information about fan failure). A fan is considered to have failed if the tachometer speed returned to the Chassis Manager is below 25 percent of the requested speed for more than five minutes.

Note that fan failures trigger an alert so that the fan can be replaced (no action is required on the blade).

### 4.3.4 Sensor Failure

If a PWM signal from a specific blade is not detected or is determined to be unrealistic (less than 0 or more than 100), the blade is assigned a request of the minimum fan speed, and the speed requests from the other blades in the system will take priority.

If there is only one blade is in the system and if the PWM signal is not present, the chassis will operate fans at the minimum speed. If blade activity forces a thermal shut-down under these conditions, the blade must be replaced or repaired.

If the blades in the chassis are plugged in but are in standby mode, the Chassis Manager will drive fan speed at the minimum level.

### 4.4 Fan Failure

Analysis shows that fan failures (tachometer speed below 25 percent of the requested speed for more than five minutes) are rare.

### 4.4.1 Fan Failure Rate

Failure rate for the fans is calculated using the following information:

- Mean time between failures (MTBF) provided by the manufacturer is 50K hours at 60°C.

- Failure rate improves two times for every 10°C reduction.

- Average outlet operating temperature is approximately 46°C, allowing for a greater than two times reduction.

- Annualized failure rate is therefore:

- 6x10E-6 per chassis

- o 2.4x10E-5 per rack

- Failures per year are therefore:

- 0.05 for a chassis (one failure every 20 years)

- 0.20 for a rack (one failure every 5 years)

Data from the server vendor indicates that the most common cause of fan failure is a lubricant leak, which causes a fan to speed up for approximately a week before stopping when the lubricant is gone. Chassis management can monitor the speed of the fans and identify an algorithm to address speeds that are too fast or too slow. When a fan failure is detected, chassis management will speed up the remaining fans to compensate.

#### 4.4.2 Fan Repair

If fan repair does become necessary, the fan tray assembly is mounted on a pinned hinge so that the full tray can be easily removed for repair, and both sides of the fans have wire screen guards for safety during service.

The following steps describe how to replace a fan:

- 1. Prepare all materials and a ladder if the fan is in the upper half of the rack.

- 2. Open the fan door and disconnect the cable.

- 3. Lift the fan tray off the hinge.

- 4. Install the new fan tray onto the hinge.

- 5. Plug in the cable.

- 6. Close the fan door.

Note that if chassis management turned the chassis attention LED on because of the fan failure, it will turn the LED off when it detects that the fans are operating correctly.

### 4.5 Thermal Considerations for the Blade

The blade must be able to operate at full-load capacity in all conditions described in this specification, including the upper and lower ambient temperatures, humidity levels, altitude levels, and available fan capability. If conditions are outside the prescribed limits, the blade should continue to operate as long as hardware and data are not at risk; if conditions are likely to cause damage, the blade should be shut down.

For the largest possible operating range, the inlet temperature to the system should not drive blade shut down. The temperature of sensitive components should be individually monitored to prevent an unnecessary system shut down.

Note that blade components frequently have an average operating temperature target that optimizes long-term reliability and an upper temperature limit to prevent hardware damage and maintain data integrity. Components should normally operate at the target, but they can operate at a higher temperature for a short time as long as they remain below the upper limit.

The only thermal response the Chassis Manager gives is control of fan speed. While alerts are logged if a fan or a blade fails, the Chassis Manager does not request blade shut downs. The blade is responsible for shut downs or throttling caused by high inlet temperature.

# **5** Systems Management

The following sections provide specifications for OCS systems management

Systems management in OCS is designed to present a consistent, optimized interface. A Chassis Manager provides the front end through an applications interface (RESTful web API) for automated management and a command-line interface (CLI) for manual management (see Table 1 in <u>Section 1</u> for a list of available specifications). The Chassis Manager manages all devices within the rack and communicates directly with the blade management system through a serial multiplexor.

Note that there are two possible paths for systems management in OCS: in-band and out-of-band (OOB).

- The in-band management path is through the primary NIC while the operating system is running.

- The out-of-band path is through the Chassis Manager.

In-band is the preferred path for systems management whenever possible.

### 5.1 Systems Management Connectivity

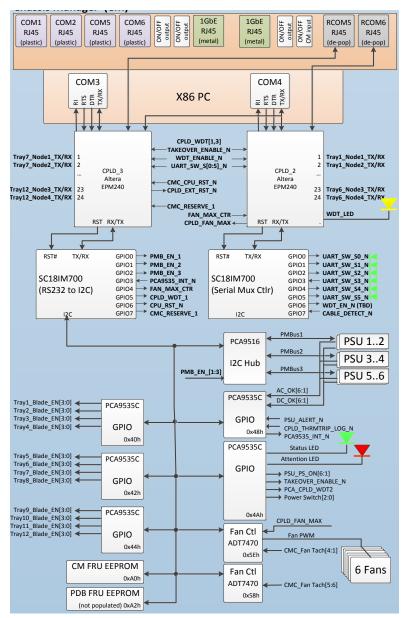

Chassis management consists of a Chassis Manager module (the PCBA) that plugs into the power distribution backplane through a connector. This card is responsible for management and monitoring of the power supplies and fans, and makes it possible to keep active components off the power distribution and tray backplanes.

A serial multiplexor (baud rate of 115200) lets the Chassis Manager distribute Blade\_EN signals to the individual blades. The signals must be able to be modified so as to coordinate power cycling of multiple JBOD trays.

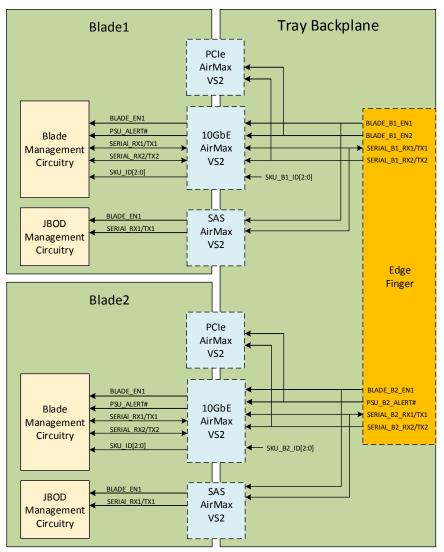

Figure 23 shows management signals passed through the passive tray backplane to the blades.

Figure 23: Tray and blade management connectivity

### 5.2 Chassis Manager Specifications

The Chassis Manager, a general purpose and highly flexible device, is located in the plenum of the chassis.

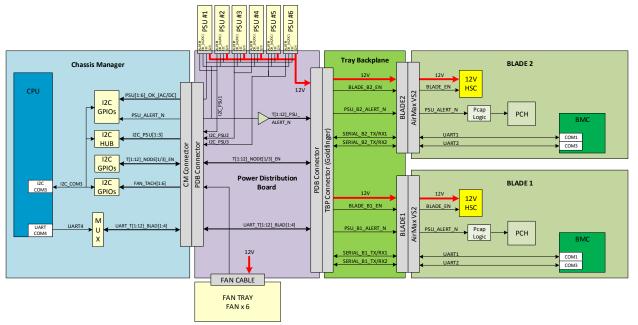

Figure 24 shows a block diagram of the chassis, including the Chassis Manager, trays, power supplies, and fans.

| 2 x 1GbE 4 x RS232 Power Control<br>General NWK Switch 3 x Outputs<br>Purpose Management 1 x Input |              |  |  |  |

|----------------------------------------------------------------------------------------------------|--------------|--|--|--|

| Chassis Manager                                                                                    | Chassis      |  |  |  |

| Win7 Embedded                                                                                      | Tray<br>1 12 |  |  |  |

| Serial Fanout                                                                                      |              |  |  |  |

| Power Control                                                                                      | PSUs<br>1 6  |  |  |  |

| PSU Monitoring                                                                                     |              |  |  |  |

| Fan Control and<br>Monitoring                                                                      | Fan Tray     |  |  |  |

Figure 24: Chassis Manager block diagram

Following are specifications of the Chassis Manager:

- Input/Output:

- 2 x 1GbE Ethernet (general purpose to be used for network access or for direct connector to the top-of-rack management ports)

- 4 x RS-232 (network switch management for boot strap initial start-up)

- Windows Embedded operating system (enables a secure solution)

- Embedded x86 processor

- Hot repair, no downtime during replacement

- Memory—4GB with error-correcting code (ECC)

- Storage—8GB solid-state drive (SSD)

- Power control—one input signal, three output signals to the PDU or to another Chassis Manager for remote power control

- No Peripheral Component Interconnect (PCI) or PCI Express (PCIe) slot

- USB and Video Graphics Array (VGA) support used for early debugging only, will be removed for production

Figure 25 shows a detailed block diagram of the Chassis Manager.

Figure 25: Chassis Manager hardware block diagram

### 5.2.1 Communication Ports

Table 5 lists the definition and translation of the serial COM port signals of the RJ-45 connector for ports 1 and 2. These match the functionality of switch consoles that use RJ-45, but can be used to select cables that convert from DB-9 or DB-25 connections. The system swaps received data/transmitted data (RxD/TxD), clear to send/request to send (CTS/RTS), and data terminal ready/data set ready (DTR/DSR) signals so a straight Ethernet cable can be used.

| Signal on CM board | RJ-45 connector pin | RJ-45 connector pin | Switch console port |

|--------------------|---------------------|---------------------|---------------------|

| RTS                | 1                   | 1                   | CTS                 |

| DSR                | 2                   | 2                   | DTR                 |

| RxD                | 3                   | 3                   | TxD                 |

| GND                | 4                   | 4                   | GND                 |

| GND                | 5                   | 5                   | GND                 |

| TxD                | 6                   | 6                   | RxD                 |

| DTR                | 7                   | 7                   | DSR                 |

| СТЅ                | 8                   | 8                   | RTS                 |

Table 5: Serial RJ-45 cable definition for port 1 and port 2

Table 6 lists the definition and translation of the serial COM port signals of the RJ-45 connector for serial COM ports 5 and 6. Note that COM port 3 and 4 are internal to the Chassis Manager board.

| Signal on CM board | RJ-45 connector pin | RJ-45 connector pin | Switch console port |

|--------------------|---------------------|---------------------|---------------------|

| RTS                | 1                   | 1                   | CTS                 |

| DSR                | 2                   | 2                   | DTR                 |

| RxD                | 3                   | 3                   | TxD                 |

| RI                 | 4                   | 4                   | GND                 |

| GND                | 5                   | 5                   | GND                 |

| TxD                | 6                   | 6                   | RxD                 |

| DTR                | 7                   | 7                   | DSR                 |

| CTS                | 8                   | 8                   | RTS                 |

Table 6: Serial RJ-45 cable definition for port 5 and port 5

#### 5.2.2 Power Control

The Blade\_EN signals let all servers on a single tray be powered on/off coincidently, and let servers on different trays be powered on/off either coincidently or through timed power control.

Timed power control can be used to control servers and JBODs, (for example, to prevent incorrect errors from being reported when using a head server node and JBOD blades). The following steps can be used:

1. Power off the head (server) node, and allow a short delay.

- 2. Power off the JBOD blade, and allow a five second delay.

- 3. Power on the JBOD blade, and allow a short delay.

- 4. Power on the head (server) node.

Timed delays can be easily adjusted to match the needs of the hardware and storage though the Chassis Manager.

The Chassis Manager exports up to three 12V ON/OFF signals. The default is 0V (ON); 12V is OFF. The signals are sent to either relays on a PDU or to other Chassis Managers.

### 5.2.3 Chassis Manager Software and Programming Model

Microsoft will write the software that runs on the Chassis Manager, including software for monitoring and managing the power supplies, system fans, and Blade\_EN signals. A vendor will write, document, and test a driver to interface to chassis management. Microsoft will provide the higher-level interface and API for attachment to the Chassis Manager.

#### 5.2.4 Blade Numbering

Blades are hard wired through the management subsystem to specific positions. This ensures that there is zero ambiguity for service or networking. Table 7 lists the blade numbers, with both front and rear views.

| U number | Blades viewed from front |    | Blades viewed from rear |    |

|----------|--------------------------|----|-------------------------|----|

| 12       | 12                       | 24 | 24                      | 12 |

| 11       | 11                       | 23 | 23                      | 11 |

| 10       | 10                       | 22 | 22                      | 10 |

| 9        | 9                        | 21 | 21                      | 9  |

| 8        | 8                        | 20 | 20                      | 8  |

| 7        | 7                        | 19 | 19                      | 7  |

| 6        | 6                        | 18 | 18                      | 6  |

| 5        | 5                        | 17 | 17                      | 5  |

| 4        | 4                        | 16 | 16                      | 4  |

| 3        | 3                        | 15 | 15                      | 3  |

| 2        | 2                        | 14 | 14                      | 2  |

| 1        | 1                        | 13 | 13                      | 1  |

#### Table 7: Blade numbers

### 5.2.5 Chassis LEDs

Each chassis has two light-emitting diodes (LEDs) on the Chassis Manager: a health status LED that is green and an attention LED that is red. Both LEDs are driven by a single GPIO bit off the blade's management i2c tree.

#### 5.2.5.1 Chassis Health Status LED

The chassis health status LED indicates whether the Chassis Manager has booted. Note that if the 12V power is off, the LEDs on the power supplies are also off. Table 8 describes the operation of the chassis health status LED.

| LED status            | Condition                                                                                                                                                                    |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| OFF                   | <ul> <li>Backplane 12V power is OFF if power supply LEDs are OFF</li> <li>Backplane 12V power is ON, but Chassis Manager never booted if power supply LEDs are ON</li> </ul> |  |  |

| Solid green <b>ON</b> | <ul> <li>Backplane 12V power is ON and Chassis Manager has booted</li> </ul>                                                                                                 |  |  |

Table 8: Chassis health status LED description

#### 5.2.5.2 Chassis Attention LED

The chassis attention LED is visible from the rear of the chassis without opening the fan tray. This LED directs service technicians to the correct chassis during repair. When possible, blade diagnostics are used to direct repairs; alternately, the Microsoft scale-out management software can be used. In both cases, logs of the repair work are available.

The chassis attention LED indicates the following conditions:

• Operator directed

An operator can manually set the chassis attention LED (for example, identification of chassis cables).

• Power supply failure

Chassis Manager has detected a power supply failure.

• Fan failure

Chassis Manager has detected a fan failure.

Note that the chassis attention LED must be turned off after service is complete.

Table 9 describes the operation of the chassis attention LED

| LED status                                                                   | Condition              |  |  |

|------------------------------------------------------------------------------|------------------------|--|--|

| OFF                                                                          | No attention indicated |  |  |

| Solid red ON       • Operator directed         • Power supply or fan failure |                        |  |  |

#### Table 9: Chassis attention LED description

# 6 Tray Backplane Specification

The sections that follow describe the tray backplane.

## 6.1 Tray Backplane Overview

The tray backplane provides a connector backplane interface to two half-width blade Printed Circuit Assemblies (PCAs) or a single full-width blade PCA. The purpose of the tray backplane is to enable external connector and cable interfaces to the internal blade assemblies, as well as to pass 12V power from the PDU to the blade assemblies.

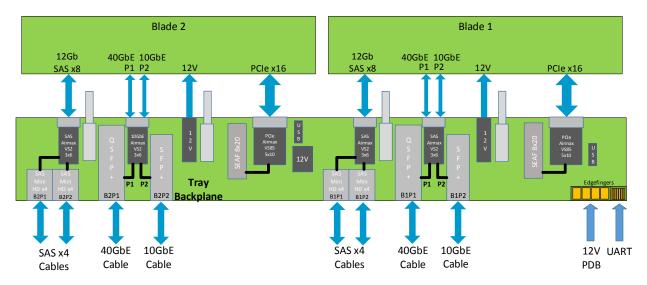

Figure 26 shows the major interfaces between the blade assembly and the tray backplane assembly. The block diagram is not to scale, but is intended to communicate relative location of the components on the tray backplane.

Figure 26: V2.0 OCS tray backplane block diagram

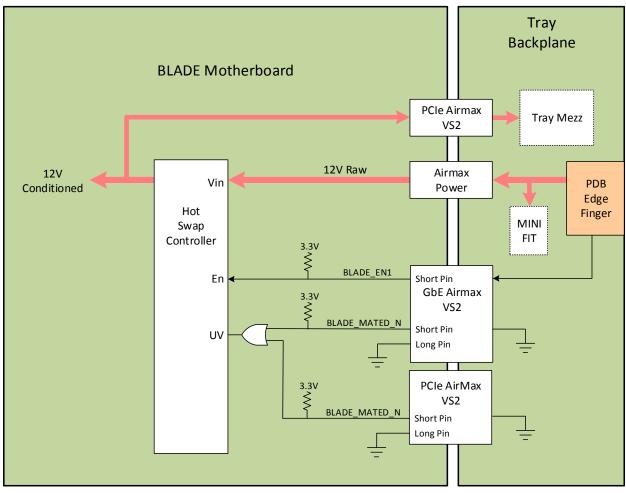

# 6.2 12V Power Distribution

The tray backplane will accept 12V originating from the PDU through the PDB, and will distribute the 12V to each of the two blade motherboards through AirMax power connectors. The tray backplane will support a maximum of 40A to each blade. The 12V will also be distributed to an optional Mini-Fit Jr.™ connector for cabling to separate assemblies, and will support a maximum of 10A.

A conditioned 12V is received by the tray backplane through the PCIe AirMax VS2 connector for distribution to the tray mezzanine card. The tray backplane will support a maximum of 3A to each tray mezzanine card.

Figure 27 shows a block diagram of the 12V distribution.

Figure 27: 12V power distribution

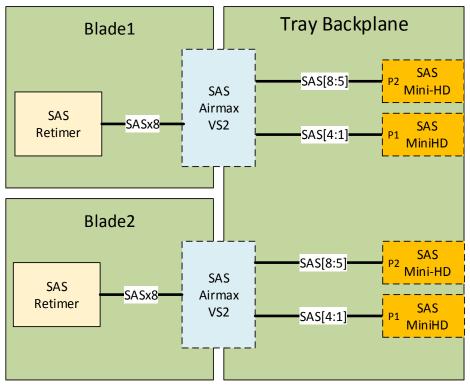

# 6.3 SAS Channels

The tray backplane will support a 12Gb Serial Attached Small Computer System Interface (SAS) x8 interface from the blade through an AirMax VS 3x6 connector, and will distribute to two SAS x4 cables through SAS Mini-HD x4 side-by-side connectors, as shown in Figure 28.

Figure 28: SAS block diagram

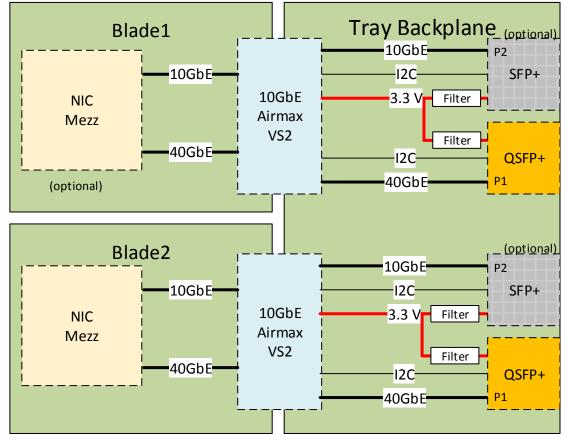

## 6.4 10 Gb/40Gb Ethernet

The tray backplane will support a 10GbE and 40GbE ports from the blade through an AirMax VS2 3x6 connector, and will distribute to a small form-factor pluggable (SFP+) and quad SFP+ (QSFP+) cable, as shown in Figure 29. This will include 3.3V power support for the enhanced SFP+/QSFP+ passive, active, or optical cables. The port2 SFP+ connectors will be a load option, and may not be loaded on all board revisions.

Figure 29: Ethernet block diagram

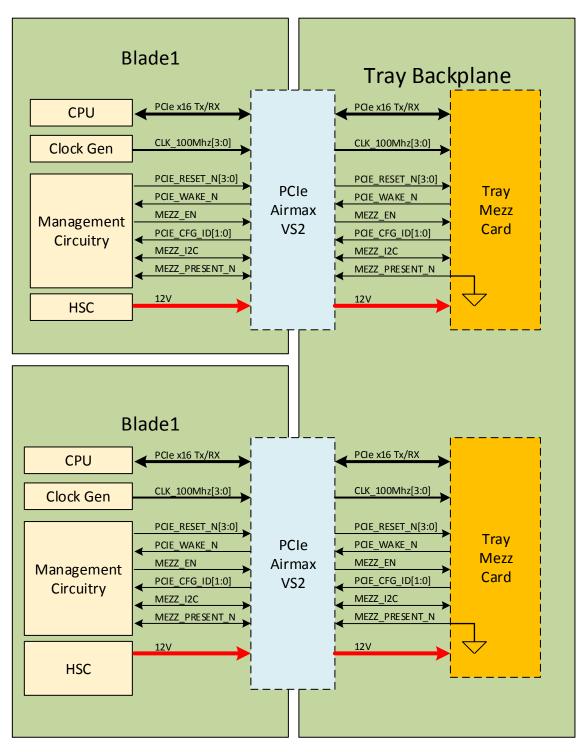

# 6.5 Tray Mezzanine Card

The tray backplane will support two tray mezzanine cards, one per blade. Each tray mezzanine card supports a PCIe Gen3 x16 to a CPU on the blade. The PCIe interface includes four separate PCIe clocks, and resets to supports PCIe bifurcation of 1x4, 2x8, and 4x4. Bifurcation is communicated to the blade through CFG\_ID signals. The tray mezzanine card is powered by 12V supplied by the blade, and will support a minimum supply current of 3A.

Figure 3 shows a block diagram of the interface.

Figure 30: Tray mezzanine card block diagram

### 6.5.1 Chassis Management

The tray backplane will distribute chassis management signals from the Chassis Manager to each of the blades. Figure 31 shows details of these signals.

Figure 31: Management block diagram

### 6.5.2 Guide Pins

The tray backplane will provide two guide pins for insertion and alignment of the blade to the tray backplane. The guide pins will be connected to GND on the tray backplane. The guide pins will be FCI MPN 10044366-101LF pins or equivalent.

# 6.6 **Connector Pinouts and Signal Descriptions**

The sections that follow detail the connector pinouts and signals.

## 6.6.1 PDB 12V Power Connector

The tray backplane will interface to the PDB through edge finger connections; these connections are designed to interface to an FCI MPN 10117936-003LF connector (or equivalent) on the PDB. This interface will provide for a minimum of 50A (600W) capacity on the 12V connections.

Table 10 shows the pinout for the edge finger connector to the PDB.

| Pin             | Signal name    | Pin | Signal name    |

|-----------------|----------------|-----|----------------|

| P1              | GND            | Р5  | GND            |

| P2              | GND            | Р6  | GND            |

| Р3              | P12V           | Р7  | P12V           |

| P4              | P12V           | Р8  | P12V           |

| Orientation key |                |     |                |

| S1              | SERIAL_B1_TXD1 | S7  | SERIAL_B2_TXD1 |

| S2              | SERIAL_B1_RXD1 | S8  | SERIAL_B2_RXD1 |

| S3              | BLADE_B1_EN1   | S9  | BLADE_B2_EN1   |

| S4              | PSU_B1_ALERT_N | S10 | PSU_B2_ALERT_N |

| S5              | SERIAL_B1_TXD2 | S11 | SERIAL_B2_TXD2 |

| S6              | SERIAL_B1_RXD2 | S12 | SERIAL_B2_RXD2 |

#### Table 10: PDB 12V power connector pinout

Table 11 describes the signals for this interface.

#### Table 11: PDB 12V power connector signal descriptions

| Signal name        | I/O | Logic | Description                                                                                                |

|--------------------|-----|-------|------------------------------------------------------------------------------------------------------------|

| SERIAL_B1_TXD[2:1] | I   | 3.3V  | Universal Asynchronous Receiver/Transmitter (UART) serial communication from the Chassis Manager to blade1 |

| SERIAL_B1_RXD[2:1] | 0   | 3.3V  | UART serial communication from blade 1 to the Chassis<br>Manager                                           |

| BLADE_B1_EN1       | Ι   | 3.3V  | Blade1 Enable from the Chassis Manager                                                                     |

| PSU_B1_ALERT_N     | Ι   | 3.3V  | Power supply alert from the Chassis Manager or PSU                                                         |

| SERIAL_B2_TXD[2:1] | I   | 3.3V  | UART serial communication from the Chassis Manager to blade                                                |

| SERIAL_B2_RXD[2:1] | 0   | 3.3V  | UART serial communication from the blade to the Chassis<br>Manager                                         |

| Signal name    | I/O | Logic | Description                                        |

|----------------|-----|-------|----------------------------------------------------|

| BLADE_B2_EN1   | Ι   | 3.3V  | Blade2 Enable from the Chassis Manager             |

| PSU_B2_ALERT_N | Ι   | 3.3V  | Power supply alert from the Chassis Manager or PSU |

| P12V           | Ι   | 12V   | 12V power from PDB (PDU)                           |

### 6.6.2 Blade 12V Power Connector

The tray backplane will distribute 12V power to each blade slot through an AirMax Power 2x2 FCI MPN 10052620-4555P00LF header receptacle connector (or equivalent). The connector will provide for a minimum of 40A (480W capacity) for each blade.

Table 12 shows the pinout for the 12V power connector to the blade. Note that there are two of these connectors on the tray backplane, one for each blade.

| Pin | Signal name | Description            |  |  |  |

|-----|-------------|------------------------|--|--|--|

| A1  | GND         |                        |  |  |  |

| A2  | GND         |                        |  |  |  |

| A3  | GND         |                        |  |  |  |

| A4  | GND         |                        |  |  |  |

| A5  | GND         |                        |  |  |  |

| A6  | GND         |                        |  |  |  |

| B1  | P12V        | 12V raw power to blade |  |  |  |

| B2  | P12V        | 12V raw power to blade |  |  |  |

| В3  | P12V        | 12V raw power to blade |  |  |  |

| B4  | P12V        | 12V raw power to blade |  |  |  |

| B5  | P12V        | 12V raw power to blade |  |  |  |

| B6  | P12V        | 12V raw power to blade |  |  |  |

| C1  | P12V        | 12V raw power to blade |  |  |  |

| C2  | P12V        | 12V raw power to blade |  |  |  |

| C3  | P12V        | 12V raw power to blade |  |  |  |

| C4  | P12V        | 12V raw power to blade |  |  |  |

| C5  | P12V        | 12V raw power to blade |  |  |  |

| C6  | P12V        | 12V raw power to blade |  |  |  |

Table 12: Blade 12V power connector pinout

| Pin | Signal name | Description |

|-----|-------------|-------------|

| D1  | GND         |             |

| D2  | GND         |             |

| D3  | GND         |             |

| D4  | GND         |             |

| D5  | GND         |             |

| D6  | GND         |             |

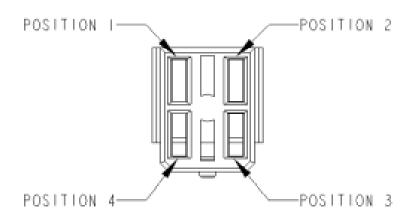

Figure 32 shows a front view of the header pins to the power connector.

Figure 32: Front view of header pins

Table 13 details the header pins and the current capacity.

| Pin        | Signal name             | Capacity (in A) |

|------------|-------------------------|-----------------|

| Position 1 | 12V return – first mate | 20A             |

| Position 2 | 12V supply              | 20A             |

| Position 4 | 12V supply              | 20A             |

| Position 3 | 12V return              | 20A             |

### 6.6.3 Blade SAS Interface

The connector interfacing SAS from the blade to the tray backplane will be AirMax VS2 3x6, FCI MPN 10122643-101LF (or equivalent). Table 14 shows the pinout for the connector.

Note that only blade 1 is shown, but the pinouts for blade1 and blade 2 are identical. The designation **\_B1\_** in the signal names indicates a connection to blade 1, and **\_B2\_** indicates the connection to blade 2.

| GND         |             | GND             |               | GND         |             | J |

|-------------|-------------|-----------------|---------------|-------------|-------------|---|

| SAS_B1_RX7N | GND         | SAS_B1_RX5N     | GND           | SAS_B1_RX2N | GND         | I |

| SAS_B1_RX7P | SAS_B1_TX7N | SAS_B1_RX5P     | SAS_B1_TX4N   | SAS_B1_RX2P | SAS_B1_TX2N | Н |

| GND         | SAS_B1_TX7P | GND             | SAS_B1_TX4P   | GND         | SAS_B1_TX2P | G |

| SAS_B1_TX8N | GND         | SAS_B1_TX5N     | GND           | SAS_B1_TX3N | GND         | F |

| SAS_B1_TX8P | SAS_B1_RX6N | SAS_B1_TX5P     | SAS_B1_RX4N   | SAS_B1_TX3P | SAS_B1_RX1N | E |

| GND         | SAS_B1_RX6P | GND             | SAS_B1_RX4P   | GND         | SAS_B1_RX1P | D |

| SAS_B1_RX8N | GND         | BLADE_B1_EN1    | GND           | SAS_B1_RX3N | GND         | С |

| SAS_B1_RX8P | SAS_B1_TX6N | JBOD_B1_MATED_N | SERIAL_B1_RX1 | SAS_B1_RX3P | SAS_B1_TX1N | В |

| GND         | SAS_B1_TX6P | GND             | SERIAL_B1_TX1 | GND         | SAS_B1_TX1P | А |

| 6           | 5           | 4               | 3             | 2           | 1           |   |

#### Table 14: Blade SAS interface connector pinout

Table 15 describes the signals for this interface.

| Signal name    | I/O | Logic                          | Description                                                                   |  |

|----------------|-----|--------------------------------|-------------------------------------------------------------------------------|--|

| SAS_B1_TX[8:1] | I   | Current<br>mode logic<br>(CML) | 12Gb SAS Transmit from blade1                                                 |  |

| SAS_B1_RX[8:1] | 0   | CML                            | 12Gb SAS Receive to blade1                                                    |  |

| BLADE_B1_EN1   | 0   | 3.3V                           | Blade Enable from the Chassis Manager to blade<br>For use by JBOD             |  |

| SERIAL_B1_TX1  | 0   | 3.3V                           | Serial communication from the Chassis Manager to blade<br>For use by JBOD     |  |

| SERIAL_B1_RX1  | I   | 3.3V                           | Serial communication from the blade to the Chassis Manager<br>For use by JBOD |  |

| JBOD_MATED_N   | 0   | 3.3V                           | Indicates to blade that the blade is mated to TBP                             |  |

## 6.6.4 Mini-SAS HD Connector

The connector interfacing SAS from the tray backplane to SAS cables will be an SAS Mini-HD 1x2 connector, FCI MPN 10112627-101LF. Table 16 shows the connector pinout for a single x4 Mini-HD SAS connector.

Each connector supports a side-by-side cable (ports 1 and 2). There are two cable connections per tray backplane, one for each blade. Only blade 1 Port 1 is shown. Note that the designation **\_B1P1\_** in the signal names indicates a connection to Blade1 Port1.

| Pin | Signal name   | I/O | Logic | Description                  |

|-----|---------------|-----|-------|------------------------------|

| A1  | RSVD          | N/A |       | NC (not supported by design) |

| A2  | INTL          | N/A |       | NC (not supported by design) |

| A3  | GND           |     |       |                              |

| A4  | SAS_B1P1_RX2P | I   | CML   | SAS serial input from cable  |

| A5  | SAS_B1P1_RX2N | I   | CML   | SAS serial input from cable  |

| A6  | GND           |     |       |                              |

| A7  | SAS_B1P1_RX4P | I   | CML   | SAS serial input from cable  |

| A8  | SAS_B1P1_RX4N | I   | CML   | SAS serial input from cable  |

| A9  | GND           |     |       |                              |

| B1  | VACT          | N/A |       | NC (not supported by design) |

| B2  | MODPRSL       | N/A |       | NC (not supported by design) |

| B3  | GND           |     |       |                              |

| B4  | SAS_B1P1_RX1P | I   | CML   | SAS serial input from cable  |

| B5  | SAS_B1P1_RX1N | I   | CML   | SAS serial input from cable  |

| B6  | GND           |     |       |                              |

| B7  | SAS_B1P1_RX3P | I   | CML   | SAS serial input from cable  |

| B8  | SAS_B1P1_RX3N | I   | CML   | SAS serial input from cable  |

| B9  | GND           |     |       |                              |

| C1  | SCL           | N/A |       | NC (not supported by design) |

| C2  | SDA           | N/A |       | NC (not supported by design) |

| C3  | GND           |     |       |                              |

| C4  | SAS_B1P1_TX2P | 0   | CML   | SAS serial output to cable   |

| C5  | SAS_B1P1_TX2N | 0   | CML   | SAS serial output to cable   |

| C6  | GND           |     |       |                              |

| C7  | SAS_B1P1_TX4P | 0   | CML   | SAS serial output to cable   |

| C8  | SAS_B1P1_TX4N | 0   | CML   | SAS serial output to cable   |

| C9  | GND           |     |       |                              |

| D1  | VACT          | N/A |       | NC (not supported by design) |

| D2  | VMON          | N/A |       | NC (not supported by design) |

| D3  | GND           |     |       |                              |

#### Table 16: Mini-SAS HD connector pinout

| Pin | Signal name   | I/O | Logic | Description                |

|-----|---------------|-----|-------|----------------------------|

| D4  | SAS_B1P1_TX1P | 0   | CML   | SAS serial output to cable |

| D5  | SAS_B1P1_TX1N | 0   | CML   | SAS serial output to cable |

| D6  | GND           |     |       |                            |

| D7  | SAS_B1P1_TX3P | 0   | CML   | SAS serial output to cable |

| D8  | SAS_B1P1_TX3N | 0   | CML   | SAS serial output to cable |

| D9  | GND           |     |       |                            |

## 6.6.5 Blade 10Gb Ethernet Connector

The connector interfacing the 10GbE from the blade to the tray backplane will be an AirMax VS2 3x6 connector, FCI MPN 10122643-101LF (or equivalent).

Table 17 shows the pinout for the 10GbE connector. Note that only blade1 is shown, but the pinouts for blade1 and blade2 are identical. The designation **\_B1** in the signal name indicates a connection to blade1.

| GND            |                  | GND            |                | GND              |                | J |

|----------------|------------------|----------------|----------------|------------------|----------------|---|

| ETH40G_B1_TX0N | BLADE_MATED_B1_N | SKU_B1_ID1     | P3V3_B1_QSFP   | ETH10G_B1_PRES_N | GND            | I |

| ETH40G_B1_TX0P | ETH40G_B1_PRES_N | SERIAL_B1_TX2  | SERIAL_B1_TX1  | BLADE_B1_EN1     | ETH10G_B1_TXN  | н |

| GND            | PSU_B1_ALERT_N   | SERIAL_B1_RX2  | SERIAL_B1_RX1  | GND              | ETH10G_B1_TXP  | G |

| ETH40G_B1_RX0N | GND              | ETH40G_B1_SCL  | SKU_B1_ID0     | SKU_B1_ID2       | GND            | F |

| ETH40G_B1_RX0P | P3V3_B1_QSFP     | ETH40G_B1_SDA  | ETH10G_B1_SCL  | RSVD             | ETH10G_B1_RXN  | E |

| GND            | P3V3_B1_QSFP     | GND            | ETH10G_B1_SDA  | GND              | ETH10G_B1_RXP  | D |

| ETH40G_B1_TX1N | GND              | ETH40G_B1_TX2N | GND            | ETH40G_B1_RX3N   | GND            | с |

| ETH40G_B1_TX1P | ETH40G_B1_RX1N   | ETH40G_B1_TX2P | ETH40G_B1_RX2N | ETH40G_B1_RX3P   | ETH40G_B1_TX3N | В |

| GND            | ETH40G_B1_RX1P   | GND            | ETH40G_B1_RX2P | GND              | ETH40G_B1_TX3P | А |

| 6              | 5                | 4              | 3              | 2                | 1              |   |

#### Table 17: Blade 10GbE connector pinout

Table 18 describes the signals for this interface.

| Table 18: | Blade | 10GbE | signal | definitions |

|-----------|-------|-------|--------|-------------|

| 10010 10. | Didde | TOOPL | JIBLIU | actinitions |

| Bus type      | I/O | Logic | Description                              |

|---------------|-----|-------|------------------------------------------|

| ETH10G_B1_TX  | Ι   | CML   | 10GbE Transmit from Blade1 Port1 to SFP+ |

| ETH10G_B1_RX  | 0   | CML   | 10GbE Receive from Blade1 Port1 to SFP+  |

| ETH10G_B1_SCL | Ι   | 3.3V  | I2C Clock from the blade to SFP+         |

| ETH10G_B1_SDA | I/O | 3.3V  | I2C Data from the blade to SFP+          |

| Bus type          | I/O | Logic | Description                                                                                                                   |

|-------------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------|

| ETH10G_B1_PRES_N  | ο   | 3.3V  | Indicates the presence of a 10GbE cable to the blade through MOD_ABS signal from SFP+ connector                               |

| ETH40G_B1_TX[7:0] | Ι   | CML   | 10GbE Transmit from Blade1 Port2 to QSFP+                                                                                     |

| ETH40G_B1_RX[7:0] | 0   | CML   | 10GbE Receive from Blade1 Port2 to QSFP+                                                                                      |

| ETH40G_B1_SCL     | Ι   | 3.3V  | I2C Clock from the blade to QSFP+                                                                                             |

| ETH40G_B1_SDA     | I/O | 3.3V  | I2C Data from the blade to SFP+                                                                                               |

| ETH40G_B1_PRES_N  | 0   | 3.3V  | Indicates the presence of a 10GbE cable through the Direct<br>Attach Cable (DAC) PRESENT_N signal from the QSFP+<br>connector |

| SKU_B1_ID<2:0>    | 0   | 3.3V  | ID signal indicating the SKU of the tray backplane<br>Each should be tied to GND through a 0 ohm resistor                     |

| P3V3_B1_QSFP      | Ι   | 3.3V  | 3.3V SFP+ connector I2C device power                                                                                          |

| BLADE_B1_MATED_N  | 0   | 3.3V  | Indicates to the blade that the blade and tray backplane are<br>mated<br>Should be tied to GND on the tray backplane          |

| SERIAL_B1_RX[2:1] | I   | 3.3V  | UART serial communication from the blade to the Chassis<br>Manager<br>Two nodes per blade.                                    |

| SERIAL_B1_TX[2:1] | 0   | 3.3V  | UART serial communication from the Chassis Manager to the blade<br>Two nodes per blade                                        |

| BLADE_B1_EN1      | 0   | 3.3V  | Node/Blade Enable signal from the Chassis Manager to the blade                                                                |

| PSU_B1_ALERT_N    | 0   | 3.3V  | Power supply alert signal from the Chassis Manager or PSU                                                                     |

| MEZZ_B1_PRESENT_N | 0   | 3.3V  | Indicates to the blade that a tray mezzanine card is installed<br>Signal is tied to GND on the tray mezzanine card            |

| MEZZ_B1_EN        | Ι   | 3.3V  | 3.3V Power Enable for the tray mezzanine card                                                                                 |

| Ground            |     | 0V    | Ground pins                                                                                                                   |

## 6.6.6 10GbE SFP+ Connector

The connector interfacing 10GbE from the tray backplane to the Ethernet cables will be an SFP+ connector, FCI MPN 10099099-111LF (or equivalent). The connector shall be supported by a SFP+ connector cage, FCI MPN 10099100-011LF (or equivalent). The connector cage must not include a heat sink.

Table 19 shows the standard pinout for the SFP+ connector. The design supports Direct Attach Cable (DAC) and does not support active cables.

| Pin | Signal name | I/O | Logic | Description                                                                            |

|-----|-------------|-----|-------|----------------------------------------------------------------------------------------|

| 1   | VEET        |     |       | Module transmitter ground                                                              |

| 2   | TX_FAULT    | 0   | LVTTL | Module transmitter fault (not used)<br>Low voltage transistor-transistor logic (LVTTL) |

| 3   | TX_DISABLE  | I   | LVTTL | Transmitter disable (not used)                                                         |

| 4   | SDA         | I/O | LVTTL | I2C data                                                                               |

| 5   | SCL         | I   | LVTTL | I2C clock                                                                              |

| 6   | MOD_ABS     | 0   |       | Module absent<br>Connected to GND in the module                                        |

| 7   | RSO         | I   | LVTTL | Rate select 0 (not used)                                                               |

| 8   | RX_LOS      | 0   | LVTTL | Receiver loss of signal (not used)                                                     |

| 9   | RS1         | I   | LVTTL | Rate select 1 (not used)                                                               |

| 10  | VEER        |     |       | Module receiver ground                                                                 |

| 11  | VEER        |     |       | Module receiver ground                                                                 |

| 12  | RD_N        | 0   | CML   | Receiver non-inverted data output                                                      |

| 13  | RD_P        | 0   | CML   | Receiver inverted data output                                                          |

| 14  | VEER        |     |       | Module receiver ground                                                                 |

| 15  | VCCR        |     |       | Module receiver 3.3V supply                                                            |

| 16  | VCCT        |     |       | Module transmitter 3.3V supply                                                         |

| 17  | VEET        |     |       | Module transmitter ground                                                              |

| 18  | TD_P        | I   | CML   | Transmitter non-inverted data input                                                    |

| 19  | TD_N        | I   | CML   | Transmitter inverted data input                                                        |

| 20  | VEET        |     |       | Module transmitter ground                                                              |

#### Table 19: 10GbE SFP+ connector pinout

### 6.6.7 40GbE QSFP+ Connector

The connector interfacing 40GbE from the tray backplane to Ethernet cables will be a QSFP+ connector, FCI MPN 10099113-102LF (or equivalent). The connector will be supported by a QSFP+ connector cage, FCI MPN 10099114-001LF (or equivalent). The connector cage must not include a heat sink.

Table 20 shows the standard pinout for the QSFP+ connector. The design supports DAC only, and does not support active cables.

| Pin | Signal name    | I/O | Logic  | Description                         |

|-----|----------------|-----|--------|-------------------------------------|

| 1   | GND            |     |        | Ground                              |

| 2   | ETH40G_B1_TX2P | 0   | CML    | 10G data output to cable            |

| 3   | ETH40G_B1_TX2P | 0   | CML    | 10G data output to cable            |

| 4   | GND            |     |        | Ground                              |

| 5   | ETH40G_B1_TX4N | 0   | CML    | 10G data output to cable            |

| 6   | ETH40G_B1_TX4P | 0   | CML    | 10G data output to cable            |

| 7   | GND            |     |        | Ground                              |

| 8   | ModSelL        | 0   | LVTTL  | Module select (not used)            |

| 9   | ResetL         | 0   | LVTTL  | Module reset (not used)             |

| 10  | VccRx          | 0   |        | +3.3V power supply receiver         |

| 11  | SCL            | I/O | LVCMOS | 2-wire serial interface clock       |

| 12  | SDA            | I/O | LVCMOS | 2-wire serial interface data        |

| 13  | GND            |     |        | Ground                              |

| 14  | ETH40G_B1_RX3P | I   | CML    | 10G data input from cable           |

| 15  | ETH40G_B1_RX3N | Ι   | CML    | 10G data input from cable           |

| 16  | GND            |     |        | Ground                              |

| 17  | ETH40G_B1_RX1P | Ι   | CML    | 10G data input from cable           |

| 18  | ETH40G_B1_RX1N | Ι   | CML    | 10G data input from cable           |

| 19  | GND            |     |        | Ground                              |

| 20  | GND            |     |        | Ground                              |

| 13  | RD_P           | 0   | CML    | Receiver inverted data output       |

| 14  | VEER           |     |        | Module receiver ground              |

| 15  | VCCR           |     |        | Module receiver 3.3V supply         |

| 16  | VCCT           |     |        | Module transmitter 3.3V supply      |

| 17  | VEET           |     |        | Module transmitter ground           |

| 18  | TD_P           | Ι   | CML    | Transmitter non-inverted data input |

| 19  | TD_N           | Ι   | CML    | Transmitter inverted data input     |

| 20  | VEET           |     |        | Module transmitter ground           |

#### Table 20: 40GbE QSFP+ connector pinout

| 7 7 7 7 8 |                    |     | 1     |                                                  |

|-----------|--------------------|-----|-------|--------------------------------------------------|

| Pin       | Signal name        | I/O | Logic | Description                                      |

| 21        | ETH40G_B1_RX2N     | Ι   | CML   | 10G data input from cable                        |

| 22        | ETH40G_B1_RX2P     | Ι   | CML   | 10G data input from cable                        |

| 23        | GND                |     |       | Ground                                           |

| 24        | ETH40G_B1_RX4N     | Ι   | CML   | 10G data input from cable                        |

| 25        | ETH40G_B1_RX4P     | Ι   | CML   | 10G data input from cable                        |

| 26        | GND                |     |       | Ground                                           |

| 27        | ModPrsL            | I   | LVTTL | Module present<br>Connected to GND in the module |

| 28        | IntL               | Ι   | LVTTL | Interrupt (not used)                             |

| 29        | VccTx              | 0   |       | +3.3V power supply transmitter                   |

| 30        | Vcc1               | 0   |       | +3.3V power supply                               |

| 31        | LPMode             | 0   | LVTTL | Low power mode (not used)                        |

| 32        | GND                |     |       | Ground                                           |

| 33        | ETH40G_B1_TX3P     | 0   | CML   | 10G data output to cable                         |

| 34        | ETH40G_BLADE1_TX3N | 0   | CML   | 10G data output to cable                         |

| 35        | GND                |     |       | Ground                                           |

| 36        | ETH40G_B1_TX1P     | 0   | CML   | 10G data output to cable                         |

| 37        | ETH40G_B1_TX1N     | 0   | CML   | 10G data output to cable                         |

| 38        | GND                |     |       | Ground                                           |

|           |                    |     |       |                                                  |