Telco enhanced Open Rack Server variant

Revision 0.1

Author: Samuli Toivola, Nokia

28/09/2018 1 / 87

# License (OCP CLA Option)

Contributions to this Specification are made under the terms and conditions set forth in **Open Compute Project Contribution License Agreement ("OCP CLA") ("**Contribution License") by: **Nokia Solutions and Networks OY**

You can review the signed copies of the applicable Contributor License(s) for this Specification on the OCP website at <a href="http://www.opencompute.org/products/specsanddesign">http://www.opencompute.org/products/specsanddesign</a>

Usage of this Specification is governed by the terms and conditions set forth in **Open Compute Project** Hardware License – Permissive ("OCPHL Permissive"), ("Specification License").

You can review the applicable Specification License(s) executed by the above referenced contributors to this Specification on the OCP website at http://www.opencompute.org/participate/legal-documents/

**Note**: The following clarifications, which distinguish technology licensed in the Contribution License and/or Specification License from those technologies merely referenced (but not licensed), were accepted by the Incubation Committee of the OCP: [insert "None" or a description of the applicable clarifications].

NOTWITHSTANDING THE FOREGOING LICENSES. THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN, THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO, OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION, INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

28/09/2018 2 / 87

# **Contents**

| License | (OCP CLA Option)              | 2  |

|---------|-------------------------------|----|

| 1       | Introduction                  | 5  |

| 2       | Hardware Structure            | 6  |

| 2.1     | Major Hardware Components     | 7  |

| 2.1.1   | Processor                     | 9  |

| 2.1.2   | System Memory Interface       | 14 |

| 2.1.3   | Lewisburg PCH                 | 16 |

| 2.1.4   | PCI Express                   | 20 |

| 2.1.5   | Ethernet                      | 23 |

| 2.1.6   | BMC                           | 24 |

| 2.1.7   | CPLD                          | 30 |

| 2.1.8   | TPM                           | 31 |

| 2.2     | Power Feed                    | 32 |

| 2.2.1   | System Power Distribution     | 33 |

| 2.2.2   | Power Sequence                | 36 |

| 2.2.3   | Voltage Monitoring and Alarm  | 38 |

| 2.3     | Printed Circuit Board         | 40 |

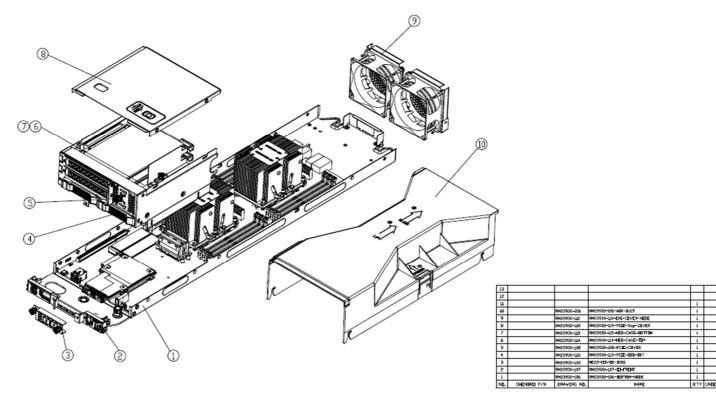

| 3       | Mechanical Overview           | 41 |

| 3.1     | Main Components Placement     | 42 |

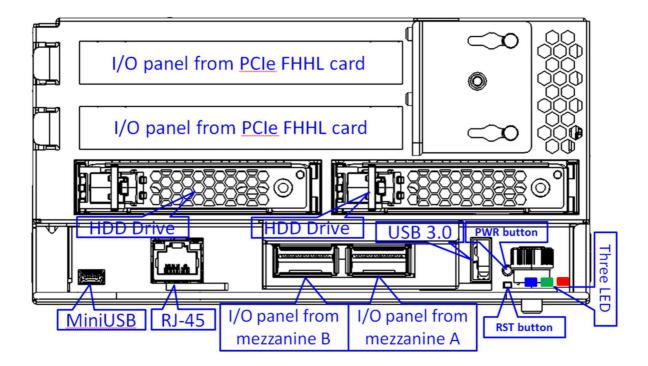

| 3.2     | Front panel design            | 43 |

| 3.3     | Fan                           | 45 |

| 3.4     | Cables                        | 46 |

| 3.5     | Board Subassembly             | 48 |

| 3.6     | Server photos                 | 50 |

| 4       | Interfaces                    | 51 |

| 4.1     | Interfaces at the Front Panel | 52 |

| 4.1.1   | Ethernet Port                 | 52 |

| 4.1.2   | USB 3.0                       | 53 |

| 4.1.3   | Mini USB                      | 53 |

| 4.2     | Interfaces at the Rear Side   | 55 |

| 4.2.1   | Power Input                   | 55 |

| 4.2.2 | Signal Interconnect             | 55 |

|-------|---------------------------------|----|

| 4.3   | Interfaces inside the Board     | 56 |

| 4.3.1 | M.2 Connector                   | 56 |

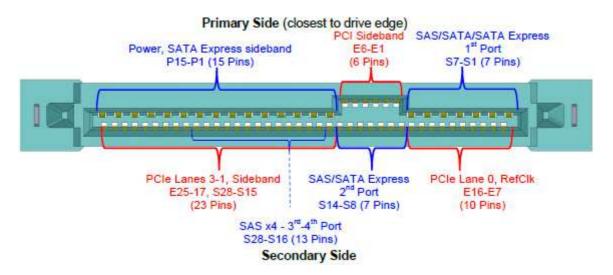

| 4.3.2 | U.2 Connector                   | 58 |

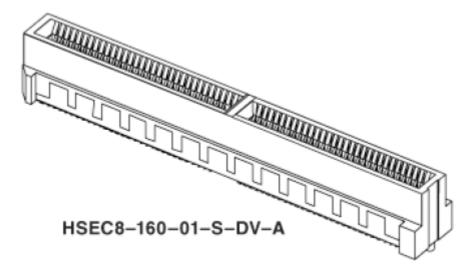

| 4.3.3 | Mezzanine Connector             | 62 |

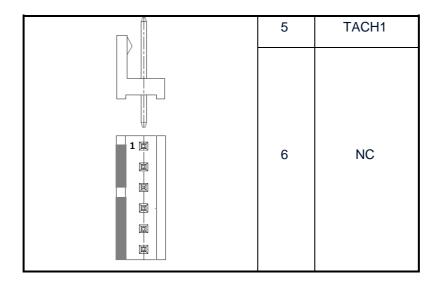

| 4.3.4 | Fan Connector                   | 66 |

| 4.4   | PCIe Riser Slot                 | 67 |

| 4.5   | Jumper                          | 72 |

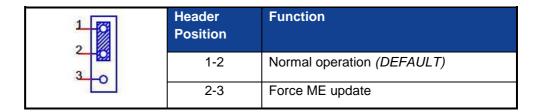

| 4.5.1 | ME Update                       | 72 |

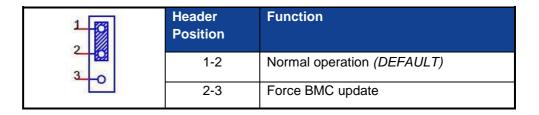

| 4.5.2 | BMC Update                      | 73 |

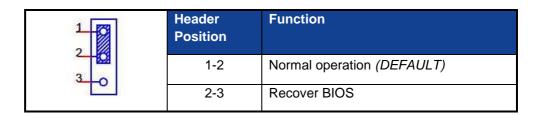

| 4.5.3 | BIOS Recovery                   | 73 |

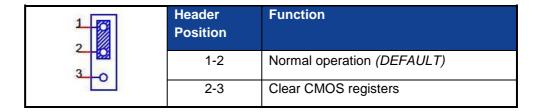

| 4.5.4 | Clear CMOS                      | 73 |

| 5     | Operating the unit              | 74 |

| 5.1   | Unit Start-up                   | 74 |

| 5.2   | LED                             | 75 |

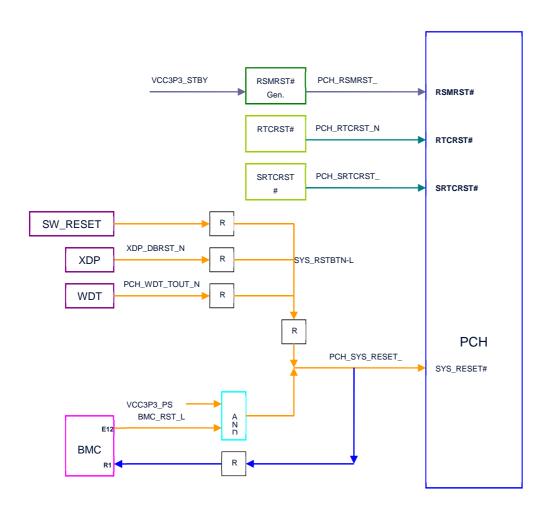

| 5.3   | Reset Logic                     | 75 |

| 5.3.1 | Power-up Reset                  | 75 |

| 5.3.2 | Reset Button                    | 75 |

| 5.3.3 | BMC Initiated Reset             | 76 |

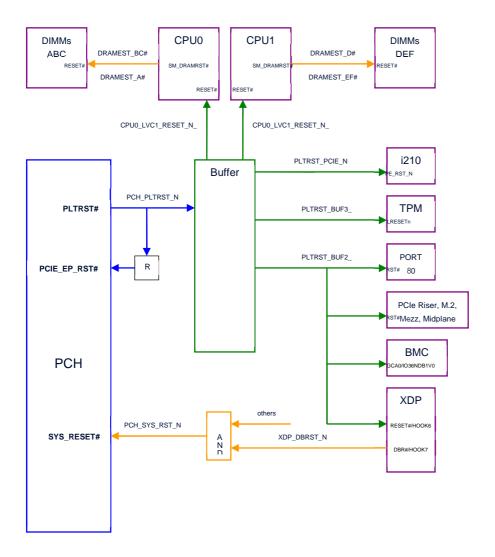

| 5.3.4 | Reset implementation            | 78 |

| 5.4   | System Management               | 80 |

| 5.4.1 | Hardware Monitor                | 82 |

| 5.4.2 | Power control via IPMI over LAN | 83 |

| 5.4.3 | Serial over LAN                 | 83 |

| 5.4.4 | FRU                             | 83 |

| 5.4.5 | SEL                             | 83 |

| 5.5   | Error Handling                  | 84 |

| 6     | Environmental                   | 86 |

| 7     | Labels and Markings             | 86 |

|       |                                 |    |

# 1 Introduction

Nokia has designed OCP Open Rack V2 compatible server variant optimized to telco NFV use cases.

New server design solves challenges to meet various customers CO site specific requirements like EMI shielding and ETSI environmental requirements.

Server design enables flexible and effective configurations for various networking and storage focused use cases.

Enhancements to NUMA performance issue have implemented by PCIe routing to CPU1 from riser slot and to storage performance with redundant NVMe SSD's.

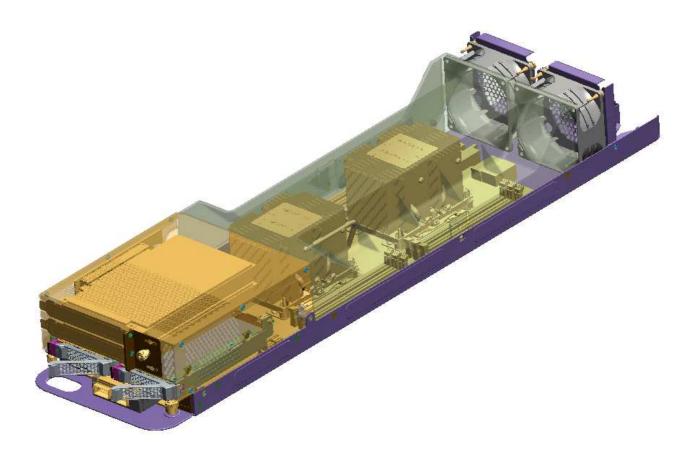

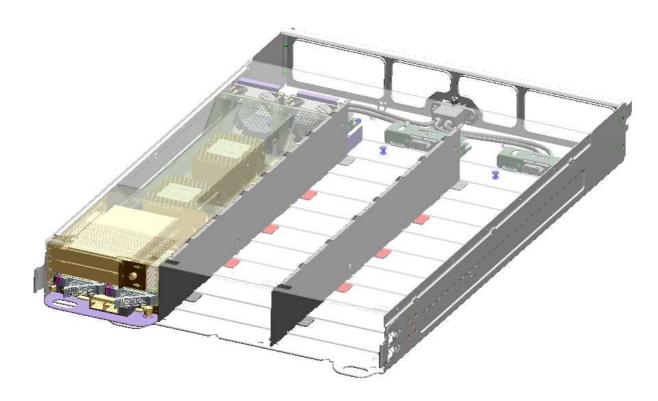

Open Rack Server variant is a design based on the Intel® Purley platform, including dual Skylake processors and a Lewisburg PCH chipset. The motherboard is designed to be fitted into an OCP Open Rack V2 compatible server sled. The server sled is compatible with the Cubby shelf and is compatible with the OCP rack design, Open Rack V2 (ORv2).

This document is the hardware specification of server sled, and is used to describe, at a high level, the hardware implementation details. Some features other than hardware, such as the mechanical, software, and system management are also briefly covered.

28/09/2018 5 / 87

# 2 Hardware Structure

The following table lists in tabular format the major hardware components:

| Form Factor      | Board dimensions 6.5"x20"                                                                                                            |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Processor        | Dual Intel® Skylake Server processors                                                                                                |

|                  | Total 12 DIMMs DDR4                                                                                                                  |

| Memory           |                                                                                                                                      |

|                  | 6 channels per CPU, 1 DIMM per channel                                                                                               |

|                  | Support RDIMM (SR and DR)                                                                                                            |

| Chipset          | Intel Lewisburg PCH (C621)                                                                                                           |

| Gigabit Ethernet | 1 x Shared-GbE RJ45 from Intel I210, driven by BMC through NC SI and SMBus                                                           |

| Serial ATA       | Four SATA3 ports. Supported storage interfaces, M.2 and U.2. Two ports for each interface                                            |

|                  | Advanced Host Controller Interface (AHCI) support                                                                                    |

| LPC interface    | Low Pin Count (LPC) interface support                                                                                                |

| SPI              | Serial Peripheral Interface, dual BIOS support. BMC is capable to perform BIOS remote upgrade and recovery                           |

| TPM              | Infineon SLB9670 TPM compliant with rev 1.2/2.0 standard                                                                             |

| ВМС              | ASPEED AST2500                                                                                                                       |

| PCIe slot        | One PCIe Gen3 x32 slot, which holds x32 PCIe Gen 3 signals, x16 from CPU0 and x16 from CPU1. The slot supports two type riser cards: |

|                  | Type A Riser: One slot type.                                                                                                         |

|                  | Slot1 is PCIe x16 connector with x16 PCIe signal from CPU0 and support FHHL PCIE card.                                               |

|                  | Type B Riser: Two slots type.                                                                                                        |

|                  | Bottom slot (Slot2) is x16 PCIe connector with x16 PCIe signal from CPU0 and support FHHL PCIe card.                                 |

|                  | TOP slot (Slot3) is x16 PCIe connector with x16 PCIe signal from CPU1 and also support FHHL PCIe card.                               |

| OCP Mezzanine    | Two PCIe x8 OCP Mezzanine Card specification 2.0 compliant connectors with dual x8 PCIe Gen 3 signal from CPU0.                      |

| USB              | One USB 3.0/2.1 compliant port on the front panel                                                                                    |

| mini-B USB       | One mini-B USB port on the front panel for BMC debug and in-band firmware update                                                     |

| M.2              | Two M.2 connectors. Each connector supports one PCle x1 and one optional PCle x1 / SATA.                                             |

|                  | Support form factor 2280 single-side and double-side M.2 module.                                                                     |

28/09/2018 6 / 87

**U.2**

Two U.2 connectors. Each connector supports one SATA and one PCle x4.

## **Table 1 Server Sled Hardware Component Summary**

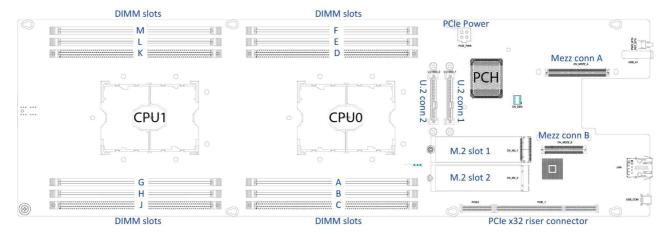

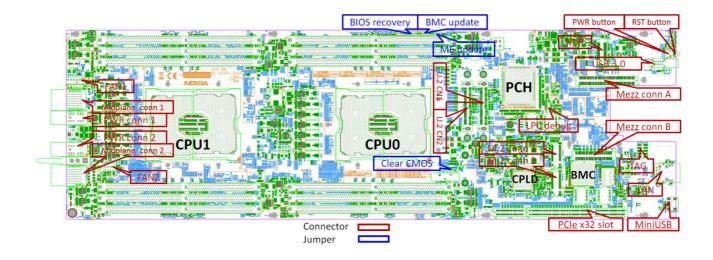

## 2.1 Major Hardware Components

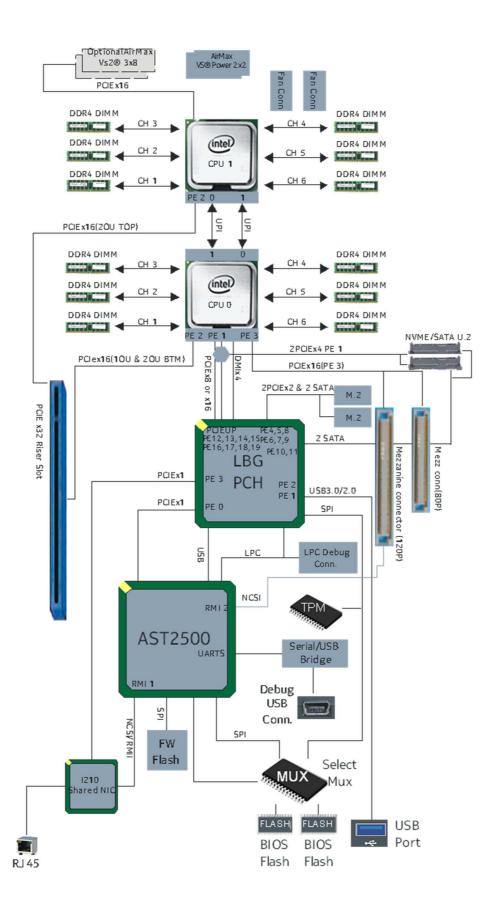

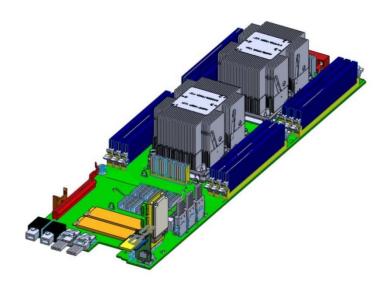

Open Rack Server is a dual processor server board. It consists of the Intel® Skylake server processor product family, used in conjunction with the Lewisburg PCH. The reference design is the Intel® Crescent City Customer Reference board, optimized for the telco NFV use cases.

Each Skylake processor supports 6 RDIMMs. The master processor (CPU0) supports one PCIe Gen3 x16 interface for the riser slot and two OCP mezzanine interfaces. The slave processor (CPU1) supports one PCIe Gen3 x16 interface for the riser slot and two PCIe Gen3 x8 interface for the middle plane.

The PCH supports two M.2, two U.2, SATA3, and one USB 3.0 ports. One LPC interface works with BMC controlled multiplexer to support dual BIOS.

One ASPEED AST2500 BMC for system management. It covers the power sequence control, hardware monitoring, and thermal control.

One 1000 Base-T Gigabit Ethernet LOM port with RJ-45.

For the security support, the server sled hardware design supports the BIOS secure boot and the TPM for security options.

The figure below shows the Server system block diagram.

28/09/2018 7 / 87

28/09/2018 8 / 87

Figure 1 Server Sled Block Diagram

## 2.1.1 Processor

The Skylake processor is the next generation of 64-bit, multi-core server processor built on 14-nm process technology. The processor socket type is the LGA3647-0 SMT socket. The package is a 43.18 x 50.24 mm Flip-Chip Land Grid Array (FC-LGA14).

The processor TDP can be up to 165W. Concerning the thermal design capability, the following SKU's processors are available with Open Rack Server:

| No. | Vendor | Model | Name    | Core    | Frequency | Watt |

|-----|--------|-------|---------|---------|-----------|------|

| 1   | Intel  | 4116  | Skylake | 12 Core | 2.1GHz    | 85W  |

| 2   | Intel  | 5118  | Skylake | 12 Core | 2.3GHz    | 115W |

| 3   | Intel  | 6130  | Skylake | 16 Core | 2.1GHz    | 125W |

| 4   | Intel  | 6138  | Skylake | 20 Core | 2.0GHz    | 125W |

| 5   | Intel  | 6140  | Skylake | 18 Core | 2.3GHz    | 140W |

| 6   | Intel  | 8160  | Skylake | 24 Core | 2.1GHz    | 150W |

| 7   | Intel  | 4108  | Skylake | 8 Core  | 1.8GHz    | 85W  |

| 8   | Intel  | 4114  | Skylake | 10 Core | 2.2GHz    | 85W  |

| 9   | Intel  | 5115  | Skylake | 10 Core | 2.4GHz    | 85W  |

| 10  | Intel  | 6148  | Skylake | 20 Core | 2.4GHz    | 150W |

| 11  | Intel  | 8176  | Skylake | 28 Core | 2.1GHz    | 165W |

| 12  | Intel  | 6130T | Skylake | 16 Core | 2.1GHz    | 125W |

| 13  | Intel  | 6142  | Skylake | 16 Core | 2.6GHz    | 150W |

| 14  | Intel  | 3104  | Skylake | 6 Core  | 1.7GHz    | 85W  |

| 15  | Intel  | 6150  | Skylake | 18 Core | 2.7GHz    | 165W |

Table 2 Intel Skylake Server Processor SKU's

Single processor mode is supported.

The following table summarizes the Skylake Server processor features.

| Features                   | Description         |

|----------------------------|---------------------|

| Memory: Technology Support | DDR4 ECC RDIMM      |

|                            | DDR4 ECC LRDIMM     |

|                            | DDR4 ECC LRDIMM 3DS |

28/09/2018 9 / 87

| Memory: Speeds                                  | DDR4:                                 |

|-------------------------------------------------|---------------------------------------|

|                                                 | 2666, 2400, 2133 and 1866 MT/s        |

| Memory: Max DIMMs per Socket                    | 6                                     |

| Memory: Max Capacity (w/256 GB DIMM) per Socket | 1536 GB                               |

| Intel® UPI Interfaces per Socket                | 2                                     |

| Intel® UPI Speeds                               | 10.4 GT/s                             |

| PCI Express Lanes per Socket                    | 48 Gen3 lanes                         |

|                                                 | (plus 4 DMI3 lanes)                   |

| Peripheral Controller Hub (PCH)                 | Intel® LBG Series Chipset (Lewisburg) |

| PECI                                            | V3.1 compliant                        |

| TPM                                             | V1.2 and V2.0 compliant               |

#### **Table 3 Intel Skylake Server Processor Features**

Below subsections describe the thermal reporting and protection schemes.

#### 2.1.1.1 Platform Environmental Control Interface for thermal reporting

The Skylake CPU has an on-die Digital Thermal Sensor (DTS) for monitoring the processor die temperature. The DTS can be retrieved through S/W interface and H/W interface. The S/W interface is the processor Model Specific Register (MSR). The H/W interface is the Platform Environmental Control Interface (PECI). On server sled the PECI is implemented for accessing the DTS.

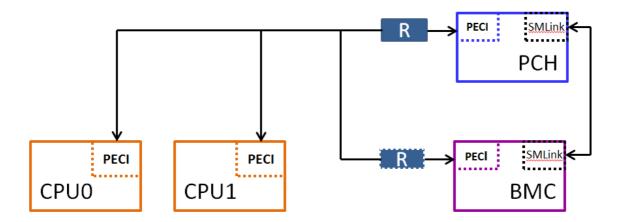

The PECI is a one-wire interface that provides a communication channel between a PECI client and a PECI master.

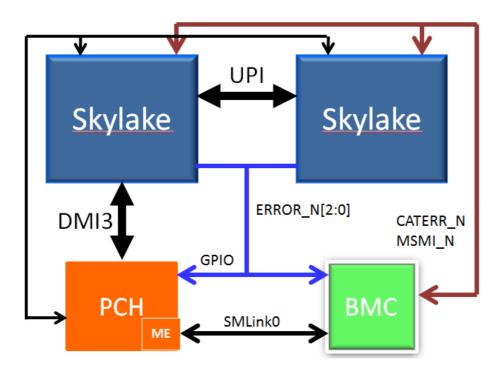

For a platform with BMC present, there are two different PECI connectivity options offering the PECI access to the BMC.

- PECI Proxy service of the Management Engine: PECI doesn't route to the BMC, but the BMC requires routing to the PCH SMLink0.

- PECI direct access from the BMC : PECI routes to the BMC instead of the PCH.

28/09/2018 10 / 87

Figure 2 PECI topology on server sled

The default PECI connection is routed to the PCH. The BMC accesses the PCH SMLink interface to get the thermal sensor data from CPU, DIMM, and PCH.

#### 2.1.1.2 Processor Thermal Protection

Basically, the processor thermal protection scheme is implemented with pure hardware level since Skylake. For previous generation processors, BIOS needs to configure the thermal monitor register such as the TM1 and TM2. Now it isn't required. The Skylake processor will select an appropriate scheme to use on a dynamic basis.

The processor has two internal thermal control signals for thermal protection. One signal is the PROCHOT#, and the other signal is THERMTRIP#.

#### PROCHOT#

The PROCHOT# is a bi-directional signal. It's connected between CPU and BMC. The following cases assert the PROCHOT#.

- When one or more cores of the processor reach the maximum safe operating temperature, the PROCHOT# is activated by CPU. An interrupt is generated. The interrupt is connected internally to the processor integrated local APIC controller. In this case, the PROCHOT# is sent to BMC just for status information and to make design flexible in case PROCHOT# is needed to generate NMI.

- BMC thermal sensors alarm. The BMC asserts the PROCHOT# to inform CPU speed down.

- CPU voltage regulator overheat. The regulator asserts the PROCHOT# to inform CPU speed down.

#### THERMTRIP#

When CPU's temperature goes to a catastrophically high point, its internal thermal protection mechanism activates the THERMTRIP# signal. The THERMTRIP# indicates one of two

28/09/2018 11 / 87

possible critical over temperature conditions. One is the processor junction temperature reaches a level that the permanent silicon damage may occur, the other is the system memory interface exceeds a critical temperature limit set by BIOS.

The THERMTRIP# is routed to the CPLD. If the THERMTRIP# is asserted, the CPLD will follow the power off sequence to turn all the power rails off to prevent CPU from eternal damage.

The CPLD also re-directs the THERMTRIP# to the BMC. Once the THERMTRIP# is activated, the BMC will know the status and keep the event logged.

#### 2.1.1.3 Use of Power Management States

The Purley platform supports the power management states such as P-States, C-States, and S-States. They are all defined by the ACPI. Brief introduction as below.

#### **P-States**

The purpose of P-state is to optimize the CPU performance and the power efficiency. In practice, it means the Intel® SpeedStep technology.

Both the CPU running frequency and the operating voltage can be changed to vary the performance and the power consumption. Each P-state assigns a CPU frequency and voltage operating point. Configure the P-states transition properly to get the optimal performance and power efficiency.

The software, mainly the OS and BIOS, has the permission to make P-state change. The software monitors the loading status and change the CPU frequency by writing to the CPU MSRs. Based on the selected frequency and the number of active processor cores, the voltage is regulated accordingly.

P-states transition rule is summarized as below.

- If the target frequency is higher than the current frequency, the voltage is ramped up in steps to an optimized voltage. This voltage is signaled by the SVID bus to the voltage regulator. Once the voltage is established, the PLL locks on to the target frequency.

- If the target frequency is lower than the current frequency, then the PLL locks to the target frequency, then transitions to a lower voltage by signaling the target voltage on the SVID bus.

- Software-requested transitions are accepted at any time. If a previous transition is in progress, then the new transition is deferred until the previous transition is completed.

The number of P-states will vary depending on the CPU SKU. P1 means the highest speed. The other P-states are the descending of P0 with a defined frequency stepping. For Skylake, the stepping is 100MHz.

**NOTE**: P0 is also a P-state, but it represents the turbo frequency. Only few SKUs support the Turbo mode.

#### **C-States**

ACPI defines the low-power idle states as C-state when the CPU is going to be idle. The C-states are the CPU SKU specific as well. The normal operating mode is C0. More power saving actions are taken for numerically higher C-states. In lower C-states the processor stops

28/09/2018 12 / 87

executing and power is saved by turning different parts of the processor off. The lower the state, the higher latency comes back to C0.

## **S-States**

ACPI defines the system level power states as the S-states. There are seven S-states : S0  $\sim$  S6. The S-states definition are quite common for PC industry. S0 means system on. S1 means power on suspend. S3 means Suspend to RAM. S5 means soft off.

All the S-states transitions are initiated by the CPH

## P-States, C-States, S-States combinations

The following table shows the combinations of different P-states, C-states, and S-States.

28/09/2018 13 / 87

| Sleep (S) State | Processor Core<br>(C) State | System Clocks   | Description                             |

|-----------------|-----------------------------|-----------------|-----------------------------------------|

| S0              | CO                          | On              | CPU On, P-states change per application |

| SO              | C1 or C1E                   | On              | CPU Auto-Halt                           |

| S0              | C3                          | On              | CPU Deep Sleep                          |

| S0              | C6 or C7                    | On              | CPU Deep Power<br>Down                  |

| S1              | C6 or C7                    | On              | Power on Suspend                        |

| S3              | Power off                   | Off, except RTC | Suspend to RAM                          |

| S4              | Power off                   | Off, except RTC | Suspend to Disk                         |

| S5              | Power off                   | Off, except RTC | Soft Off                                |

**Table 4 Different Power States Combinations**

## 2.1.2 System Memory Interface

The Intel® Skylake processor product family memory interface supports the DDR4 DIMM technology. The supported features are listed below.

28/09/2018 14 / 87

| Туре       |                         | DIMM Capac   | ity (GB)     |  |  |  |  |  |  |

|------------|-------------------------|--------------|--------------|--|--|--|--|--|--|

|            | Ranks Per DIMM and Data | DRAM Density |              |  |  |  |  |  |  |

|            | Width                   | 4Gb          | 8Gb          |  |  |  |  |  |  |

| RDIMM      | SRx4                    | 8GB          | 16GB         |  |  |  |  |  |  |

| RDIMM      | SRx8                    | 4GB          | 8GB          |  |  |  |  |  |  |

| RDIMM      | DRx8                    | 8GB          | 16GB         |  |  |  |  |  |  |

| RDIMM      | DRx4                    | 16GB         | 32GB         |  |  |  |  |  |  |

| RDIMM 3DS  | QRx4                    | N/A          | 2H-<br>64GB  |  |  |  |  |  |  |

|            | QRx8                    | N/A          | 4H-<br>128GB |  |  |  |  |  |  |

| LRDIMM     | QRx4                    | 32GB         | 64GB         |  |  |  |  |  |  |

| LRDIMM 3DS | QRx4                    | N/A          | 4H-<br>164GB |  |  |  |  |  |  |

|            | 8Rx4                    | N/A          | 64GB         |  |  |  |  |  |  |

## **Table 5 Supported DDR4 DIMM Type List**

Maximum DIMMs per socket: six

• Each channel consists of 64 data and 8 ECC bits

Supported data rate: 1866, 2133, 2400, 2666MT/s

• Unbuffered DIMM is not supported

28/09/2018 15 / 87

*NOTE*: 3DS means 3D stack. 2H or 4H means the stack counts by using the through-silicon vias(TSV).

## 2.1.3 Lewisburg PCH

Open Rack Server incorporates the Lewisburg PCH SKU LBG-1G(C621) for extensive I/O support.

Functions and capabilities include:

| Supported I/O and features | Description                                                                                                 |

|----------------------------|-------------------------------------------------------------------------------------------------------------|

| DMI3                       | PCIe Gen3 lane x4, interface between CPU and PCH                                                            |

| PECI                       | Sideband signals between CPU and PCH                                                                        |

| PCIe Gen 3                 | Root port : 20 lanes                                                                                        |

|                            | Downsteam port : 24 lanes                                                                                   |

| SATA3                      | AHCI mode support, RAID mode support                                                                        |

|                            | Support 6 ports on server sled                                                                              |

| USB 3.0                    | One Standard-A USB 3.0 port on the front panel                                                              |

| SPI                        | Support 3 devices at most, including two flash and one TPM                                                  |

| LPC v1.1                   | 24 MHz, No DMA                                                                                              |

| SMBus v2.0                 | Be a SMBus host and provide up to 6 SMLink interface                                                        |

| ACPI v4.0a                 | Advanced power management support                                                                           |

| Real Time Clock            | Operate with 32.768KHz crystal to count date and time. 256 bytes of battery-backed RAM to store system data |

| GPIO                       |                                                                                                             |

Table 6 Lewisburg PCH I/O Features

Below subsections describe the LPC, SPI, and SMBus topology. They are concerning the system management scheme.

28/09/2018 16 / 87

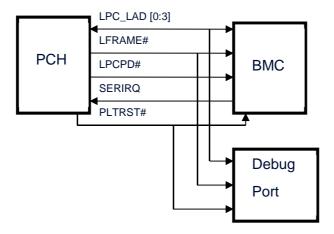

#### 2.1.3.1 LPC Topology

. BMC and a BIOS postcode indicator are located on the LPC bus. The indicator is for debug purpose only.

Figure 3 LPC bus topology on server sled

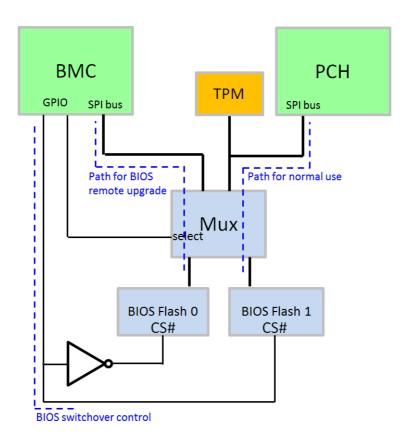

## 2.1.3.2 SPI Topology

The PCH has a SPI bus and supports up to two SPI compatible flash devices.

Open Rack Server is equipped with two boot flashes located on the SPI interface, where BIOS image and ME firmware are stored. The two flash devices keep duplicated BIOS image and ME firmware for redundancy.

ME means management engine. It's a hardware-based management scheme initiated by Intel. ME can monitor and maintain the system through out-of-band connection. This means ME can work without the presence of OS or locally installed management agent. ME needs to load firmware to work and the firmware saves in the BIOS flash.

Below a figure shows the connection between the PCH, BMC, and two BIOS flashes. There is a multiplexer to switch the BIOS flashes to the PCH or the BMC. The multiplexer is controlled by the BMC.

For normal use, the BMC controls the multiplexer to switch the BIOS flashes to the PCH SPI bus. The PCH can load BIOS code for boot up, or access the flash content for application.

28/09/2018 17 / 87

For BIOS remote upgrade, the BMC controls the multiplexer to switch the BIOS flashes to the BMC SPI bus. The BMC can control the relative chip select (CS#) to choose the flash for upgrade.

Figure 4 SPI Topology for Dual BIOS Support

#### Redundancy

Open Rack Server saves the same copies of BIOS image and ME firmware on two separate SPI flashes. Each copy of the BIOS portion consists of boot block and main BIOS block. In addition, the flash also contains vendor specific data and setup data. BIOS vendor shall specify and document the exact organization (memory map) of the SPI flashes.

It is controllable to set either flash 0 or flash 1 as the active BIOS flash while the other flash becoming backup. The flash selection is controlled by BMC. The SW spec details how the active flash is selected. Once selected, the active flash keeps active over any kind of resets but is defaulted to flash 0 after power down.

BMC includes two watchdog timers to monitor the BIOS boot up status. One is the FRB2 WDT, the other is the POST WDT. The FRB2 WDT monitors the BIOS code loading and decompression status. The POST WDT monitors the BIOS code running status.

28/09/2018 18 / 87

When BIOS code execution starts, the FRB2 WDT is enabled and started automatically by the BMC. BIOS boot block verifies code integrity by checksum calculation. If the active BIOS boot block is found data missing or corrupted, the FRB2 WDT timeout. BMC regards the timeout as a BIOS code loading failure and switchover to the backup flash. BMC makes BIOS switchover by triggering CS# pin to set the relative flash active. After that, BMC sends a reset to reboot system.

If BIOS code loads and starts to run successfully, BIOS must send commands to BMC to disable the FRB2 WDT and enable the POST WDT. If BIOS finishes the code execution, BIOS sends commands to BMC to stop the POST WDT before transferring to OS. Otherwise, the POST WDT timeout will cause the BMC reset the system.

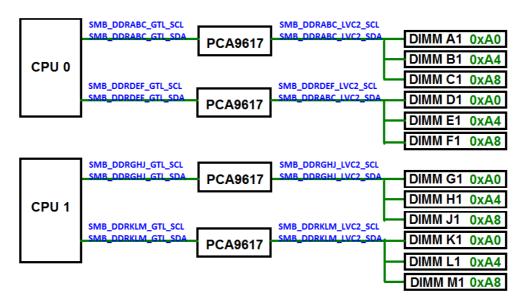

## 2.1.3.3 SMBus Topology

PCH accesses the SMBus for reading SPD data from DIMMs and configure clock synthesizer work mode.

The SMBus configuration is as below.

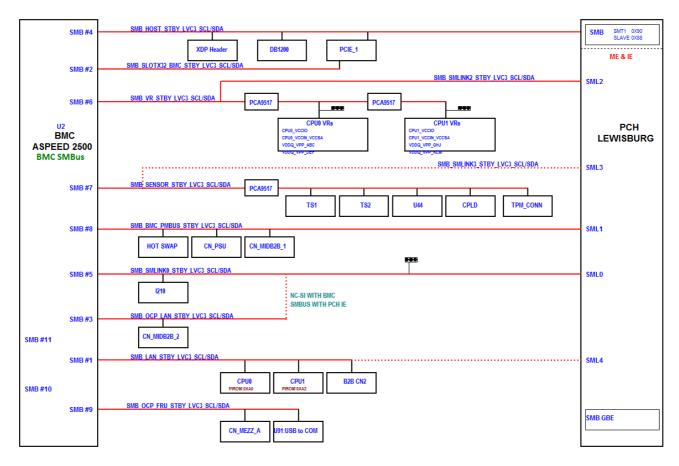

Figure 5 SMBus configuration on server sled

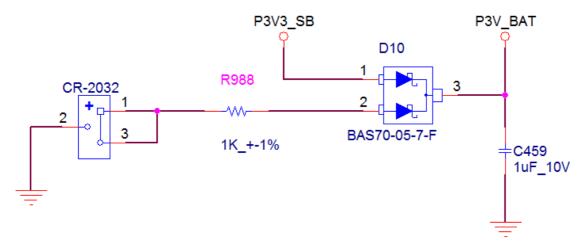

## 2.1.3.4 Real Time Clock (RTC)

The PCH contains a Motorola MC146818B-compatible real-time clock with 256 bytes of battery-backed RAM. There is two key functions for the RTC. One is to keep track of the time of day and the other is to store the system data.

To count the time of day, the RTC operates with a 32.768KHz crystal. To store the system data, a 3V battery supplies the power for the RAM to keep system data.

28/09/2018 19 / 87

The RTC power circuit is implemented as below. The 3.3V standby power is ORed with the battery power through a diode. When system power on, the 3.3V standby power supplies the power for the RTC circuit to preserve the battery energy. When mechanical off or power loss, the battery discharged to supply the RTC circuit.

Figure 6 RTC Power Circuit on server sled

The PCH RTC circuit consumes 6uA at most. And the minimum voltage for holding the RTC data is 2V. The nominal capacity of the CR-2032 battery is 225mAh (to 2V).

225mAh / 6uA = 37500 hr = 4.28 yr.

At the worst case, the RTC data can be sustained for 4.28 years.

## 2.1.4 PCI Express

Both Skylake CPUs and the PCH provide PCI Express resources for I/O applications.

## **CPU PCI Express resource**

The processor PCIe lane assignment is shown as below.

CPU0

28/09/2018 20 / 87

| PCIe port   | PCIe lane width | Lane assignment                                                                                                                                                                                               |  |  |  |  |  |  |

|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Port 1      | Lane [7:0]      | These 8 lanes can optionally route to the PCH PCIe Upstream port or two U.2 connectors with BOM option. Each U.2 connector can get 4 lanes for application.  Default: Route the 8 lanes to two U.2 connectors |  |  |  |  |  |  |

|             | Lane [15:8]     | Straight to PCH PCIe Upstream port                                                                                                                                                                            |  |  |  |  |  |  |

| Port 2      | Lane [15:0]     | PCle x32 slot                                                                                                                                                                                                 |  |  |  |  |  |  |

| Port 3      | Lane [7:0]      | OCP mezzanine connector 1 (80 pin)                                                                                                                                                                            |  |  |  |  |  |  |

| Lane [15:8] |                 | OCP mezzanine connector 2 (120 pin)                                                                                                                                                                           |  |  |  |  |  |  |

|             |                 | CPU1                                                                                                                                                                                                          |  |  |  |  |  |  |

| PCle port   | PCIe lane width | Lane assignment                                                                                                                                                                                               |  |  |  |  |  |  |

| Port 1      | Lane [7:0]      | Middle plane connector 1 (non-stuff)                                                                                                                                                                          |  |  |  |  |  |  |

| Lane [15:8] |                 | Middle plane connector 2 (non-stuff)                                                                                                                                                                          |  |  |  |  |  |  |

| Port 2      | Lane [15:0]     | PCIe x32 slot                                                                                                                                                                                                 |  |  |  |  |  |  |

| Port 3      | Lane [15:0]     | Not used                                                                                                                                                                                                      |  |  |  |  |  |  |

**Table 7 CPU PCIe Resource Assignment**

## **PCH PCI Express resource - root port**

The PCH implements a flexible I/O architecture. It allows several high speed interfaces such as the PCIe, USB 3.0, and SATA to be multiplexed with limited high speed I/O(HSIO here after) lanes.

There are 26 HSIO lanes on the PCH. Some of them can be configured to be PCIe Gen3 ports, and others for USB 3.0 or SATA3 depending on the I/O requirement of a platform.

The PCH HSIO lane muxing is summarized as the figure below.

28/09/2018 21 / 87

## **HSIO** Muxing on Lewisburg

| FlexI/OPort#           | 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23 | 24 |   |

|------------------------|---|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|

| USB 3.0                | 1 | 2 | 3 | 4 | 5 | 6 | 7  | 8  | 9  | 10 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    | Γ |

| PCle Root Port         |   |   |   |   |   |   | 0  | 1  | 2  | w  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 |   |

| GbE                    |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |

| SATA                   |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    | 0  | 1  | 2  | 3  | 4  | 5  | 6  |   |

| SSATA                  |   |   |   |   |   |   |    |    |    |    |    |    | 0  | 1  | 2  | 3  | 4  | 5  |    |    |    |    |    |    |    |   |

| Pae Uplink             |   |   |   |   |   |   |    |    |    |    |    |    |    |    |    |    |    |    | 0  | 1  | 2  | 3  | 4  | 5  | 6  |   |

|                        |   |   |   |   |   |   | X4 |    |    | X4 |    |    | 4  |    |    | >  | (4 |    |    | Х  | 4  |    |    | χ  | 4  |   |

| PCIe Configurations    |   |   |   |   |   |   | χ  | 2  | X  | 2  | Х  | 2  | Х  | 2  | Х  | 2  | Х  | 2  | X  | 2  | χ  | 2  | Х  | 2  | Х  | 2 |

| rae con lingui auto is |   |   |   |   |   |   | Х  | 2  | X1 | X1 | X  | 2  | X1 | X1 | Х  | 2  | X1 | X1 | X  | 2  | X1 | X1 | Х  | 2  | X1 |   |

|                        |   |   |   |   |   |   | X1 | 1 |

Figure 7 PCH HSIO Lane Muxing

| HSIO lane width | Lane assignment                                                |

|-----------------|----------------------------------------------------------------|

| Lane [0]        | Configure to be PCIe Gen3 root port for BMC                    |

| Lane [1]        | Configure to be PCIe Gen3 root port for LAN controller i210-IT |

| Lane [3:2]      | Not used                                                       |

| Lane [5:4]      | Configure to be PCIe Gen3 root port for M.2 connector 1        |

| Lane [7:6]      | Configure to be PCIe Gen3 root port for M.2 connector 2        |

| Lane [8]        | Configure to be SATA3 port for M.2 connector 1                 |

| Lane [9]        | Configure to be SATA3 port for M.2 connector 2                 |

| Lane [10]       | Configure to be SATA3 port for U.2 connector 1                 |

| Lane [11]       | Configure to be SATA3 port for U.2 connector 2                 |

| Lane [15:12]    | Not used                                                       |

| Lane [19:16]    | Not used                                                       |

**Table 8 PCH HSIO Lane Assignment**

## **PCH PCI Express resource - uplink port**

The PCH has two uplink ports to handle the PCIe traffic towards the CPU. One is x16 port, the other is x8 port. The uplink ports configuration depends on the data transfer bandwidth requirement and the special functionality support such as the Intel® QAT or 10GbE port.

28/09/2018 22 / 87

The default SKU of server sled is implemented with the PCH SKU C621. It doesn't support the Intel ® QAT. Only the x16 uplink port is supported. The PCIe lane assignment is shown as below.

| PCIe port      | PCIe lane width | Lane assignment                                                 |  |  |  |  |

|----------------|-----------------|-----------------------------------------------------------------|--|--|--|--|

| x16 Lane [7:0] |                 | CPU0 PCIe port 1 for PCIe traffic or U.2 connector (BOM option) |  |  |  |  |

|                | Lane [15:8]     | Straight to CPU0 PCIe port 1                                    |  |  |  |  |

## **Table 9 PCH PCIe Uplink Port Assignment**

#### 2.1.5 Ethernet

Open Rack Server has one GbE LAN port for network access. The GbE port is implemented via an Intel i210-IT single-port GbE controller.

The i210-IT is located on the PCIe x1 port of the Intel PCH. It offers a fully-integrated GbE Media Access Control (MAC), Physical Layer (PHY) port and a SGMII/NC-SI port. The highest supported transmission rate is 1000Base-T.

There is a SPI serial EEPROM device attached with the i210-IT. The EEPROM capacity is 4Mb. After power up, the BIOS assigns I/O resources to initialize the i210-IT. Then the i210-IT loads the EEPROM content for LAN port configuration.

For system management purpose, the i210-IT provides both SMBus and NC-SI interface. SMBus and NC-SI are sideband interfaces for pass-through and configuration traffic between the BMC and the GbE. Server sledi mplements both interfaces for the BMC.

For pass-through traffic, the usable bandwidth can be up to 250Mb/s. For sideband interfaces, the usable bandwidth for either direction is up to 1Mb/s when using SMBus and 100Mb/s for the NC-SI interface.

The BMC works in shared-NIC mode with separated MAC.

The concept diagram is illustrated as below.

28/09/2018 23 / 87

Figure 8 Shared-NIC Concept Diagram

Shared-NIC mode means a common Ethernet connection is shared between the operating system and the BMC. The system management traffic multiplexes with the regular Ethernet traffic. Shared-NIC mode has fewer cabling requirement between the server and the network. This simplifies the hardware design.

Separated MAC means the BMC has a dedicated MAC address. All kinds of traffic (HTTP, NFS, IPMI) on Ethernet can be filtered by MAC address. The management traffic is extracted and sent to the BMC via NC-SI interface.

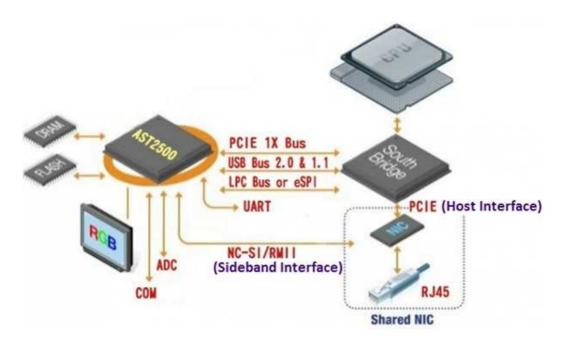

## 2.1.6 BMC

Open Rack Server uses the ASPEED® AST2500 BMC for system management such as board healthy monitoring, sensor monitoring, fan speed control, remote management.

The AST2500 is an ARM1176JZF-S core based MCU. It has a local SPI interface to support two SPI flashes. Where duplicated firmware image are stored for redundancy. Both I<sup>2</sup>C and NC-SI ports for Out-Of-Band access. The NC-SI port is from the Intel i210 GbE controller. The firmware remote upgrade is supported as well.

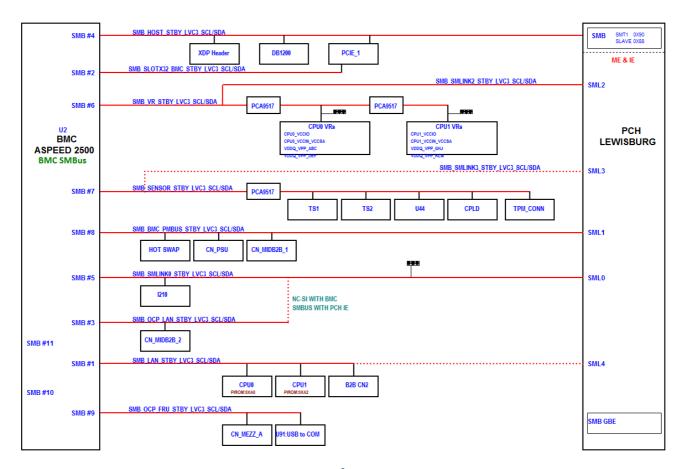

The BMC application block diagram is shown as the figure below.

28/09/2018 24 / 87

Figure 9 Server Sled BMC Application Block Diagram

#### AST2500 main features:

- Bus support: PCle v2.0, USB 2.0, LPC, SPI, eSPI, PECI, I<sup>2</sup>C, SMBus, UART

- Various analog/digital sensors for voltage and temperature monitoring

- Fan tachometer and speed control

- GPIO

- Programmable timer for alarm with interrupt generation

- Hash & Crypto Engine

- Support storage redirection

- Support KVM redirection

- JTAG

- Max power consumption (include DRAM) < 2.1W</li>

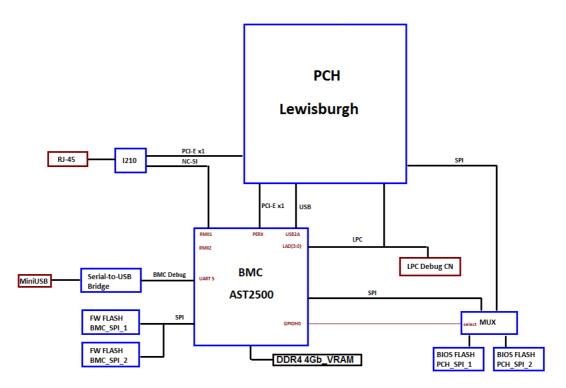

The BMC has several I<sup>2</sup>C compatible buses for different operation purposes.

The figure below shows the block diagram.

28/09/2018 25 / 87

Figure 10 BMC SMBus Block Diagram

The AST2500 implements hardware monitoring to check server board status and raise an alarm if malfunction. Hardware monitor shall support the following features:

- Voltage monitoring for 14 voltage planes

- Temperature sensors: the monitoring of CPUs and chipset utilizing built in on-die sensors + additional temperature sensor located on the coolest area of PCB

- Emergency power shut down in case THERMTRIP# asserted

- PROCHOT# for CPU thermal throttling

- MEMHOT# for memory thermal throttling

## Voltage monitoring

| Voltage Plane  | Signal Name |

|----------------|-------------|

| Vcore for CPU0 | PVCCIN_CPU0 |

| Vcore for CPU1 | PVCCIN_CPU1 |

28/09/2018 26 / 87

| 1.2V for DIMM ABC     | PVDDQ_ABC    |

|-----------------------|--------------|

| 1.2V for DIMM DEF     | PVDDQ_DEF    |

| 1.2V for DIMM GHJ     | PVDDQ_GHJ    |

| 1.2V for DIMM KLM     | PVDDQ_KLM    |

| 5V main power         | P5V          |

| 3.3V main power       | P3V3         |

| 1.0V standby for PCH  | PVNN_PCH_SB  |

| 1.05V standby for PCH | P1V05_PCH_SB |

| 1.8V standby for PCH  | P1V8_PCH_SB  |

| 1.0V for CPU0 I/O     | PVCCIO_CPU0  |

| 1.0V for CPU1 I/O     | PVCCIO_CPU 1 |

| Battery               | VBAT_HM      |

**Table 10 BMC Voltage Monitoring List**

## **Thermal Sensor**

| Device Name | Description                                                                                                                                | Address |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|

| TS1         | This sensor is located at the end far away from the fan tray. It's nearby the front panel and the mini USB connector.                      | 0x90    |

| TS2         | This sensor is located at the fan inlet side. It' nearby the midplane connector 2 to monitor the air temperature in front of the fan tray. | 0x94    |

**Table 11 BMC Thermal Sensor List**

**NOTE**: The LM73 includes three fixed I2C I/O address inside the device. The LM73 provides one ADDR pin with status float, ground, and Vdd to configure the I/O address. For the LM73 type "-0", the status float, ground, and Vdd means the I/O address is configured with 0x90h, 0x92h, and 0x94h. For the LM73 type "-1", the status float, ground, and Vdd means the I/O address is configured with 0x98h, 0x9Ah, and 0x9Ch. Server sled has two LM73-0 devices to configure a unique I2C I/O address.

## GPIO assignment for fan control

| Signal name | Description | GPIO |

|-------------|-------------|------|

|             |             |      |

28/09/2018 27 / 87

| BMC_FAN01_PWM | Fan 0 and fan 1 duty cycle control                                                                                 | GPION0            |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------------|

| BMC_FAN23_PWM | Fan 2 and fan 3 duty cycle control                                                                                 | GPION1            |

| BMC_FAN_TACH0 | Fan speed detection for fan 0                                                                                      | GPIOO0            |

| BMC_FAN_TACH1 | Fan speed detection for fan 1                                                                                      | GPIOO1            |

| BMC_FAN_TACH2 | Fan speed detection for fan 2                                                                                      | GPIOO2            |

| BMC_FAN_TACH3 | Fan speed detection for fan 3                                                                                      | GPIOO3            |

| FAN_WDT_OUT   | This is the BMC fail-safe function. In case BMC is dead, this pin asserts to make system fan run at largest speed. | GPIOP6_T<br>ACH14 |

**Table 12 BMC GPIO Assignment for Fan Speed Control**

## GPIO assignment for miscellaneous functions

| Signal name                  | Description                               | GPIO                          |  |  |

|------------------------------|-------------------------------------------|-------------------------------|--|--|

| FM_PWR_BTN_N                 | Power button from the front panel         | GPIOE2_NDSR3                  |  |  |

| FM_BMC_PWRBTN_<br>OUT_N      | Power button output to PCH                | GPIOZ2_VPOG4_N<br>ORA2_SIOPBO |  |  |

| RST_SYSTEM_BTN_<br>N         | Reset button from the front panel         | GPIOE0_NCTS3                  |  |  |

| RST_BMC_SYSRST<br>_BTN_OUT_N | Reset button output to PCH                | GPIOE1_NDCD3                  |  |  |

| FM_SLPS4_N                   | SLPS4_N status check                      | GPIOY0                        |  |  |

| FM_CPU0_SKTOCC<br>_LVT3_N    | CPU0 present                              | GPIOS2                        |  |  |

| FM_CPU1_SKTOCC<br>_LVT3_N    | CPU1 present                              | GPIOS3                        |  |  |

| CPLD_PWRGD_SYS<br>_PWROK     | System power good healthy detection       | GPIOZ1                        |  |  |

| CPLD_ALL_PGD                 | Power good status of all the power planes | GPIOC4                        |  |  |

| FM_BIOS_POST_CM<br>PLT_N     | BIOS POST complete                        | GPIOG3                        |  |  |

| EM DACKLID DIOS              | BIOS flash selection.                     |                               |  |  |

| FM_BACKUP_BIOS_<br>SEL N     | H: primary BIOS flash                     | GPIOQ4                        |  |  |

|                              | L: secondary BIOS flash                   |                               |  |  |

28/09/2018 28 / 87

| EW DOLL ODI DMC                | BIOS SPI path control H: SPI BIOS ROM from PCH (Default)                                                    |                               |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------|--|

| FM_PCH_SPI_BMC_<br>CTRL_N      | L: SPI BIOS ROM from BMC                                                                                    | GРІОН0                        |  |

| FM_I210_SPI_BMC_<br>CTRL_N     | LAN SPI flash control  H: SPI LAN image ROM connected to i210. (Default) L: SPI LAN image upgrade from BMC. | GPIOH4                        |  |

| IRQ_BMC_PCH_SMI<br>_LPC_N      | LPC SMI                                                                                                     | GPIOB5_LPCPD_LP<br>CSMI#      |  |

| IRQ_SML1_PMBUS_<br>ALERT_N     | Alert from the HotSwap controller                                                                           | GPIOAA1_VPOR3_<br>NORD1_SALT8 |  |

| FM_PMBUS_ALERT<br>_BUF_EN_N    | PMBUS alert output                                                                                          | GPIOAA2_VPOR4_<br>NORD2_SALT9 |  |

| FM_FAST_PROCHO<br>T_EN_N       | PROCHOT# event output                                                                                       | GPIOR3_SPI2CK                 |  |

| FM_CPU0_PROCHO<br>T_LVT3_N     | CPU0 processor hot event input                                                                              | GPIOP0                        |  |

| FM_MEM_THERM_E<br>VENT_LVT3_N  | Memory thermal event from the DIMMs                                                                         | GPIOB3                        |  |

| FM_PCH_BMC_THE<br>RMTRIP_N     | THERMTRIP# event input                                                                                      | GPIOG2_SGPS1I0                |  |

| SMB_SLOTX32_SBL<br>VC3_ALERT_N | Riser card alert input                                                                                      | GPIOAA0_VPOR2_<br>NORD0_SALT7 |  |

| IRQ_MEZZ_LAN_AL<br>ERT_N       | Mezzanine card alert input                                                                                  | GPIOE5_NRTS3                  |  |

| IRQ_FORCE_NM_TH<br>ROTTLE_N    | THROTTLE# event output                                                                                      | GPIOR2_SPI2CS0                |  |

| FM_CPU_ERR2_LVT<br>3_N         | ERROR_N[2] input. IIO or DMI3 found fatal errors.                                                           | GPIOG0_SGPS1CK                |  |

| FM_CPU_MSMI_CAT<br>ERR_LVT3_N  | CATERR_N and MSMI_N combined input. CPU or DIMM found errors.                                               | GPIOG1_SGPS1LD                |  |

| FM_BOARD_SKU_ID<br>0           | Board SKU ID 0                                                                                              | GPIOG4                        |  |

| FM_BOARD_SKU_ID<br>1           | Board SKU ID 1                                                                                              | GPIOG5                        |  |

| FM_BOARD_SKU_ID<br>2           | Board SKU ID 2                                                                                              | GPIOG6                        |  |

28/09/2018 29 / 87

| FM_BOARD_SKU_ID<br>3 | Board SKU ID 3            | GPIOG7                 |  |

|----------------------|---------------------------|------------------------|--|

| FM_BOARD_SKU_ID 4    | Board SKU ID 4            | GPIOGJ3                |  |

| PCB_REV0             | PCB REV0                  | GPIOJ0                 |  |

| PCB_REV1             | PCB REV1                  | GPIOJ1                 |  |

| PCB_REV2             | PCB REV2                  | GPIOJ2                 |  |

| PWR_LINK_B_LED       | Power LED, color: Blue    | GPIOO5                 |  |

| ALERT_R_LED          | Alert LED, color: Red     | GPIOO6                 |  |

| BMC_RDY_N            | BMC ready. Output to PCH  | GPIOP7                 |  |

| PU_BMC_GPIOS7        | VGA class code            | GPIOS7_VPOB9           |  |

| PD_BMC_GPIOZ7        | Strap for fast reset mode | GPIOZ7_VPOG9_N<br>ORA7 |  |

**Table 13 BMC GPIO Assignment for Miscellaneous Functions**

## Ethernet traffic filtering

The BMC works in shared-NIC mode with separated MAC. The BMC has a dedicated MAC address. All kinds of traffic (HTTP, NFS, IPMI) on Ethernet can be filtered by MAC address. The normal traffic passes through PCIe when payload operating. The management traffic is extracted and sent to the BMC via NC-SI interface no matter payload on and off.

## **Dual boot flash for redundancy**

The BMC has two SPI flashes for redundancy. There is a watchdog timer for boot time counting. When the main flash boots up successfully, the watchdog timer should be disabled before timeout. If the firmware running on the main flash doesn't disable the watchdog timer within 22 seconds, the watchdog bites and reset the BMC. After reset, the BMC boots with the 2<sup>nd</sup> flash.

## 2.1.7 CPLD

Server sled implements an Altera MAX 10 series CPLD device. The model number is 10M04DAU324. It's a 324-pin, 15mm x 15mm, UBGA packaged chip. There are 4K logic elements can be configured to fulfill applications. The advantage of CPLD is to make the hardware design flexible, reduce components to simplify design, and save cost.

28/09/2018 30 / 87

The major functions of the CPLD are:

- Power on/off sequencing control

- Reset control

- Logic control such as logic calculation, signal multiplex, delay, buffered, level shift

- Misc signals re-route for flexibility

- GPIO

- I/O port expansion

- Sensor event

- Device present, package ID

- Interrupt routing

- Error reporting

#### 2.1.8 TPM

Server sled implements an Infineon SLB9670VQ2.0 FW7.61 TPM to support secure key and file storage.

The SLB9670VQ2.0 FW7.61 is a TCG rev1.2/2.0 compliant TPM device. TCG means Trusted Computing Group. It's an industry group specialized in trusted computing.

The SLB9670VQ2.0 FW7.61 TPM connects with PCH via SPI interface. The features are summarized below.

- Compliant to TPM main specification, Family "2.0", Level 00, Revision 01.16

- Support SPI interface

- Meeting Intel TXT, Microsoft Windows and Google Chromebook certification criteria for successful platform qualification

- True Random Number Generator

- Full personalization with Endorsement Key (EK) and EK certificate

- 7206 Byte free NV memory

- Low standby power consumption. Typical 110uA

- Hardware hash accelerator for SHA-1 and SHA-256 algorithm

- Built-in support by Linux Kernel

28/09/2018 31 / 87

#### 2.2 Power Feed

Server motherboard is supplied by the 12V source from the datacenter rack. The nominal input voltage is 12.5V DC at light loading with a range of 11V ~ 13V.

At any loading, the server shall accept and operate normally with input voltage tolerance range between 10.8V ~ 13.2V.

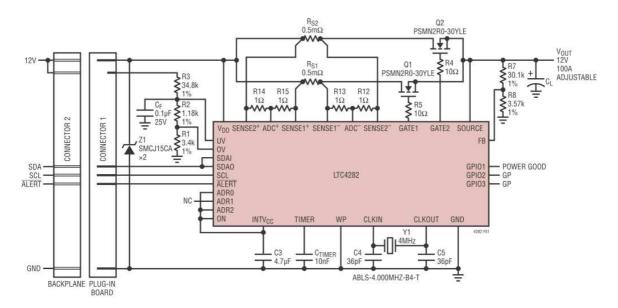

There is a hot swap controller(HSC) in series with the power feed path. Besides the hot swap, the HSC provides input voltage monitoring and protection. The figure below shows the block diagram of the circuitry.

Figure 11 Hot Swap Controller Block Diagram

This HSC circuit implements several functions including:

- 1. In-rush current control when power on

- 2. Monitors Current, Voltage, Power and Energy

- Current limiting protection for over current and short circuit conditions. Trip point: 48.8A ~ 41.4A

- 4. Under-voltage protection level: 10V ~ 10.1V with hysteresis

- 5. Send alerts when alarm thresholds exceeded

- 6. Fault protection for OVP and UVP events, the default scheme is auto-retry for every 50ms

- 7. Fault protection for OCP events, the default scheme is latch-off

- 8. All the trip point settings and the fault protection schemes can be reconfigured by the HSC I<sup>2</sup>C interface

28/09/2018 32 / 87

## 2.2.1 System Power Distribution

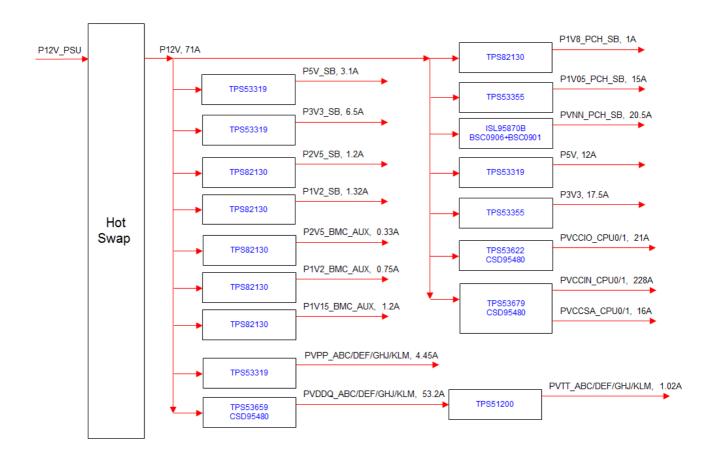

## **System Power Flow**

The figure below is a System Power Flow Map. It shows where the voltage rails are regulated from. The power budget statistics and the power solutions are listed in the map as well. The power rails are derived from 12V. The total maximum power for devices in server will be up to 800W theoretically.

Figure 12 System Power Flow Map

28/09/2018 33 / 87

# **System Power Budget Analysis**

The table below shows the power budget analysis of all the power rails.

28/09/2018 34 / 87

| Page | Output Net Name | Solution     | Input Net Name | Vout         | Iout     | Vin   | η   | Iin    | Remark |

|------|-----------------|--------------|----------------|--------------|----------|-------|-----|--------|--------|

|      |                 |              | СР             | J <b>VRD</b> |          |       |     |        |        |

|      | PVCCIN_CPU0     | TPS53679_1a  | P12V           | 1.80 V       | 228.00 A | 12 V  | 94% | 36.6 A |        |

|      | PVCCIN_CPU1     | TPS53679_2a  | P12V           | 1.80 V       | 228.00 A | 12 V  | 94% | 36.6 A |        |

|      | PVCCSA_CPU0     | TPS53679_1b  | P12V           | 0.85 V       | 16.00 A  | 12 V  | 92% | 1.2 A  |        |

|      | PVCCSA_CPU1     | TPS53679_2b  | P12V           | 0.85 V       | 16.00 A  | 12 V  | 92% | 1.2 A  |        |

|      | PVCCIO_CPU0     | TPS53622     | P12V           | 1.00 V       | 21.00 A  | 12 V  | 90% | 1.9 A  |        |

|      | PVCCIO_CPU1     | TPS53622     | P12V           | 1.00 V       | 21.00 A  | 12 V  | 90% | 1.9 A  |        |

|      |                 |              |                |              |          |       |     |        |        |

|      |                 |              | Swi            | tching       |          |       |     |        |        |

|      | P_VDDQ_ABC      | TPS53659     | P12V           | 1.215 V      | 45.22 A  | 12 V  | 91% | 5.1 A  |        |

|      | P_VDDQ_DEF      | TPS53659     | P12V           | 1.215 V      | 53.22 A  | 12 V  | 92% | 5.9 A  |        |

|      | P_VDDQ_GHJ      | TPS53659     | P12V           | 1.215 V      | 53.22 A  | 12 V  | 92% | 5.9 A  |        |

|      | P_VDDQ_KLM      | TPS53659     | P12V           | 1.215 V      | 53.22 A  | 12 V  | 92% | 5.9 A  |        |

|      | P_VPP_ABC       | TPS53319     | P12V           | 2.58 V       | 4.45 A   | 12 V  | 94% | 1.0 A  |        |

|      | P_VPP_DEF       | TPS53319     | P12V           | 2.58 V       | 4.45 A   | 12 V  | 94% | 1.0 A  |        |

|      | P_VPP_GHJ       | TPS53319     | P12V           | 2.58 V       | 4.45 A   | 12 V  | 94% | 1.0 A  |        |

|      | P_VPP_KLM       | TPS53319     | P12V           | 2.58 V       | 4.45 A   | 12 V  | 94% | 1.0 A  |        |

|      | PVNN_PCH_SB     | ISL95870BIRZ | P12V           | 1.00 V       | 20.50 A  | 12 V  | 88% | 1.9 A  |        |

|      | P1V05_PCH_SB    | TPS53355A    | P12V           | 1.05 V       | 15.00 A  | 12 V  | 86% | 1.5 A  |        |

|      | P5V_SB          | TPS53319     | P12V           | 5.00 V       | 3.10 A   | 12 V  | 95% | 1.4 A  |        |

|      | P3V3_SB         | TPS53319     | P12V           | 3.30 V       | 6.44 A   | 12 V  | 94% | 1.9 A  |        |

|      | P2V5_SB         | TPS82130     | P12V           | 2.50 V       | 1.19 A   | 12 V  | 87% | 0.3 A  |        |

|      | P1V8_PCH_SB     | TPS82130     | P12V           | 1.80 V       | 1.00 A   | 12 V  | 83% | 0.2 A  |        |

|      | P1V2_SB         | TPS82130     | P12V           | 1.20 V       | 1.32 A   | 12 V  | 79% | 0.2 A  |        |

|      | P1V2_BMC_AUX    | TPS82130     | P12V           | 1.20 V       | 0.75 A   | 12 V  | 79% | 0.1 A  |        |

|      | P1V15_BMC_AUX   | TPS82130     | P12V           | 1.15 V       | 1.20 A   | 12 V  | 79% | 0.1 A  |        |

|      | P5V             | TPS53319     | P12V           | 5.00 V       | 12.00 A  | 12 V  | 94% | 5.3 A  |        |

|      | P3V3            | TPS53355     | P12V           | 3.30 V       | 17.50 A  | 12 V  | 94% | 5.1 A  |        |

|      |                 |              |                |              |          |       |     |        |        |

|      | _               |              | Hot            | -Swap        |          |       |     |        |        |

|      | P12V            | LTC4282      | P12V_PSU       | 12.000 V     | 70.933 A | 12 V  |     |        |        |

|      |                 |              |                |              |          |       |     |        |        |

|      | _               |              | LDO            |              |          |       | T   | PD     | Remark |

|      | PVTT_ABC        | TPS51200DRCT | P_VDDQ_ABC     | 0.608 V      | 1.02 A   | 1.2 V | 50% | 0.62 W |        |

|      | PVTT_DEF        | TPS51200DRCT | P_VDDQ_DEF     | 0.608 V      | 1.02 A   | 1.2 V | 50% | 0.62 W |        |

|      | PVTT_GHJ        | TPS51200DRCT | P_VDDQ_GHJ     | 0.608 V      | 1.02 A   | 1.2 V | 50% | 0.62 W |        |

|      | PVTT_KLM        | TPS51200DRCT | P_VDDQ_KLM     | 0.608 V      | 1.02 A   | 1.2 V | 50% | 0.62 W |        |

|      | P2V5_BMC_AUX    | TPS74801     | P3V3_SB        | 2.50 V       | 0.33 A   | 3.3 V | 76% | 0.26 W |        |

|      |                 |              |                |              |          |       |     |        |        |

**Table 14 System Power Budget**

28/09/2018 35 / 87

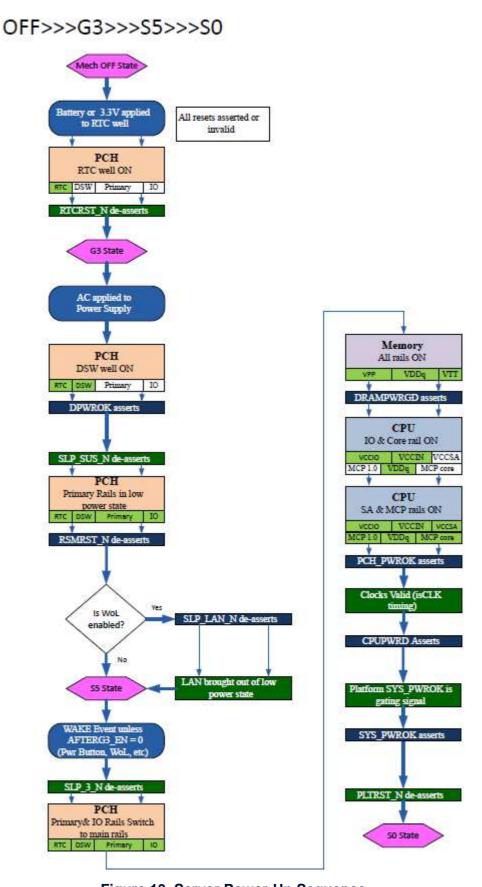

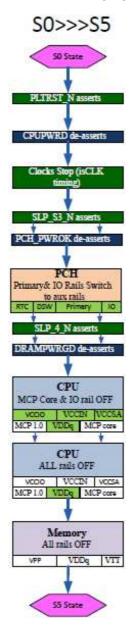

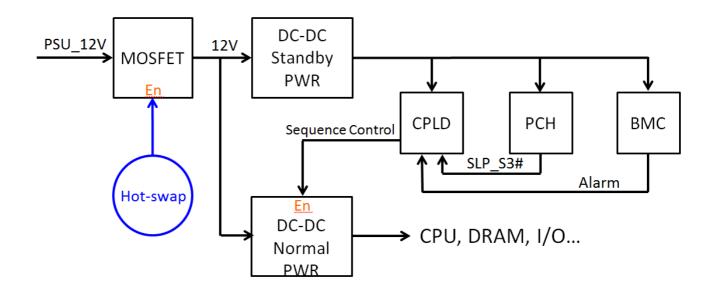

## 2.2.2 Power Sequence

It is guaranteed that the IC devices will not be damaged during supply voltage ramp up by strictly following IC vendors' power sequence recommendations.

The 12V input is gated by the BMC. In the start-up of server, the BMC is initialized. After that, the BMC enables the DC/DC converter.

The server has a CPLD to control the power sequence. The timing is implemented according to Intel's Cresecnt CRB Revision 1.04 for CPU and chipset portion. Resistor options are also reserved as Intel's recommendation in the reference schematics. In case the CPLD design error causes boot up failure, the resistor options can bypass the CPLD control to make the board boot up successfully. But this only happens in develop phase, suppose the CPLD should design well once production.

## **Power-Up Sequence**

After the 12V in, the power-up sequence is described in the following figure.

28/09/2018 36 / 87

Figure 13 Server Power-Up Sequence

28/09/2018 37 / 87

# **Power-Down Sequence**

The power-Down sequence is described in the following figure.

Figure 14 Server Power-down Sequence

# 2.2.3 Voltage Monitoring and Alarm

All the internal DC voltages of server are monitored by the BMC.

28/09/2018 38 / 87

From the ramp-up of 12V, 5V and 3.3V to the all sequential system powers, the power sequence mechanism actually receives all their power-good signals and ANDs them together aggregately into the final power-good signal of SYS\_PWRGD. Any voltage is out of specification will cause a hardware based reset.

All the local system power's outputs are monitored by their own voltage regulators respectively. However, some of them do not have native over voltage protection ability. For these cases, the server has external comparators for the over voltage protection.

When under voltage, over voltage or over current event happens, their controllers drive their own power good signals low. Power good signals are effectively aggregated to the last one, SYS\_PWRGD. The SYS\_PWRGD low will make the PCH to reset the whole system (excluding BMC).

Below table lists the set points of under voltage, over voltage and over current protections.

|            |              |               | Voltage | UVP             | OVP       | Current  | OCP     |

|------------|--------------|---------------|---------|-----------------|-----------|----------|---------|

| Power Well | VR P/N       | Power Name    | Vtyp    | 0.0             | (1.0)     |          | (0)     |

| VVCII      |              |               | (V)     | (V)             | (V)       | lmax(A)  | (A)     |

|            | ISL95870BIRZ | PVNN_PCH_SB   | 1.00 V  | VOUT*84%        | VOUT*116% | 20.50 A  | 26.7 A  |

|            | TPS53355A    | P1V05_PCH_SB  | 1.05 V  | 0.74 V          | 1.26 V    | 15.00 A  | 19.5 A  |

|            | TPS53319     | P5V_SB        | 5.00 V  | 3.50 V          | 6.00 V    | 3.10 A   | 4.0 A   |

|            | TPS53319     | P3V3_SB       | 3.30 V  | 2.31 V          | 3.96 V    | 6.44 A   | 8.4 A   |

| STBY       | TPS82130     | P2V5_SB       | 2.50 V  | N/A             | N/A       | 1.19 A   | 3.6 A   |

|            | TPS82130     | P1V8_PCH_SB   | 1.80 V  | N/A             | N/A       | 1.00 A   | 3.6 A   |

|            | TPS82130     | P1V2_SB       | 1.20 V  | N/A             | N/A       | 1.32 A   | 3.6 A   |

|            | TPS82130     | P1V2_BMC_AUX  | 1.20 V  | N/A             | N/A       | 0.75 A   | 3.6 A   |

|            | TPS82130     | P1V15_BMC_AUX | 1.15 V  | N/A             | N/A       | 1.20 A   | 3.6 A   |

|            | TPS53679     | PVCCIN_CPU0   | 1.80 V  | VID-VDROOP-0.37 | VID+0.33  | 228.00 A | 273.6 A |

|            | TPS53679     | PVCCIN_CPU1   | 1.80 V  | VID-VDROOP-0.37 | VID+0.33  | 228.00 A | 273.6 A |

|            | TPS53679     | PVCCSA_CPU0   | 0.85 V  | VID-VDROOP-0.37 | VID+0.33  | 16.00 A  | 20.8 A  |

| Main       | TPS53679     | PVCCSA_CPU1   | 0.85 V  | VID-VDROOP-0.37 | VID+0.33  | 16.00 A  | 20.8 A  |

| IVIAIII    | TPS53622     | PVCCIO_CPU0   | 1.00 V  | VID-VDROOP-0.37 | VID+0.33  | 21.00 A  | 27.3 A  |

|            | TPS53622     | PVCCIO_CPU1   | 1.00 V  | VID-VDROOP-0.37 | VID+0.33  | 21.00 A  | 27.3 A  |

|            | TPS53659     | P_VDDQ_ABC    | 1.215 V | VID-VDROOP-0.37 | VID+0.33  | 45.22 A  | 58.8 A  |

|            | TPS53659     | P_VDDQ_DEF    | 1.215 V | VID-VDROOP-0.37 | VID+0.33  | 53.22 A  | 69.2 A  |

28/09/2018 39 / 87

| TPS53659     | P_VDDQ_GHJ   | 1.215 V | VID-VDROOP-0.37 | VID+0.33 | 53.22 A | 69.2 A |

|--------------|--------------|---------|-----------------|----------|---------|--------|

| TPS53659     | P_VDDQ_KLM   | 1.215 V | VID-VDROOP-0.37 | VID+0.33 | 53.22 A | 69.2 A |

| TPS53319     | P_VPP_ABC    | 2.58 V  | 1.80 V          | 3.09 V   | 4.45 A  | 5.8 A  |

| TPS53319     | P_VPP_DEF    | 2.58 V  | 1.80 V          | 3.09 V   | 4.45 A  | 5.8 A  |

| TPS53319     | P_VPP_GHJ    | 2.58 V  | 1.80 V          | 3.09 V   | 4.45 A  | 5.8 A  |

| TPS53319     | P_VPP_KLM    | 2.58 V  | 1.80 V          | 3.09 V   | 4.45 A  | 5.8 A  |

| TPS53319     | P5V          | 5.00 V  | 3.50 V          | 6.00 V   | 12.00 A | 15.6 A |

| TPS53355     | P3V3         | 3.30 V  | 2.31 V          | 3.96 V   | 17.50 A | 22.8 A |

| TPS51200DRCT | PVTT_ABC     | 0.608 V | N/A             | N/A      | 1.02 A  | 3.00 A |

| TPS51200DRCT | PVTT_DEF     | 0.608 V | N/A             | N/A      | 1.02 A  | 3.00 A |

| TPS51200DRCT | PVTT_GHJ     | 0.608 V | N/A             | N/A      | 1.02 A  | 3.00 A |

| TPS51200DRCT | PVTT_KLM     | 0.608 V | N/A             | N/A      | 1.02 A  | 3.00 A |

| TPS74801     | P2V5_BMC_AUX | 2.50 V  | N/A             | N/A      | 0.33 A  | 2.00 A |

Table 15 Over Voltage and Under Voltage Threshold of Local DC/DC SMPS

#### 2.3 Printed Circuit Board

The PCB material for server motherboard is the TU-862HF.

TU-862HF is a Hi-Tg halogen free material and made of epoxy resin and E-glass fabric. TU-862HF achieves flammability class of UL94V-0 by incorporating nitrogen compounds in the materials. This series of green materials are designed to eliminate the use of halogenated resins due to the potential hazardous effects from the environmental concerns. These products are suitable for boards that need to survive severe thermal cycles, or to experience excessive assembly work. TU-862 HF laminates also exhibit superior chemical resistance, thermal stability for lead free soldering assembly.

Industry approvals for the TU-862HF:

IPC-4101 Type Designation : /127, /128, /130

UL Designation - ANSI Grade : FR-4.1

UL File Number: E189572

Flammability Rating: 94V-0

Maximum Operating Temperature: 130°C

In order to be compatible with the ORv2 sled mechanical design, the nominal PCB thickness should be 89.44mil with tolerance ±8 mil.

28/09/2018 40 / 87

The following figure shows the PCB stack-up and the impedance control of the server motherboard.

| stack-up  | •                  |                   |                      |                    |                  |          |          |                  |                         |              |                  |              |                                            |          |                                            |          |                                             |          |

|-----------|--------------------|-------------------|----------------------|--------------------|------------------|----------|----------|------------------|-------------------------|--------------|------------------|--------------|--------------------------------------------|----------|--------------------------------------------|----------|---------------------------------------------|----------|

| _         |                    |                   |                      |                    |                  |          |          |                  |                         |              |                  |              |                                            |          |                                            |          |                                             |          |

|           | NDC \$18-OCP \$tac | cxup              |                      |                    |                  |          |          |                  |                         |              |                  |              |                                            |          |                                            |          |                                             |          |

| macerial. | MID-LESS SUCCESS   | suggestion        |                      |                    |                  |          |          |                  | DDR 2 SPC DQ/DQS/N      | tice I/O. SE | DDD 4 EDC DO/DOS | /Micc I/O    | 1) PCIe, UPI, DMI                          |          | SFI 10G-KR (option :                       | 1        | SFI 10G-KR (option 2                        | 1        |

| Layer     |                    | suggestion        | Dielectric thickness | DK @4GHz           | DF @4GHz         | DK @8GHz | DF @8GHz | Estimateted      | clocks                  | nisci/O, sc  | SE clocks        | y wisc i/ O, | 2)Diff CLKs<br>3)USB2/3, SATA3             |          | 311 IOG-KK (Option)                        | -)       | 311 Iod-kk (option)                         | -1       |

| Name      | Ві                 | uild - up         | (unit mil)           | DK @4GHZ           | DF @4dHz         | DK @BGHZ | Dr @adnz | residual copper  | 40 +/-4.0 oh            | m            | 50 +/-5.0 0      | hm           | 85 +/- 8.5 0                               | hm       | 93 +/- 9.3 0                               | hm       | 100 +/- 10                                  | .0 ohm   |

|           |                    |                   |                      |                    |                  |          |          |                  | TraceWidth(mil)         |              | TraceWidth(mil)  |              | TraceWidth(mil)                            |          | TraceWidth(mil)                            |          | TraceWidth(mil)                             |          |

|           |                    | sm                | 0.7                  | 4                  | 0.022            | 4        | 0.022    |                  |                         |              |                  |              |                                            |          |                                            |          |                                             |          |

| L1TOP     | 0.5oz+plating      |                   | 1.6                  |                    |                  |          |          |                  | 8.1                     | 40+/-4       | 5.1              | 50+/-5       | 5/4.5                                      | 85+/-8.5 | 4.5/6                                      | 93+/-9.3 | 4/7                                         | 100+/-10 |

|           | PP                 | 1080-67%          | 3.20                 | 3.4                | 0.0171           | 3.4      | 0.0181   |                  | 40.8                    | 146.21       | 51.4             | 145.58       | 84.8<br>4G:0.581dB/inch<br>8G:1.103dB/inch | 142.99   | 93.9<br>4G:0.581dB/inch<br>8G:1.103dB/inch | 142.77   | 101.1<br>4G:0.581dB/inch<br>8G:1.103dB/inch | 142.77   |

| LZGND     | 10z                |                   | 1.2                  |                    |                  |          |          |                  |                         |              |                  |              | SG.1.1030by mon                            |          | 04.1.1030b/ mcn                            |          | 56.1.1030by men                             |          |

|           | Core               | 1080*1            | 3.00                 | 3.4                | 0.0166           | 3.4      | 0.0176   |                  |                         |              |                  |              |                                            |          |                                            |          |                                             |          |

| L3SIG     | 1oz                |                   | 1.2                  | ·                  |                  |          |          |                  | 6.5                     | 40+/-4       | 4                | 50+/-5       | 4.5/5.5                                    | 85+/-8.5 | 4.1/8                                      | 93+/-9.3 | 3.5/9                                       | 100+/-10 |

|           | PP                 | 2116-55%*2        | 9.10                 | 4.2                | 0.0151           | 4.1      | 0.0161   |                  | 40.1                    | 156.23       | 50.8             | 156.23       | 85.6<br>4G:0.579dB/inch<br>8G:1.048dB/inch | 156.23   | 94.1<br>4G:0.579dB/inch<br>8G:1.048dB/inch | 156.23   | 101.8<br>4G:0.579dB/inch<br>8G:1.048dB/inch | 156.23   |

| L4SIG     | 10z                |                   | 1.2                  |                    |                  |          |          |                  | 6.5                     | 40+/-4       | 4                | 50+/-5       | 4,5/5,5                                    | 85+/-8.5 | 4.1/8                                      | 93+/-9.3 | 3,5/9                                       | 100+/-10 |

|           | 202                |                   |                      |                    |                  |          |          |                  |                         | 401/ 4       |                  | 301/3        | 85.6                                       | 0317 0.5 | 94.1                                       | 2217 2.2 | 101.8                                       |          |

|           | Core               | 1080*1            | 3.00                 | 3.4                | 0.0166           | 3.4      | 0.0176   |                  | 40.1                    | 156.23       | 50.8             | 156.23       | 4G:0.579dB/inch<br>8G:1.048dB/inch         | 156.23   | 4G:0.579dB/inch<br>8G:1.048dB/inch         | 156.23   | 4G:0.579dB/inch<br>8G:1.048dB/inch          | 156.23   |

| L5GND     | 1oz                |                   | 1.2                  |                    |                  |          |          |                  |                         |              |                  |              |                                            |          |                                            |          |                                             |          |