OCP Engineering Workshop 25 September 2017 Dallas, TX

OCP Engineering Workshop – 25 September 2017 – Dallas, TX OCP NIC 3.0 Dell EMC Update Jon Lewis **Distinguished Engineer**

# Agenda

- Form Factor Update

- Pinout:

- Proposed changes to some pins/features

- Pinout proposal for Connector A and B

- Closing thoughts

### Form Factor

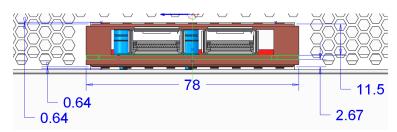

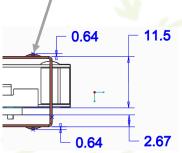

- Enumeration 14: 76 mm x 115 mm

- Top-side keepout: 11.0 mm

- Bottom-side keepout: 2.25 mm < x < 2.67 mm</li>

- Really need the NIC vendors to finalize this number.

- Motherboard Thickness: Agree with 0.062", 0.076" and 0.093" +/- 10% tolerances.

- Allows a wide range of layer counts and materials to be supported.

- Connector A = SFF-TA-1002 style 168 pin straddle mount connector.

- Connector B → Proposing 140 pin to allow a full x16.

- RJ-45 connectors should be mid-plane mounted. (3D models available)

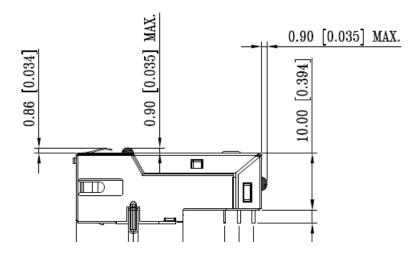

- 1x1 max top side height is 8.8 mm

- 1x4 max top side height is 10.0 mm

## Faceplate Spec Definition

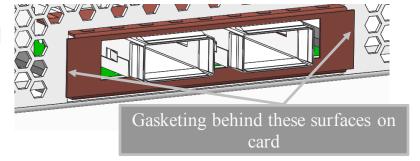

- Dell prefers design similar to the design shown:

- Enables EMI solution on card.

- Enables convenient space for latching.

- Minimizes vertical stack.

- Design intent and spec details:

- Top/Bottom fold over and are inserted into the chassis.

- Left/Right side EMI seal flush against rear wall.

- EMI fingers need to compress to be flush with top/bottom flanges.

- Proposal gives flexibility for different connectors.

- Open Items, in order:

- Do we need to protect the entire underside of card for installation?

- Retention mechanism selection and definition (internal/external/both?)

- Options for latching could include 1/4 turn retention.

- Should EMI fingers be on card or designed into chassis?

- Do we need to specify LED locations, definitions, ...?

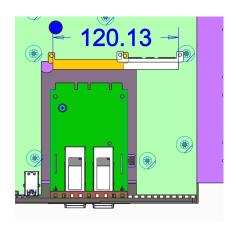

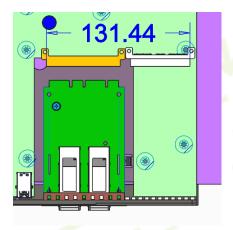

### Wider Card Consideration

- For the wider board Dell EMC would like to see the board grow to the right instead of the left.

- Prefer a x16 on the additional section

- Grow width to support additional 140 pin

- Top picture: Single connector instead of 2 connectors. Not sure if this is possible but would represent the minimum width for a wider card = ~127mm.

- Bottom picture: Connector B = 140 pins from the current concept models for the connector suppliers. The would make the card ~138mm.

## **Proposed Pinout Description**

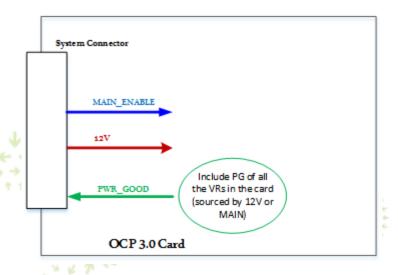

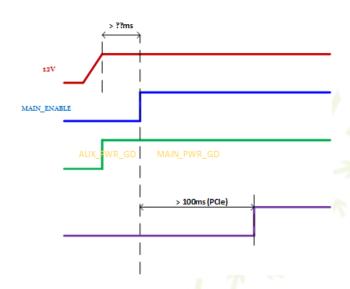

#### Power

- Repurpose the 12VAUX pins

- = 6 12V pins ~= 79W which should be sufficient (assume 1.1A per pin)

- MAIN\_EN: Signal from System to NIC indicating main power available.

- PWR GOOD: Signal from NIC to System indicating VRs are operating nominally.

- Indudes all NIC rails.

### Pinout - continued

- Deprecate CLK\_REQ

- Systems Management:

- One SMBus

- Includes FRU and temp sensor

- One NC-SIRBT bus (including arbitration pins)

- Add at least one "addressing" pin to enable dual OCP NIC 3.0 on the same management bus: SLOT\_ID

- I2C address changed

- NC-SI package ID changed (This assumes that the maximum number of OCP NIC 3.0 cards on a bus is 2. Additional addressing pins would be necessary if that increased.)

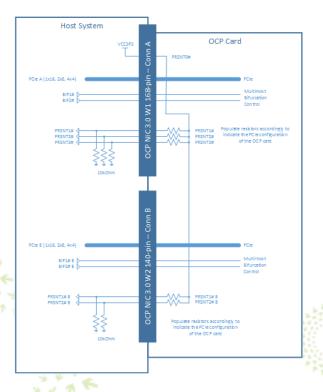

- Multi-Host: For Gen4/5 PCIe x4 ports seem to be an optimal choice

- 4 x {PERST#, WAKE#, REFCLK}

- REFCLK likely still required prior to Gen 5 PCle!

- Connector B: (140 pin to include x16)

- 12V pins 5 additional pins to increase power to ~145W (nominal assuming 1.1A per pin)

- Multi-host support (4 sets of PERST#, WAKE#, REFCLK)

## Pinout - continued

- Presence/Bifurcation

- Dual-purpose the existing 3 presence pins and add 2 pins (BIFn#).

- Allows for bidirectional bifurcation

#### Multi-host Bifurcation (from Host to OCP card)

| W1 Conn A |       | W2 Conn B |        | Host Root Port Configuration |       |

|-----------|-------|-----------|--------|------------------------------|-------|

| BIF1#     | BIF2# | BIF1#B    | BIF2#B | Bus A                        | Bus B |

| 0         | 0     | 0         |        | x16                          | x16   |

| 1         | 0     | 0         |        | 2 x8                         | 2 x8  |

| 0         | 1     | 0         |        | 4 x4                         | 4 x4  |

| 1         | 1     | 0         |        | x16                          | 2 x8  |

| 0         | 0     | 1         |        | x16                          | 4 x4  |

| 1         | 0     | 1         |        | 2 x8                         | x16   |

| 0         | 1     | 1         |        | 2 x8                         | 4 x4  |

| 1         | 1     | 1         |        | 4 x4                         | x16   |

|           |       |           |        | 4 x4                         | 2 x8  |

#### Root Port Bifurcation (from OCP card to Host)

| W1 Conn A |         |         | W2 Conn B |          | Conn A End    | Conn B End    |  |

|-----------|---------|---------|-----------|----------|---------------|---------------|--|

| PRSNT3#   | PRSNT2# | PRSNT1# | PRSNT2# B | PRSNT1#B | Device Config | Device Config |  |

| RFU       | 0       | 0       | 0         | 0        | Not present   | Not present   |  |

| RFU       | 0       | 1       | 0         | 0        | x16           | Not present   |  |

| RFU       | 1       | 0       | 0         | 0        | 2 x8          | Not present   |  |

| RFU       | 1       | 1       | 0         | 0        | RFU           | Not present   |  |

| RFU       | 0       | 1       | 0         | 1        | x16           | x16           |  |

| RFU       | 1       | 0       | 0         | 1        | 2 x8          | x16           |  |

| RFU       | 1       | 1       | 0         | 1        | RFU           | x16           |  |

| RFU       | 0       | 1       | 1         | 0        | x16           | 2 x8          |  |

| RFU       | 1       | 0       | 1         | 0        | 2 x8          | 2 x8          |  |

| RFU       | 1       | 1       | 1         | 0        | RFU           | 2 x8          |  |

| RFU       | 0       | 1       | 1         | 1        | x16           | RFU           |  |

| RFU       | 1       | 0       | 1         | 1        | 2 x8          | RFU           |  |

| RFU       | 1       | 1       | 1         | 1        | x32           |               |  |

Proposed pinout GND

PER<sub>b</sub>7

GND

PRSNT24

Key

GND H OCP x16 168 pin

## Closing Thoughts

- Given the current trajectory it would be nice to get together more frequently in targeted groups for discussions to close open items:

- Mechanical: Faceplate, latching mechanism, ...

- Pinout: definition of pins, new features, ...

### Contact information:

Jon Lewis | Distinguished Engineer

Dell EMC | Infrastructure Solutions Group

Email: jon.lewis@dell.com | IM/Skype: jon.lewis@dell.com

Office: (512)723-0767 | Mobile: (214) 505-5924

One Dell Way, MS RP5-31; Round Rock, TX 78682