# Big Basin-JBOG Specifications Rev 1.0

#### **Author:**

Kevin LEE, Technical Program Manager, Facebook Jia NING, Hardware Engineer, Facebook K.Y. THOON, Hardware Engineer, Facebook Whitney Zhao, Hardware Engineer, Facebook

# 1 Revision History

| Date | Name       | Description                                                      |

|------|------------|------------------------------------------------------------------|

| 0.01 | 5/11/2016  | Initial release                                                  |

| 0.02 | 7/31/2016  | Update Project name to Big Basin                                 |

| 0.03 | 11/21/2016 | Update for review                                                |

| 0.04 | 12/21/2016 | Minor corrections                                                |

| 0.05 | 01/19/2017 | Change factory default power policy to always-on                 |

| 0.06 | 02/17/2017 | Minor edits and corrections for table description in Section 7.3 |

|      |            | Corrected part numbers in Table 5-2                              |

| 1.0  | 12/31/2017 | Corrected typos in section 8                                     |

|      | -          | Update Volta support related information through the spec        |

|      | 1/102017   | Section 8.3.2 correct the fan size to 92x92x76                   |

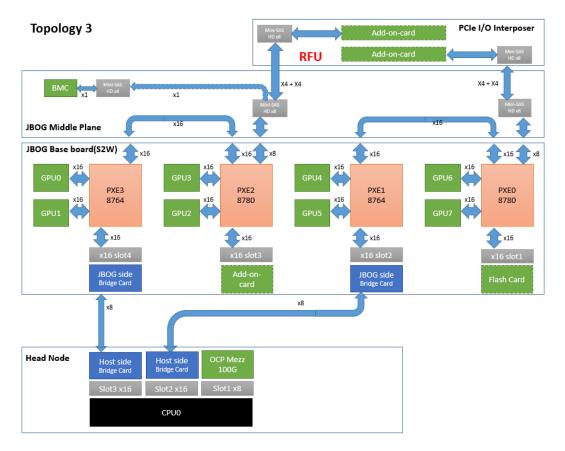

|      |            | Section 4.2 add topology 3                                       |

|      |            | Section 4.3 add Nvlink topology for Volta GPU                    |

|      |            | Table 4-1 add 2xStandard PCIe slots for baseboard                |

|      |            | Section 14-8 update IPC6012C to 6012D                            |

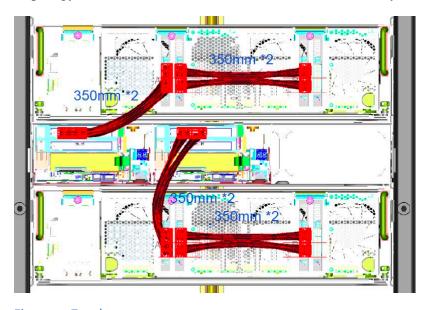

|      |            | Section 5.1.2 add topology 3 picture with cable                  |

|      |            |                                                                  |

|      |            |                                                                  |

#### Open Compute Project • Big Basin-JBOG Specifications

#### © 2016 Facebook.

As of July 20, 2017, the following persons or entities have made this Specification available under the Open Compute Project Hardware License (Permissive) Version 1.0 (OCPHL-P), which is available at <a href="http://www.opencompute.org/.../spec-submission-process/">http://www.opencompute.org/.../spec-submission-process/</a>.

#### Facebook, Inc.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The Specification implementer and user assume the entire risk as to implementing or otherwise using the Specification. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE."

# 2 Scope

This document describes technical specifications for Facebook's Big Basin-JBOG for use in Open Rack  $V2^1$ .

# 3 Contents

| 1 | Revisio | n History                             | 2  |  |  |  |  |  |  |

|---|---------|---------------------------------------|----|--|--|--|--|--|--|

| 2 | Scope   |                                       |    |  |  |  |  |  |  |

| 3 | Conten  | ents                                  |    |  |  |  |  |  |  |

| 4 | Overvie | ew                                    | 7  |  |  |  |  |  |  |

|   | 4.1     | Introduction                          | 7  |  |  |  |  |  |  |

|   | 4.2     | PCIe Block Diagram                    | 7  |  |  |  |  |  |  |

|   | 4.3     | NVLINK topology                       | 9  |  |  |  |  |  |  |

|   | 4.4     | GPU Baseboard Design                  | 10 |  |  |  |  |  |  |

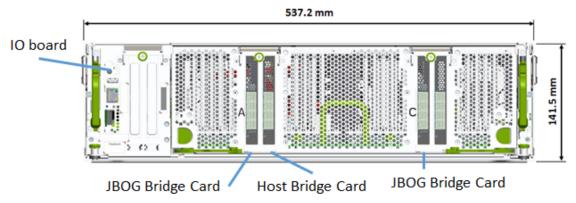

| 5 | JBOG Ir | nterface to Host                      | 11 |  |  |  |  |  |  |

|   | 5.1     | PCIe Cable Interface                  | 11 |  |  |  |  |  |  |

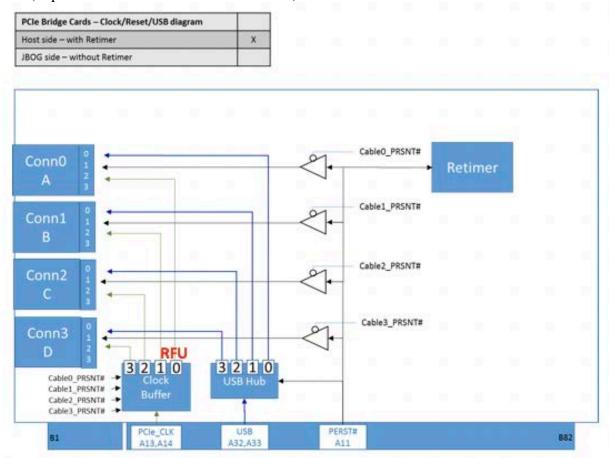

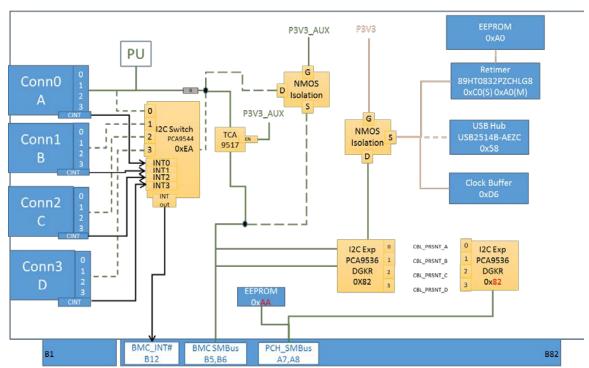

|   | 5.2     | PCIe Bridge Cards                     | 14 |  |  |  |  |  |  |

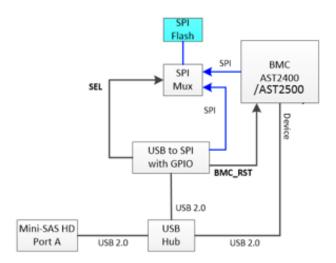

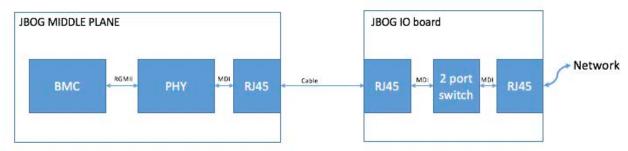

|   | 5.3     | Host to JBOG BMC Interface            | 23 |  |  |  |  |  |  |

| 6 | User LE | D and Buttons                         | 24 |  |  |  |  |  |  |

| 7 | BMC or  | 1 JBOG                                | 26 |  |  |  |  |  |  |

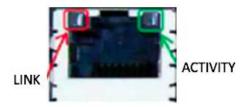

|   | 7.1     | Management Network Interface          | 26 |  |  |  |  |  |  |

|   | 7.2     | FRU                                   | 26 |  |  |  |  |  |  |

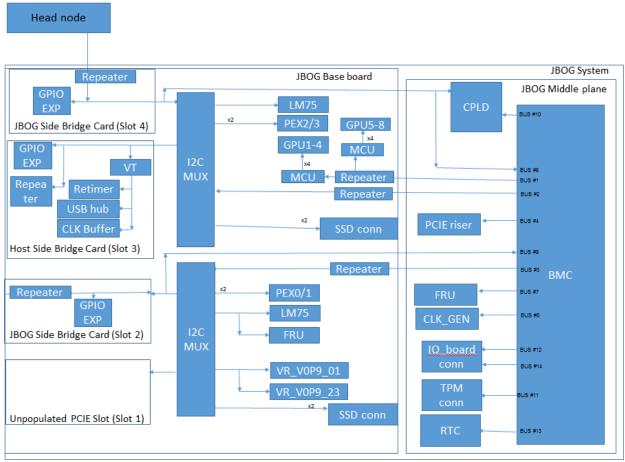

|   | 7.3     | I2C/SMB/IPMB Connection               | 27 |  |  |  |  |  |  |

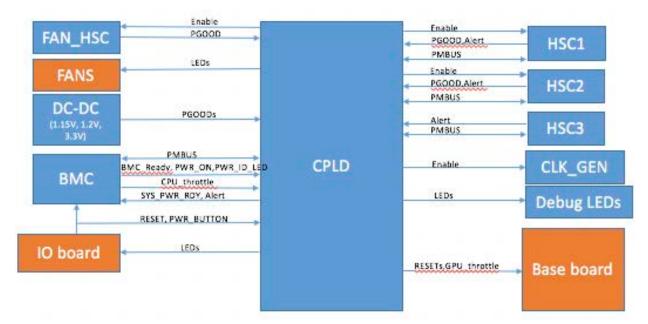

|   | 7.4     | CPLD                                  | 29 |  |  |  |  |  |  |

|   | 7.5     | Debug support                         | 30 |  |  |  |  |  |  |

|   | 7.6     | Local Serial Console                  | 31 |  |  |  |  |  |  |

|   | 7.7     | Remote Power Control and Power Policy | 32 |  |  |  |  |  |  |

|   | 7.8     | Power/Thermal Monitoring and Limits   | 32 |  |  |  |  |  |  |

|   | 7.9     | Sensors Used                          | 32 |  |  |  |  |  |  |

|   | 7.10    | System Event Log (SEL)                | 36 |  |  |  |  |  |  |

|   | 7.11    | Fan Speed Control (FSC) on JBOG       | 37 |  |  |  |  |  |  |

|   | 7.12    | OEM Commands                          | 39 |  |  |  |  |  |  |

|   |         |                                       |    |  |  |  |  |  |  |

<sup>1</sup> http://files.opencompute.org/oc/public.php?service=files&t=348f3df2cc4ce573397fcc4424f68ca6&download

|    | 7.13     | BMC Firmware Update                       | . 39 |

|----|----------|-------------------------------------------|------|

|    | 7.14     | CPLD Firmware Update                      | . 40 |

|    | 7.15     | BMC Average Power Reporting               | . 40 |

| 8  | Therma   | al Design Requirements                    | . 41 |

|    | 8.1      | Data Center Environmental Conditions      | . 41 |

|    | 8.2      | Operational Condition                     | . 42 |

|    | 8.3      | Thermal Kit Requirements                  | . 42 |

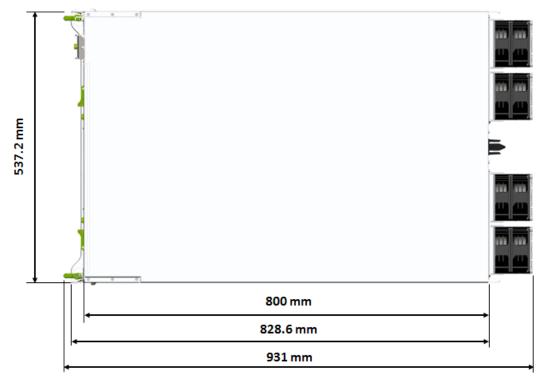

| 9  | Mechai   | nical                                     | . 44 |

|    | 9.1      | JBOG Mechanical                           | . 44 |

|    | 9.2      | PCB Stackup Information                   | . 51 |

| 10 | Power    | Delivery                                  | . 53 |

|    | 10.1     | Input Voltage                             | . 53 |

|    | 10.2     | Hot Swap Controller (HSC) Circuit on 12V  | . 53 |

|    | 10.3     | VRM Design Guideline                      | . 54 |

|    | 10.4     | System VRM Efficiency                     | . 54 |

|    | 10.5     | System Power On                           | . 54 |

| 11 | Environ  | nmental and Regulations                   | . 56 |

|    | 11.1     | Environmental Requirements                | . 56 |

|    | 11.2     | Vibration & Shock                         | . 57 |

|    | 11.3     | Regulations                               | . 57 |

| 12 | Labels   | and Markings                              | . 58 |

| 13 | Prescril | bed Materials                             | . 59 |

|    | 13.1     | Disallowed Components                     | . 59 |

|    | 13.2     | Capacitors & Inductors                    | . 59 |

|    | 13.3     | Component De-rating                       | . 59 |

| 14 | Reliabil | ity and Quality                           | . 60 |

|    | 14.1     | Specification Compliance                  | . 60 |

|    | 14.2     | Change Orders                             | . 60 |

|    | 14.3     | Failure Analysis                          | . 60 |

|    | 14.4     | Warranty                                  | . 60 |

|    | 14.5     | MTBF Requirements                         | . 60 |

|    | 14.6     | Quality Control                           | . 60 |

|    | 14.7     | Change Authorization and Revision Control | 61   |

|    | 14.8    | PCB Tests                             | 61   |

|----|---------|---------------------------------------|------|

|    | 14.9    | Secondary Component                   | 62   |

| 15 | Deliver | ables                                 | 62   |

|    | 15.1    | OS Support                            | 62   |

|    | 15.2    | Accessories                           | 62   |

|    | 15.3    | Documentation                         | 62   |

|    | 15.4    | Mass Production First Article Samples | 63   |

| 16 | Shippin | g                                     | 63   |

| 17 | Append  | lix                                   | . 64 |

|    | 17.1    | JBOG Debug POST codes.                | . 64 |

|    | 17.2    | Commonly Used Acronyms                | . 69 |

#### 4 Overview

#### 4.1 Introduction

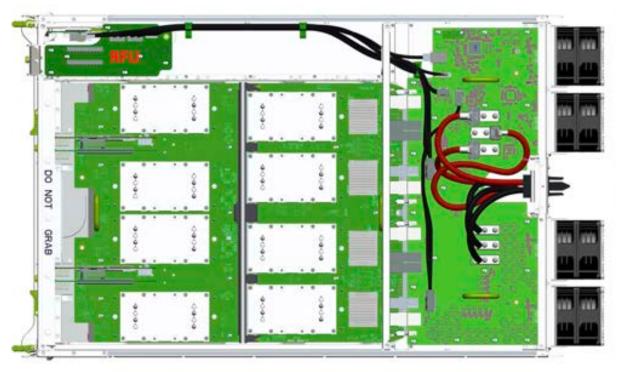

JBOG (Just-a-bunch-of-GPUs) supports 8x GPUs with flexible interconnect internally, and externally to host. There is no server head node in JBOG design. JBOG needs to work with a server head node such as Facebook server Intel Next Generation Xeon motherboard v3.1<sup>2</sup>.

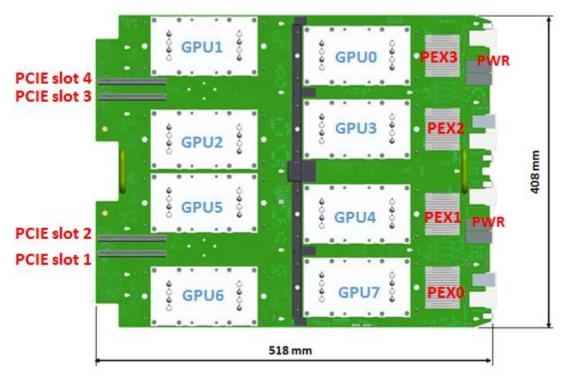

JBOG shall be compatible with Open Rack V2 (ORv2) and occupies 3x Open U(OU) of space. JBOG supports 8x NVIDIA Pascal P100 or Volta V100 GPUs in SXM2 form factor. The baseboard design is to be able to support next gen SXM2 GPU as well.

Below is a list of important items that form the JBOG system.

| Ta | ιbl | e | 4- | 1 |

|----|-----|---|----|---|

| Item                  | Description/Major components                     |  |  |

|-----------------------|--------------------------------------------------|--|--|

|                       | 8 NVIDIA Tesla P100 or Volta V100 SXM2 GPUs      |  |  |

|                       | 4 PCIE switches                                  |  |  |

|                       | 8 x16 PCIE Gen3 slots for GPU                    |  |  |

| Baseboard             | 2 x16 Standard PCIe Gen3 Slots for AICs          |  |  |

|                       | BMC and CPLD                                     |  |  |

|                       | Power connectors from Rack Bus bar               |  |  |

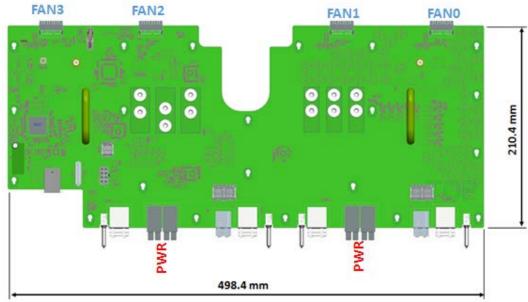

|                       | Power/Signal connectors for Baseboard            |  |  |

| Middle Plane Board    | Power/Signal connectors for IO board             |  |  |

|                       | BMC network port                                 |  |  |

|                       | OCP Debug card support                           |  |  |

| IO board              | User LEDs                                        |  |  |

|                       | 4 mini-SAS HD connectors                         |  |  |

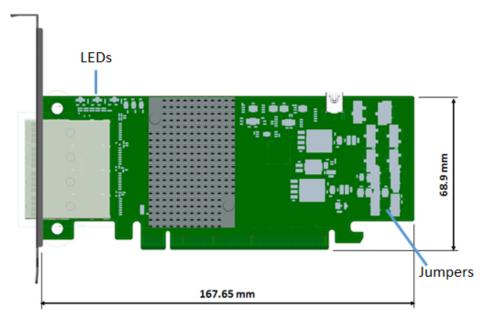

|                       | x16 PCIE Gen3 retimer                            |  |  |

|                       | config jumpers to configure retimer in different |  |  |

| Host Side Bridge Card | modes                                            |  |  |

| JBOG Side Bridge Card | 4 mini-SAS HD connector                          |  |  |

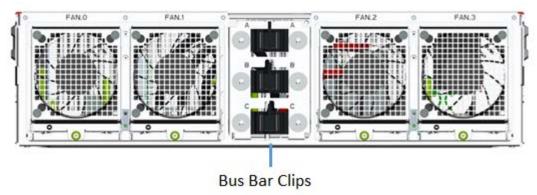

| Fans                  | 4x System fans for cooling                       |  |  |

| Power Supply          | Open Rack V2                                     |  |  |

| Chassis               | 3 OU BOX for Open Rack v2                        |  |  |

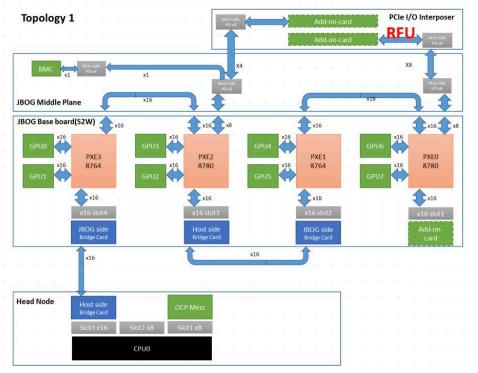

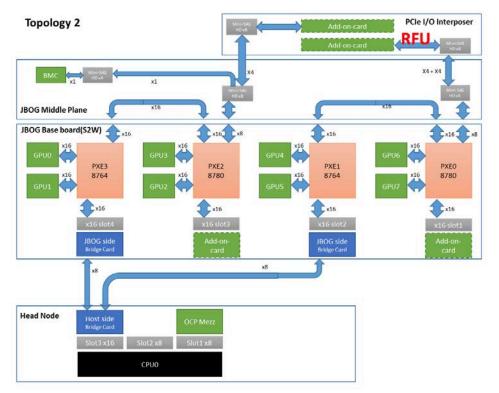

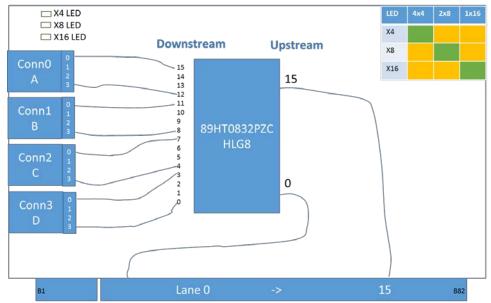

# 4.2 PCIe Block Diagram

There are 2x topologies for the JBOG system PCIe connection shown below, using a head node (Facebook server Intel Next Generation Xeon motherboard v3.1<sup>2</sup>).

User shall be able to configure the system in these topologies with only jumper change to retimer cards.

\_

Figure 4-1

Figure 4-2

Figure 4-3

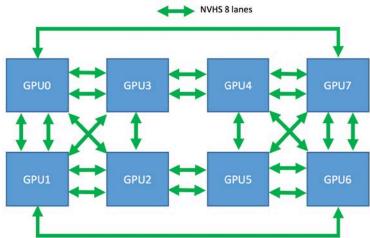

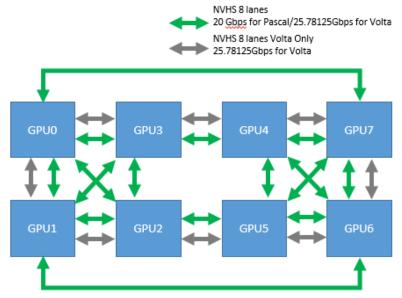

# 4.3 NVLINK topology

For JBOG with 8x GPUs in SXM2 form factor, it shall support NVLINK interconnection shown below. The Tesla P100 GPU has SERDES running at 20 Gbps. The Volta V100 GPU has SERDES running at 25.7812Gbps.

Figure 4-4

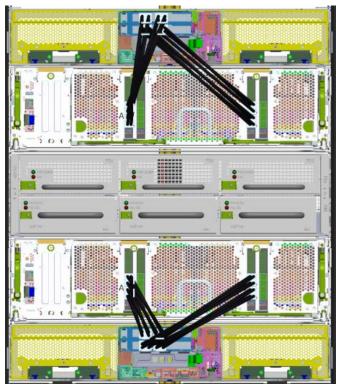

# 4.4 GPU Baseboard Design

JBOG for SXM2 GPUs leverages from the GPU Baseboard design of NVIDIA DGX-1 system. (http://www.nvidia.com/object/deeplearningsystem.html?mboxSession=8742eb98c6df4426b172 \cappa8881c7c6f7c3a)

JBOG for PCIe form factor GPU card will need a new PCIe GPU baseboard design. The detailed design is not in the scope of this specification. The vendor shall provision this use case when designing the rest of the system.

# 5 JBOG Interface to Host

This chapter defines the interface between JBOG and Host, including retimer cards, cables, and Host to JBOG side band connection for JBOG BMC.

#### 5.1 PCIe Cable Interface

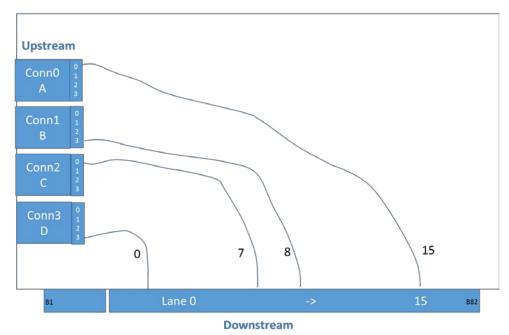

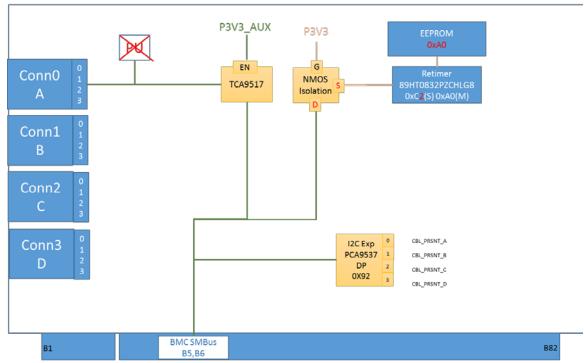

A MiniSAS-HD cable is used to provide connection from host node to JBOG, from JBOG to another JBOG, and within JBOG itself. Each cable has an x8 PCIe lane with side band signals defined in this section. Cables shall be plugged into PCIe bridge cards, which are plugged into the host node and JBOG enclosure. More details of PCIe bridge cards are described in section 5.2.

#### 5.1.1 Mini-SAS HD Connector (SFF-8644)

The pinout of host connectors has been modified from a standard Mini-SAS HD connection to allow for a sideband signaling. An external Mini-SAS HD connector is SFF-8644 standard form factor.

Please note the recent swap of PCIe Lane 0 and Lane 1 to be compatible with PCIe external cabling spec (PCI\_Express\_External\_Cabling\_Rev3 0\_v0 6 20151006)

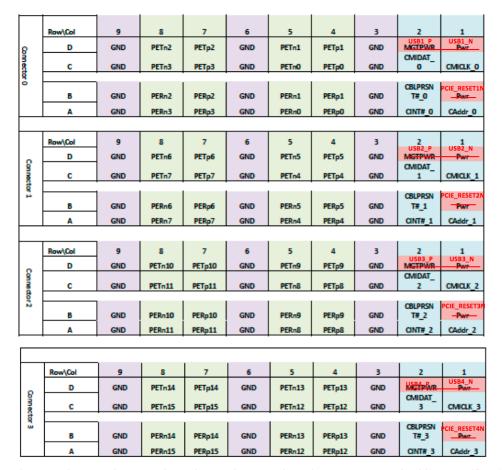

Table 5-1

| PCI Ext cable Dual layou | HOST                |       |             |       | END POINT           | PCI Ext cable Dual layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|---------------------|-------|-------------|-------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Name                | Pin   |             | Pin   | Name                | A STATE OF THE STA |

|                          | GND                 | D9 -  |             | В9    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETn2               | D8    | <b>→</b>    | B8    | PERn2               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETp2               | D7    | <b>→</b>    | В7    | PERp2               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | D6 -  |             | В6    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETn1               | D5    | <b>→</b>    | B5    | PERn1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETp1               | D4    | <b>→</b>    | B4    | PERp1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | D3    |             | В3    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

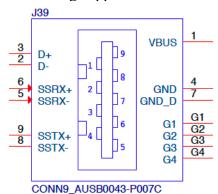

| MGTPWR                   | USB_DP              | D2    |             | D2    | USB_DP              | MGTPWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PWR                      | USB_DN              | D1    |             | D1    | USB_DN              | PWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                          | SCL                 | C1 -  |             | C1    | SCL                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | SDA                 | C2    |             | C2    | SDA                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | С3 —  |             | A3    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETp0               | C4    |             | A4    | PERp0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETn0               | C5    | <b>→</b>    | A5    | PERn0               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | C6    |             | A6    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETp3               | C7    | <b>→</b>    | A7    | PERp3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PETn3               | C8    | <b>→</b>    | A8    | PERn3               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | C9    |             | Α9    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | В9    |             | D9    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PERn2               | B8 <  |             | D8    | PETn2               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PERp2               | B7 <  |             | D7    | PETp2               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | В6    |             | D6    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PERn1               | B5 <  |             | D5    | PETn1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | PERp1               | B4 <  |             | D4    | PETp1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | GND                 | В3 —  |             | D3    | GND                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | CBLPRSNT#           | B2 —  | -           | B2    | CBLPRSNT#           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PWR                      | PCIE_RESET_N<br>RFU | B1    | <b>→</b>    | B1    | PCIE_RESET_N<br>RFU | PWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Caddr                    | PCIE_CLOCK_DP       | A1 -  | <b>&gt;</b> | A1    | PCIE_CLOCK_DP       | Caddr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |