# Panther+ Micro-Server Card Hardware Vo.7

#### Authors:

Mike Yan, Storage Hardware Design Engineer, Facebook Song Liu, Storage System Software Engineer, Facebook Jon Ehlen, Mechanical Engineer, Facebook

# 1 Contents

| 1 | Cont  | ents                                   | 2    |

|---|-------|----------------------------------------|------|

| 2 | Scop  | e                                      | 4    |

| 3 | Intro | duction                                | 4    |

|   | 3.1   | License                                | 4    |

| 4 | Pant  | her+ Overview                          | 5    |

|   | 4.1   | Micro-Server Card Specification        | 5    |

|   | 4.2   | Panther+ Feature List                  | 5    |

|   | 4.3   | Panther+ Block Diagram                 | 6    |

|   | 4.4   | Panther+ SKUs / Configurations         | 6    |

| 5 | Pant  | her+ Mechanical                        | 8    |

|   | 5.1   | Panther+ PCB Dimension                 | 8    |

|   | 5.2   | Panther+ Key Component Placement       | 10   |

|   | 5.3   | Panther+ Retention and Removal         | 10   |

| 6 | Pant  | her+ Thermal                           | 12   |

|   | 6.1   | System Airflow or Volumetric Flow      | 12   |

|   | 6.2   | Operational Ambient Temperatures       | 12   |

|   | 6.3   | Thermal Margin                         | 12   |

|   | 6.4   | Heat Sink Requirements                 | 12   |

|   | 6.5   | Temperature Sensors                    | .13  |

|   | 6.6   | Thermal Alerts                         | .13  |

| 7 | Pant  | her+ Electrical                        | 14   |

|   | 7.1   | DDR <sub>3</sub> ECC SO-DIMM           | 14   |

|   | 7.2   | mSATA SSD Module                       | 14   |

|   | 7.3   | NGFF Flash Card                        | 14   |

|   | 7.4   | BIOS SPI Flash and Socket              | 15   |

|   | 7.5   | FRU EEPROM                             | 15   |

|   | 7.6   | Ethernet and NIC EEPROM                | 16   |

|   | 7.7   | FPGA                                   | 16   |

|   | 7.8   | Voltage Monitor                        | . 17 |

|   | 7.9   | Pin Definition of PCI-E Edge Connector | .17  |

|   | 7.10  | LEDs                                   | 19   |

|   | 7.11  | PCB Stack-up                           | 20   |

| 8 | Pant  | her+ Power Budget                      | 23   |

|    | 8.1   | Power Budget for High Configuration            | 23 |

|----|-------|------------------------------------------------|----|

|    | 8.2   | Power Budget for Medium Configuration          | 23 |

|    | 8.3   | Power Budget for Low Configuration             | 23 |

| 9  | Pant  | her+ Functional                                | 24 |

|    | 9.1   | BIOS Feature List                              | 24 |

|    | 9.2   | BMC Feature Support                            | 25 |

|    | 9.3   | I2C Addressing                                 | 25 |

|    | 9.4   | Serial Console                                 | 26 |

|    | 9.5   | Power Control                                  | 26 |

|    | 9.6   | IPMI Commands Support                          | 26 |

|    | 9.7   | System Sensors                                 | 26 |

| 10 | Envir | onmental Requirements and Reliability          | 27 |

|    | 10.1  | Environmental Requirements                     | 27 |

|    | 10.2  | Vibration and Shock                            | 27 |

|    | 10.3  | Mean Time Between Failures (MTBF) Requirements | 27 |

|    | 10.4  | Regulations                                    | 28 |

| 11 | Labe  | ls and Markings                                | 28 |

|    | 11.1  | PCBA Labels and Markings                       | 28 |

|    | 11.2  | Chassis Labels and Markings                    | 28 |

| 12 | Preso | cribed Materials2                              | 29 |

|    | 12.1  | Sustainable Materials                          | 29 |

|    | 12.2  | Disallowed Components                          | 29 |

|    | 12.3  | Capacitors and Inductors                       | 29 |

|    | 12.4  | Component De-Rating                            | 30 |

| 13 | Revis | sion History                                   | 30 |

# 2 Scope

This document describes the technical specifications used in the design of an Intel Avoton SoC based Micro-Server card for Open Compute Project, known as the Panther+.

# 3 Introduction

When data center design and hardware design move in concert, they can improve efficiency and reduce power consumption. To this end, the Open Compute Project is a set of technologies that reduces energy consumption and cost, increases reliability and choice in the marketplace, and simplifies operations and maintenance. One key objective is openness -- the project is starting with the opening of the specifications and mechanical designs for the major components of a data center, and the efficiency results achieved at facilities using Open Compute technologies.

One component of this project is a Micro-Server design, which is a PCI-E-like card that hosts an SoC, dynamic memories for the SoC, and storage devices. This Micro-Server can be installed in slots on a baseboard that provides power distribution and control, BMC management capabilities, and network distribution. Depends on different baseboard and platform design, the Micro-Server can be applied to various areas such as server, storage, networking and other IT equipment. The modularized design concept of Micro-Server makes it easy to be adopted and configured, also flexible to upgrade the compute module in different pace from the system.

Panther+ is an Intel Avoton based Micro-Server card. It's compatible with Micro-Server x16 card specification, comes with a fixed maximum length of 210mm, and supports up to 80W total power consumption.

#### 3.1 License

As of April 7, 2011, the following persons or entities have made this Specification available under the Open Web Foundation Final Specification Agreement (OWFa 1.0), which is available at

http://www.openwebfoundation.org/legal/the-owf-1-o-agreements/owfa-1-o

Facebook, Inc.

You can review the signed copies of the Open Web Foundation Agreement Version 1.0 for this Specification at http://opencompute.org/licensing/, which may also include additional parties to those listed above.

Your use of this Specification may be subject to other third party rights. THIS SPECIFICATION IS PROVIDED "AS IS". The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF

CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

# 4 Panther+ Overview

# 4.1 Micro-Server Card Specification

Panther+ follows the general design specification for a standard Micro-Server card, which can be found on the Open Compute Project website:

- Open\_Compute\_Project\_Micro-Server\_Card\_Specification\_vo.7.pdf

- From: <a href="http://www.opencompute.org/projects/motherboard-design/">http://www.opencompute.org/projects/motherboard-design/</a>

- Or: <a href="http://www.opencompute.org/wiki/Motherboard/SpecsAndDesigns">http://www.opencompute.org/wiki/Motherboard/SpecsAndDesigns</a>

#### 4.2 Panther+ Feature List

Panther+ is a Micro-Server card based on Intel Avoton SoC, a new generation of Intel Atom processor. Main feature list of Panther+ card is as following:

- One Intel Avoton SoC, SKU selection:

- o C2750: 8 cores, 2.4GHz, 20W TDP

- o C2550: 4 cores, 2.4GHz, 14W TDP

- o C2350: 2 cores, 1.7GHz, 6W TDP

- Up to four SO-DIMM slots

- o Two channels, two DIMMs per channel

- o DDR3-1600, only support DDR3L (low-voltage, 1.35V)

- o ECC enabled

- O 32 GB max

- One mSATA SSD module

- SATA3 interface

- o 256 GB max

- One NGFF flash card (M.2)

- SATA<sub>3</sub> or PCI-E x<sub>4</sub> interface (BOM Option)

- o 2280 form factor (option to support 2260)

- o 256 GB max

- Three Status LEDs

- One Blue LED for power

- o One Amber / Orange LED for beep

- o One Yellow-Green LED reserved for diagnostic

- One JTAG connector

- Reserved for OCP test purpose

As defined in Micro-Sever specification, Panther+ supports below features on the interface to baseboard through the PCI-E x16 golden finger:

- One PCI-E x8 port, Gen2

- One PCI-E x4 port, Gen2

- One 1GbE port (SerDes)

- One SATA2 port

- One USB 2.0 port

- One UART port

- One I2C bus for management bridge IC (FPGA)

- One I2C / SMBus dedicated for Shared-NIC

- Four pins for slot ID (or hardware revision)

- One pin for power button

- One pin for system reset

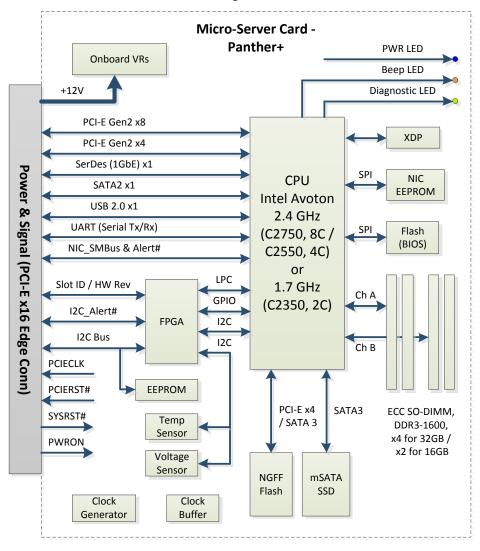

# 4.3 Panther+ Block Diagram

Figure 1 illustrates the functional block diagram of the Panther+ Micro-Server card.

Figure 1 Panther+ Block Diagram

# 4.4 Panther+ SKUs / Configurations

There are three different SKUs / configurations for Panther+ that's targeted for different use cases, all of them are now being built and tested.

#### 4.4.1 Panther+ High Configuration

Typical use case for Panther+ high configuration now is mainly for storage server.

- One Intel Avoton SoC

- o C2750: 8 cores, 2.4GHz, 20W TDP

- Four SO-DIMM slots

- o Two channels, two DIMMs per channel

- O 32 GB POR

- One mSATA SSD module on SATA3 interface

- o 256 GB POR

- One NGFF (M.2) flash card on SATA3 interface

- o 256 GB POR

# 4.4.2 Panther+ Medium Configuration

Typical use case for Panther+ medium configuration now is mainly for network switch control plane.

- One Intel Avoton SoC

- C2550: 4 cores, 2.4GHz, 14W TDP

- Four SO-DIMM slots

- o Two channels, two DIMM slots per channel, only one DIMM on channel A

- o 32 GB Max, 8 GB POR

- One mSATA SSD module on SATA3 interface

- o 128 GB POR

# 4.4.3 Panther+ Low Configuration

Typical use case for Panther+ low configuration now is mainly for rack and power monitoring.

- One Intel Avoton SoC

- o C2350: 2 cores, 1.7GHz, 6W TDP

- One SO-DIMM slot

- o On DIMM channel A

- o 4 GB POR

- One mSATA SSD module on SATA3 interface

- o 60 GB POR

# 4.4.4 Panther+ Common Components

Other common key components among different Panther+ SKUs / configurations are:

- PCB

- BIOS chip

- FPGA

- EEPROM

- Voltage Monitor

- Temperature Sensor

- Clock generator and buffer

- On-board voltage regulators

- LEDs

# 5 Panther+ Mechanical

# 5.1 Panther+ PCB Dimension

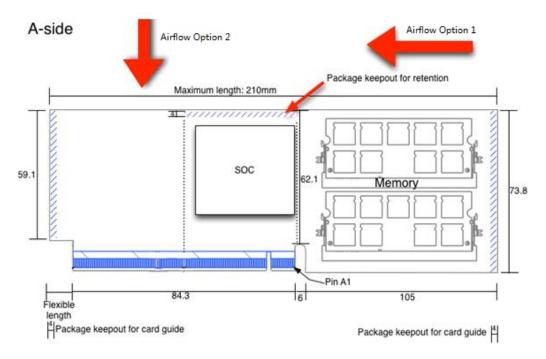

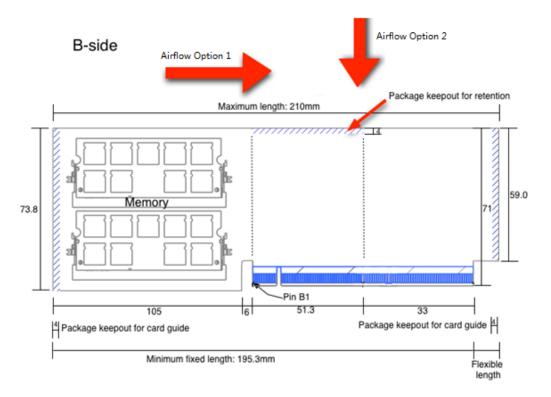

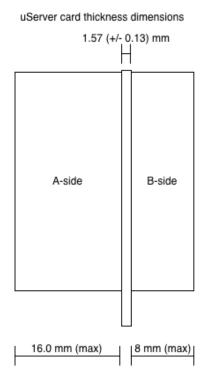

Figure 2 to Figure 4 shows the details of the Panther+ PCB dimension. The A-side is also referred as the top side, while the B-side is referred to as the bottom side.

Instead of a flexible length for the generic Micro-Server card specification, Panther+ adopts the fixed length at the maximum (210mm). Its dimensions are as below:

Width: 73.8mmLength: 210mm

Because Panther+ will be used in different platforms and systems, Figure 2 and Figure 3 show the two airflow options for cooling.

Figure 2 Panther+ Card Dimension, A side

Figure 3 Panther+ Card Dimension, B side

Figure 4 Panther+ Card Height Limitation

# 5.2 Panther+ Key Component Placement

Figure 2 and Figure 3 above already show the suggested placement for key components on Panther+ card. The following items are requested or recommended:

- Avoton SoC must be placed on the top side

- SO-DIMM slots can be placed on the top side, bottom side, or both sides. But they must be placed ahead of SoC (toward the cold-aisle in airflow option 1)

- SO-DIMM slots may be oriented in any direction. The drawing is for illustration only and not intended to define specific placement or quantity of SO-DIMM slots

- mSATA SSD module may be placed on the bottom side

- NGFF flash card may be placed on the bottom side

- Supports form factor of 2280

- Option to support form factor of 2260

# 5.3 Panther+ Retention and Removal

# 5.3.1 Panther+ Keep-out Areas

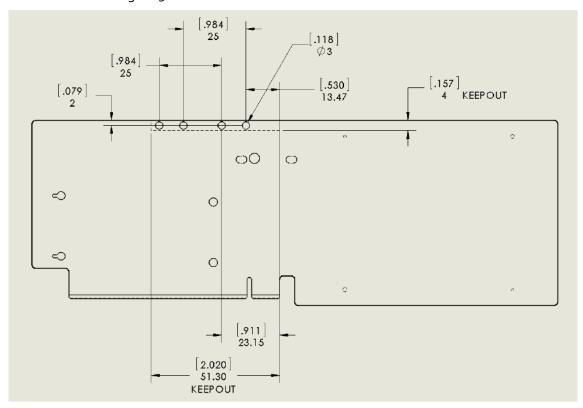

In addition to the 4mm keep-outs along the edges of the card, a 51.3m x 4mm keep-out is defined directly above the PCI-E edge connector / golden finger. This keep-out also includes two sets of two small holes that can be used to attach tool to ease insertion and extraction of the cards. See Figure 5 for more details.

Figure 5 Panther+ Hole Definition for Insertion and Removal

#### 5.3.2 Panther+ Card Grip (Optional)

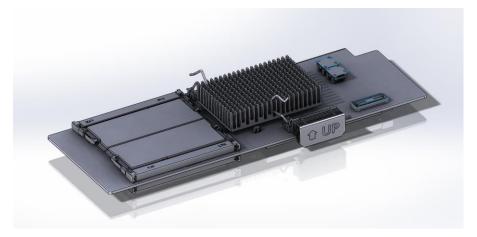

The Panther+ assembly shall be removed from the baseboard with one hand. A "grip" feature is suggested to be installed in the keep out area, allowing the user to grab the PCBA for insertion and removal, without touching components or keep outs directly. Concept of this grip feature is shown below in Figure 6. Any proposed grip features shall resemble the look and feel of the example, and shall be designed to be as generous as possible in finger grip area, while allowing unimpeded access to the rest portion of the system for service, and without negatively impacting the airflow.

Figure 6 Concept of Card Grip for Panther+

# 5.3.3 Panther+ Card Latch (Optional)

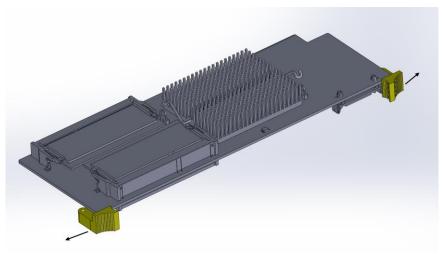

Latches on the left and right side of the Panther+ PCB shall restrain it. These latches, as shown below in Figure 7, will rotate horizontally, and will not be spring-loaded. If a latch is opened it will stay open until it is manually closed. These latches will have features that will impart a tactile feedback ("click") when in the fully open and fully closed positions. They must pass transportation shock and vibration testing in the closed position, without additional parts or packing material. There will be a hard stop to restrain the latch from opening wider than necessary to allow the card to pass by, thus eliminating difficulty in retrieving a latch that has over-rotated into the chassis. The design of the latches shall copy as closely as space allows, the shape and size of the example. The pivot features are TBD by the vendor.

#### Figure 7 Concept of Latch Mechanism for Panther+

#### 6 Panther+ Thermal

# 6.1 System Airflow or Volumetric Flow

The unit of airflow (or volumetric flow) used for this specification is CFM (cubic feet per minute). The maximum allowable airflow per Watt in the system must be 0.16 CFM. The desired airflow per watt is 0.1 CFM or lower in the system at the mean temperature (plus or minus standard deviation).

# 6.2 Operational Ambient Temperatures

The minimum and average operational ambient temperatures for Panther+ would be 20°C and 25°C, respectively. The maximum operational temperature would be 30°C when the inlet / outlet of enclosure has less than 50% opening, or 35°C when the inlet / outlet of enclosure has greater than 50% opening.

# 6.3 Thermal Margin

The thermal margin is the difference between the maximum theoretical safe temperature and the actual temperature. The minimum 5% thermal margin in Tjunction / Tcase or both is allowed for every component on the card. The stabilized / operational target temperature for every components on the card should be at least 8% below its maximum theoretical safe temperature.

# 6.4 Heat Sink Requirements

It is required for Panther+ to use one heat sink design to cover both two airflow options, as shown in Figure 2 and Figure 3, and meet the thermal margin requirements as above.

The CPU and other heat sink retainers (such as spring clips, compression springs etc.) shall be designed to use the maximum allowable force specified by the chip manufacturer, and shall be centrally located so as to exert its force in the middle of the chip case in order to avoid tilting the heat sink during shock and vibration.

In the event that the heat sink is not centrally located over the CPU, and is biased or cantilevered to one side, there shall be sufficient retainers on the cantilevered side to restrain it from (a) tilting and striking the PCP or components under it during shock and vibration, and (b) tilting and separating from the PCB at an angle, potentially striking components or system features above it. Due to the nature of the thermal interface material requiring tight coplanarity between the bottom of the heat sink and the top of the CPU, it is critical that the heat sink not be allowed to tilt at any angle, or else risk breaking the TIM seal.

Additionally, the retention feature should not allow the user to inadvertently tile the heat sink either upwards or downwards, during its installation. It is preferred that the retention feature allow the heat sink to "float" enough to avoid this.

# 6.5 Temperature Sensors

Each card must provide temperature sensors for the SoC, the SO-DIMM(s), and one ambient temperature sensor. All temperature readings for each sensor must be readable via the management sideband interface to the baseboard.

Additionally, over-temperature thresholds are configurable and an alert mechanism is provided to enable thermal shutdown and / or an increase in airflow. The sensors are accurate to +/-2C.

The ambient temperature sensor can be a *TMP75* from Texas Instruments or an equivalent part from other vendors. Its I2C address is set to ox98. This sensor is placed along the rear edge of the card on the A-side. Please see the blue, circled area in the following Figure 8 for more information. Depends on different system platform placement and airflow condition, reading values from this sensor could have a certain off-set to the real ambient temperature surround it. The BMC software need to deal with it according to system thermal test results.

# A-side Maximum length: 210mm SOC Memory 73.8 Package keepout for card guide Flexible length Minimum fixed length: 162.3mm

Figure 8 Panther+ Ambient Temperature Sensor Location

#### 6.6 Thermal Alerts

Panther+ provides a mechanism to provide thermal alerts and over temperature notifications. The BMC on baseboard must be able to receive these alerts in a timely fashion to allow the system to take action quickly. The I<sub>2</sub>C alert signal must be used. In some cases, an over temperature condition may occur which forces Panther+ to power-off immediately. This condition must be logged.

# 7 Panther+ Electrical

# 7.1 DDR3 ECC SO-DIMM

Avoton supports DDR<sub>3</sub>-1600 SO-DIMM, with ECC feature enabled. Panther+ adopts both two channels, with two DIMMs on each channel, to support up to four DIMM slots with 32 GB maximally in total memory capacity. Only DDR<sub>3</sub>L, low-voltage (1.35V) SO-DIMM will be supported in Panther+ card.

8GB SO-DIMM modules for high configuration are as below:

- Micron, MT18KSF1G72HZ-1G6E2

- Hynix, HMT41GA7AFR8A-PBTo

4GB SO-DIMM modules for low configuration are as below:

- Micron, MT8KTF51264HZ-1G6N1

- Hynix, HMT451A7AFR8A-PB

In the cases of less than four SO-DIMM modules populated, the two slots on the bottom side (Ao and / or Bo) should be in the default configuration.

# 7.2 mSATA SSD Module

The mSATA SSD module on the SATA3 port o, mainly serves as a boot drive. It also keeps system configurations, event logs, etc. The maximum capacity is 256GB, but other capacities are also tested and targeted for different use cases.

Vendor and part number for high capacity (240GB~256GB):

- Micron, MTFDDAT240MAV-1AE12ABYY

- Intel, SSDMCEAW240A4

Vendor and part number for medium capacity (120GB~128GB):

- Micron, MTFDDAT120MAV-1AE12ABYY

- Intel, SSDMCEAW120A4

Vendor and part number for low capacity (6oGB~8oGB):

- Micron, MTFDDATo64MAY-1AH12ABYY

- Intel, TBD

# 7.3 NGFF Flash Card

The NGFF flash card will support two interfaces by different BOM options. The first and default setting is SATA3 port 1, the other is PCI-E Gen2 x4. For both options, the selected form factor is M.2 2280. Vendor can keep the design to support M.2 2260 form factor on Panther+ but it's optional.

Maximum capacity of the SATA<sub>3</sub>-based NGFF flash card is 256 GB. Vendor and part number selections are as below:

- SanDisk, SD6SN1M-256G

- Samsung, MZNTE256HMHP-0000

Maximum capacity of the PCI-E-based NGFF flash card is 256 GB. Vendor and part number selections are below (to be tested later):

- SanDisk, SD6PP4M-256G

- Samsung, MZHPU256HCGM-00000

#### 7.4 BIOS SPI Flash and Socket

BIOS code is stored in an SPI flash chip. This flash chip must be at least 64 Mbits. It can be a W25Q64FV from Winbond or an equivalent part from other vendors.

To enable the easy service in case of BIOS code crash, SO-8 package is preferred, and a corresponding socket is required.

# 7.5 FRU EEPROM

Each Panther+ card must include an FRU EEPROM. This EEPROM must be accessible from the I<sub>2</sub>C connection going to the baseboard and be at least <sub>12</sub>8 Kbits. Its I<sub>2</sub>C address is set to 0xA<sub>2</sub>. It can be a *M*<sub>2</sub>4<sub>12</sub>8-BWMN6TP from ST Microelectronics or an equivalent part from other vendors.

The FRU EEPROM will contain the field replacement unit ID (FRUID) information and any additional configuration information that may be required. The FRUID is formatted in accordance with the IPMI Platform Management FRU Information Storage Definition document.

The EEPROM must contain the following:

- Device Description

- Chassis Serial Number

- Board Manufacturer

- Board Product Name

- Board Part Number

- Board Serial Number

- Product Manufacturer

- Product Name

- Product Part Number

- Product Serial Number

- Product Asset Tag

- Product Build: e.g., EVT, DVT, PVT, MP

- Product Version: e.g., C1

- Product Comments

- Manufacturing date code

- Manufacturing lot code: (preferred, but optional)

- Manufacturing work order: (preferred, but optional)

- PCB revision

- SoC model name / part number

- SoC revision

- SoC Tj (junction temperature) maximum

#### 7.6 Ethernet and NIC EEPROM

The 1GbE port to Panther+ golden finger / edge connector supports SerDes interface. Avoton LAN port link mode configuration should choose "o1" for 1000BASE-KX as below Figure 9 shows, which is digested from Intel Avoton platform design guide.

#### **LAN Port Link Mode**

|   | Bits 5:4 - Initialization Control 3 (EEPROM)<br>also<br>Bits 23:22 - CTRL_EX (MMIO) | LAN Port Interface Link Mode                |

|---|-------------------------------------------------------------------------------------|---------------------------------------------|

| L | 00                                                                                  | Reserved                                    |

|   | 011                                                                                 | 1000BASE-KX (1 GbE)<br>2500BASE-X (2.5 GbE) |

|   | 10                                                                                  | SGMII                                       |

|   | 11                                                                                  | Reserved                                    |

Figure 9 Avoton LAN Port Link Mode

There is a NIC EEPROM on SPI bus for Ethernet configuration. This NIC EEPROM must be at least 128 Kbits. It can be an AT25128B from Atmel, M95128 from ST Microelectronics or an equivalent part from other vendors.

To perform on-line programing to the NIC EEPROM, the Maximum Fragment Size need to be set at 240 Byte in order to expedite the updating process.

# 7.7 FPGA

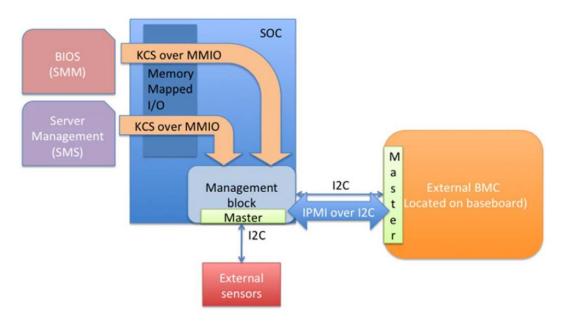

There's an FPGA on the Panther+ card. It is EP4CE6E22C8N from Altera (EP4CE10E22C8N for EVT / DVT build and test). The FPGA works as a management interface with the Avoton SoC. It provides an I2C bus as a system interface (to BMC on baseboard). The FPGA functional block diagram is shown in Figure 10.

Figure 10 Panther+ FPGA Functional Block Diagram

The FPGA implements the following peripherals on the local Host / CPU side:

- Two Intelligent Platform Management Interface (IPMI) keyboard controller style (KCS) interfaces (SMM and SMS) as defined in the IPMI specification

- At least one standard 16550 (mapped as COM1/0x3f8 to the host)

- General-purpose input / outputs (GPIOs) for controlling host functions and obtaining status (e.g., processor presence, voltage domain presence, power control, host reset, etc.)

- I2C Proxy interfaces for control and status (e.g., obtaining DIMM and CPU temperatures)

- Optional POST code buffer to hold BIOS/POST progress (mapped as Port 8oh to the host)

The interface to the baseboard is an I2C slave device. From a hardware perspective, this is a standard SMBus 2.0 open drain interface. It supports a minimum speed of 400 kHz. The BMC on the baseboard will act as the master on the bus during normal operation. During POST, the Avoton SoC may also act as a master. It is acceptable to have a small amount of glue logic on the card to support translating and/or buffering Avoton SoC signals. The I2C alert is signal is required. It is used as an interrupt for the BMC. Both the Avoton SoC and the BMC on the baseboard may be masters on the bus, so a multi-master environment must be supported.

# 7.8 Voltage Monitor

In order to ensure proper operation of all power rails at all times, a voltage monitor is required on the Panther+ card. It can be an *ADS7828* from TI or an equivalent part from other vendors. The I<sub>2</sub>C address of the voltage monitor should be 0x92.

Voltages are reported as part of the system enclosure status information. The power rails to be monitored are shown in Table 1.

| Power Rail                            | Voltage     |

|---------------------------------------|-------------|

| CPU VCCP                              | 0.5V ~ 1.3V |

| CPU VNN                               | 0.5V ~ 1.3V |

| CPU P1V0                              | 1.0V        |

| VDDQ                                  | 1.35V       |

| P <sub>1</sub> V8                     | 1.8V        |

| P <sub>3</sub> V <sub>3</sub> Main    | 3.3V        |

| P <sub>3</sub> V <sub>3</sub> Standby | 3.3V        |

| Input 12V                             | 12.5V       |

Table 1 Monitored Power Rails on Panther+ Card

# 7.9 Pin Definition of PCI-E Edge Connector

According to Micro-Server x16 card specification, Panther+ can support below two configurations. Table 2 shows relevant pin assignments.

- 1. Supports 3x PCI-E x4 + 1x Eth + 1x SATA + 8oW cards

- 2. Supports 1x PCI-E x4 + 1x PCI-E x8 + 1x Eth + 1x SATA + 8oW cards

Table 2 Pin Assignments for Panther+ PCI-E Golden Finger

| Pin Name                              | Side B   | Side A   | Pin Name                               |

|---------------------------------------|----------|----------|----------------------------------------|

| P12V                                  | 1        | 1        | PRSNT#                                 |

| P12V                                  | 2        | 2        | P12V                                   |

| P12V                                  | 3        | 3        | P <sub>12</sub> V                      |

| GND                                   | 4        | 4        | GND                                    |

| I <sub>2</sub> C_SCL                  | 5        | 5        | SVR_IDo/GPIOo                          |

| I <sub>2</sub> C_DATA                 | 6        | 6        | SVR_ID1/GPIO1                          |

| GND                                   | 7        | 7        | COM_TX                                 |

| PWR_BTN#                              | 8        | 8        | COM_RX                                 |

| USB_P                                 | 9        | 9        | SVR_ID2/GPIO2                          |

| USB_N                                 | 10       | 10       | SVR_ID <sub>3</sub> /GPIO <sub>3</sub> |

| SYS_RESET#                            | 11       | 11       | PCIE_RESET#                            |

|                                       |          |          |                                        |

| I <sub>2</sub> C_ALERT#               | 12       | 12       | GND                                    |

| GND                                   | 13       | 13       | PCIEo_REFCLK_P                         |

| GND                                   | 14       | 14       | PCIEo_REFCLK_N                         |

| PCIEo_TXo_P                           | 15       | 15       | GND                                    |

| PCIEo_TXo_N                           | 16       | 16       | GND                                    |

| GND                                   | 17       | 17       | PCIEo_RXo_P                            |

| GND                                   | 18       | 18       | PCIEo_RXo_N                            |

| PCIEo_TX1_P                           | 19       | 19       | GND                                    |

| PCIEo_TX1_N                           | 20       | 20       | GND                                    |

| GND                                   | 21       | 21       | PCIEo_RX1_P                            |

| GND                                   | 22       | 22       | PCIEo_RX1_N                            |

| PCIEo_TX2_P                           | 23       | 23       | GND                                    |

| PCIE <sub>0</sub> _TX <sub>2</sub> _N | 24       | 24       | GND                                    |

| GND                                   | 25       | 25       | PCIEo_RX2_P                            |

| GND                                   | 26       | 26       | PCIEo_RX2_N                            |

| PCIEo_TX3_P                           | 27       | 27       | GND                                    |

| PCIEo_TX3_N                           | 28       | 28       | GND<br>DCIE - DV - D                   |

| GND                                   | 29       | 29       | PCIEo_RX3_P                            |

| GND                                   | 30       | 30       | PCIEo_RX3_N                            |

| SATAO_TX_P                            | 31       | 31       | GND                                    |

| SATAo_TX_N                            | 32       | 32       | GND                                    |

| GND<br>GND                            | 33       | 33       | SATAo_RX_P<br>SATAo_RX_N               |

| PCIE1_REFCLK_P                        | 34       | 34       | GND                                    |

| PCIE1_REFCLK_N                        | 35<br>36 | 35<br>36 | GND                                    |

| GND                                   |          |          | PCIE2_REFCLK_P                         |

| GND                                   | 37<br>38 | 37<br>38 | PCIE2_REFCLK_N                         |

| PCIE1_RESET#                          |          |          | GND                                    |

| PCIE1_RESET#                          | 39<br>40 | 39<br>40 | GND                                    |

| GND                                   | 41       | 40       | RESERVED                               |

| GND                                   | 42       | 42       | NIC_SMBUS_ALERT#                       |

| NIC_SMBUS_SCL                         | 43       | 43       | GND                                    |

| NIC_SMBUS_SDA                         | 43       | 44       | GND                                    |

| GND                                   | 45       | 45       | GEo_RX_P                               |

| GIAD                                  | 45       | 45       | GEO_IVY_I                              |

| GND         | 46 | 46 | GEo_RX_N          |

|-------------|----|----|-------------------|

| GEo_TX_P    | 47 | 47 | GND               |

| GEo_TX_N    | 48 | 48 | GND               |

| GND         | 49 | 49 | PCIEo_RX4_P       |

| GND         | 50 | 50 | PCIEo_RX4_N       |

| PCIEo_TX4_P | 51 | 51 | GND               |

| PCIEo_TX4_N | 52 | 52 | GND               |

| GND         | 53 | 53 | PCIEo_RX5_P       |

| GND         | 54 | 54 | PCIEo_RX5_N       |

| PCIEo_TX5_P | 55 | 55 | GND               |

| PCIEo_TX5_N | 56 | 56 | GND               |

| GND         | 57 | 57 | PCIEo_RX6_P       |

| GND         | 58 | 58 | PCIEo_R6_N        |

| PCIEo_TX6_P | 59 | 59 | GND               |

| PCIEo_TX6_N | 60 | 60 | GND               |

| GND         | 61 | 61 | PCIEo_RX7_P       |

| GND         | 62 | 62 | PCIEo_RX7_N       |

| PCIEo_TX7_P | 63 | 63 | GND               |

| PCIEo_TX7_N | 64 | 64 | GND               |

| GND         | 65 | 65 | PCIE1_RXo_P       |

| GND         | 66 | 66 | PCIE1_RXo_N       |

| PCIE1_TXo_P | 67 | 67 | GND               |

| PCIE1_TXo_N | 68 | 68 | GND               |

| GND         | 69 | 69 | PCIE1_RX1_P       |

| GND         | 70 | 70 | PCIE1_RX1_N       |

| PCIE1_TX1_P | 71 | 71 | GND               |

| PCIE1_TX1_N | 72 | 72 | GND               |

| GND         | 73 | 73 | PCIE1_RX2_P       |

| GND         | 74 | 74 | PCIE1_RX2_N       |

| PCIE1_TX2_P | 75 | 75 | GND               |

| PCIE1_TX2_N | 76 | 76 | GND               |

| GND         | 77 | 77 | PCIE1_RX3_P       |

| GND         | 78 | 78 | PCIE1_RX3_N       |

| PCIE1_TX3_P | 79 | 79 | GND               |

| PCIE1_TX3_N | 80 | 80 | GND               |

| GND         | 81 | 81 | P <sub>12</sub> V |

| GND         | 82 | 82 | P <sub>12</sub> V |

# 7.10 LEDs

The Panther+ Micro-Server card has three LEDs on its front / leading edge, to display various types of information:

- One single color LED in blue for power status

- One single color LED in amber (or orange) for beep indication

- One single color LED in yellow-green reserved for diagnostics purpose

Table 3 through Table 5 summarizes the behavior of the LEDs.

# Table 3 LED for Power Status

| Power Status             | Blue LED |

|--------------------------|----------|

| Power on and good        | ON       |

| Power off or any problem | OFF      |

#### Table 4 LED For Beep Indication

| Beep Indication | Amber / Orange LED  |  |

|-----------------|---------------------|--|

| Beep off        | OFF                 |  |

| Beep on         | Follow Beep Pattern |  |

Table 5 LED Reserved For Diagnostics Purpose

| Diagnostics     | Yellow-Green LED           |  |

|-----------------|----------------------------|--|

| Diagnostics off | OFF                        |  |

| Diagnostics on  | Follow Diagnostics Pattern |  |

# 7.11 PCB Stack-up

The PCB thickness of the Panther+ card is 1.57mm. Based on different placement and routing strategies, the vendor may use either 12 layers or 14 layers of PCB for the Panther+ card. Table 6 and Table 7 show the example of 12 layers' PCB stack-up and impedance control. Table 8 and Table 9 shows the 14 layers'.

Table 6 PCB Stack-up for Panther+ Card, 12 Layers

| Layer          | er Plane Description |             | Copper Weight (oz) | Thickness (mil) | Dielectric (er) |  |

|----------------|----------------------|-------------|--------------------|-----------------|-----------------|--|

|                |                      | Solder Mask |                    | 0.5             | 3.7             |  |

| L1             | TOP                  | Signal      | o.5 + plating      | 1.9             |                 |  |

|                |                      | PrePreg     |                    | 2.7             | 3.5             |  |

| L <sub>2</sub> | GND1                 | Ground      | 1.0                | 1.3             |                 |  |

|                |                      | Core        |                    | 4.0             | 3.6             |  |

| L <sub>3</sub> | IN1                  | Signal      | 1.0                | 1.3             |                 |  |

|                |                      | PrePreg     |                    | 4.0             | 3.6             |  |

| L4             | GND<br>2             | Ground      | 1.0                | 1.3             |                 |  |

|                |                      | Core        |                    | 4.0             | 3.6             |  |

| L <sub>5</sub> | IN <sub>2</sub>      | Signal      | 1.0                | 1.3             |                 |  |

|                |                      | PrePreg     |                    | 4.0             | 3.6             |  |

| L6             | VCC1                 | Power       | 1.0                | 1.3             |                 |  |

|                |                      | Core        |                    | 7.0             | 4.0             |  |

| L <sub>7</sub> | VCC2                 | Power       | 1.0                | 1.3             |                 |  |

|                |                      | PrePreg     |                    | 4.0             | 3.6             |  |

| L8             | IN <sub>3</sub>      | Signal      | 1.0                | 1.3             |                 |  |

|                |                      | Core        |                    | 4.0             | 3.6             |  |

| L9  | GND <sub>3</sub> | Ground          | 1.0              | 1.3  |         |

|-----|------------------|-----------------|------------------|------|---------|

|     |                  | PrePreg         |                  | 4.0  | 3.6     |

| L10 | IN4              | Signal          | 1.0              | 1.3  |         |

|     |                  | Core            |                  | 4.0  | 3.6     |

| L11 | GND<br>4         | Ground          | 1.0              | 1.3  |         |

|     |                  | PrePreg         |                  | 2.7  | 3.5     |

| L12 | ВОТ              | Signal          | o.5 + plating    | 1.9  |         |

|     |                  | Solder Mask     |                  | 0.5  | 3.7     |

|     |                  | Total Thickness | s and Tolerance: | 62.2 | +/-6mil |

Table 7 PCB Impedance Control for Panther+ Card, 12 Layers

| Trace Width (mil) | Air Gap Spacing<br>(mil) | Impedance<br>Type | Layer       | Impedance<br>Target (ohm) | Tolerance<br>(+/-) |

|-------------------|--------------------------|-------------------|-------------|---------------------------|--------------------|

| 9.5               |                          | Single Ended      | 1, 12       | 33                        | 5 ohm              |

| 7.5               |                          | Single Ended      | 1, 12       | 38                        | 5 ohm              |

| 7.0               |                          | Single Ended      | 1, 12       | 40                        | 5 ohm              |

| 4.5               |                          | Single Ended      | 1, 12       | 50                        | 5 ohm              |

| 8.5               | 6.0                      | Differential      | 1, 12       | 65                        | 10%                |

| 5.5               | 8.0                      | Differential      | 1, 12       | 85                        | 10%                |

| 7.5               |                          | Single Ended      | 3, 5, 8, 10 | 33                        | 5 ohm              |

| 6.0               |                          | Single Ended      | 3, 5, 8, 10 | 38                        | 5 ohm              |

| 5.5               |                          | Single Ended      | 3, 5, 8, 10 | 40                        | 5 ohm              |

| 3.5               |                          | Single Ended      | 3, 5, 8, 10 | 50                        | 5 ohm              |

| 7.5               | 9.0                      | Differential      | 3, 5, 8, 10 | 65                        | 10%                |

| 4.5               | 8.5                      | Differential      | 3, 5, 8, 10 | 85                        | 10%                |

Table 8 PCB Stack-up for Panther+ Card, 14 Layers

| Layer          | Plane D          | Description | Copper Weight (oz) | Thickness (mil) | Dielectric (er) |

|----------------|------------------|-------------|--------------------|-----------------|-----------------|

|                |                  | Solder Mask |                    | 0.5             | 3.4             |

| L1             | TOP              | Signal      | o.5 + plating      | 1.9             |                 |

|                |                  | PrePreg     |                    | 2.9             | 3.3             |

| L <sub>2</sub> | GND <sub>1</sub> | Ground      | 0.5                | 0.65            |                 |

|                |                  | Core        |                    | 3.0             | 3.3             |

| L <sub>3</sub> | IN1              | Signal      | 0.5                | 0.65            |                 |

|                |                  | PrePreg     |                    | 5.0             | 3.4             |

| L4             | GND<br>2         | Ground      | 0.5                | 0.65            |                 |

|                |                  | Core        |                    | 3.0             | 3.3             |

| L <sub>5</sub> | IN <sub>2</sub>  | Signal      | 0.5                | 0.65            |                 |

|                |                  | PrePreg        |                      | 5.0  | 3.4     |

|----------------|------------------|----------------|----------------------|------|---------|

| L6             | GND <sub>3</sub> | Ground         | 0.5                  | 0.65 |         |

|                |                  | Core           |                      | 3.0  | 3.3     |

| L <sub>7</sub> | VCC1             | Power          | 1.0                  | 1.3  |         |

|                |                  | PrePreg        |                      | 5.0  | 3.4     |

| L8             | VCC <sub>2</sub> | Power          | 1.0                  | 1.3  |         |

|                |                  | Core           |                      | 3.0  | 3.3     |

| L9             | GND<br>4         | Ground         | 0.5                  | 0.65 |         |

|                |                  | PrePreg        |                      | 5.0  | 3.4     |

| L10            | IN <sub>3</sub>  | Signal         | 0.5                  | 0.65 |         |

|                |                  | Core           |                      | 3.0  | 3.3     |

| L11            | GND <sub>5</sub> | Ground         | 0.5                  | 0.65 |         |

|                |                  | PrePreg        |                      | 5.0  | 3.4     |

| L12            | IN <sub>4</sub>  | Signal         | 0.5                  | 0.65 |         |

|                |                  | Core           |                      | 3.0  | 3.3     |

| L13            | GND<br>6         | Ground         | 0.5                  | 0.65 |         |

|                |                  | PrePreg        |                      | 2.9  | 3.3     |

| L14            | ВОТ              | Signal         | o.5 + plating        | 1.9  |         |

|                |                  | Solder Mask    | Solder Mask          |      | 3.4     |

|                |                  | Total and Tole | Total and Tolerance: |      | +/-6mil |

Table 9 PCB Impedance Control for Panther+ Card, 14 Layers

| Trace Width (mil) | Air Gap Spacing<br>(mil) | Impedance<br>Type | Layer        | Impedance<br>Target (ohm) | Tolerance<br>(+/- %) |

|-------------------|--------------------------|-------------------|--------------|---------------------------|----------------------|

| 10.5              |                          | Single Ended      | 1, 14        | 33                        | 5 ohm                |

| 7.5               |                          | Single Ended      | 1, 14        | 40                        | 5 ohm                |

| 4.8               |                          | Single Ended      | 1, 14        | 50                        | 5 ohm                |

| 3.9               |                          | Single Ended      | 1, 14        | 55                        | 10%                  |

| 5.9               | 8.6                      | Differential      | 1, 14        | 85                        | 10%                  |

| 4.2               | 9.8                      | Differential      | 1, 14        | 100                       | 10%                  |

| 7.8               |                          | Single Ended      | 3, 5, 10, 12 | 33                        | 5 ohm                |

| 6.3               |                          | Single Ended      | 3, 5, 10, 12 | 38                        | 5 ohm                |

| 3.9               |                          | Single Ended      | 3, 5, 10, 12 | 50                        | 5 ohm                |

| 4.8               | 7.2                      | Differential      | 3, 5, 10, 12 | 85                        | 10%                  |

| 3.7               | 9.8                      | Differential      | 3, 5, 10, 12 | 100                       | 10%                  |

# 8 Panther+ Power Budget

# 8.1 Power Budget for High Configuration

Board level power budget of Panther+ high configuration is about 37.3W. Table 10 shows the details of calculation estimated as of now.

Table 10 Panther+ Power Budget for High Configuration

| Major Device                | TDP max (W) | Qty | Utilization (%) | Power (W) |

|-----------------------------|-------------|-----|-----------------|-----------|

| Processor (Avoton) 8 core   | 20          | 1   | 90%             | 18        |

| DDR3 U-DIMM / SO-DIMM       | 5           | 4   | 70%             | 14        |

| M-SATA SSD                  | 2.3         | 1   | 70%             | 1.61      |

| PCI-E NGFF Flash            | 3           | 1   | 70%             | 2.1       |

| Other uServer Card Logic/IC | 2           | 1   | 80%             | 1.6       |

| Power Buidget for Panth     | 37.31       |     |                 |           |

# 8.2 Power Budget for Medium Configuration

The board level power budget of Panther+ medium configuration is about 22.8W. Table 11 shows the details of calculation estimated as of now.

Table 11 Panther+ Power Budget for Medium Configuration

| Major Device                                          | TDP max (W) | Qty | Utilization (%) | Power (W) |

|-------------------------------------------------------|-------------|-----|-----------------|-----------|

| Processor (Avoton) 4 core                             | 14          | 1   | 90%             | 12.6      |

| DDR3 U-DIMM / SO-DIMM                                 | 5           | 2   | 70%             | 7         |

| M-SATA SSD                                            | 2.3         | 1   | 70%             | 1.61      |

| PCI-E NGFF Flash                                      | 3           | 0   | 70%             | 0         |

| Other uServer Card Logic/IC                           | 2           | 1   | 80%             | 1.6       |

| Power Buidget for Panther+ Card, Medium Configuration |             |     |                 | 22.81     |

# 8.3 Power Budget for Low Configuration

The board level power budget of Panther+ low configuration is about 11.3W. Table 12 shows the details of calculation estimated as of now.

Table 12 Panther+ Power Budget for Low Configuration

| Major Device                | TDP max (W) | Qty   | Utilization (%) | Power (W) |

|-----------------------------|-------------|-------|-----------------|-----------|

| Processor (Avoton) 2 core   | 6           | 1     | 90%             | 5.4       |

| DDR3 U-DIMM / SO-DIMM       | 5           | 1     | 70%             | 3.5       |

| M-SATA SSD                  | 2.3         | 1     | 70%             | 1.61      |

| PCI-E NGFF Flash            | 3           | 0     | 70%             | 0         |

| Other uServer Card Logic/IC | 80%         | 0.8   |                 |           |

| Power Buidget for Pant      | nfiguration | 11.31 |                 |           |

# 9 Panther+ Functional

# 9.1 BIOS Feature List

The Panther+ BIOS design will follow the same requirements as the generic Micro-Server card. Highlighted key items as below:

- UEFI compatible

- Configuration and features

- o Disable unused devices

- BIOS setup menu

- SoC settings to allow tuning to achieve the optimal combination of performance and power consumption

- BIOS settings tools

- Default boot device priority

- Network / PXE -> mSATA SSD module -> NGFF flash card -> Other removable devices

- PXE boot

- Supports PXE boot and provide the ability to modify the boot sequence. When PXE booting, the card first attempts to boot from the first Ethernet device (etho). If this fails, the PXE boot will attempt on the next Ethernet device.

- iSCSI network boot

- Other boot options

- Also supports booting from SATA/SAS and USB interfaces

- o Provides the capability to select boot options

- Remote BIOS update

- Scenario 1: Sample / audit BIOS settings

- Scenario 2: Update BIOS with pre-configured set of BIOS settings

- Scenario 3: BIOS / firmware update with a new revision

- Update from the operating system over the LAN

- Can complete BIOS update or setup change with a single reboot (no PXE boot, no multiple reboots)

- No user interaction (e.g., prompts)

- BIOS updates and option changes do not take longer than five minutes to complete

- o Can be scripted and propagated to multiple machines

- Event log

- o Implement SMBIOS type 15 per SMBIOS specification Rev 2.6

- Hold more than 500 event records (assuming the maximum event record length is 24 bytes, then the size will be larger than 12KB)

- Each event record includes enhanced information identifying the error source device's vendor ID, card slot ID, and device ID

- A system access interface and application software to retrieve and clear the event log from the BIOS

- Logged errors

- o CPU / memory errors

- PCI-E errors

- SATA errors

- POST errors

- System reboot events

- o Sensor values exceeding warning or critical thresholds

- Error thresholds

- o Setting must be enabled for both correctable and uncorrectable errors

- o Threshold for Memory Correctable ECC is TBD

- o PCI-E error, follow chipset vendor's suggestion

- POST codes

- o To be displayed on debug card

- o To be provided on the serial console

# 9.2 BMC Feature Support

The BMC on baseboard will support DCMI 1.5 plus an extended set of commands to enable support for the multi-node environment. The following is a list of features that Panther+ BIOS need to support in relevant BMC firmware design:

- All SEL commands

- All sensor commands

- All SDR commands

- LAN print / set commands

- Power on/off/cycle / hardware reset / soft reset commands

- Chassis identify force on/off

- Micro-Server card reset cold/warm

- Micro-Server card info

- SoL activate/de-activate

- FRU list

- System boot parameters

# 9.3 I2C Addressing

The Panther+ and baseboard BMC will communicate by using IPMI 2.0 commands transmitted over the I2C connection through the FPGA. In a multiple Micro-Server cards environment, each Panther+ need to have a unique I2C address that is determined using the slot ID. The upper 3 bits of the I2C address are defined as objoo while the lower 4 bits are composed of the slot ID bits. The FPGA I2C slave address is calculated by: ox40 + svr\_id[3:0]. Please refer to Table 13 for the details.

Table 13 Panther+ I2C address assignment

| Node # | SVR_ID | FPGA I2C Address |

|--------|--------|------------------|

| Node o | oboooo | ox8o             |

| Node 1 | obooo1 | 0x82             |

| Node 2 | ob0010 | ox84             |

| Node 3 | ob0011 | ox86             |

| Node 4 | obo100 | ox88             |

| Node 5 | ob0101 | ox8A             |

| Node 6 | obo110 | ox8C             |

| Node 7  | obo111 | ox8E |

|---------|--------|------|

| Node 8  | ob1000 | 0x90 |

| Node 9  | ob1001 | 0X92 |

| Node 10 | ob1010 | 0X94 |

| Node 11 | ob1011 | ox96 |

| Node 12 | ob1100 | ox98 |

| Node 13 | ob1101 | ох9А |

| Node 14 | ob1110 | ох9С |

| Node 15 | ob1111 | ox9E |

# 9.4 Serial Console

Panther+ provides a UART port on the card edge. This connection will be used as the BIOS or OS serial console and will also be available as a Serial over LAN (SoL) connection via the BMC. The BIOS menus must be fully accessible and text-based. Any required hot keys must be transmittable through a serial console session.

The BIOS should set default to 57600bps/8N1.

# 9.5 Power Control

The BMC controls power on, off, and reset directly via the signals defined in the pin-out. If 12V to the card is lost and returns ("AC Lost"), the BIOS must be configurable to enable immediate or delayed power-on, or reverting to the last power state prior to the event.

# 9.6 IPMI Commands Support

The following list of IPMI commands must be supported by Panther+ through FPGA.

TBD

# 9.7 System Sensors

The following list of sensors are provided by Panther+, and will be reported to the BMC on baseboard.

- Analog sensors

- CPU Temp sensor(s)

- o CPU Package Power (PECI)

- DIMM Temperature(s)

- Panther+ on-board Temp sensor(s)

- Panther+ on-board Voltage(s)

- Discrete sensors

- o CPU Thermal Trip

- Power Threshold Event

- SEL Status: Clear, Rollover

- DCMI Watchdog

- Processor Fail

- Event only sensors

- o POST Error

- Proc Hot Ext

- Mem Hot Ext

- Machine Check Error

- o PCI-E Error

- Voltage Error

- Memory ECC Error

# 10 Environmental Requirements and Reliability

# 10.1 Environmental Requirements

The Panther+ Micro-Server card should support the related system(s) to meet the following environmental requirements:

- Gaseous contamination: Severity Level G1 per ANSI/ISA 71.04-1985

- Operating and storage relative humidity: 10% to 90% (non-condensing)

- Storage temperature range: -40°C to +70°C (long-term storage)

- Transportation temperature range: -55°C to +85°C (short-term storage)

- Operating altitude with no de-rating to 1,000m (3,300 feet)

# 10.2 Vibration and Shock

The Panther+ Micro-Server card should support the related system(s) to meet shock and vibration requirements according to the following IEC specifications: IEC78-2-(\*) & IEC721-3-(\*) Standard & Levels. The testing requirements are listed in Table 14.

Table 14 Vibration and Shock Requirements

|           | Operating                                                                                                               | Non-Operating                                                                                                         |

|-----------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Vibration | o.5g acceleration, 5 to 500 Hz, 10 sweeps at 1 octave/minute per each of the three axes (one sweep is 5 to 500 to 5 Hz) | 1g acceleration, 5 to 500 Hz, 10 sweeps at 1 octave/minute per each of the three axes (one sweep is 5 to 500 to 5 Hz) |

| Shock     | 6g, half-sine 11mS, 5 shocks per each of the three axes                                                                 | 12g, half-sine 11mS, 10 shocks per each of the three axes                                                             |

# 10.3 Mean Time Between Failures (MTBF) Requirements

The Panther+ Micro-Server card should support the related system(s) to have a minimum calculated MTBF of 300,000 hours at 95% confidence level at 25°C ambient temperature while running at full load.

The system(s) shall meet a demonstrated MTBF of minimum 300,000 hours at 95% confidence level prior to the mass production ramp.

The system(s) shall have a minimum service life of 5 years (24 hours/day, full load, at 35°C ambient temperature).

# 10.4 Regulations

The Panther+ Micro-Server card should support the related system(s) to obtain CB reports by the vendor(s). Facebook will need these documents to have rack level CE.

# 11 Labels and Markings

# 11.1 PCBA Labels and Markings

Panther+ PCBAs shall include the following labels on the component side of the boards. The labels shall not be placed in such a way that may cause them to disrupt the functionality or the airflow path of the system.

Table 15 PCBA Label Requirements

| Description                                                                                                                                                                                                                                                                                                                                         | Туре           | Barcode<br>Required? |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------|

| Safety markings                                                                                                                                                                                                                                                                                                                                     | Silkscreen     | No                   |

| Vendor P/N, S/N, REV (revision would increment for any approved changes)                                                                                                                                                                                                                                                                            | Adhesive label | Yes                  |

| Vendor logo, name & country of origin                                                                                                                                                                                                                                                                                                               | Silkscreen     | No                   |

| PCB vendor logo, name                                                                                                                                                                                                                                                                                                                               | Silkscreen     | No                   |

| Facebook P/N                                                                                                                                                                                                                                                                                                                                        | Adhesive label | Yes                  |

| Date code (industry standard: WEEK/YEAR)                                                                                                                                                                                                                                                                                                            | Adhesive label | Yes                  |

| DC input ratings                                                                                                                                                                                                                                                                                                                                    | Silkscreen     | No                   |

| RoHS compliance                                                                                                                                                                                                                                                                                                                                     | Silkscreen     | No                   |

| WEEE symbol: The motherboard will have the crossed out wheeled bin symbol to indicate that it will be taken back by the manufacturer for recycling at the end of its useful life. This is defined in the European Union Directive 2002/96/EC of January 27, 2003 on Waste Electrical and Electronic Equipment (WEEE) and any subsequent amendments. | Silkscreen     | No                   |

# 11.2 Chassis Labels and Markings

For any system(s) with Panther+ Micro-Server card, the chassis shall carry the following adhesive barcoded labels in visible locations where they can be easily scanned during integration. Vendor and Facebook will have an agreement for the label locations.

Table 16 Chassis Label Requirements

| Description                                                              |

|--------------------------------------------------------------------------|

| Vendor P/N, S/N, REV (revision would increment for any approved changes) |

#### Facebook P/N

Date code (industry standard: WEEK/YEAR)

The assembly shall be marked "THIS SIDE UP", "TOP SIDE", "UP ^" or other approved marking in bright, large characters in a color TBD. This printing may be on the PCB itself, or on an installed component such as an air baffle. The label should be clear and easy to read in low light conditions, when viewed from above or below from 2 feet away and at an angle of approximately 60 degrees off horizontal.

# 12 Prescribed Materials

#### 12.1 Sustainable Materials

Materials and finishes that reduce the life cycle impact of servers should be used where cost and performance are not compromised. This includes the use of non-hexavalent metal finishes, recycled and recyclable base materials and materials made from renewable resources, with associated material certifications.

Facebook identified plastic alternatives including polypropylene plus natural fiber (PP+NF) compounds that meet functionality requirements while reducing cradle to gate environmental impact when compared to PC/ABS. GreenGranFo23T is one acceptable alternate material. JPSECO also offers a PP+NF material that is acceptable; the model number will be available at a later date. It is strongly preferred that such alternatives are identified and used. If vendor is unable to use this, or a similar alternate material, vendor will provide a list of materials that were considered and why they were not successfully incorporated.

#### 12.2 Disallowed Components

The following components shall not be used in the design of the motherboard:

- Components disallowed by the European Union's Restriction of Hazardous Substances Directive (RoHS)

- Trimmers and/or potentiometers

- Dip switches

# 12.3 Capacitors and Inductors

The following limitations shall be applied to the use of capacitors:

- Only aluminum organic polymer capacitors from high-quality manufacturers are used; they must be rated 105°C

- All capacitors have a predicted life of at least 50,000 hours at 45°C inlet air temperature, under worst conditions

- Tantalum capacitors are forbidden

- SMT ceramic capacitors with case size > 1206 are forbidden (size 1206 still allowed when installed far from PCB edge, and with a correct orientation that minimizes risks of cracks)

- Ceramics material for SMT capacitors must be X7R or better material (COG or NPo type should be used in critical portions of the design)

Only SMT inductors may be used. The use of through-hole inductors is disallowed.

# 12.4 Component De-Rating

For all inductors, capacitors and FETs, de-rating analysis should be based on at least 20% derating.

# 13 Revision History

| Version              | Date | Changes                                   |

|----------------------|------|-------------------------------------------|

| 0.7 12/2/2014 Initia |      | Initial version submitted for OCP review. |

|                      |      |                                           |

|                      |      |                                           |