Hawk Motherboard Design Specification

Revision 1.0

Author: Ampere Computing™

## Contents

| 1.     | Open Web Foundation (OWF) Contribution License Agreement  | 13 |

|--------|-----------------------------------------------------------|----|

| 2.     | Scope                                                     | 14 |

| 3.     | Overview                                                  | 14 |

| 4.     | Overview of the Hawk Board                                | 16 |

| 4.1.   | Block Diagram                                             | 16 |

| 4.2.   | Component Placement and Form Factor                       | 17 |

| 4.2.1. | I/O Connectors and Switches on the Rear                   | 19 |

| 4.2.2. | Hawk Board Power Connectors                               | 20 |

| 4.2.3. | Hawk Board Thermal Considerations                         | 20 |

| 4.3.   | CPU and Memory                                            | 21 |

| 4.3.1. | DDR4 Memory Controller Architecture                       | 23 |

| 4.3.2. | DDR4 CK, CKE, CS, and ODT Connections in Two Slot Systems | 24 |

| 4.4.   | DIMM Memory Population Sequence                           | 25 |

| 4.5.   | DIMM Sockets                                              | 25 |

| 4.6.   | Network Interfaces                                        | 25 |

| 4.6.1. | Dedicated Network Ports                                   | 25 |

| 4.6.2. | Management Ethernet                                       | 25 |

| 4.6.3. | Add-on NIC Cards                                          | 25 |

| 4.7.   | PCI Express (PCIe) Interfaces                             | 26 |

| 4.7.1. | PCIe Reference Clock (Differential)                       | 26 |

| 4.7.2. | Miscellaneous PCIe Signals                                | 28 |

| 4.8.   | PCIe x16 Slot/Riser Card                                  | 30 |

| 4.9.   | SATA Connectivity                                         | 33 |

| 4.10.  | M.2 Connectivity                                          | 34 |

| 4.11.  | USB 2.0 Connectivity                                      | 34 |

| 4.12.  | UART Connectivity                                         | 35 |

| 4.12.1 | L. UART Channel Selection                                 | 36 |

| 4.12.2 | 2. UART Summary and Schematics                            | 37 |

| 4.13.  | Fan Connectivity                                          | 38 |

| 4.14.  | VGA Connector                                             |    |

|--------|-----------------------------------------------------------|----|

| 4.15.  | SPI Interface                                             |    |

| 4.16.  | I2C (IIC) Buses                                           | 40 |

| 4.17.  | GPIO Signals                                              | 42 |

| 4.18.  | JTAG Debug Interfaces                                     | 42 |

| 4.19.  | Serial Console                                            | 44 |

| 4.20.  | Serial Trace Debug Interface                              | 44 |

| 5.     | PCB Stack-up Guidelines                                   | 44 |

| 6.     | Bootstrap Configuration                                   | 50 |

| 6.1.   | Bootstrap EEPROM Reset                                    | 50 |

| 6.1.1. | Bootstrap EEPROM Software Reset                           | 50 |

| 6.1.2. | Software Requirements for Bootstrap EEPROM Software Reset | 50 |

| 7.     | Secure Boot Support                                       | 50 |

| 8.     | Clocking                                                  | 51 |

| 8.1.   | System Reference Clocks (Differential)                    | 51 |

| 8.2.   | Miscellaneous Reference Clocks (Single-ended)             | 51 |

| 9.     | Power Supply and Reset                                    | 52 |

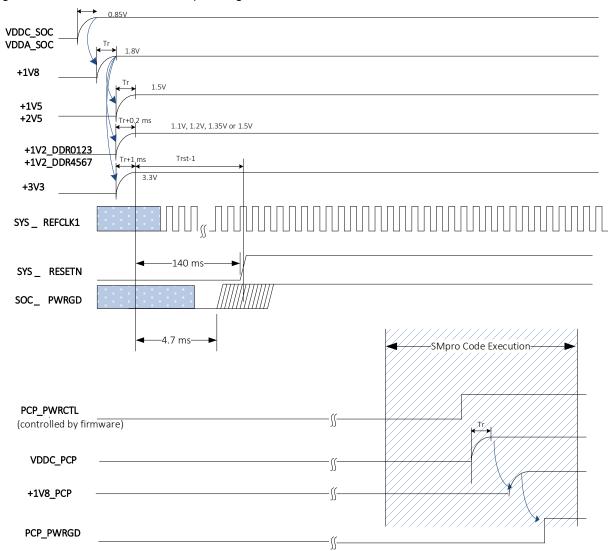

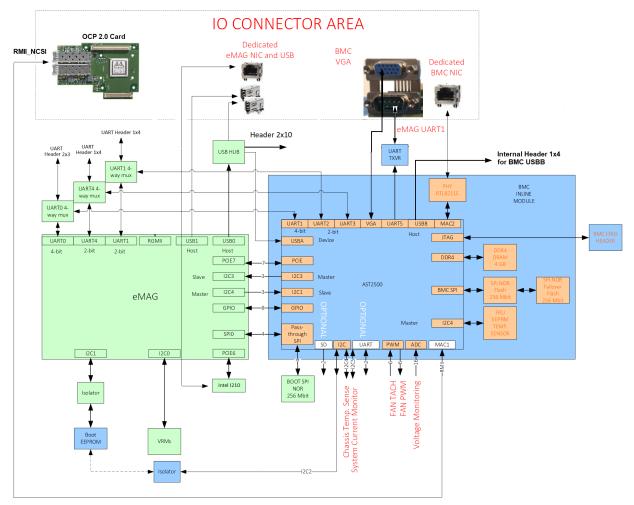

| 9.1.   | eMAG Power Domains and Power Sequencing                   | 52 |

| 9.2.   | eMAG CPU Power Sequencing on the Hawk Board               | 53 |

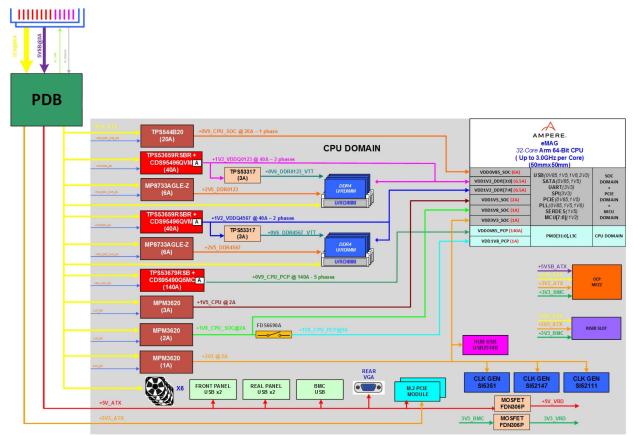

| 9.3.   | System Power Chart                                        | 54 |

| 9.4.   | Power Regulator Capabilities                              | 55 |

| 9.5.   | System Power Supply Requirements                          | 55 |

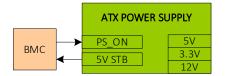

| 9.6.   | Power Supply Block Diagrams                               | 55 |

| 9.6.1. | Power Supply for the BMC Subsystem                        | 55 |

| 9.6.2. | Power Supply for the SoC and PCP Domains                  | 56 |

| 9.7.   | eMAG System Reset Schematics                              | 56 |

| 10.    | Baseboard Management Controller (BMC)                     | 57 |

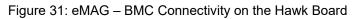

| 10.1.  | BMC Block Diagram                                         | 58 |

| 10.2.  | BMC GPIO Signals                                          | 60 |

| 10.3.  | BMC – eMAG I/O Isolation                                  | 63 |

| 10.3.1 | 1. UARTO/UART1/UART4 Isolation                            | 63 |

| 10.3.2.  | I2C Bus (SCL, SDA)                           | 63 |

|----------|----------------------------------------------|----|

| 10.3.3.  | Bootstrap EEPROM                             | 63 |

| 10.3.4.  | GPIO Isolation                               | 64 |

| 10.3.5.  | USB and PCIe                                 | 64 |

| 10.3.6.  | SPI                                          | 64 |

| 10.3.7.  | BMC Fan Control                              | 64 |

| 10.3.8.  | BMC Voltage Monitoring                       | 64 |

| 10.4.    | Standard BMC Features                        | 65 |

| 10.4.1.  | Platform Support                             | 65 |

| 10.4.2.  | Networking                                   | 66 |

| 10.4.3.  | Access Control                               | 66 |

| 10.4.4.  | Security Features                            | 67 |

| 10.4.5.  | Firmware Update and Configuration Management | 68 |

| 10.4.6.  | Date and Time Management                     | 68 |

| 10.4.7.  | SDR and Logging                              | 69 |

| 10.4.8.  | FRU Support                                  | 69 |

| 10.4.9.  | Hardware Health Detection and Monitoring     | 70 |

| 10.4.10. | Chassis Control                              | 70 |

| 10.4.11. | Alerts and Notifications                     | 71 |

| 10.4.12. | WebUI                                        | 71 |

| 10.5.    | eMAG – BMC Connectivity and Communication    | 72 |

| 10.5.1.  | eMAG to BMC Hardware Connectivity            | 72 |

| 10.5.2.  | GPIO Table                                   | 74 |

| 10.6.    | Other Design Considerations                  | 75 |

| 10.7.    | eMAG to BMC Communication                    | 77 |

| 10.7.1.  | SMBus                                        | 77 |

| 10.7.2.  | Out-of-band Communication                    | 77 |

| 10.7.3.  | In-band Communication                        | 77 |

| 10.8.    | Detailed Software Functions                  | 78 |

| 10.8.1.  | Host-to-BMC Communications                   | 78 |

| 10.8.2.  | BMC-to-eMAG Communications                   | 78 |

| 10.8.3. Error Detection and Reporting                  | 78  |

|--------------------------------------------------------|-----|

| 10.8.4. Fail Safe                                      | 79  |

| 10.9. eMAG Register Map                                | 81  |

| 10.9.1. Logical Sensor Definitions                     | 81  |

| 10.9.2. Extended LM75 Format                           | 82  |

| 10.9.3. I2C Register Map Definitions                   | 82  |

| 10.9.4. Accessing the Register Map from Linux          | 102 |

| 11. Pinouts for Selected Connectors and LED Indicators | 103 |

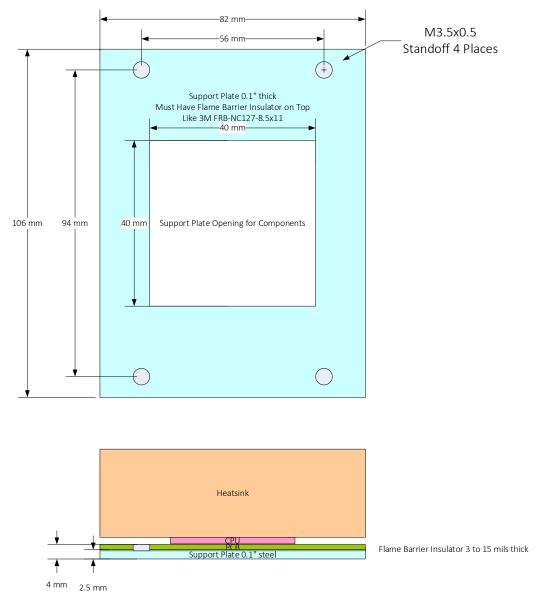

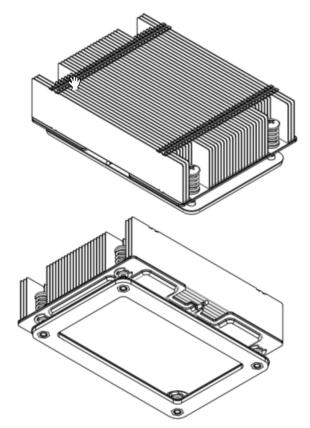

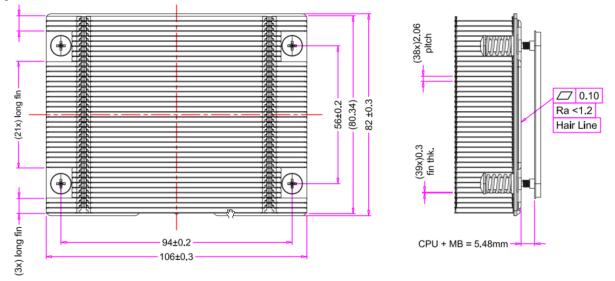

| 11.1. Heat Sink Footprint                              | 116 |

| 11.2. Standard LGA2011 Heat Sink Modifications         | 116 |

| 11.3. Approved Heat Sink Vendors and Part Numbers      | 117 |

| 11.4. CPU Thermal Sensors                              | 117 |

| 11.5. BMC Thermal Sensors                              | 117 |

| 11.6. Inlet Temperature                                | 117 |

| 11.7. Fan Redundancy                                   | 117 |

| 11.8. System Airflow or Volumetric Flow                | 117 |

| 11.9. Delta T                                          | 118 |

| 11.10. Thermal Margin                                  | 118 |

| 11.10.1. Thermal Kit Requirements                      |     |

| 11.11. System Fan                                      |     |

| 11.12. Air Duct                                        | 118 |

| 12. Installing the Hawk Board into a Chassis           | 118 |

| 13. Interfacing the Hawk Board with a Sled Interposer  | 119 |

| 13.1. Independent Loading Mechanisms (ILMs)            |     |

| 14. Board Power Supplies                               |     |

| 14.1. Input Voltages                                   |     |

| 14.1.1. 12V_ATX Input Voltage Level                    |     |

| 14.1.2. 5V_ATX Input Voltage Level                     |     |

| 14.1.3. 3V3_ATX Input Voltage Level                    | 122 |

| 14.2. CPU Voltage Regulators                           | 122 |

| 14.3. SoC Voltage Regulator Efficiency                 |     |

| 14.3.1 | SoC Core Voltage Regulator Configuration                                | 123 |

|--------|-------------------------------------------------------------------------|-----|

| 14.3.2 | SoC Multi-Layer Ceramic Capacitor (MLCC) Co-Layout                      | 123 |

| 14.4.  | DIMM Voltage Regulators                                                 | 123 |

| 14.4.1 | DIMM Maximum Power                                                      | 123 |

| 14.4.2 | DIMM Voltage Regulator Optimizations                                    | 123 |

| 14.4.3 | DIMM Voltage Regulator Efficiency                                       | 124 |

| 14.4.4 | DIMM Voltage Regulator Configuration                                    | 124 |

| 14.4.5 | DIMM Voltage Regulator Multi-Layer Ceramic Capacitor (MLCC) Co-Layout . | 124 |

| 14.5.  | Processor Complex (PCP) VRM                                             | 125 |

| 14.6.  | PCP VRM Efficiency                                                      | 125 |

| 14.7.  | PCP Core VRM Configuration                                              | 125 |

| 14.7.1 | PCP Multi-Layer Ceramic Capacitor (MLCC) Co-Layout                      | 126 |

| 14.8.  | VRM Design Guidelines                                                   | 126 |

| 14.9.  | Hard Drive Power                                                        | 127 |

| 14.10. | System VRM Efficiency                                                   | 127 |

| 14.11. | Power-on Conditions                                                     | 127 |

| 14.12. | High Power Use Cases                                                    | 127 |

| 15. /  | Acronyms and Abbreviations                                              | 127 |

| 16.    | Document Revision History                                               | 129 |

# Figures

| Figure 1: Hawk Board with OCP 2.0 Mezzanine Card                            | 15 |

|-----------------------------------------------------------------------------|----|

| Figure 2: Hawk Board Block Diagram                                          | 16 |

| Figure 3: Hawk Board Form Factor                                            | 17 |

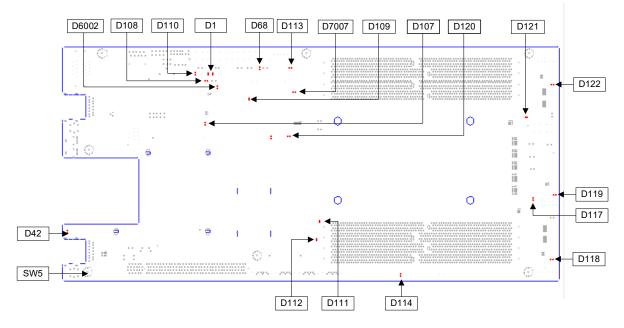

| Figure 4: Hawk Board Top-view                                               | 18 |

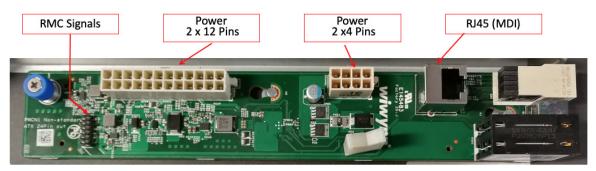

| Figure 5: I/O Connectors and Switches on the Rear Side of the Hawk Board    | 19 |

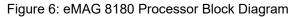

| Figure 6: eMAG 8180 Processor Block Diagram                                 | 21 |

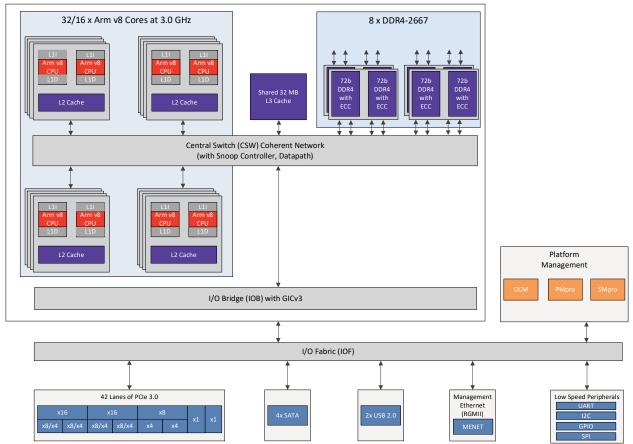

| Figure 7: Hawk DDR4 Functional Block Diagram                                | 23 |

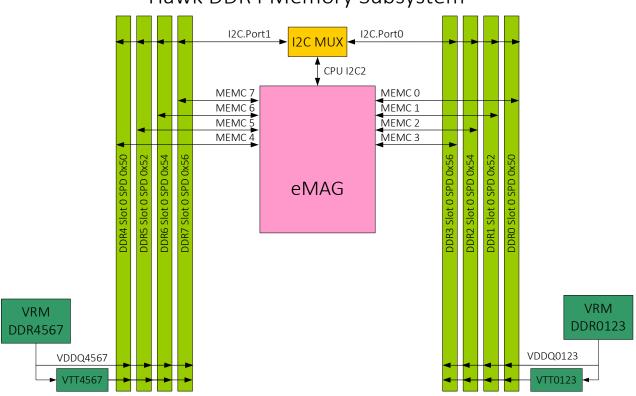

| Figure 8: DDR4 Memory Channel Connections to Slots on Hawk                  | 24 |

| Figure 9: Hawk PCIe Reference Clocks – Non Spread Spectrum                  | 26 |

| Figure 10: Hawk PCIe Reference Clocks – Spread Spectrum                     | 27 |

| Figure 11: I2C for PCIe Mux on Hawk                                         | 28 |

| Figure 12: PCIe Port 0 PERST# Connection Header                             | 29 |

| Figure 13: PCIe Riser Card on the Hawk Board                                |    |

| Figure 14: I2C to GPIO Expander Implementation on the Hawk Board            |    |

| Figure 15: USB Subsection Implementation on the Hawk Board                  | 34 |

| Figure 16: CPU UART[0,4] and BMC UART[1-3,5] Connectivity on the Hawk Board | 35 |

| Figure 17: 4-Way Mux/Demux for eMAG/BMC UARTs on the Hawk Board             | 35 |

| Figure 18: Hawk Board UART Schematics – 1                                   | 37 |

| Figure 19: Hawk Board UART Schematics – 2                                   |    |

| Figure 20: eMAG SPIO Boot Bus                                               |    |

| Figure 21: eMAG GPIO Signal Schematics                                      | 42 |

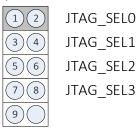

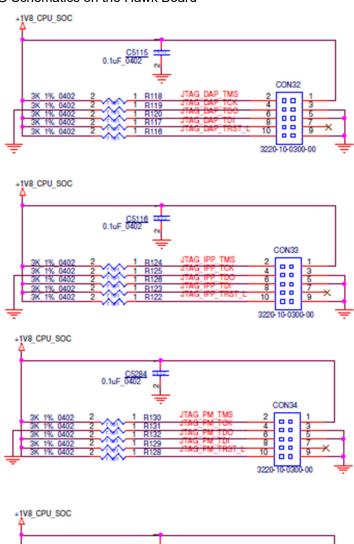

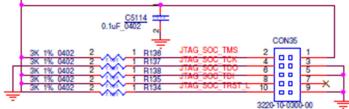

| Figure 22: Hawk JTAG Select Header (J2) Pinout                              | 43 |

| Figure 23: eMAG JTAG Schematics on the Hawk Board                           | 43 |

| Figure 24: Bootstrap EEPROM Software Reset Sequence                         | 50 |

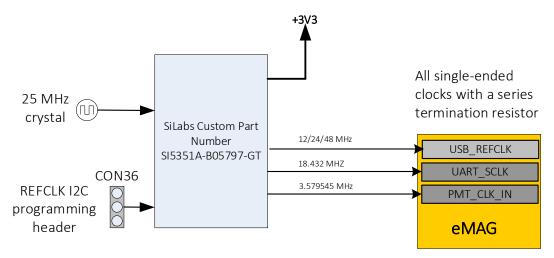

| Figure 25: Miscellaneous Reference Clocks on the Hawk Board                 | 51 |

| Figure 26: Hawk Board Power Sequencing                                      | 53 |

| Figure 27: Power Chart for a Typical Hawk Board-based System                | 54 |

| Figure 28: ATX PSON                                                         | 55 |

| Figure 29: Hawk Board SoC and PCP Domain Power Supplies                     | 56 |

| Figure 30: eMAG System Reset Schemes on the Hawk Board                  | 56  |

|-------------------------------------------------------------------------|-----|

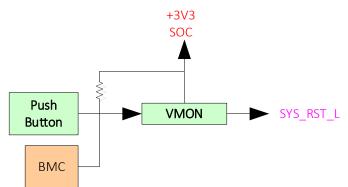

| Figure 31: eMAG – BMC Connectivity on the Hawk Board                    | 58  |

| Figure 32: Bootstrap EEPROM System Connectivity on the Hawk Board       | 63  |

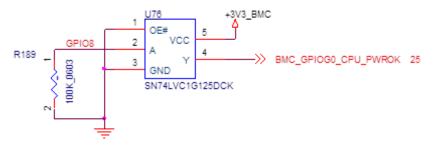

| Figure 33: CPU PWROK Isolation Circuit                                  | 64  |

| Figure 34: eMAG BMC Hardware Connectivity                               | 76  |

| Figure 35: Fail-Safe Operation Sequence                                 | 80  |

| Figure 36: Hawk Motherboard LEDs Reference Designator                   | 112 |

| Figure 37: CPU Heat Sink Mounting Footprint for the Hawk Board          | 116 |

| Figure 38: Interposer Board from Wiwynn                                 | 119 |

| Figure 39: Hawk Motherboard Installed in the Wiwynn EP100 openEDGE Sled | 120 |

| Figure 40: Hawk Board Heat Sink Assembly                                | 121 |

| Figure 41: Hawk Board Heat Sink Dimensions                              |     |

# Tables

| Table 1: Hawk Motherboard Features                                            | 14 |

|-------------------------------------------------------------------------------|----|

| Table 2: Hawk Board Jumpers and Connectors                                    | 18 |

| Table 3: I/O Connector and Switches on the Rear                               | 20 |

| Table 4: Hawk Board DIMM Memory Population Sequence                           | 25 |

| Table 5: Hawk Board PCIe Modes, Lane Bifurcations, and Usage                  | 26 |

| Table 6: PCIe Connector Pin Descriptions for the Hawk Board                   |    |

| Table 7: UARTO 2x3 Header Pinout on the Hawk Board                            |    |

| Table 8: UART1, 2, 3, and 4 1x4 Header Pinout on the Hawk Board               |    |

| Table 9: UART Mode Control Signals on the Hawk Board                          |    |

| Table 10: Hawk Fan Connector Pinout                                           |    |

| Table 11: Standard Female DB9 VGA Connector Pinout                            |    |

| Table 12: SPI Devices on the Hawk Board                                       |    |

| Table 13: eMAG I2C Buses Available on the Hawk Board                          | 40 |

| Table 14: eMAG I2C Devices Available on the Hawk Board                        | 40 |

| Table 15: Hawk Board Serial Port DB9 Female Pin Connector Pinout              | 44 |

| Table 16: Serial Trace Connector Pinout on the Hawk Board                     | 44 |

| Table 17: Hawk Board PCB Stack-up                                             | 44 |

| Table 18: Motherboard PCB Impedance Control – 1                               | 46 |

| Table 19: Motherboard PCB Impedance Control – 2                               | 47 |

| Table 20: Motherboard PCB Impedance Control – 3                               | 48 |

| Table 21: eMAG Power Domains and Power Sequencing                             | 52 |

| Table 22: Hawk Board Power Regulator Margins                                  | 55 |

| Table 23: ATX Gold 650 W Power Supply Unit for Hawk (with HDD Storage or GPU) | 55 |

| Table 24: BMC Features Supported on the Hawk Board                            | 57 |

| Table 25: BMC GPIO Signals Used on the Hawk Board                             | 60 |

| Table 26: BMC ADC to Hawk Power Net Mapping and Scaling Factors               | 64 |

| Table 27: Platform Features Supported by the BMC                              | 65 |

| Table 28: Networking Features Supported by the Hawk Board                     | 66 |

| Table 29: Access Control Features Supported by the Hawk Board                 | 66 |

| Table 30: Security Features Supported by the Hawk Board                          | 67           |

|----------------------------------------------------------------------------------|--------------|

| Table 31: Firmware and Configuration Management Features Supported by the Hawk   | Board68      |

| Table 32: Date and Time Management Features Supported by the Hawk Board          | 68           |

| Table 33: SDR and Logging Features Supported by the Hawk Board                   | 69           |

| Table 34: FRU Support Features Provided on the Hawk Board                        | 69           |

| Table 35: Hardware Health Detection and Monitoring Features Supported by the Haw | /k Board .70 |

| Table 36: Chassis Control Features Supported by the Hawk Board                   | 70           |

| Table 37: Alerts and Notifications-related Features Supported by the Hawk Board  | 71           |

| Table 38: WebUI Features Supported by the Hawk Board                             | 71           |

| Table 39: GPIO Assignments                                                       | 74           |

| Table 40: Additional Alert Signals                                               | 76           |

| Table 41: Logical Sensor Definitions                                             | 81           |

| Table 42: System GUID                                                            | 82           |

| Table 43: Capability Registers                                                   | 83           |

| Table 44: Sensor Registers                                                       | 85           |

| Table 45: GPI Mask Registers                                                     | 88           |

| Table 46: GPI Source Registers                                                   | 89           |

| Table 47: Alert Behaviors                                                        | 90           |

| Table 48: GPI Status Registers                                                   | 91           |

| Table 49: PMD/CPU Error Registers                                                | 95           |

| Table 50: Memory Error Registers                                                 | 96           |

| Table 51: RAS Internal Error Registers                                           | 97           |

| Table 52: PCIe Error Registers                                                   | 98           |

| Table 53: SATA Error Registers                                                   | 99           |

| Table 54: ACPI State Registers                                                   | 100          |

| Table 55: CON47: USB 2.0 Header                                                  | 103          |

| Table 56: CON52: Front Panel Header                                              | 103          |

| Table 57: CON68, CON70, CON69: Fan Connector                                     | 104          |

| Table 58: CON67: RMC Signal Header (openEDGE)                                    | 104          |

| Table 59: CON40: 8-Pin CPU Power Connector                                       | 104          |

| Table 60: CON39: 24-Pin Main Power Connector                                     | 105          |

| Table 61: CON37: VGA and Serial Port DB9 Connector                    |     |

|-----------------------------------------------------------------------|-----|

| Table 62: CON50: BMC ATX PMBus Connector                              |     |

| Table 63: CON17 – Pins A1 to A82: Standard PCIe x16 Connector         |     |

| Table 64: CON17 – Pins B1 to B82: Standard PCIe x16 Connector         |     |

| Table 65: CON60: Chassis Intrusion Sensor Connector                   |     |

| Table 66: CON63: RMC MDI (openEDGE) Connector                         |     |

| Table 67: CON19: NVMe M.2 Connector                                   |     |

| Table 68: CON62: NVMe M.2 Connector                                   |     |

| Table 69: CON29: Serial Trace Probe Connector                         |     |

| Table 70: CON32: JTAG DAP (Debug Access Port) Interface               |     |

| Table 71: CON35: SoC JTAG Interface                                   |     |

| Table 72: CON33: Serial Trace Probe Connector                         |     |

| Table 73: CON34: PMpro JTAG Interface                                 |     |

| Table 74: D42: BMC Heartbeat LED                                      |     |

| Table 75: Designators for LEDs and Switches on the Hawk Board         |     |

| Table 76: Hawk Board Debug Ports                                      |     |

| Table 77: SW4: ID Switch / LED                                        |     |

| Table 78: SW5: Power Switch / LED                                     |     |

| Table 79: SW2: BMC Reset                                              |     |

| Table 80: PS ON Jumper                                                |     |

| Table 81: J4: PCIe Spread Spectrum Jumper                             |     |

| Table 82: J2: JTAG Select / Boundary Scan Option Select               |     |

| Table 83: J11: Linux Console                                          |     |

| Table 84: J12: ATF                                                    |     |

| Table 85: J13: SMpro                                                  |     |

| Table 86: Approved Vendor and Part Number List for Hawk CPU Heat Sink |     |

| Table 87: Recommended ICs for Generating SoC Voltage Rails            |     |

| Table 88: 0.9 V SoC Power Rail Capacitors                             |     |

| Table 89: DIMM Power Rail Capacitors                                  |     |

| Table 90: PCP VRM Power Rails                                         |     |

| Table 91: PCP Power Rail Capacitors                                   | 126 |

| Table 92: CPU and DIMM VR Power Stages | 126 |

|----------------------------------------|-----|

| Table 93: Acronyms and Abbreviations   | 127 |

| Table 94: Document Revision History    | 129 |

# 1. Open Web Foundation (OWF) Contribution License Agreement

Contributions to this Specification are made under the terms and conditions set forth in Open Web Foundation Contributor License Agreement ("OWF CLA 1.0") ("Contribution License") by:

#### **Ampere Computing**

4655 Great America Parkway, Santa Clara, CA 95054 Phone: (669) 770-3700 https://www.amperecomputing.com

Usage of this Specification is governed by the terms and conditions set forth in the Open Web Foundation Final Specification Agreement ("OWFa 1.0").

**Note**: The following clarifications, which distinguish technology licensed in the Contribution License and/or Specification License from those technologies merely referenced (but not licensed), were accepted by the Incubation Committee of the OCP:

NOTWITHSTANDING THE FOREGOING LICENSES. THIS SPECIFICATION IS PROVIDED BY OCP "AS IS" AND OCP EXPRESSLY DISCLAIMS ANY WARRANTIES (EXPRESS, IMPLIED, OR OTHERWISE), INCLUDING IMPLIED WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR A PARTICULAR PURPOSE, OR TITLE, RELATED TO THE SPECIFICATION. NOTICE IS HEREBY GIVEN, THAT OTHER RIGHTS NOT GRANTED AS SET FORTH ABOVE, INCLUDING WITHOUT LIMITATION, RIGHTS OF THIRD PARTIES WHO DID NOT EXECUTE THE ABOVE LICENSES, MAY BE IMPLICATED BY THE IMPLEMENTATION OF OR COMPLIANCE WITH THIS SPECIFICATION. OCP IS NOT RESPONSIBLE FOR IDENTIFYING RIGHTS FOR WHICH A LICENSE MAY BE REQUIRED IN ORDER TO IMPLEMENT THIS SPECIFICATION. THE ENTIRE RISK AS TO IMPLEMENTING OR OTHERWISE USING THE SPECIFICATION IS ASSUMED BY YOU. IN NO EVENT WILL OCP BE LIABLE TO YOU FOR ANY MONETARY DAMAGES WITH RESPECT TO ANY CLAIMS RELATED TO. OR ARISING OUT OF YOUR USE OF THIS SPECIFICATION. INCLUDING BUT NOT LIMITED TO ANY LIABILITY FOR LOST PROFITS OR ANY CONSEQUENTIAL, INCIDENTAL, INDIRECT, SPECIAL OR PUNITIVE DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND EVEN IF OCP HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Date: April 22, 2020

# 2. Scope

This document provides the technical specification for the Ampere Computing<sup>™</sup> Hawk motherboard powered by Ampere's Arm<sup>®</sup> 64-bit eMAG<sup>™</sup> 8180 multi-core processor. The Hawk board is targeted for high density telco, edge, and data center deployments. The motherboard is compatible with half-width openEDGE servers.

# 3. Overview

The Ampere Hawk board is an eMAG 8180-based 1U half-width single socket server board targeted for high-density telco, edge, and datacenter deployments. The board is designed to fit into the OCP openEDGE chassis.

This flexible and efficient server platform enables diverse applications requiring low latency and high data-processing capabilities for edge computing.

With a powerful and efficient 32-core eMAG 8180 processor, up to 8 DIMM slots and 4 native SATA ports that can be used to connect SATA-compliant mass storage devices with a maximum transfer rate of 6 Gb/s, this extremely flexible platform offers tremendous total cost of ownership (TCO) value with the best performance per dollar and best performance per watt to customers using high volume servers, and for customers using servers for edge, storage, and web server applications.

Two direct-connect M.2 NVMe ports on the board provide ultra-fast reads/writes while loading the OS from an NVMe drive, and reduces costs by eliminating PCIe adapters.

For network connectivity, the Hawk board provides an integrated 1 GbE port and an OCP Mezzanine card connector supporting 10/40/100 GbE NIC.

Table 1 lists the features of the Hawk board.

| ITEM                    | DESCRIPTION                                                                                                                                                                                              |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Form Factor             | Designed to fit into the OCP openEDGE Chassis                                                                                                                                                            |

| Number of<br>Processors | 1 x Ampere eMAG 8180 CPU with 32 x ARMv8 64-bit CPU cores at 3.30 GHz with Turbo                                                                                                                         |

| Memory                  | Up to 256 GB in 8x slots using 32 GB DIMMs; 2666 MHz DDR4 RDIMM (1DPC)                                                                                                                                   |

| Expansion Slots         | 1 x PCle x16 (PCle 2)                                                                                                                                                                                    |

| Rear Panel I/O Ports    | <ul> <li>1 x Power Control Button</li> <li>1 x UID Button</li> <li>1 x RJ45 (BMC)</li> <li>1 x RJ45 for 1 GbE NIC</li> <li>1 x VGA (DB15)</li> <li>1 x Serial Port (DB9)</li> <li>2 x USB 2.0</li> </ul> |

Table 1: Hawk Motherboard Features

| ITEM                          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Internal I/O<br>Connectors    | <ul> <li>4 x SATA 6.0 Gb/s Connectors</li> <li>2 x NVMe M.2 (PCIe 4, 5)</li> <li>1 x OCP Mezzanine Card 2.0 (Conn. A and Conn. B) supporting<br/>10/40/100 GbE NIC</li> <li>2 x PCIe (PCIe 0, 1)</li> <li>3 x 6-Pin Hot Plug Fan Connector supporting single/dual rotor fans</li> <li>1 x 24-pin Multi-Input ATX Power Connector</li> <li>1 x 8-pin 12 V Power Connector</li> </ul> |  |  |  |  |

| Network Interfaces            | <ul> <li>1 x RJ45 for BMC</li> <li>1 x RJ45 for 1 GbE</li> </ul>                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| System<br>Management          | IPMI 2.0, iKVM                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Installed Operating<br>System | CentOS 7.x                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| UEFI                          | AMI Aptio <sup>®</sup> V                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| ВМС                           | AMI MegaRAC <sup>®</sup>                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Others                        | GCC and LLVM tool chain bundled with latest eMAG software release                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| Dimensions                    | 22.10 mm (H) × 165.1 mm (W) × 351.79 mm (D) / 0.87" (H) × 6.5" (W) × 13.85" (D)                                                                                                                                                                                                                                                                                                     |  |  |  |  |

*Figure 1* shows the Hawk board with the OCP 2.0 Mezzanine Card.

Figure 1: Hawk Board with OCP 2.0 Mezzanine Card

# 4. Overview of the Hawk Board

## 4.1. Block Diagram

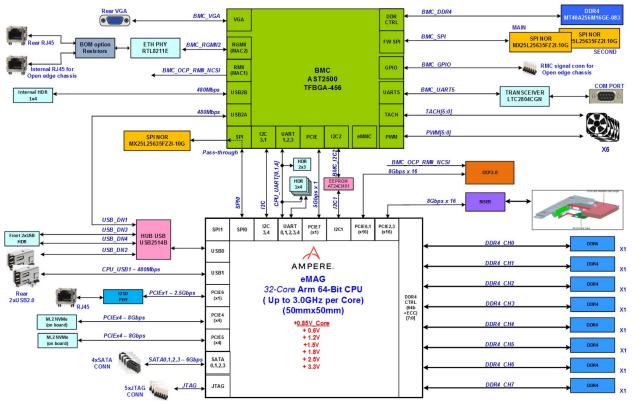

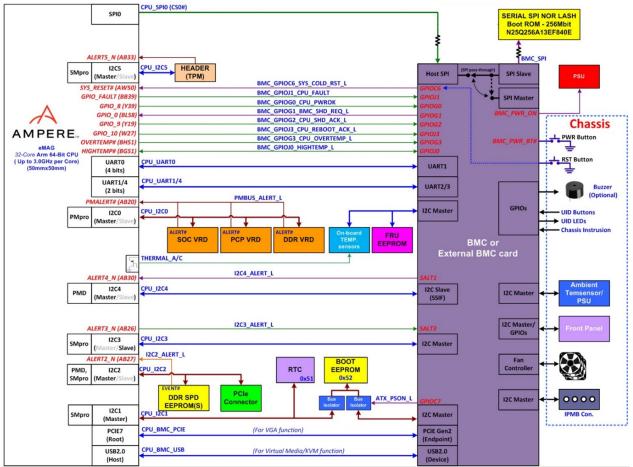

Figure 2 illustrates the Hawk board's block diagram.

Figure 2: Hawk Board Block Diagram

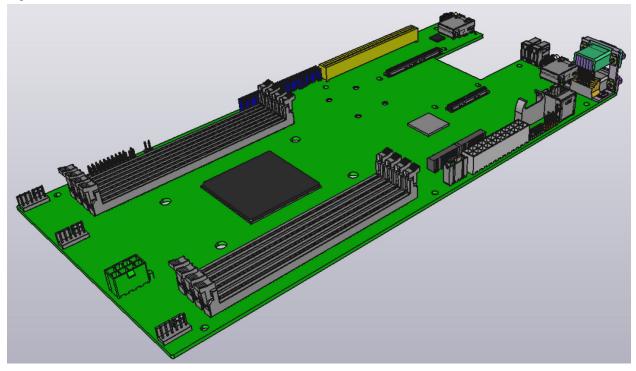

# 4.2. Component Placement and Form Factor

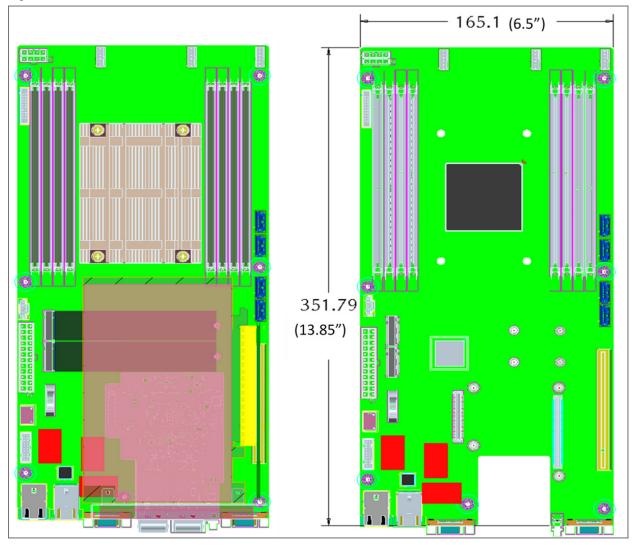

The Hawk board is designed as a  $6.5^{\circ} \times 13.85^{\circ}$  motherboard to fit into a chassis conforming to the openEDGE Chassis Specification. *Figure* 3 illustrates the Hawk board dimensions and form factor.

Figure 3: Hawk Board Form Factor

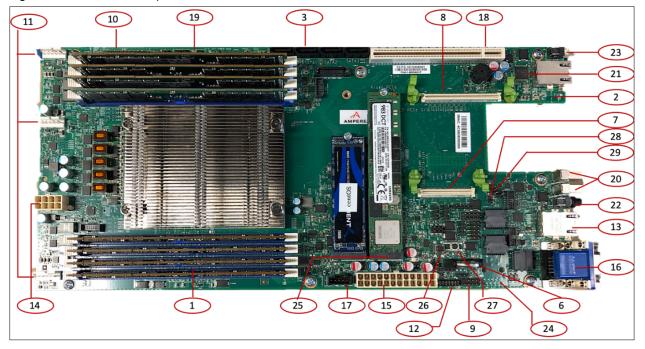

*Figure 4* shows the top-view of the Hawk board.

Figure 4: Hawk Board Top-view

| Table 2 lists the in | umpore and | aannaatara | on the Hould | heard shown in | Eiguro A  |

|----------------------|------------|------------|--------------|----------------|-----------|

| Table 2 lists the ju | umpers anu | connectors |              | Doard Shown II | riguie 4. |

| Table 2: Hawk Board Jumpers and Connectors |                                       |   |  |  |  |

|--------------------------------------------|---------------------------------------|---|--|--|--|

| #                                          | JUMPERS AND CONNECTORS                |   |  |  |  |

| 1                                          | CON2, CON4, CON6, CON8, CON10, CON12, | D |  |  |  |

| #  | JUMPERS AND CONNECTORS                                | ITEM                                                   |

|----|-------------------------------------------------------|--------------------------------------------------------|

| 1  | CON2, CON4, CON6, CON8, CON10, CON12,<br>CON14, CON16 | DDR4-RDIMM (8)                                         |

| 2  | D42                                                   | BMC (Baseboard Management<br>Controller) heartbeat LED |

| 3  | CON21, CON22, CON23, CON54                            | SATA connector (4)                                     |

| 6  | BT1                                                   | Coin-Battery                                           |

| 7  | CON65                                                 | OCP Mezzanine 2.0 connector B                          |

| 8  | CON41                                                 | OCP Mezzanine 2.0 connector A                          |

| 9  | CON47                                                 | USB 2.0 header (front USB port)                        |

| 10 | CON52                                                 | Front panel IO header                                  |

| 11 | CON68, CON69, CON70                                   | Fan connector                                          |

| 12 | CON67                                                 | RMC signal header (OpenEdge)                           |

| 13 | CON38                                                 | RJ45 management port                                   |

| 14 | CON40                                                 | 8-pin CPU power connector                              |

| 15 | CON39                                                 | 24-pin main power Connector                            |

| #  | JUMPERS AND CONNECTORS | ITEM                                            |

|----|------------------------|-------------------------------------------------|

| 16 | CON37                  | VGA and serial port DB9 connector               |

| 17 | CON50                  | BMC ATX PMBus connector                         |

| 18 | CON17                  | Standard PCIe x16 connector                     |

| 19 | CON60                  | Intrusion sensor connector                      |

| 20 | CON71, CON72           | USB 2.0                                         |

| 21 | U5002                  | Intel Ethernet controller I210-AT and RJ45 Port |

| 22 | SW4                    | ID Switch/LED                                   |

| 23 | SW5                    | Power Switch/LED                                |

| 24 | CON63 <sup>1</sup>     | RMC MDI (OpenEdge)                              |

| 25 | CON19, CON62           | NVMe M.2 connector                              |

| 26 | SW2                    | BMC_RST# button                                 |

| 27 | SW1                    | System reset button                             |

| 28 | J1                     | Power supply on                                 |

| 29 | J4                     | PCle spread spectrum                            |

### 4.2.1. I/O Connectors and Switches on the Rear

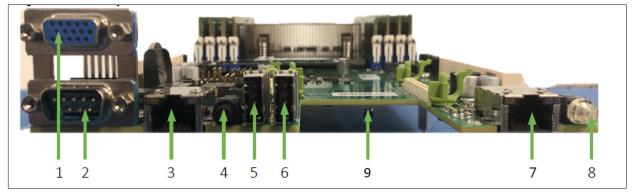

*Figure 5* shows the connectors and switches on the rear side of the Hawk board and *Table 3* provides the list of these connectors and switches.

Figure 5: I/O Connectors and Switches on the Rear Side of the Hawk Board

<sup>&</sup>lt;sup>1</sup> CON63 may not be populated by default. For more information, contact technical support at https://connect.amperecomputing.com/help

| ITEM | DESCRIPTION                     | ITEM | DESCRIPTION                 |

|------|---------------------------------|------|-----------------------------|

| 1    | VGA Port                        | 2    | DB9 Connector (BMC Console) |

| 3    | RJ45 Management Port            | 4    | ID Switch / LED             |

| 5    | USB 2.0 (CPU)                   | 6    | USB 2.0 (USB Hub)           |

| 7    | Intel I210 GbE (System Console) | 8    | Power Switch / LED          |

| 9    | OCP 2.0 Mezzanine LAN Card      | -    | -                           |

Table 3: I/O Connector and Switches on the Rear

### 4.2.2. Hawk Board Power Connectors

The Hawk board has the following power connectors populated on-board:

- Baseboard main power connector: 24-pin Molex 44472 family equivalent

- Processor power connector: 8-pin Molex 44472 family equivalent

There are two power domains from the ATX power connector:

- ATX domain includes +12V\_ATX, +5V\_ATX and +3V3\_ATX

- Standby domain includes +5VSB\_ATX

The following are the power connections on the Hawk board:

- All +12V\_ATX power pins are connected into a single 12V\_ATX plane on the Hawk board

- PCIe connectors are powered by +12V\_ATX and +3V3\_ATX

- +5V\_ATX is used for VRM regulators and USB VBUS

- +12V\_ATX is used for VRM and CPU's power regulators

- +5VSB\_ATX is used for BMC's power regulators

#### 4.2.3. Hawk Board Thermal Considerations

The Hawk board requires active air flow for cooling the CPU and memory modules. It is provisioned to support 6 system fans (each operating at 12 V). BMC controls the system fan speeds via PWM, without which, the fans will run at full speed.

Hawk uses a customized LGA2011 socket heat sink, with screws and springs that are modified for use with a soldered eMAG CPU with a backplate. See section *11.3* for a list of supported heat sinks.

The Hawk board provides multiple temperature sensors and thermal measurement test points as listed below:

- On-die temperature sensors for the eMAG CPU

- DIMM module temperature sensors

- Motherboard temperature sensors

## 4.3. CPU and Memory

The Hawk board is powered by the Ampere Computing eMAG 8180 64-bit, custom designed, multi-core processor targeting today's cloud workloads and future data center requirements by providing a large number of high-performance cores, high-memory bandwidth and capacity, general purpose high-bandwidth I/O, and a high level of integration—all within an efficient power envelope.

Figure 6 shows the eMAG processor block diagram.

#### Processor Subsystem

- Thirty-two eMAG processor cores operating at up to 3.30 GHz with Turbo

- Arm<sup>®</sup>v8 compliant 64-bit processor cores

- 32 KB L1 data cache, 32 KB L1 instruction cache per core

- Floating Point and SIMD Unit per core

- Shared 256 KB L2 cache per each pair of cores

- ECC protection on caches

- Shared 32 MB L3 cache

- Arm<sup>®</sup> Generic Interrupt Controller (GICv3)

- Four DDR4 memory controllers with ECC (72-bit)

- IO virtualization (SMMUv2)

- Enterprise server-class RAS

- End-to-end data poisoning

- Error containment and isolation

- Background L3 and DRAM scrubbing

#### Connectivity

- 42 lanes of PCIe Gen3, with 8 controllers:

- x16 or two x8/x4

- x16 or two x8/x4

- x8 or two x4

- Two x1

- 4 x SATA Gen3 ports

- 2 x USB 2.0 ports

#### **Other Interfaces**

- Six I2C ports

- Five UARTs

- GPIOs

- Two SPI

- JTAG / Trace

#### Memory Subsystem

- Shared 32 MB L3 cache

- Eight DDR4-2667 channels

- ECC, Symbol-based ECC, and DDR4 RAS features

- Up to 16 DIMMs and 1 TB/socket

- Follows the updated JEDEC DDR4 specification with 288-pin DIMM socket

- Supports DDR4 protocol (1.2 V) at up to DDR4-2667 speed grade

- 72-bit DRAM interface (64 data bits and 8 ECC bits)

Hawk supports up to 8 x 32 GB 2667 MT DDR4 RDIMM at 1 DIMM per Channel (1DPC) configuration.

#### Functionality

- ARM Server Base System Architecture (SBSA) Level 3

- ARM Server Base Boot Requirements Compliant

- Advance Power Management

- Dynamic estimation, Turbo, Voltage drop mitigation

- Two dedicated 32-bit Cortex-M3 processor (with 128 KB I/D RAM and debug port), PMpro and SMpro for power and system management, respectively.

### 4.3.1. DDR4 Memory Controller Architecture

Figure 7: Hawk DDR4 Functional Block Diagram

# Hawk DDR4 Memory Subsystem

As shown in *Figure 7*, Hawk DDR4 memory subsystem comprises of 8 DDR4 memory channels each supporting a single 288-pin DDR4 DIMM socket. Total system capacity is 8 DDR4 DIMM slots with up to 256 GB of DDR4 memory using 32 GB memory modules.

Memory channels have similar functional connectivity to corresponding DIMM slots; each side has its own VTT regulator for eight DIMM slots.

Memory channels on the right and left side of eMAG have separate power planes on the package. This plane separation is also provided on the board, so that left side DIMMs and controller pins are powered from one VRM, and right side DIMMs and controller pins from another VRM.

DIMM slot I2C bus is connected to dedicated eMAG I2C2 bus through I2C bus mux.

4.3.2. DDR4 CK, CKE, CS, and ODT Connections in Two Slot Systems

On Hawk, only one DDR slot is implemented for each memory channel. Unused DIMM1 signals (CKE2, CKE3, CS4, CS5, CS6, CS7, ODT2, ODT3, CLK2\_N, CLK2\_P, CLK3\_N, CLK3\_P) are left unconnected as shown in *Figure 8*.

Figure 8: DDR4 Memory Channel Connections to Slots on Hawk

## 4.4. DIMM Memory Population Sequence

Hawk supports up to eight memory channels. It also supports six, four, and two memory controller configurations, but only as per the configuration options listed in *Table 4*. Each channel provides DDR connections for one DIMM memory module.

| CONN     | 2            | 4            | 6            | 8            | 10           | 12           | 14           | 16           |

|----------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|

| 2 RDIMM  | $\checkmark$ |              |              |              | $\checkmark$ |              |              |              |

| 4 RDIMMs | $\checkmark$ | $\checkmark$ |              |              | $\checkmark$ | $\checkmark$ |              |              |

| 6 RDIMMs | $\checkmark$ | $\checkmark$ | $\checkmark$ |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |              |

| 8 RDIMMs | $\checkmark$ |

Table 4: Hawk Board DIMM Memory Population Sequence

## 4.5. DIMM Sockets

The motherboard has 8 DIMM sockets and each slot requires a 15  $\mu$ -inch gold contact for the DDR4 SMT DIMM socket. This socket incorporates a blue housing with a white/nature latch for the DIMM in DDR channel. The vendor must announce if the color selection will increase the cost of the DIMM socket.

## 4.6. Network Interfaces

### 4.6.1. Dedicated Network Ports

The Hawk board provides two 10/100/1000 Ethernet ports accessible in the I/O connector area:

- Dedicated 10/100/1000 Ethernet port (through an onboard Intel<sup>®</sup> I210 Ethernet Controller)

- Dedicated BMC Management 10/100/1000 Ethernet port

BMC implements BMC Management 10/100/1000 Ethernet port using MAC2 RGMII and PHY. PHY MDIO Address is set to 0x1.

### 4.6.2. Management Ethernet

The Hawk board supports two options of management network interfaces for the BMC connection.

- 10/100/1000 MDI connected to RJ45 from Realtek RTL8211E driven by BMC through RGMII

- 10/100 NCSI connected from OCP 2.0 Mezzanine NIC driven by BMC through RMII

### 4.6.3. Add-on NIC Cards

Additional add-on NIC cards can be enabled either through the onboard PCIe expansion slot (x16) or through the OCP 2.0 connector.

## 4.7. PCI Express (PCIe) Interfaces

The Hawk board provides one x16 PCIe connector and one OCP 2.0 Mezzanine Card connector (with support for x16 lanes). All Hawk PCIe interfaces support Gen1, Gen2, and Gen3 data transfer speeds.

Note: There is no PCIe hot-swap circuit implemented on the Hawk board.

Table 5 lists the PCIe modes, lane bifurcations and usage of the PCIe ports on the Hawk board.

| Hawk PCIe PORT | BIFURCATION | LANES | MODE                   | SYSTEM USAGE           |

|----------------|-------------|-------|------------------------|------------------------|

| 0/1            | x8x8        | x16   | Root Complex           | OCP 2.0 Mezzanine Card |

| 2/3            | x8x8        | x16   | Root Complex, Endpoint | GPU/NIC                |

| 4/5            | x4x4        | x8    | Root Complex, Endpoint | Storage                |

| 6              | -           | x1    | Root Complex           | On Board NIC           |

| 7              | -           | x1    | Root Complex           | BMC                    |

Table 5: Hawk Board PCIe Modes, Lane Bifurcations, and Usage

### 4.7.1. PCIe Reference Clock (Differential)

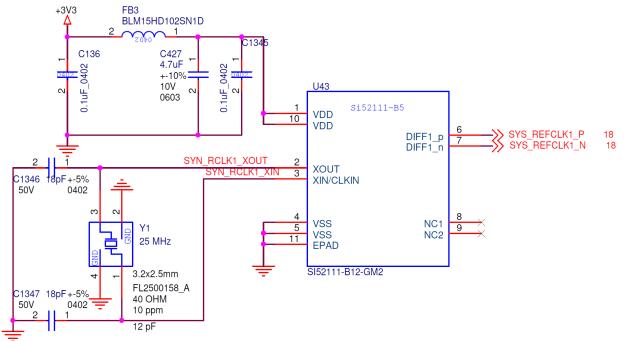

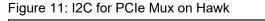

PCIe reference clock for any eMAG PCIe port can be sourced either from the non-spread spectrum SYS\_REFCLK1 (see *Figure 9*) or from spread spectrum capable SYS\_REFCLK2 (see *Figure 10*).

Figure 9: Hawk PCIe Reference Clocks - Non Spread Spectrum

### Figure 10: Hawk PCIe Reference Clocks – Spread Spectrum

eMAG takes two differential clocks (both of which are PCIe Gen4 compliant) as inputs. SYS\_REFCLK1 pair is non-spread spectrum, while SYS\_REFCLK2 is spread spectrum. Internally, any SerDes can be connected to either of the clock inputs, giving the system designer flexibility on supporting a mix of spread spectrum and non-spread spectrum ports.

The Hawk board implements differential system reference clocks using SiLabs PCIe Gen4 compliant clock generators Si52111-B5 (non-spread spectrum) and Si52147 (spread spectrum). All PCIe connectors and BMC derive their PCIe clock from a spread spectrum capable generator. The board implements a jumper to enable/disable spread spectrum clocking to test different modes as listed below.

Jumper J4 is used to enable spread spectrum for SYS\_REFCLK2 and for reference clocks to PCIe expansion slots. It is disabled by default. Insert the J4 cap (jumper on) to enable spread spectrum.

Hawk PCIe reference clock architecture allows testing the following modes defined in the PCI Express Base Specification Revision 3.1:

- PCIe Ports 0-7 as Root Complex with Common Clock Architecture.

- PCIe Ports 0/2/4 as Endpoint with Common Clock Architecture if Host and Endpoint ports are connected with PCIe cable adapter on the same board.

- PCIe Ports 0-6 as Root Complex/Endpoint with Separate Refclk No SSC (SRNS) architecture.

- PCIe Ports 0-6 as Root Complex/Endpoint with Separate Refclk with Independent SSC (SRIS) architecture.

- Separate clock architectures SRNS and SRIS are supported using two eMAG system reference clocks (SYS\_REFCLK1 and SYS\_REFCLK2). Each PCIe port inside eMAG can be connected to one of two differential system reference clocks. If one port is connected to SYS\_REFCLK1 and

another to SYS\_REFCLK2, separate clock architecture is enabled. Enabling SSC on SYS\_REFCLK2 sets SRIS mode, while disabling it sets SRNS mode.

• PCIe Port 7 is connected to BMC module, which is based on AST2500 and supports only PCIe Gen2, and is compliant with *PCI Express Base Specification Revision 2.0*.

### 4.7.2. Miscellaneous PCIe Signals

The Hawk board provides special provisions for miscellaneous PCIe signals: PCIe reference clocks, I2C, WAKE#, PRESENT\_DETECT, PERST#. These provisions allow the board to be configured for Root Complex or Endpoint on Ports 0/1, 2/3, 4/5 as well as common and separate clock architecture (SRNS and SRIS).

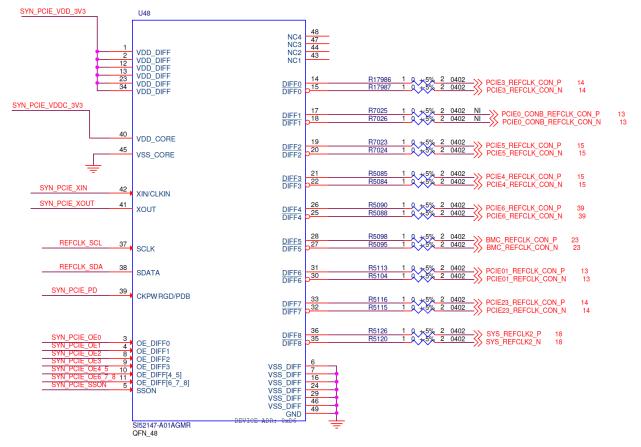

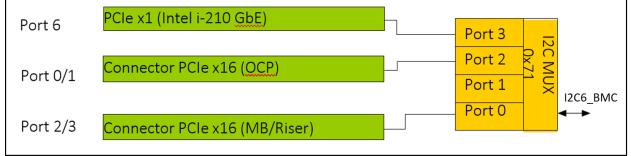

#### 4.7.2.1.I2C for PCIe Connectors

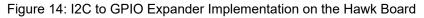

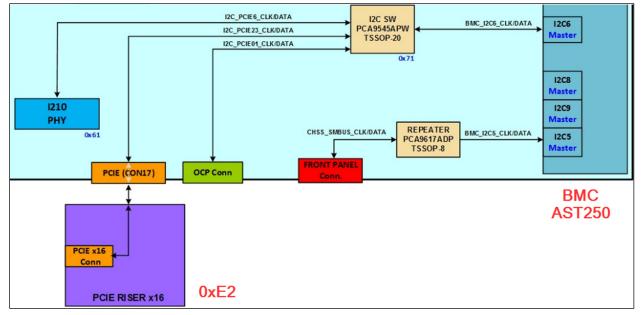

Hawk implements an I2C mux to provide access from eMAG I2C2 bus to each of the four PCIe vertical connectors, as shown in *Figure 11*.

#### 4.7.2.2.PCle Wake#

Hawk connects Wake# signal from PCIe slots to interrupt signal of corresponding port of I2C mux at address 0x71 on CPU I2C6\_BMC bus. If Wake# is asserted, interrupt will be propagated by the mux to I2C6\_ALERT\_L signal. eMAG must poll I2C6 mux registers to find out which port had the interrupt asserted.

#### 4.7.2.3.PCIe Present Detect

Hawk connects Present Detect signal from each of four PCIe connectors to GPI pin. eMAG firmware can detect board presence by checking status of GPI pins.

### 4.7.2.4.PCIe PERST#

In Hawk form-factor, all PCIe ports are set as Root Complex. By default, output RC\_PERST# signal from eMAG port is connected to PERST# pin of corresponding PCIe connector.

eMAG supports bifurcation on ports 0/1, 2/3, 4/5 and has another RC\_PERST# signal for the second port. eMAG also supports Endpoint mode on ports 0, 2, 4 and has input EP\_PERST# pins.

See *Figure 12*. For PCIe x16 slot on Hawk board using PCIE23:

- PCIE2\_RC\_PERSTN is connected directly to PCIe connector pin A11.

- PCIE3\_RC\_PERSTN is connected to PCIe connector reserved pin A50. It is used as a reset signal for the second PCIe x8 slot on a PCIe riser card when a PCIe riser card with two PCIe x8 slots are used.

Figure 12: PCIe Port 0 PERST# Connection Header

## 4.8. PCIe x16 Slot/Riser Card

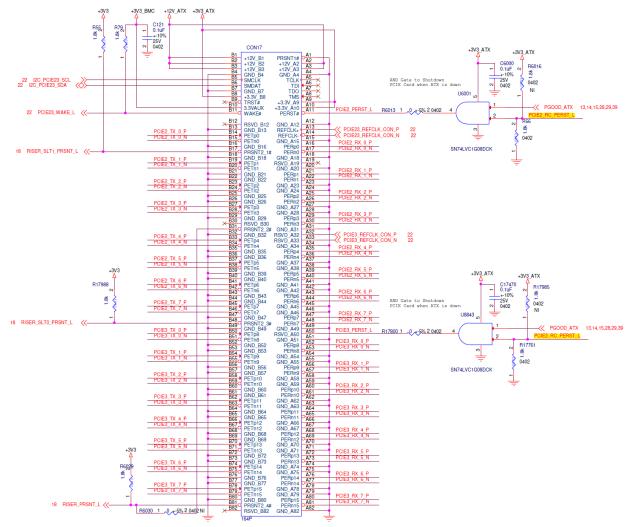

The motherboard has a single, 1x socket to be used by PCIe Riser card x16 slot (164 pins) – used for x16 PCIe and power delivery (see *Figure 13*).

Figure 13: PCIe Riser Card on the Hawk Board

Slot location must follow mechanical requirement that are outlined in the DXF document. The PCIe x16 slot combines between PCIe2 x8 lanes (LOW byte) and PCIe3 x8 lanes (HIGH byte) of CPU (refer *Table 6*).

| PIN | SIDE B CO | NNECTOR           | SIDE A CO | NNECTOR                     |

|-----|-----------|-------------------|-----------|-----------------------------|

| #   | NAME      | DESCRIPTION       | NAME      | DESCRIPTION                 |

| 1   | +12 V     | +12 volt power    | PRSNT#1   | Hot plug presence<br>detect |

| 2   | +12 V     | +12 volt power    | +12 V     | +12 volt power              |

| 3   | +12 V     | +12 volt power    | +12 V     | +12 volt power              |

| 4   | GND       | Ground            | GND       | Ground                      |

| 5   | SMCLK     | SMBus clock       | JTAG2     | ТСК                         |

| 6   | SMDAT     | SMBus data        | JTAG3     | TDI                         |

| 7   | GND       | Ground            | JTAG4     | TDO                         |

| 8   | +3.3 V    | +3.3 volt power   | JTAG5     | TMS                         |

| 9   | JTAG1     | +TRST#            | +3.3 V    | +3.3 volt power             |

| 10  | 3.3Vaux   | +3.3 V volt power | +3.3 V    | +3.3 volt power             |

Table 6: PCIe Connector Pin Descriptions for the Hawk Board

| PIN | SIDE B CC | NNECTOR             | SIDE A CC | NNECTOR           |

|-----|-----------|---------------------|-----------|-------------------|

| #   | NAME      | DESCRIPTION         | NAME      | DESCRIPTION       |

| 11  | WAKE#     | Link Reactivation   | PWRGD     | Power Good        |

|     |           | Mechanical I        | Key       |                   |

| 12  | RSVD      | Reserved            | GND       | Ground            |

| 13  | GND       | Ground              | REFCLK+   | Reference Clock   |

| 14  | HSOp(0)   | Transmitter Lane 0, | REFCLK-   | Differential pair |

| 15  | HSOn(0)   | Differential pair   | GND       | Ground            |

| 16  | GND       | Ground              | HSIp(0)   | Receiver Lane 0,  |

| 17  | PRSNT#2   | Hotplug detect      | HSIn(0)   | Differential pair |

| 18  | GND       | Ground              | GND       | Ground            |

| 19  | HSOp(1)   | Transmitter Lane 1, | RSVD      | Reserved          |

| 20  | HSOn(1)   | Differential pair   | GND       | Ground            |

| 21  | GND       | Ground              | HSIp(1)   | Receiver Lane 1,  |

| 22  | GND       | Ground              | HSIn(1)   | Differential pair |

| 23  | HSOp(2)   | Transmitter Lane 2, | GND       | Ground            |

| 24  | HSOn(2)   | Differential pair   | GND       | Ground            |

| 25  | GND       | Ground              | HSIp(2)   | Receiver Lane 2,  |

| 26  | GND       | Ground              | HSIn(2)   | Differential pair |

| 27  | HSOp(3)   | Transmitter Lane 3, | GND       | Ground            |

| 28  | HSOn(3)   | Differential pair   | GND       | Ground            |

| 29  | GND       | Ground              | HSIp(3)   | Receiver Lane 3,  |

| 30  | RSVD      | Reserved            | HSIn(3)   | Differential pair |

| 31  | PRSNT#2   | Hot plug detect     | GND       | Ground            |

| 32  | GND       | Ground              | RSVD      | Reserved          |

| 33  | HSOp(4)   | Transmitter Lane 4, | RSVD      | Reserved          |

| 34  | HSOn(4)   | Differential pair   | GND       | Ground            |

| 35  | GND       | Ground              | HSIp(4)   | Receiver Lane 4,  |

| 36  | GND       | Ground              | HSIn(4)   | Differential pair |

| 37  | HSOp(5)   | Transmitter Lane 5, | GND       | Ground            |

| 38  | HSOn(5)   | Differential pair   | GND       | Ground            |

| 39  | GND       | Ground              | HSIp(5)   | Receiver Lane 5,  |

| 40  | GND       | Ground              | HSIn(5)   | Differential pair |

| 41  | HSOp(6)   | Transmitter Lane 6, | GND       | Ground            |

| PIN | SIDE B CC | DNNECTOR             | SIDE A CC | DNNECTOR          |

|-----|-----------|----------------------|-----------|-------------------|

| #   | NAME      | DESCRIPTION          | NAME      | DESCRIPTION       |

| 42  | HSOn(6)   | Differential pair    | GND       | Ground            |

| 43  | GND       | Ground               | HSIp(6)   | Receiver Lane 6,  |

| 44  | GND       | Ground               | HSIn(6)   | Differential pair |

| 45  | HSOp(7)   | Transmitter Lane 7,  | GND       | Ground            |

| 46  | HSOn(7)   | Differential pair    | GND       | Ground            |

| 47  | GND       | Ground               | HSIp(7)   | Receiver Lane 7,  |

| 48  | PRSNT#2   | Hot plug detect      | HSIn(7)   | Differential pair |

| 49  | GND       | Ground               | GND       | Ground            |

| 50  | HSOp(8)   | Transmitter Lane 8,  | RSVD      | Reserved          |

| 51  | HSOn(8)   | Differential pair    | GND       | Ground            |

| 52  | GND       | Ground               | HSIp(8)   | Receiver Lane 8,  |

| 53  | GND       | Ground               | HSIn(8)   | Differential pair |

| 54  | HSOp(9)   | Transmitter Lane 9,  | GND       | Ground            |

| 55  | HSOn(9)   | Differential pair    | GND       | Ground            |

| 56  | GND       | Ground               | HSIp(9)   | Receiver Lane 9,  |

| 57  | GND       | Ground               | HSIn(9)   | Differential pair |

| 58  | HSOp(10)  | Transmitter Lane 10, | GND       | Ground            |

| 59  | HSOn(10)  | Differential pair    | GND       | Ground            |

| 60  | GND       | Ground               | HSIp(10)  | Receiver Lane 10, |

| 61  | GND       | Ground               | HSIn(10)  | Differential pair |

| 62  | HSOp(11)  | Transmitter Lane 11, | GND       | Ground            |

| 63  | HSOn(11)  | Differential pair    | GND       | Ground            |

| 64  | GND       | Ground               | HSIp(11)  | Receiver Lane 11, |

| 65  | GND       | Ground               | HSIn(11)  | Differential pair |

| 66  | HSOp(12)  | Transmitter Lane 12, | GND       | Ground            |

| 67  | HSOn(12)  | Differential pair    | GND       | Ground            |

| 68  | GND       | Ground               | HSIp(12)  | Receiver Lane 12, |

| 69  | GND       | Ground               | HSIn(12)  | Differential pair |

| 70  | HSOp(13)  | Transmitter Lane 13, | GND       | Ground            |

| 71  | HSOn(13)  | Differential pair    | GND       | Ground            |

| 72  | GND       | Ground               | HSIp(13)  | Receiver Lane 13, |

| 73  | GND       | Ground               | HSIn(13)  | Differential pair |

| PIN | SIDE B CO | NNECTOR                 | SIDE A CONNECTOR |                   |

|-----|-----------|-------------------------|------------------|-------------------|

| #   | NAME      | DESCRIPTION             | NAME             | DESCRIPTION       |

| 74  | HSOp(14)  | Transmitter Lane 14,    | GND              | Ground            |

| 75  | HSOn(14)  | Differential pair       | GND              | Ground            |

| 76  | GND       | Ground                  | HSIp(14)         | Receiver Lane 14, |

| 77  | GND       | Ground                  | HSIn(14)         | Differential pair |

| 78  | HSOp(15)  | Transmitter Lane 15,    | GND              | Ground            |

| 79  | HSOn(15)  | Differential pair       | GND              | Ground            |

| 80  | GND       | Ground                  | HSIp(15)         | Receiver Lane 15, |

| 81  | PRSNT#2   | Hot plug present detect | HSIn(15)         | Differential pair |

| 82  | RSVD#2    | Hot Plug Detect         | GND              | Ground            |

The riser card must implement I2C to GPIO expander (PCA9545) to be accessed by BMC on motherboard to tell which ICs are currently on each slot. Vendor must follow the SMBUS addresses defined in *Figure 14* to avoid address conflicts. The PCIe x16 slot's SMBus connects to downstream channel 0 of SMBUS switch IC – PCA9545, the SCL/SDA upstream connects to BMC I2C6 and the 8 bit address of this PCA9545 is 0xE2.

## 4.9. SATA Connectivity

Hawk provides four SATA connectors. SATA0-3 are standard 7-pin vertical connectors intended to be used with SATA cable.

The vertical SATA connector needs to be placed near the I/O side of the motherboard for easy access. HDDs attached to all SATA connectors need to follow spin-up delay requirements as described below.

When a hard drive spins up after power on, it draws excessive current on both 12 V and 5 V. The peak current may reach 1.5 A  $\sim$  2 A range on the 12 V rail. Based on the number of hard drives in the system,

Date: April 22, 2020

all hard drives must spin up in a sequential manner. The BIOS must implement a 5-second delay between each hard drive spinning up. In order to do this, the SATA hard drive's power cable must have pin 11 as NC (No Connection) to enable hard drive's spin-up delay function.

## 4.10. M.2 Connectivity

The motherboard has 2x M.2 NVMe connectors with Key ID=M and H6.7 Type. M.2 connector has an optional connection of PCIe x4 from CPU. The onboard M.2 connector supports both 2280 and 22110 card form factors with both single-sided and double-sided contacts.

The PERST# signal must go active before the power on M.2 connector is removed per the *PCI Express Card Electromechanical Specification*.

The vendor must add SMBUS and Alert connections to the CPU base on the latest M.2 specification. Please be aware that the M.2 SMBUS is at 1.8 V level. The vendor must use a shunt regulator to create 1.8 V for SMBUS pull-up and add a level shifter to connect it to the CPU.

## 4.11. USB 2.0 Connectivity

The motherboard has two external Type-A, vertical, right angle USB 2.0 ports and two 5x2 USB 2.0 headers located on the right side of the board. The BIOS must support the following USB devices:

- USB keyboard and mouse

- USB flash drive (bootable)

The 5x2 header is used for two front panel USB 2.0 ports. A USB extension cable is required in this case.

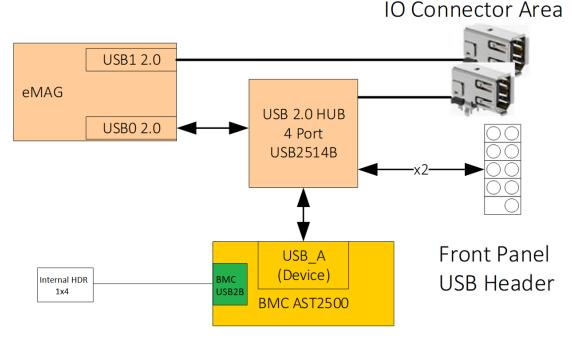

As shown in Figure 15, the eMAG CPU has two USB 2.0 ports.

USB0 is connected to a 4 port USB 2.0 hub. The hub's downstream ports are connected to BMC USB\_B port, front panel USB header (two USB ports) and USB connector in I/O connector area.

USB1 is directly connected to USB connector in I/O connector area.

Every USB port is equipped with a USB LDO with overcurrent protection and can support devices with up to 500 mA VBUS current limit.

Figure 15: USB Subsection Implementation on the Hawk Board

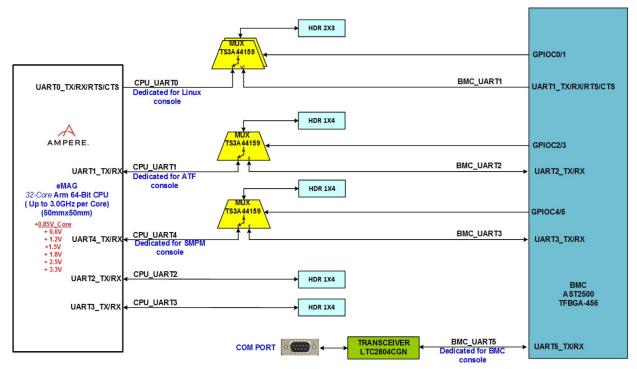

## 4.12. UART Connectivity

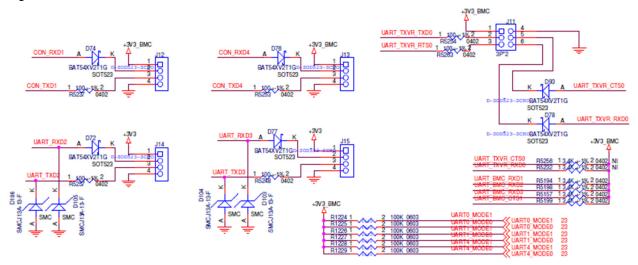

The UART connectivity on the Hawk board is shown in *Figure 16*.

Figure 16: CPU UART[0,4] and BMC UART[1-3,5] Connectivity on the Hawk Board

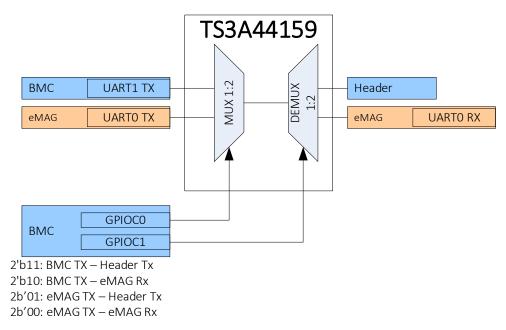

*Figure 17* illustrates the 4-way multiplexer/demultiplexer implementation for the eMAG/BMC UARTs on the Hawk board.

Figure 17: 4-Way Mux/Demux for eMAG/BMC UARTs on the Hawk Board

BMC UART5 (debug console) is connected directly through a transceiver to DB9 in I/O area.

Date: April 22, 2020

A four-way mux/demux is powered from BMC standby voltage and is power sequenced together with BMC. eMAG CPU pins are in "No Connect" mode unless BMC drives the correct control signals to it.

*Table 7* lists the 4-pin UART0 header 2x3 on the Hawk board.

| Table 7: UART0 2x3 | Header Pinout or     | the Hawk Board      |

|--------------------|----------------------|---------------------|

|                    | i leauer i litout or | T LITE T IAWK DUALU |

| PIN # | SIGNAL         | PIN # | SIGNAL         |

|-------|----------------|-------|----------------|

| 1     | +3V3           | 2     | UART_TXVR_TXD0 |

| 3     | UART_TXVR_RTSO | 4     | GND            |

| 5     | UART_TXVR_CTS0 | 6     | UART_TXVR_RXD0 |

Table 8 lists the 2-pin UART1, 2, 3, 4 header 1x4 on the Hawk board.

Table 8: UART1, 2, 3, and 4 1x4 Header Pinout on the Hawk Board

| PIN # | SIGNAL    | PIN # | SIGNAL    |

|-------|-----------|-------|-----------|

| 1     | +3V3      | 2     | UART_RXDx |

| 3     | UART_TXDx | 4     | GND       |

### 4.12.1. UART Channel Selection

BMC UART5 (debug console) is connected directly through transceiver to DB9 in IO area.

A four-way mux/demux is powered from BMC stand-by voltage and is power sequenced together with BMC. eMAG CPU pins are in No Connect mode unless BMC drives the correct control signal state to it.

The four-way mux/demux is controlled by BMC GPIOC0-5 interface. Control can be overridden by installing UART control override jumpers on the UART header.

*Table 9* lists the UART mode control signals.

Table 9: UART Mode Control Signals on the Hawk Board

| BMC SIGNALS | UART MODE       | CONTROL STATE | UART MODE                   |

|-------------|-----------------|---------------|-----------------------------|

| GPIOC[1:0]  | UARTO_MODE[1:0] | 2b'00         | eMAG UARTO Loopback         |

| GPIOC[1:0]  | UARTO_MODE[1:0] | 2b'01         | eMAG UARTO > IO Area Header |

| GPIOC[1:0]  | UARTO_MODE[1:0] | 2b'10         | BMC UART1 > eMAG UART0      |

| GPIOC[1:0]  | UARTO_MODE[1:0] | 2b'11         | BMC UART1 > IO Area Header  |

| GPIOC[3:2]  | UART1_MODE[1:0] | 2b'00         | eMAG UART1 Loopback         |

| GPIOC[3:2]  | UART1_MODE[1:0] | 2b'01         | eMAG UART1 > IO Area Header |

| GPIOC[3:2]  | UART1_MODE[1:0] | 2b'10         | BMC UART2 > eMAG UART1      |

| GPIOC[3:2]  | UART1_MODE[1:0] | 2b'11         | BMC UART2 > IO Area Header  |

| GPIOC[5:4]  | UART4_MODE[1:0] | 2b'00         | eMAG UART4 Loopback         |

| GPIOC[5:4]  | UART4_MODE[1:0] | 2b'01         | eMAG UART4 > IO Area Header |

| GPIOC[5:4]  | UART4_MODE[1:0] | 2b'10         | BMC UART3 > eMAG UART4      |

| GPIOC[5:4]  | UART4_MODE[1:0] | 2b'11         | BMC UART3 > IO Area Header  |

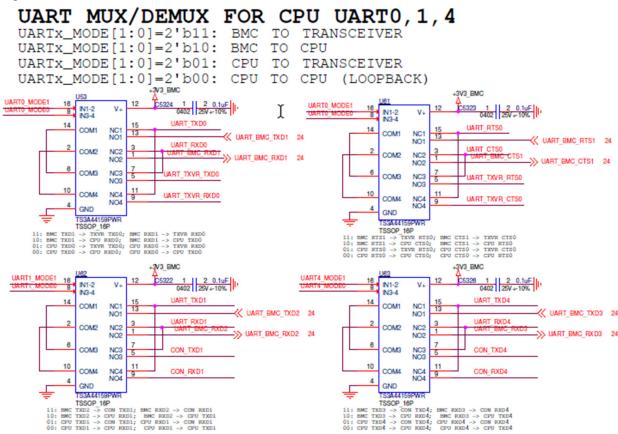

### 4.12.2. UART Summary and Schematics

- eMAG UART0: Non-secure 4-way switch to BMC UART1 and I/O header

- eMAG UART4: Secure 4-way switch to BMC UART3 and I/O header

- eMAG UART1: SMpro console, 4-way switch to BMC UART2 and I/O header

- BMC UART1: 4-way switch to eMAG UART0 and I/O header

- BMC UART2: 4-way switch to eMAG UART1 and I/O header

- BMC UART3: 4-way switch to eMAG UART4 and I/O header

- BMC UART5: BMC debug console, connected to transceiver and I/O header

Figure 18 and Figure 19 illustrate the UART schematics for the Hawk board.

Figure 18: Hawk Board UART Schematics - 1

Figure 19: Hawk Board UART Schematics – 2

# 4.13. Fan Connectivity

The Hawk board has three system dual fan connectors. Fan connector signals must follow 4-Wire Pulse Width Modulation (PWM) Controlled Fans Specification Revision 1.3 (dated September 2005) published by Intel Corporation. Each fan connector has six pins, which is compatible with a standard 4-wire fan connector, and can also be used to support a dual rotor fan with independent PWM control signals as well as tachometer (TACH) signals. The fan connector pin definitions are listed in *Table 10*. Note that the fan power needs to be turned off during S5.

| PIN | DESCRIPTION | PIN | DESCRIPTION |

|-----|-------------|-----|-------------|

| 1   | GND         | 4   | Control #1  |

| 2   | +12 V       | 5   | Sense #2    |

| 3   | Sense #1    | 6   | Control #2  |

# 4.14. VGA Connector

The Hawk board has a right edge type DB15 VGA connector on the motherboard side. *Table 11* lists the signal assignments.

Table 11: Standard Female DB9 VGA Connector Pinout

| PIN | DESCRIPTION                                            | PIN | DESCRIPTION    | PIN | DESCRIPTION                                                            |

|-----|--------------------------------------------------------|-----|----------------|-----|------------------------------------------------------------------------|

| 1   | Red video                                              | 2   | Green video    | 3   | Blue video                                                             |

| 4   | Reserved since E-DDC,<br>formerly monitor ID.<br>Bit 2 | 5   | Ground (HSync) | 6   | Red return                                                             |

| 7   | Green return                                           | 8   | Blue return    | 9   | +5 V DC (powers EDID<br>EEPROM chip on some<br>monitors), formerly key |

| PIN | DESCRIPTION         | PIN | DESCRIPTION                                            | PIN | DESCRIPTION                                                         |

|-----|---------------------|-----|--------------------------------------------------------|-----|---------------------------------------------------------------------|

| 10  | Ground (VSync, DDC) | 11  | Reserved since E-DDC, formerly<br>monitor ID.<br>Bit 0 | 12  | I <sup>2</sup> C data since DDC2,<br>formerly monitor ID.<br>Bit 1  |

| 13  | Horizontal sync     | 14  | Vertical sync                                          | 15  | I <sup>2</sup> C clock since DDC2,<br>formerly monitor ID.<br>Bit 3 |

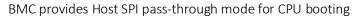

# 4.15. SPI Interface

eMAG supports two SPI interfaces (SPI0 and SPI1). Only SPI0 is used on Hawk to interface with the SPI NOR.

eMAG SPI0 is connected to BMC host SPI interface, which supports pass-through mode for normal CPU booting (refer *Figure 20*). BMC can update SPI NOR image by taking over control of the bus and providing Remote Firmware Upgrade (RFU) capability to the system.

Figure 20: eMAG SPI0 Boot Bus

Table 12 lists the devices connected to the SPI bus on the Hawk board.

Table 12: SPI Devices on the Hawk Board

| BUS NAME | SELECT | FUNCTION                     | PART NUMBER       |

|----------|--------|------------------------------|-------------------|

| SPIO     | CS0    | Boot SPI NOR flash, 256 Mbit | MX25L25635FMI-10G |

# 4.16. I2C (IIC) Buses

eMAG CPU provides five I2C buses. *Table 13* lists the eMAG SoC specification with I2C bus allocation for different system functions.

| IIC DEVICE<br># | SMB_ALERT                         | FREQ           | MASTER/<br>SLAVE | LOCATION                    | ACCESSIBILITY                | USAGE                                                                                                                                                 | IIC<br>OWNER  |

|-----------------|-----------------------------------|----------------|------------------|-----------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| IIC4            | Yes (in)-<br>EVENT#<br>(wired-OR) | 1 MHz<br>pt-pt | Master           | AHBC                        | All<br>Optionally S or<br>NS | External BMC<br>– SMpro<br>responds to<br>BMC requests,<br>Board Temp<br>Sensors, Sys<br>EEPROM, and<br>any other I2C<br>devices. (SFP+,<br>RTC etc.) | SMpro         |

| IIC3            | Yes (in)-<br>EVENT#<br>(wired-OR) | 1 MHz<br>pt-pt | Slave            | АНВС                        | All<br>Optionally S or<br>NS | External BMC<br>– SMpro<br>receives BMC<br>requests                                                                                                   | SMpro         |

| IIC2            | Yes (in)-<br>EVENT#<br>(wired-OR) | 1 MHz<br>pt-pt | Master           | AHBC                        | All Optionally S<br>or NS    | DDR DIMMs<br>SPD (with an<br>external I2C<br>mux chip<br>when more<br>than 8 SPDs<br>and/or other<br>devices as<br>well, need to<br>be attached)      | PMD,<br>SMpro |

| IIC1+ BSC       | No                                | 400<br>kHz     | Master           | SMpro<br>secure<br>boundary | Private to<br>SMpro          | EEPROM for<br>bootstrap<br>vector or<br>SMpro code                                                                                                    | SMpro         |

| IICO            | Yes (in)- VR<br>ALERT output      | 1 MHz          | Master           | PMpro                       | All Secure only              | VRs/VRMs                                                                                                                                              | PMpro         |

Table 13: eMAG I2C Buses Available on the Hawk Board

#### Table 14: eMAG I2C Devices Available on the Hawk Board

| CPU ADDRESS MAP TABLE |                  |                  |                     |  |  |  |

|-----------------------|------------------|------------------|---------------------|--|--|--|

| BUS NAME              | I2C ADDRESS (7b) | I2C ADDRESS (8b) | PART NUMBER         |  |  |  |

| IICO (I2C/PMbus)      | 0x68             | 0xD0             | TPS53659 (VDDQ0123) |  |  |  |

|                       | 0x6A             | 0xD4             | TPS53659 (VDDQ4567) |  |  |  |

|                       | 0x58             | 0xB0             | TPS53679 (CPU_PCP)  |  |  |  |

|          | CPU ADDRESS MAP TABLE |                  |                            |  |  |  |

|----------|-----------------------|------------------|----------------------------|--|--|--|

| BUS NAME | I2C ADDRESS (7b)      | I2C ADDRESS (8b) | PART NUMBER                |  |  |  |

|          | 0x18                  | 0x30             | TPS544B20RVFR (CPU_SOC)    |  |  |  |

| IIC1     | 0x52, 0x53            | 0xA4, 0xA6       | EEPROM AT24CM01            |  |  |  |

|          | 0x51                  | 0xA2             | RTC PCF85063TP/1Z          |  |  |  |

| IIC2     | 0x70                  | 0xE0             | I2C SW PCA9545APW          |  |  |  |

|          | 0x50                  | 0xA0             | DIMM#0 (PCA9545APW SW CH0) |  |  |  |

|          | 0x52                  | 0xA4             | DIMM#1 (PCA9545APW SW CH0) |  |  |  |

|          | 0x54                  | 0xA8             | DIMM#2 (PCA9545APW SW CH0) |  |  |  |

|          | 0x56                  | 0xAC             | DIMM#3 (PCA9545APW SW CH0) |  |  |  |

|          | 0x50                  | 0xA0             | DIMM#4 (PCA9545APW SW CH1) |  |  |  |

|          | 0x54                  | 0xA4             | DIMM#5 (PCA9545APW SW CH1) |  |  |  |

|          | 0x54                  | 0xA8             | DIMM#6 (PCA9545APW SW CH1) |  |  |  |

|          | 0x56                  | 0xAC             | DIMM#7 (PCA9545APW SW CH1) |  |  |  |

|          | TBD                   | TBD              | M.2_0 (PCA9545APW SW CH2)  |  |  |  |

|          | TBD                   | TBD              | M.2_1 (PCA9545APW SW CH3)  |  |  |  |

| IIC3     | TBD                   | TBD              | BMC I2C3                   |  |  |  |

| IIC4     | TBD                   | TBD              | BMC I2C1                   |  |  |  |

| IIC5     | TBD                   | TBD              | ТВД                        |  |  |  |

|          |                       | BMC ADDRESS MAP  | P TABLE                    |  |  |  |

| BUS NAME | I2C ADDRESS (7b)      | I2C ADDRESS (8b) | PART NUMBER                |  |  |  |

| IIC1     | TBD                   | TBD              | CPU I2C4                   |  |  |  |

| IIC2     | 0x52, 0x53            | 0xA4, 0xA6       | EEPROM AT24CM01            |  |  |  |

|          | 0x51                  | 0xA2             | RTC PCF85063TP/1Z          |  |  |  |

| IIC3     | TBD                   | TBD              | CPU I2C3                   |  |  |  |

| IIC4     | 0x50                  | 0xA0             | CAT24C64WI                 |  |  |  |

|          | 0x19                  | 0x32             | LM95231CIMM-1              |  |  |  |

|          | 0x48                  | 0x90             | ТМР75А                     |  |  |  |

|          | 0x49                  | 0x92             | ТМР75А                     |  |  |  |

|          | 0x4A                  | 0x94             | ТМР75А                     |  |  |  |

| IIC5     | TBD                   | TBD              | FRONT PANEL CONNECTOR      |  |  |  |

| BMC ADDRESS MAP TABLE |                  |                  |                                                              |  |  |

|-----------------------|------------------|------------------|--------------------------------------------------------------|--|--|

| BUS NAME              | I2C ADDRESS (7b) | I2C ADDRESS (8b) | PART NUMBER                                                  |  |  |

| IIC6                  | 0x71             | 0xE2             | I2C SW PCA9545PW                                             |  |  |

|                       | TBD              | TBD              | PCIE (CON17/RISER)<br>(PCA9545A PW SW CH0)                   |  |  |

|                       | 0x61             | 0xC2             | PCIE (ONBOARD INTEL I210 CONTROLLER)<br>(PCA9545A PW SW CH1) |  |  |

|                       | TBD              | TBD              | OCP (CON41/OCP)<br>(PCA9545A PW SW CH2)                      |  |  |

| IIC7                  | TBD              | TBD              | BMC AUX PMBUS CONNECTOR                                      |  |  |

| IIC8                  | TBD              | TBD              | RMC SIGNAL CONNECTOR                                         |  |  |

| IIC9                  | TBD              | TBD              | ТВД                                                          |  |  |

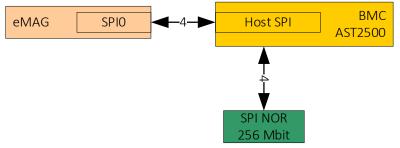

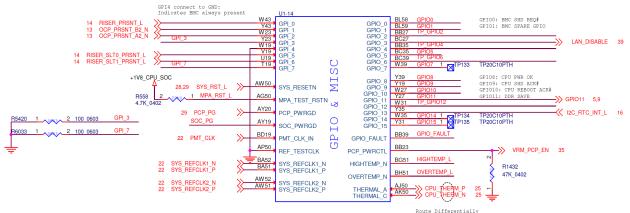

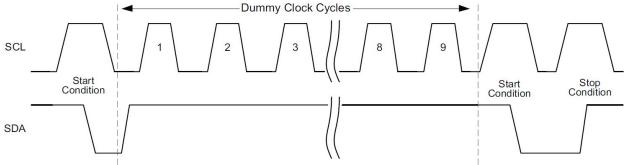

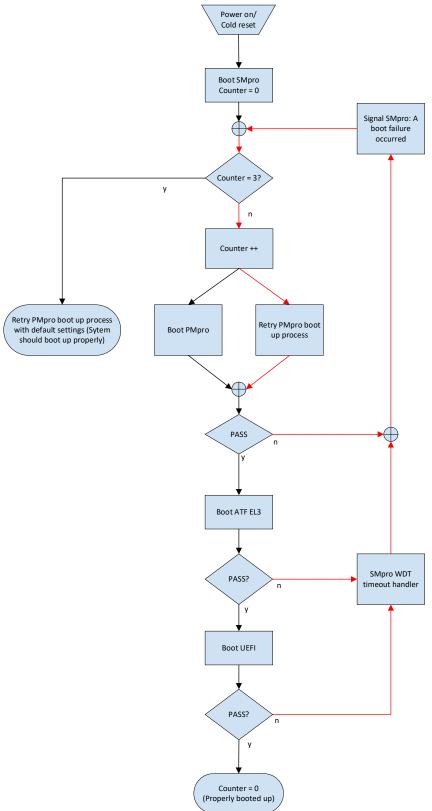

# 4.17. GPIO Signals