**EDGECORE** Networks Corporation

# Edgecore AS7316-26X

## **Programming Guide**

#### **Revision 1.0**

## **Revision History**

| Revision | Date      | Author      | Description   |

|----------|-----------|-------------|---------------|

| 1.0      | 9/15/2018 | Jeff Catlin | Initial Draft |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

|          |           |             |               |

## Contents

| Licenses       5         Scope       7         Overview       7         Physical Overview       7         Front View       7         Front View       7         Rear View       8         Dimensions       8         Top View       9         Front View Detail       10         Front View Detail       10         Front Panel LEDs       10         Network / Timing LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.2.       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM       35         1.4.       PCle       36 | Revision Histo | ory2                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------|

| Overview       7         Physical Overview       7         Front View       7         Rear View       8         Dimensions       8         Top View       9         Front View Detail.       10         Front View Detail.       10         Front View Detail.       10         Network / Timing LEDs       10         System LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.2.       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM       35         1.4.       PCie       36                                          | Licenses       |                          |

| Physical Overview       7         Front View       7         Rear View       8         Dimensions       8         Top View       9         Front View Detail.       10         Front Panel LEDs       10         Network / Timing LEDs       10         System LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.2.       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM       35         1.4.       PCle       36                                                                                                         | Scope          |                          |

| Front View       7         Rear View       8         Dimensions       8         Top View       9         Front View Detail       10         Front View Detail       10         Network / Timing LEDs       10         System LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCle       36                                                                                                                                             | Overview       |                          |

| Rear View       8         Dimensions       8         Top View       9         Front View Detail       10         Front Panel LEDs       10         Network / Timing LEDs       10         System LEDs       10         System LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree.       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCle       36                                                                                                                                           | Physical Ov    | verview7                 |

| Dimensions       8         Top View       9         Front View Detail       10         Front Panel LEDs       10         Network / Timing LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.       Power-On Reset       20         1.1.1       Power Mapping       29         1.3       RAM       35         1.4       PCle       36                                                                                                                                                                                                                                                                                      | Front Vi       | ew7                      |

| Top View.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Rear Vie       | ew                       |

| Front View Detail       10         Front Panel LEDs       10         Network / Timing LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM.       35         1.4       PCIe       36                                                                                                                                                                                                                                                                                   | Dimensi        | ons                      |

| Front Panel LEDs       10         Network / Timing LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCle       36                                                                                                                                                                                                                                                                                                                       | Top Viev       | <i>N</i> 9               |

| Network / Timing LEDs       10         System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCle       36                                                                                                                                                                                                                                                                                                                                                         | Front Vie      | ew Detail10              |

| System LEDs       12         Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                | Front Pane     | el LEDs                  |

| Front panel ports       13         Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset         1.2       PCH Strap pin definition         26       12         Memory Mapping       29         1.3       RAM         1.4       PCIe                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Network        | k / Timing LEDs          |

| Console Port       13         Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset         1.1.2       PCH Strap pin definition         26       1.2         Memory Mapping       29         1.3       RAM       35         1.4       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | System I       | LEDs                     |

| Network ports       13         Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Front pa       | anel ports13             |

| Rear View       14         Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Console        | e Port                   |

| Clock Tree       15         Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Network        | k ports                  |

| Power Tree       16         Reset Tree       18         Interrupt Tree       19         I2C/SMBus Architecture       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2       Memory Mapping       29         1.3       RAM       35         1.4       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Rear View      |                          |

| Reset Tree       18         Interrupt Tree.       19         I2C/SMBus Architecture.       20         1.1.1       Power-On Reset       20         1.1.2       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM.       35         1.4.       PCle       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Clock Tr       | ee15                     |

| Interrupt Tree.       19         I2C/SMBus Architecture.       20         1.1.1       Power-On Reset       20         1.1.2.       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM.       35         1.4.       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Power T        | ree                      |

| I2C/SMBus Architecture.       20         1.1.1.       Power-On Reset       20         1.1.2.       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM.       35         1.4.       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Reset Tr       | ree                      |

| 1.1.1.       Power-On Reset       20         1.1.2.       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM       35         1.4.       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Interrup       | t Tree19                 |

| 1.1.2.       PCH Strap pin definition       26         1.2.       Memory Mapping       29         1.3.       RAM       35         1.4.       PCIe       36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I2C/SMBus      | s Architecture           |

| 1.2.       Memory Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.1.1.         | Power-On Reset           |

| 1.3.       RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.1.2.         | PCH Strap pin definition |

| 1.4. PCIe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1.2.           | Memory Mapping           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.3.           | RAM35                    |

| 1.5. SMbus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.4.           | PCIe                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.5.           | SMbus                    |

|    | 1.6.    | UART                                | 39 |

|----|---------|-------------------------------------|----|

|    | 1.7.    | USB                                 | 40 |

|    | 1.8.    | SATA                                | 41 |

|    | 1.9.    | GPIO                                | 42 |

|    | 1.10.   | CPLD                                | 46 |

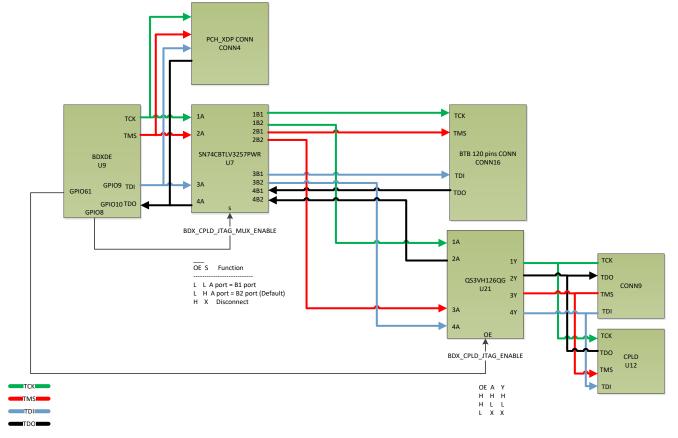

|    | 1.11.   | JTAG                                | 47 |

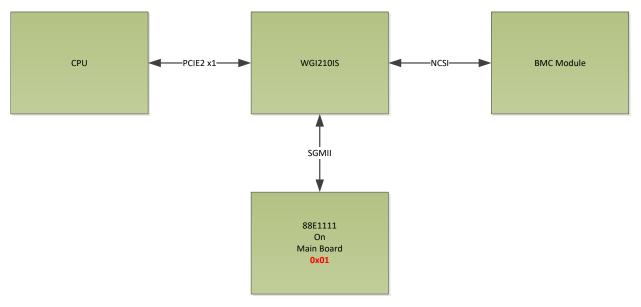

|    | 1.12.   | I210                                | 48 |

|    | 1.12.1. | Feature                             | 49 |

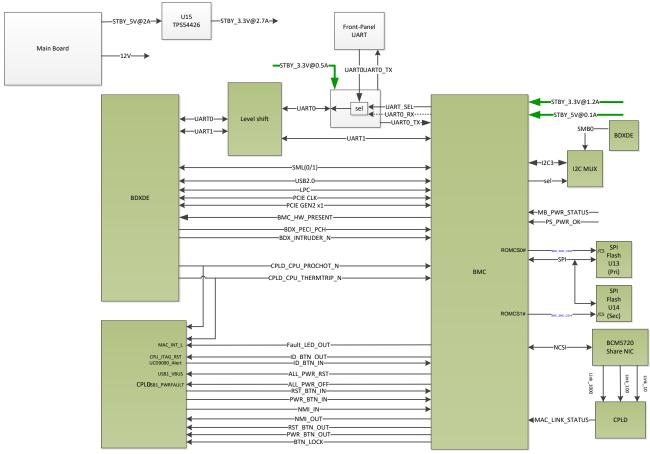

| 2. | BMC Sub | p-system                            | 49 |

|    | 2.1.    | LPC                                 | 51 |

|    | 2.2.    | SMBUS                               | 51 |

|    | 2.3.    | UART                                | 51 |

|    | 2.3.1.  | Power-On Reset                      | 51 |

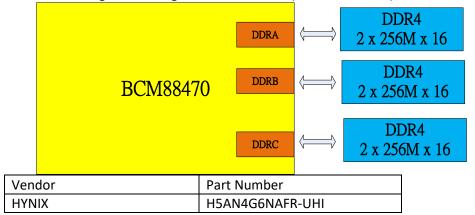

|    | 2.3.2.  | Deep buffering RAM                  | 52 |

|    | 2.3.3.  | NIF/NIFE SerDes                     | 52 |

|    | 2.3.4.  | CAUI-4 interface                    | 55 |

|    | 2.3.5.  | 10G KR interface                    | 55 |

|    | 2.3.6.  | LED stream                          | 55 |

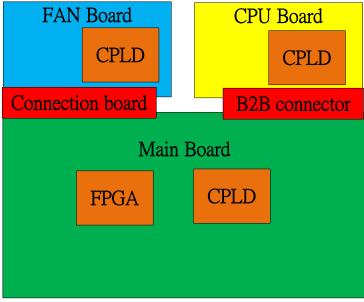

|    | 2.4.    | CPLD and FPGA                       | 58 |

|    | 2.4.1.  | FPGA/CPLD Field upgrade information | 59 |

|    | 2.4.2.  | FPGA                                | 59 |

|    | 2.4.3.  | CPLD                                | 75 |

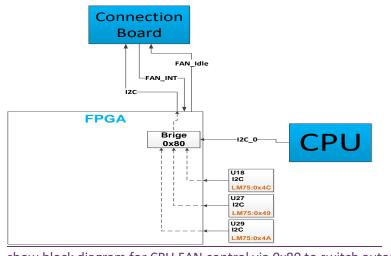

|    | 2.4.4.  | Fan Board CPLD                      | 99 |

## Licenses

All semiconductor devices that may be referred to in this specification, or required to manufacture products described in this specification, will be considered referenced only, and no intellectual property rights embodied in or covering such semiconductor devices shall be licensed as a result of this specification or such references. Notwithstanding anything to the contrary in the CLA, the licenses set forth therein do not apply to the intellectual property rights included in or related to the semi-conductor devices identifies in the specification. These references include without limitation the reference to devices listed below. For clarity, no patent claim that reads on such semiconductor devices will be considered a "Granted Claim" under the applicable Contributor License Agreement for this specification.

|                                                                                                                                                                                             | AS7316-26X                                                                                                                                                                                                              |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CPU sub-<br>system CPU: Intel Xeon D1519 1.5G<br>DDR SDRAM: 8GB x 2 2133MHz with ECC (SO-DIMM) DDR4<br>SPI Flash (Boot): 16MB x 2<br>mSATA: 128GB MLC<br>TPM: SLB 9665XT2.0 FW5.63 INFINEON |                                                                                                                                                                                                                         |  |  |

| Management                                                                                                                                                                                  | UART RS232 console port (RJ45), Out-band Management Ethernet port (RJ45)                                                                                                                                                |  |  |

| MAC                                                                                                                                                                                         | Broadcom BCM88470, 300Gbs full duplex switching                                                                                                                                                                         |  |  |

| Ethernet Ports                                                                                                                                                                              | 16x 10G SFP + 8x 25G SFP28 + 2x 100G QSFP28                                                                                                                                                                             |  |  |

| BMC                                                                                                                                                                                         | AST2400                                                                                                                                                                                                                 |  |  |

| CPLD                                                                                                                                                                                        | Altera 5M2210ZF324I5N (FBGA324) and 5M1270ZF256I5 (FBGA256)                                                                                                                                                             |  |  |

| FPGA                                                                                                                                                                                        | Altera 10M16DCU324I7G                                                                                                                                                                                                   |  |  |

| РСВ                                                                                                                                                                                         | 20-Layers, TU-883+TU-862HF (Hybrid material) for Mainboard<br>12-Layers, TG 180 for CPU module<br>10-Layers, TG 150 for Connection Board<br>4-Layers, TG 150 for FAN Board<br>8- Layers, TU-662 \$ EM-825 for BMC Board |  |  |

| Power Supply                                                                                                                                                                                | 400W PSU, airflow direction is front to back, DC to DC, AC to DC, 1+1<br>redundant load-sharing, hot-swappable.<br>Notes: The airflow is front to back from chassis system view.                                        |  |  |

| Cooling                                                                                                                                                                                     | 5 fan-tray modules with 5 pcs of 40mm x40mm x 28mm 12V fans, hot-<br>swappable                                                                                                                                          |  |  |

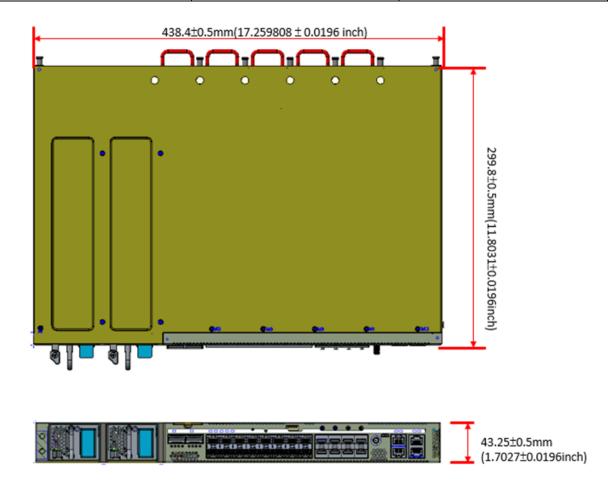

| Dimension                                                                                                                                                                                   | L(Depth):299.8±0.5mm_(11.8031±0.0196inch)<br>W(Width):438.4±0.5mm_(17.259808 ± 0.0196 inch)<br>H(Height):43.25±0.5 mm_(1.7027±0.0196inch)                                                                               |  |  |

As of September 15, 2018, this specification is contributed under the OCP Contributor Licensing Agreement (OCP-CLA) by the following entities: Acton Technology Corporation, through its subsidiary Edgecore Networks Corporation

Limitations of the OCP CLA license are noted below: No Limitations

You can review the signed copies of the OCP-CLA for this specification on the OCP website. http://www.opencompute.org/products/specsanddesign Usage of this specification is governed by the OCPHL permissive. You can review this license at <a href="http://www.opencompute.org/participate/legal-documents/">http://www.opencompute.org/products/specsanddesign</a>

Your use of this Specification may be subject to other third-party rights. THIS SPECIFICATION IS PROVIDED "AS IS." The contributors expressly disclaim any warranties (express, implied, or otherwise), including implied warranties of merchantability, non-infringement, fitness for a particular purpose, or title, related to the Specification. The entire risk as to implementing or otherwise using the Specification is assumed by the Specification implementer and user. IN NO EVENT WILL ANY PARTY BE LIABLE TO ANY OTHER PARTY FOR LOST PROFITS OR ANY FORM OF INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES OF ANY CHARACTER FROM ANY CAUSES OF ACTION OF ANY KIND WITH RESPECT TO THIS SPECIFICATION OR ITS GOVERNING AGREEMENT, WHETHER BASED ON BREACH OF CONTRACT, TORT (INCLUDING NEGLIGENCE), OR OTHERWISE, AND WHETHER OR NOT THE OTHER PARTY HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

## Scope

This document outlines the technical specifications for the Edgecore AS7316-26X Open Switch Platform submitted to the Open Compute Foundation to aid in porting software to the hardware platform.

## **Overview**

This document describes the technical specifications of the AS7316-26X Cell Site Gateway Router designed by Edgecore Networks Corporation. The AS7316-26X is a cost optimized design focused on the aggregation of 10G/25G cellular equipment and providing 100G backhaul connections. The AS7316-26X supports a broad set of IEEE 1588 /SyncE features geared towards 4G and 5G timing needs.

The AS7316-26X supports sixteen SFP+ ports, eight SFP28 ports, and two QSFP28 ports for network connectivity.

The AS7316-26X is a PHY-Less design with the network interface connections directly attaching to the Serdes interfaces of the Broadcom 88470 switching silicon providing the lowest cost, latency, and power. The AS7316-26X supports traditional features found in switches such as:

- Redundant field replaceable power supply and fan units

- Support for "Front to Back" air flow direction

- Supports a modular CPU card that allows flexibility in the CPU and/or memory configurations that can be offered.

- Support for AC or DC power supply units

## **Physical Overview**

#### **Front View**

#### **Rear View**

#### **Dimensions**

|        | Inches | Millimeters |

|--------|--------|-------------|

| Length | 11.80  | 299.8       |

| Width  | 17.26  | 438.4       |

| Height | 1.70   | 43.25       |

|        |        |             |

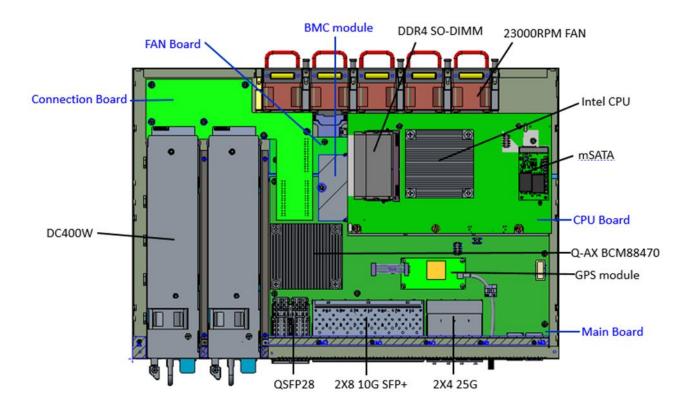

#### **Top View**

The top view of the AS7316-26X shows the PCBs and associated components in the AS7316-26X system

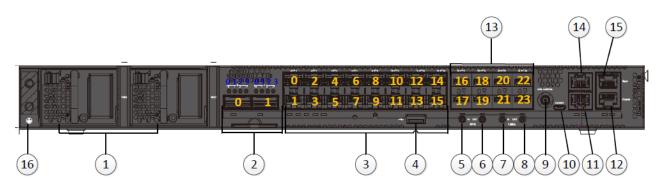

#### **Front View Detail**

The front panel view of the AS7316-26X includes the following key components:

| <b>Description</b>                  |                                                   |  |

|-------------------------------------|---------------------------------------------------|--|

| <u>1- Power Suppl</u> ies           | <u>9- GPS antenna port</u>                        |  |

| 2-100 Gigabit Ethernet QSFP28 ports | <u>10-Micro USB console port</u>                  |  |

| 3-10 Gigabit Ethernet SFP+ ports    | 11-Time of day (ToD) RJ45 port                    |  |

| 4-USB storage port                  | 12-RJ45 console port                              |  |

| 5-1PPS input port                   | 13-25 Gigabit Ethernet SFP28 ports                |  |

| 6-1PPS output port                  | 14- Building-Integrated Timing System port (BITS) |  |

| 7-10MHz input port                  | 15-Management Ethernet port (MGMT)                |  |

| <u>8-10MHz output port</u>          | <u>1</u> 6 <u>-Grounding mark</u>                 |  |

#### **Front Panel LEDs**

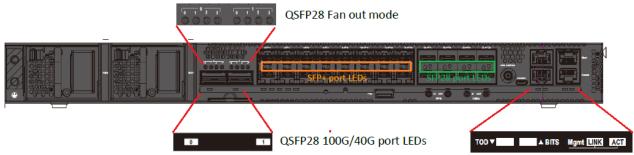

#### **Network / Timing LEDs**

The status of port LED will not be affected when the switch is in configuration mode. Each port has its dedicated LED with QSFP28 and SFP+ connectors. The management port has dedicated LED to indicate Link and Activity. The ToD and BITS ports have dedicated LED to indicate Link status.

Figure 1 Network and Timing Port LEDs

| Port LED Definition                                           |                       |                                                                                                                                                |  |

|---------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LED                                                           | CONDITION             | STATUS                                                                                                                                         |  |

| SFP+ Port LED (Port00 to<br>Port15)                           | On/Flashing<br>Green  | SFP+ port has a valid activity at 10G mode and the flashing to indicate activity.                                                              |  |

|                                                               | On/Flashing<br>Amber  | SFP+ port has a valid activity at 1G mode<br>and the flashing to indicate activity.                                                            |  |

|                                                               | Off                   | There is no link on the port.                                                                                                                  |  |

| SFP28 Port LED (Port16 to Port23)                             | On/Flashing<br>Blue   | SFP28 port has a valid activity at 25G mode and the flashing to indicate activity.                                                             |  |

|                                                               | On/Flashing<br>Green  | SFP28 port has a valid activity at 10G mode and the flashing to indicate activity.                                                             |  |

|                                                               | Off                   | There is no link on the port.                                                                                                                  |  |

| QSFP28 Port LED in 40G/100G<br>Mode. (The LEDs are under the  | On/Flashing<br>Green  | QSFP28 port has a valid activity at 100G mode and the flashing to indicate activity                                                            |  |

| port24&port25 of QSFP28 cage)                                 | On/Flashing<br>Blue   | QSFP28 port has a valid activity at 40 G mode and the flashing to indicate activity.                                                           |  |

|                                                               | Off                   | There is no link on the port.                                                                                                                  |  |

| QSFP28 Port LED in 25G Fan<br>Out Mode. (With Breakout cable) | On/Flashing<br>Amber  | QSFP28 port has a valid link at 25G via<br>break out cable. The LED on 100G<br>QSFP28 end is also present OFF.<br>Flashing indicates activity. |  |

|                                                               | Off                   | There is no link on the port.                                                                                                                  |  |

| QSFP28 Port LED in 10G Fan<br>Out Mode. (With Breakout cable) | On/Flashing<br>Purple | QSFP28 port has a valid link at 10G via<br>break out cable. The LED on 40G<br>QSFP28 end is also present OFF.<br>Flashing indicates activity.  |  |

|                                                               | Off                   | There is no link on the port.                                                                                                                  |  |

| OOB Port LED (Link)                                           | On / Green            | Port has a valid link                                                                                                                          |  |

|                                                               | Off                   | There is no link on the port                                                                                                                   |  |

| OOB Port LED (Activity) | Flashing /<br>Green  | Flashing indicates activity                                     |

|-------------------------|----------------------|-----------------------------------------------------------------|

|                         | Off                  | There is no link on the port                                    |

| ToD Status LED          | On/Flashing<br>Green | ToD port has an activity and the flashing to indicate activity. |

|                         | Off                  | There is no link on the port                                    |

| BITS Status LED         | On/Flashing<br>Green | Bits port has activity and the flashing to indicate activity.   |

|                         | Off                  | There is no link on the port                                    |

## System LEDs

The system LEDs are used to indicate the status of power and system.

Figure 2 System LEDs

| System LED Definition |             |                                                      |

|-----------------------|-------------|------------------------------------------------------|

| LED                   | CONDITION   | STATUS                                               |

| PSU0                  | Green       | This power is operating normally.                    |

| (Power Supply Status) | Amber       | PWR present but not power on or this power is fault. |

|                       | Off         | Power supply not present.                            |

| PSU1                  | Green       | This power is operating normally.                    |

| (Power Supply Status) | Amber       | PWR present but not power on or this power is fault. |

|                       | Off         | Power supply not present.                            |

| DIAG                  | Green       | System self-diagnostic test successfully completed.  |

| (Diagnostic)          | Green Blink | System self-diagnostic test is in progress.          |

|                       | Amber       | System self-diagnostic test has detected a fault.    |

| FAN                   | Green       | System FAN operating normally.                       |

|     | Green Blink       | System FAN tray is power off when ambient temperature is less than 10 degree C.                                    |

|-----|-------------------|--------------------------------------------------------------------------------------------------------------------|

|     | Amber             | System FAN tray present but is fault.                                                                              |

| LOC | Amber<br>Flashing | Flashing by remote management command. Assists the technician in finding the right device for service in the rack. |

|     | Off               | Not a particular switch that technician need to find.                                                              |

#### **Front panel ports**

- Micro USB port console port

- Used for RS232 type management

- RJ45 Console Port

- Used for RS232 type management

- RJ45 10/100/1000 Ethernet management port

- Connected directly to the system CPU

- RJ45 ToD Port

- RJ45 BITs

#### **Console Port**

The console port interface conforms to the RJ45 electrical specification.

The interface supports asynchronous mode with default eight data bits, one stop bit, and no parity. The unit will operate at any one of the following baud rates:

•9600, 19200, 38400, 57600, **115200 (Default)**

| Pin number | Pin name | Pin number | Pin name |

|------------|----------|------------|----------|

| 1          | RTS      | 2          | UART_TXD |

| 3          |          | 4          |          |

| 5          | GND      | 6          | UART_RxD |

| 7          |          | 8          | СТЅ      |

#### **Network ports**

| SFP+ Ports ( sixteen in total) | Standard SFP / SFP+ MSA compliant modules supporting 1G and 10G options for copper and fiber                                                      |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| SFP28 Ports (eight in total)   | Standard SFP / SFP+ MSA compliant modules supporting<br>1G and 10G options for copper and fiber<br>Support for 25G Copper and fiber SFP28 modules |

| QSFP28 Ports ( two in total ) | Standard 40Gb QSFP+ modules including but not limited<br>to: 40GBASE-SR4, 40GBASE-LR4, 40GBASE-ER, AOC<br>Cables                 |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| QSFP28 Ports                  | Standard DAC cables including but not limited to:<br>Passive cables up to 7m,<br>QSFP<> QSFP DAC, QSFP<>SFP+ DAC Breakout        |

| QSFP28 Ports                  | Support for all standards complaint QSFP28<br>XCVRS including but not limited to 100GBASE-<br>SR4, 100GBASE-LR4                  |

| QSFP28 Ports                  | Standard DAC cables including but not limited to:<br>Passive cables up to 3m, QSFP28<> QSFP28 DAC,<br>QSFP28<>SFP28 DAC Breakout |

#### **Rear View**

The rear view of the AS7316-26X includes the following key components:

- Five(4+1) redundant hot swappable fan modules

- LED per fan module to indicate status

- Color coding to indicate airflow direction

- Chassis Grounding Lug

#### **Clock Tree**

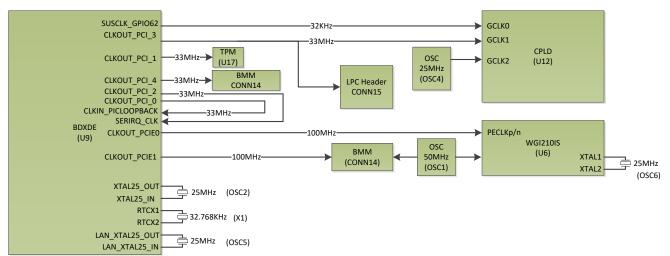

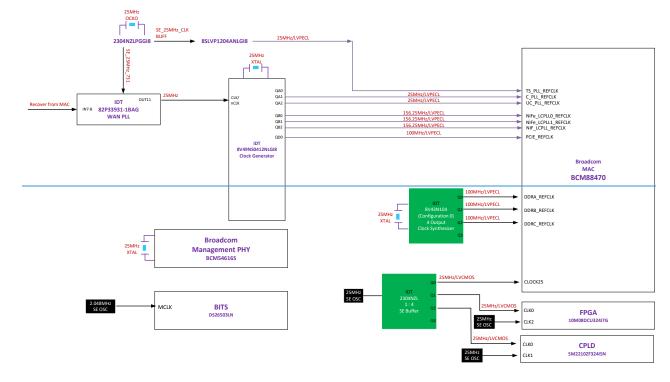

**CPU Clock Tree**

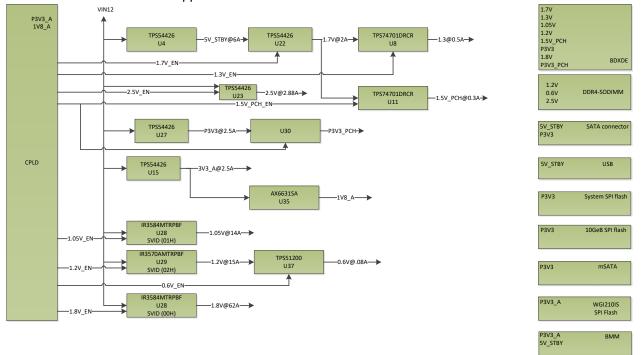

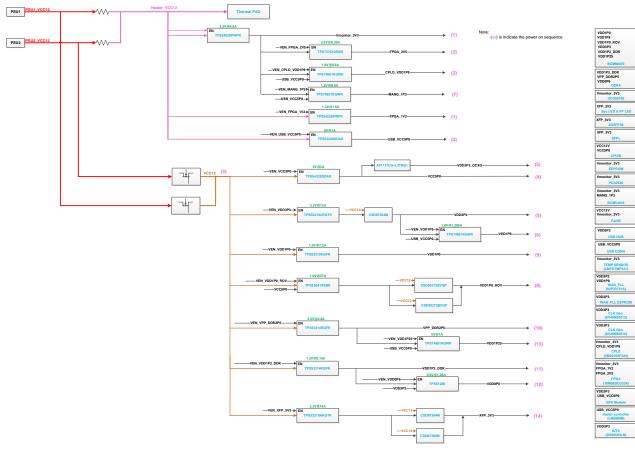

#### **Power Tree**

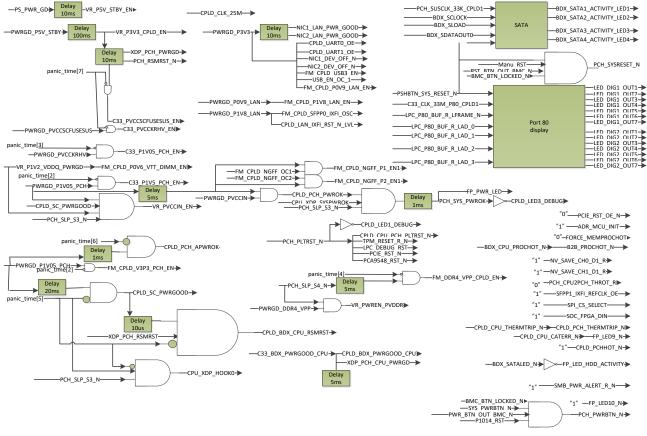

The power monitor and sequence controlled by the CPLD and there are three regulators that SVID interface need to support VR12.5 of Intel.

**Mainboard Power Tree**

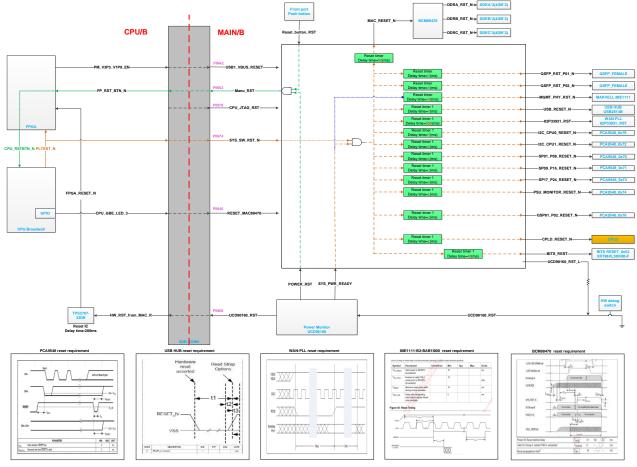

#### **Reset Tree**

**Reset Tree**

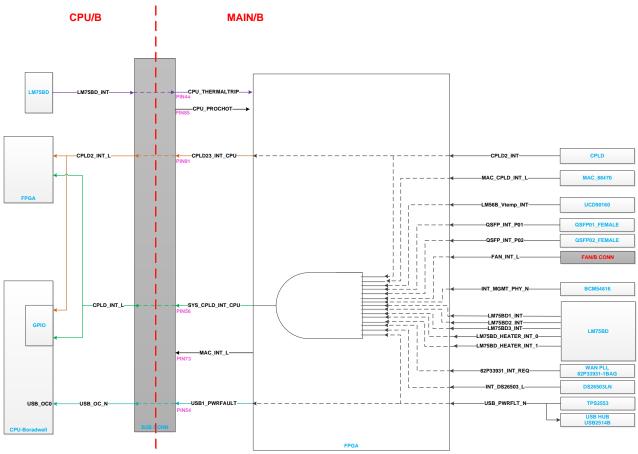

Main Board Interrupt Tree

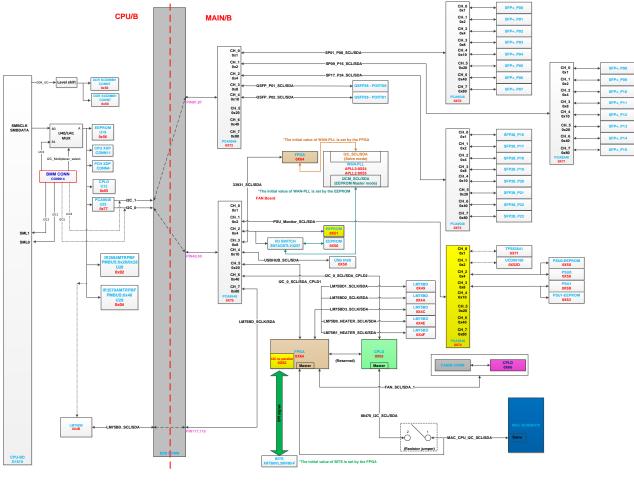

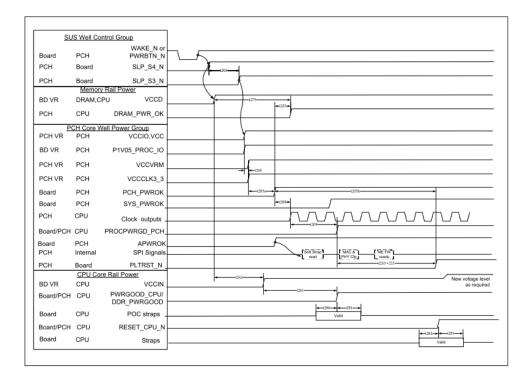

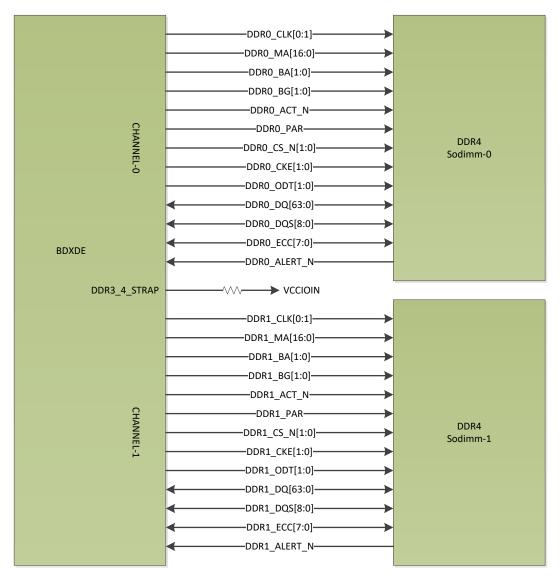

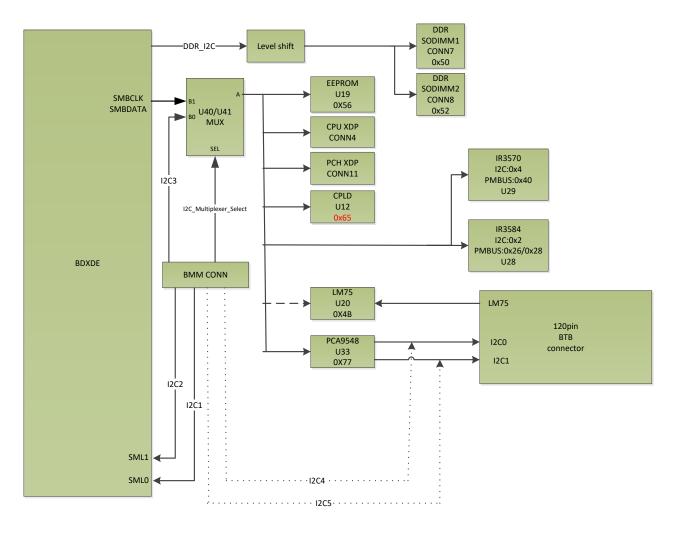

#### **I2C/SMBus Architecture**

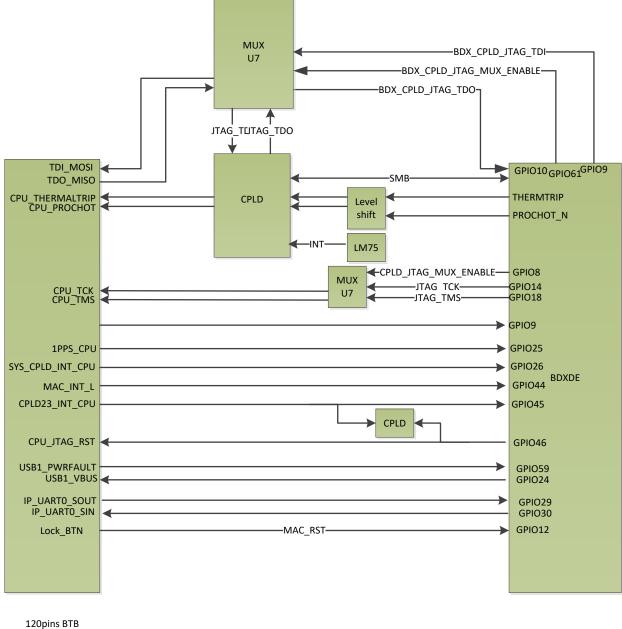

The SMbus from BDXDE can access the CPU board and main board device via SMBUSO.

The LM75 (0x4B) is accessed by the CPLD on main board.

The I2C information from DDR SPD EEPROM needs to read via another SMbus only used for DDR SPD.

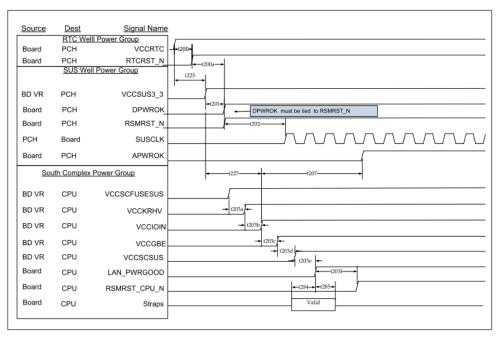

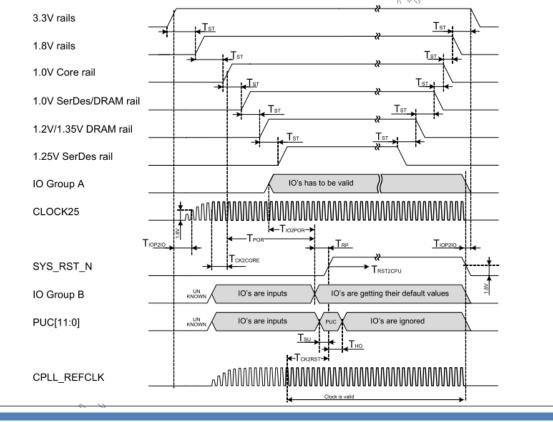

#### 1.1.1. Power-On Reset

The cores and uncore support the following reset types. Note PWRGOOD\_CPU is driven by the PCH.

Cold reset is the first time when the platform asserts PWRGOOD\_CPU and asserts RESET\_CPU\_N to the uncore. The platform has to wait for the Base Clock (BCLK) and the power to be stable before asserting PWRGOOD\_CPU. This results in reset of all the states in the processor, including the sticky state that is preserved on the other resets. PLLs come up, I/O (DMI2, uncore PCI Express, and DDR) links undergo initialization and calibration. Components in fixed and variable power planes are brought up. Ring, router, SAD, and various lookup tables in the core/Cbo are initialized. Once the

uncore initialization has completed, then the power is enabled to the cores and cores are brought out of reset. BIOS is fetched from the PCH.

Warm reset is typically a platform wide event and is indicated by assertion and deassertion of the RESET\_CPU\_N signal on the socket while PWRGOOD\_CPU remains asserted. This reset preserves the error log state and machine check bank states for use by platform debug. The warm reset preserves the error log state and machine check bank states for use by platform for post error event analysis. To maintain the DDR memory attached to the processor self refresh and sticky registers remain valid through out a warm reset, the "Reset\_warn" message must complete by the processor. The "Reset\_warn" is a message that gets issued from the PCH to all sockets prior to warm reset. BIOS will need to program the FlexRatioMSR/CSR in each socket and invoke the Warm Reset to the platform.

The reset flow is divided into the following 5 phases.

- > **Phase 0**: Expectations from the platform (before assertion of PWRGOOD\_CPU)

- Initially PWRGOOD\_CPU signal is deasserted and RESET\_CPU\_N is asserted to the socket. PWRGOOD\_CPU cannot deassert until RESET\_CPU\_N is asserted.

- PWRGOOD\_CPU must be asserted no sooner than 2 ms after the IVR Vccin supply has fully ramped-up.

- Vccioin may be brought up before Vccin for IVR is brought up if not at the same time. Vccioin is intended to source the PECI IO.

- The PWRGOOD\_CPU and RESET\_CPU\_N signals have "clean" edges.

- The reference clock (BCLK) is stable.

- All external power rails have ramped as follows: Vccin, Vccioin, VCCD are up and stable at their nominal values

- Assert PWRGOOD\_CPU (RESET\_CPU\_N still asserted) only after 2 msec of Vccin, Vccioin and VCCD at tolerance.

- After the power rails are up and stable for 2 msec and reference clocks are stable, platform asserts PWRGOOD\_CPU and continues to assert RESET\_CPU\_N signal to the socket.

- PWRGOOD\_CPU remains asserted as long as Vccin, Vccioin and VCCD remain stable.

- No power sequencing between Vccin and VCCD is required.

- Phase 1: PCU bring-up

- Phase 1a: Activity Leading to PCU Start-up

- Assertion of PWRGOOD\_CPU (the trigger to move from the end Phase 0 to the start of Phase 1a).

- Processor starts a timer (using BCLK) for determinism interval.

- The PECI and SVID interfaces are held in reset until IVR asserts its power good signal.

- The PCU PLL is enabled.

- Phase 1b: Pcode Controlled Preparing for Broad uncore Bring-Up

- Starting at the sub-phase, all steps should be synchronous.

- PCU micro controller comes out of reset to start reset pcode execution. This is the planned "re-entry" point for Warm Reset processing.

- Early reset pcode determines that it is at the start of Phase 1b.

- Pcode brings the rest of the PCU hardware out of reset.

- Pcode determines the boot config.

- Pcode issues SVID command to ramp Vccin to 1.8V for cold reset.

- Pcode reads and compares Vccin MBVR ICCMAX limit (reg 21h) vs its own supported ICCMAX limit:

- If VR's ICCMAX  $\geq$  supported ICCMAX then bootup continues.

- If VR's ICCMAX < supported ICCMAX then bootup halts and system shuts down. MSR 411h IA32\_MC4\_STATUS logs Error code 0x1e -MCA VR ICC MAX LESS THAN FUSED ICC MAX in field MSEC FW.

- Pcode sequences uncore non-boot IVRs to ramp up.

- Pcode signals uncore power good to IIO, IMC.

- Delivery of the uncore power good signals defines the transition from the end of phase 1b to the beginning of phase 1c.

- Phase 1c: PLL locking and IO Calibration

- Pcode initiates thermal sensors.

- Pcode locks PLLs in the following order: IIO, and IMC.

- Pcode instructs the ring PLLs to start locking.

- RESET\_CPU\_N signal is deasserted.

- De-assertion of RESET\_CPU\_N signal will bring PCU out of reset and signifies the transition from the end of Phase 1c to the beginning of Phase 2.

- > Phase 2: Uncore initialization and core bring up

- The starting assumptions are:

- All IVRs except core IVRs have ramped-up and are stable.

- All PLLs except core PLLs have locked.

- Phase 2 is entered as a result of de-assertion of external pin RESET\_CPU\_N.

- Boot mode related straps have been sampled and are available.

- Some IO link calibration have started and may or may not have completed by the start of this phase.

- In this phase

- PCU comes out of reset again and again determines the reset type.

- Reset is deasserted to the ring units (HA, Cbo, IIO).

- Reset is de-asserted to System Agents (IMC, IIO).

- Pcode initializes the ring stops

- Pcode performs boot mode processing based on straps. Set the advertised firmware, IO, and Intel TXT agent bits appropriately.

- Pcode services DMI2 handshake protocol. If DMI2 links are used in DMI2 mode, pcode checks if the links have trained to L0. If it's the legacy socket, and if DMI2 links does not reach L0 within 3-4 ms, pcode executes error flow.

- Pcode determines number of cores, slices and st/mt-threading for the core. In this step pcode also takes into account number of BIOS-disabled cores. Pcode determines whether BIST should be executed. BIST is executed if BIST Strap is set or requested.

- Pcode programs the logical ids and switches from physical to logical mode.

- LLC reset and configuration.

- If it's not service processor boot mode, pcode waits for links to get to parameter exchange.

- Pcode releases links to get to Normal operation (i.e. L0)

- Pcode sets core Cstate to C1

- > Phase 3: Reset execution (from core reset to fetch boot vector)

- The starting assumptions are:

- Before this phase starts, following information is provided to the core: APIC-ID, whether it's the BSP, SMT enable/disable, reset type (cold, warm, C6 exit).

- Uncore necessary to the get to the BIOS and Intel TXT Address space is fully initialized.

- In this phase:

- Initialize core's internal structures, arrays, microarchitectural and architectural state.

- Execute MLC BIST if BIST enabled.

- Initialize uncore.

- Read LLC BIST results from the uncore and report it in the EAX register.

- Report LLC and MLC BIST results.

- The core and thread selected as package BSP fetches BIOS or goes to "Waitfor-SIPI" state

- The end assumption is there is at least one thread that was designated as package BSP.

#### Phase 4: BIOS execution

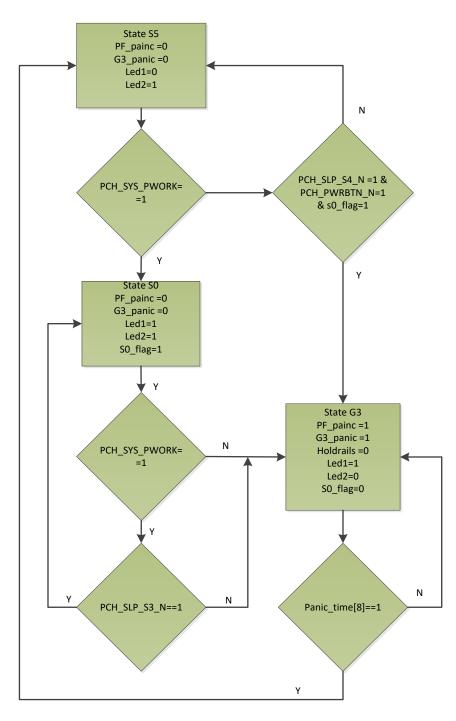

Power Sequencing Diagram G3 with RTC loss to S5

Power Sequencing Diagram S5 to S0

- BIOS has two flash memories (Flash 1/U1 and Flash 2/U31) to boot up from, the boot up sequence is same as phase 4.

- The relation of reset sequence and power on sequence:

This relation can be described from different boot status.

- Cold boot: When turning on the system after it has been powered off, the power on and reset sequence will be restarted.

- Warm boot: When restarting the system without interrupting power, the power on sequence do not restart. Reset sequence differs from power on sequence.

## 1.1.2. PCH Strap pin definition

| Strap pin       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Default       |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|                 | The field data and the desire of a strength of the strength of | Value/Setting |

| SATA1GP/ GPIO19 | This field determines the destination of accesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1             |

|                 | to the BIOS memory range. Also controllable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

|                 | using Boot BIOS Destination bit (Chipset Config                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

|                 | Registers: Offset 3410h:Bit 10). This strap is used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

|                 | in conjunction with Boot BIOS Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |

|                 | Selection 1 strap.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

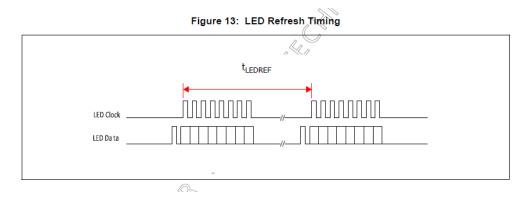

|                 | Bit11 Bit 10 Boot BIOS Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |